Professional Documents

Culture Documents

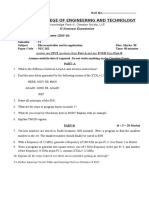

Basic Memory Interfacing To 8085

Uploaded by

Sachin PalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Basic Memory Interfacing To 8085

Uploaded by

Sachin PalCopyright:

Available Formats

Copyright 2008 by Dr.K.K.

Thyagharajan

3 . I n t e r f a c i ng M e mo r y w i t h 8 0 8 5

A microprocessor will have its own address space for accessing physical memory.

The memory locations that are directly addressed by the microprocessor is called physical

memory space. For example a microprocessor like 8085 has 16 address lines, and it can

access a physical memory space of 64K starting from 0000H to FFFFH as shown in

Table 3.1. The process of interfacing memories to microprocessor and allocating address

to each memory location is called memory mapping. The complete address space may be

considered as a single memory block. But practically, when ICs are used as memory

devices, instead of a single IC (Integrated Chip), few devices that fit into the address

space will be used. This is due to the fact a microprocessor based system requires at least

one ROM/EPROM and a RAM. For example instead of using a memory device of size

64KB (Kilo Bytes), we can use 8 memory devices with a capacity of 8KB each. This will

reduce the chip replacement cost while servicing the microprocessor-based system. When

memory blocks are used, to access all the locations in a block n address lines are needed

so that

2n = 8 K

= 23 K

= 23 x 210

= 213

Therefore n = 13

3.1

Address Decoding and Memory Mapping

Memory address decoding is nothing but to assign an address for each location in

the memory chip. The data stored in the memory is accessed by specifying its address.

Memory address can be decoded in two ways

i)

Absolute or Fully decoding

and

ii)

Linear Select or Partial decoding

There are many advantages in absolute address decoding. They are

i)

Each memory location has only one address, there is no duplication in the

address

ii)

Memory can be placed contiguously in the address space of the

microprocessor

iii)

Future expansion can be made easily without disturbing the existing

circuitry

There are few disadvantages in this method

i)

Extra decoders are necessary

ii)

Some delay will be produced by these extra decoders.

Copyright 2008 by Dr.K.K.Thyagharajan

The main advantage of linear select decoding is its simplified decoding circuit.

This reduces the hardware design cost. But there are many disadvantages in this

decoding.

i)

Multiple addresses are provided for the same location

ii)

Complete memory space of the microprocessor is not efficiently used

iii)

Adding or interfacing ICs with already existing circuitry is difficult.

3.1.1

Absolute Address Decoding

The 8085 microprocessor has 16 address lines. Therefore it can access 216

locations in the physical memory. If all these lines are connected to a single memory

device, it will decode these 16 address lines internally and produces 216 different

addresses from 0000H to FFFFH so that each location in the memory will have a unique

address as shown in table 3.1 and figure 3.1. This is called absolute address decoding.

Figure 3.1 is called the memory map of 8085 address space and it shows how each

location in the physical memory gets an address from the address space of the

microprocessor.

A15 A14 A13 A12

0 0 0

0

A11 A10 A9 A8

0 0 0 0

A7 A6 A5 A4

0 0 0 0

A3 A2 A1 A0

0 0 0 0

Hex Address

0000H

0 0

0001H

0 0

0002H

- - - - -

FFFEH

FFFFH

Table 3.1: Memory Address

Copyright 2008 by Dr.K.K.Thyagharajan

FFFF H

FFFE H

FFFD H

8001 H

8000 H

7FFF H

0002 H

0001 H

0000 H

Figure 3.1: 64KB Memory Map

(Single Block)

Instead of connecting all the 16 address lines to a single 64 KB memory device,

we can also use memory devices of lower capacity. In such cases the physical memory

space of the microprocessor is divided into smaller memory spaces or memory blocks.

Each block is selected by a block select address signal and the memory locations with in

a block are accessed by the processors address lines. This is called address portioning.

For example if the memory device (memory block) has only 13 address lines, we can use

the lower 13 address lines (A0 A12) to access the locations with in a memory block and

the remaining 3 lines (A13, A14 and A15) to access 8 such blocks. These three lines are

called the block select address signals and this is called address partitioning.

Depending on the number of memory blocks, the number of block select address lines

will change. The starting address and ending address of each block can be found as

shown in Table 3.2. Since each block is an Integrated Chip (IC), and each chip has a

Chip Select signal, the block select address lines must be used to select the ICs. We have

to produce eight chip select signals from the three address lines. Therefore we have to

decode these lines using a 3 to 8 decoder or 1 of 8 decoder. In this case the lower thirteen

address lines of the processor are connected to the 13 address lines of the memory chip

and hence they are internally decoded in the memory. The higher 3 address lines (A13,

A14 and A15) are externally decoded by a 3 to 8 decoder. Since three lines can provide a

maximum of 8 addresses, in this case they are said to be fully decoded and hence each

location in each block has a specific unique address as shown in table 3.2. This is called

as absolute address decoding. The diagrammatic representation of each block with its

address range shown in figure 3.2 is called the memory map of the microprocessor

system.

Copyright 2008 by Dr.K.K.Thyagharajan

4

Hex

Address

range

0000H to

Block

No

A15A14A13 A12

A11 A10 A9A8

A7 A6 A5 A4

A3 A2 A1 A0

0 0

0 0

0 0

0 0

0

1

1

0

1

0

1

0

1 1

0 0

1

0

1

0

1

0

1

0

1 1

0 0

1 1 1FFFH

0 0 2000H to

0

0

0

1

1

0

1

0

1

0

1

0

1 1

0 0

1

0

1

0

1

0

1

0

1 1

0 0

1 1 3FFFH

0 0 4000H to

0

0

1

1

0

1

1

0

1

0

1

0

1 1

0 0

1

0

1

0

1

0

1

0

1 1

0 0

1 1 5FFFH

0 0 6000H to

0

1

1

0

1

0

1

0

1

0

1

0

1 1

0 0

1

0

1

0

1

0

1

0

1

0

1

0

1 1

0 0

7FFFH

8000H to

1

1

0

0

0

1

1

0

1

0

1

0

1 1

0 0

1

0

1

0

1 1

0 0

1

0

1

0

1 1

0 0

9FFFH

A000H to

1

1

0

1

1

0

1

0

1

0

1

0

1 1

0 0

1

0

1

0

1 1

0 0

1

0

1

0

1 1

0 0

BFFFH

C000H to

1

1

1

1

0

1

1

0

1

0

1

0

1 1

0 0

1

0

1

0

1 1

0 0

1

0

1

0

1 1

0 0

DFFFH

E000H to

1 1

1 1

1 1

FFFFH

Table 3.2: Address Space for Memory Blocks

0 0

Copyright 2008 by Dr.K.K.Thyagharajan

FFFF Memory

RAM 7

Block8(8KB)

E000

DFFF

Memory

RAM 6

Block7(8KB)

C000

BFFF Memory

RAM 5

A000 Block6(8KB)

9FFF Memory

RAM 4

8000 Block5(8KB)

7FFF Memory

RAM 3

6000 Block4(8KB)

5FFF Memory

RAM 2

4000 Block3(8KB)

3FFF Memory

RAM 1

Block2(8KB)

2000

1FFF Memory

EPROM

Block1(8KB)

0000

Figure 3.2: 64KB Memory Map

(Eight Blocks)

We use 74LS138 address decoder to generate the chip select signals for each

memory block. In this decoder when the address lines A13, A14 and A15 are 000, the

output line Y0 will be activated as shown in figure 3.3. This in turn selects the first

memory block. Similarly when these lines are 001 (C=0, B=0 and A=1) Y1 will be

activated and the second memory block will be selected. When the 8085 microprocessor

is reset the contents of the program counter will be 0000H. Since this content is placed on

the address bus while accessing the memory, the microprocessor will start executing the

program from the address 0000H. A monitor program must be placed starting from this

address, so that it reads the inputs and takes action based on that program. The input may

even be a function key that requires a specific action to be carried over. Since this

program is fixed and developed by the manufactures of the product it is called as

firmware and it is stored in a ROM or in an EPROM. Therefore, in any microprocessor

based system an EPROM should be placed at the reset address (0000H). In addition to

EPROM, any microprocessor based system would require at least few RAM locations to

store temporary data. Specifically there should be a RAM for stack operations. So,

though we are using eight memory chips of 8KB size each, at least one of the eight ICs

must be an EPROM and it should be placed at the starting address of 0000H. The

memory map for this case can be given as shown in figure 3.2. The EPROM chip must be

selected using the chip select signal CS1 and the RAM1 chip must be selected using CS2.

The memory interface diagram may be given as shown in Figure 3.4.

Copyright 2008 by Dr.K.K.Thyagharajan

Block

Select

Address

Signals

A13

Y0

CS1

A14

Y1

CS2

A15

Y2

CS3

74LS138 Y3

CS4

Y4

CS5

G1

Y5

CS6

G2

Y6

CS7

G3

Y7

CS8

+5V

IO/M

Block

Select

Signals

Figure 3.3: Memory Block Decoder

In this type of memory interfacing, all the address lines (A0 to A15) have been

used. Each location in the memory will have a single address. This type of address

decoding is called as absolute or fully decoded addressing.

Most of the microprocessor based systems do not use the complete 64 KB

memory space. Even one EPROM and a RAM will be sufficient. For example in the

memory map shown in figure 3.2, if only the EPROM and RAM 2 are used in the

practical system, the memory map of such a system can be given as shown in figure 3.5.

Still each location has single address. Therefore it is also called absolute address

decoding. The main advantage of this type of decoding is, you can add memory devices

for this system without disturbing the already connected devices. The memory interface

diagram for this case is given in figure 3.6.

Copyright 2008 by Dr.K.K.Thyagharajan

Copyright 2008 by Dr.K.K.Thyagharajan

FFFF

E000

DFFF

Unused memory space

C000

BFFF

A000

9FFF

8000

7FFF

6000

5FFF Memory

RAM 2

4000 Block3(8KB)

3FFF

2000

1FFF Memory

EPROM

Block1(8KB)

0000

Figure 3.5: Memory Map with EPROM and RAM 2

A13

A14

Y1

A15

Y2

+5V

IO/M

CS1

Y0

74LS138

Y3

CS2

CS3

CS4

Y4

CS5

G1

Y5

CS6

G2

Y6

CS7

G3

Y7

CS8

CS

RAM 2

CS

EPROM

A0 - A12 Address Bus

Figure 3.6: Interfacing EPROM and RAM

Instead of using 3 to 8 decoder, NAND/AND/OR gates can also be used to

generate chip select signals as shown in figure 3.7. In this case, CS1 will be activated to

select the EPROM, when all the three inputs to the OR gate (OR1) are zero. Similarly the

chip select signal CS3 will be activated to select RAM 2 only when A13 = 0, A14 = 1 and

A15 = 0. This is also an absolute address decoding method. But, here we need more

Copyright 2008 by Dr.K.K.Thyagharajan

decoders (gates) when we want to add more memory chips. The main advantage of the

absolute address decoding is the contiguous placement of the memory locations. So no

memory space of the microprocessor is wasted without being used.

A13

OR 2

OR 1

A13

A14

CS1

A14

CS3

A15

A15

CS

CS

RAM 2

8K

EPROM

8K

A0 - A12 Address Bus

Figure 3.7: Address Decoding using OR Gates

3.1.2

Linear Select Address Decoding

In the circuit given in figure 3.8, the address line A15 of the microprocessor has

not been used for decoding the chip select signals. The outputs Y0 and Y2 of the 74LS138

decoder will be activated as given in table 3.3. Since the address line A15 is not connected

to the decoder and the pin C of the decoder has been grounded, irrespective of the signal

A15 (i.e.A15 is 0 or 1), the pin C is 0. So, you will get Y0 selected twice i.e. when A15 = 0

and when A15 = 1. Similarly Y2 will also be selected twice. Therefore the address map for

the EPROM and RAM is found as shown in Table 3.4.

A15 C

0

0

1

1

0

0

0

0

A14

B

0

1

0

1

A13

A

0

0

0

0

Y0

Y2

0

1

0

1

1

0

1

0

Table 3.3: Linear Select Address Decoding Chip Select Signals

Copyright 2008 by Dr.K.K.Thyagharajan

A13

Y0

A14

Y1

Y2

+5V

74LS138

IO/M

Y3

10

CS1

CS2

CS3

CS4

Y4

CS5

G1

Y5

CS6

G2

Y6

CS7

G3

Y7

CS8

CS

CS

EPROM

RAM 2

A0 - A12 Address Bus

Figure 3.8: Linear Select Address Decoding - Circuit Diagram

Block

No

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

0

0 0

0 0

0

0

0

1

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1 1

0 0

1 1

0 0

0

1

1

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1 1

0 0

1 1

0 0

1

1

0

1

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1 1

0 0

1 1

0 0

1 1

0 0

1 1

1 1

1 1

Hex

Address

range

0000H

to

1FFFH

4000H

to

5FFFH

8000H

to

9FFFH

C000H

to

DFFFH

Table 3.4: Linear Select Decoding Memory Address Ranges

The same EPROM is selected both for the address range 0000H to 1FFFH and

8000H to 9FFFH. This is due to the signals A13 and A14 which have same values in both

the cases and hence activates the same chip select signal CS1. Similarly the RAM is

selected both for the address range 4000H to 5FFFH and C000H to DFFFH. The memory

map for this case is as shown in figure 3.9.

Copyright 2008 by Dr.K.K.Thyagharajan

11

FFFF

E000

DFFF

Memory

C000 Block7(8KB)

BFFF

A000

9FFF Memory

8000 Block5(8KB)

7FFF

6000

5FFF Memory

4000 Block3(8KB)

3FFF

RAM 2

Unused memory

space

EPROM 1

RAM 2

2000

1FFF Memory

0000

Block1(8KB) EPROM 1

Figure 3.9: Linear Select Address Decoding Memory Map

A13

OR 2

OR 1

A13

CS1

CS3

A14

A14

CS

EPROM

8K

CS

RAM 2

8K

A0 - A12 Address Bus

Figure 3.10: Linear Select Address Decoding using OR gates

In this type of address decoding, if we want to add a RAM chip at the address

space 8000H to 9FFFH, which was unnecessarily occupied by the first EPROM, we have

to change the decoding circuit. We may not simply add additional circuitry without

disturbing the already existing circuit. In this method each location in the physical

memory is accessed by more than one address (here two addresses) i.e. address space is

wasted. This type of address decoding is called as Linear Select or partially decoded

addressing. This happens when we have few address lines without being used for

decoding. The same circuit can also be implemented using OR gates as shown in figure

3.10. In this circuit the OR gates require only two inputs. This is possible, since we have

left A15 address line unconnected. Therefore, linear select addressing reduces the

hardware requirements.

Copyright 2008 by Dr.K.K.Thyagharajan

3.2

12

Bus Contention

Consider the timing diagram shown in figure 3.11 that reads a byte (opcode) from

the memory. At the end of the ALE signal, all the 16 bits of the address will be available

on the bus. The decoder (74LS138) produces the chip select signals from these address

lines after a small decoding delay. The chip select signal will be generated with in 30 ns

after the trailing edge of ALE signal. When the chip select signal enables the memory

chip, since the address has been already placed on the address pins of the memory, the

memory will place the data on the data lines after a small access delay called the memory

access time. The output buffer of the memory will be enabled within 20 ns after getting

CS signal. The memory access time is the time delay between the address placed on the

address bus by the address decoder and the data placed by the memory on the data bus. If

the data are placed before the end of the T1 state, both the lower order address and the

data from the memory will be placed on the AD0 AD7 lines i.e. both the microprocessor

and the memory try to access the same lines as shown in figure 3.11 by hashed lines. If

the microprocessor tries to place 1 (+5V) and the memory tries to place 0 (0 V or

Ground), then the microprocessor pin will be shorted through the memory. This may

even damage the processor. This is called bus contention. So, the bus contention will

occur when two ICs try to place data on the same bus at the same instant of time. This

effect will be very adverse in the case of high speed memories interfaced with slow

processors. Since the RD or WR signal is issued by the processor only after the first Tstate, if these signals are used along with the output of the address decoders to select the

chip, the content of the memory will not be placed before the start of the T2 state.

Copyright 2008 by Dr.K.K.Thyagharajan

T2

T1

13

T3

T4

CLK

A15

A8

AD7

41H

Unspecified

High-Order Memorry Address

Low-Order address

Data from memory

00H

4FH Opcode

AD0

C

Delay in the decoder

ALE

CS

Access Time

Bus Contention

G

Data from

the Memory

4FH Opcode

H

Bus Contention

CS

RD

D

A

Avoiding Bus

Contention

Figure 3.11: Bus Contention Reading Opcode from the Memory

Copyright 2008 by Dr.K.K.Thyagharajan

A13

Y0

A14

Y1

A15

Y2

+5V

IO/M

RD

CS1

CS2

CS3

Y3

CS4

Y4

CS5

G1

Y5

CS6

G2

Y6

CS7

Y7

CS8

74LS138

G3

14

WR

CS

RAM 2

CS

EPROM

A0 - A12 Address Bus

Figure 3.12: Avoiding Bus Contention

By using a standard 3 to 8 decoder as shown in figure 3.12, the CS signal can be

delayed until the end of T1 state. The address decoder is enabled by the G3 signal and

hence the CS signal is generated only when RD or WR is low. In figure 3.11, point A

activates point B and point B in turn activates point C to avoid bus contention.

If you are using logic gates to decode the addresses, bus contention may be

avoided by combining the output of the final stage of the decoder with RD or WR signal

to produce an active low chip select signal.

NB: Instead of connecting the RD or WR signals to the input or output of the

address decoder, the best practice to avoid bus contention is to connect the RD signal to

the OE pin of EPROM/RAM and WR signal to R/W pin of RAM.

Example 3.1:

Interface a 4K EPROM, one 4K RAM and one 8K RAM to a microprocessor with

the following Memory Map.

Copyright 2008 by Dr.K.K.Thyagharajan

15

Figure 3.13: Memory Map

A memory chip select decoder is used to provide chip select signal for each

memory device (IC). This will decide the address range that is allotted for each memory

IC. 74LS138 is a 3 to 8 decoder and it can be used for this purpose. In this example the

minimum memory block size is 4K. To access 1K locations 10 address lines must be used

(210 =1K = 1024 locations). So to access 4K locations (4 X 1K = 22 X 210 = 212) 12

address lines (A0 A11) must be used. Since 8085 has 16 address lines the decoding can

be indicated as shown below.

Figure 3.14: Variable Address Lines

While accessing 4 K locations the lower 12 bits (A0 A11) can have either 0 or 1.

If all the 12 bits are 0 then that will be the starting address of that memory block if all 12

bits are 1 that will be the end address of the block. The remaining 4 address lines (A12 A15) are the block select address signals, which decide the memory block number. For

example, if A15 A12 is 0000 then memory block that can be accessed by the remaining

address lines is block 0. If it is 0001 the memory block that can be accessed is 1. Note

that the memory blocks 5 and 6 are combined because a 8-K RAM is to be placed there.

The following table shows the starting and ending address of each memory block.

Copyright 2008 by Dr.K.K.Thyagharajan

Block

No

A15 A14 A13 A12 A11 A10 A9 A8

16

A7 A6 A5 A4

0 0

0 0 0

0 0

0

0

0

0

0 0

0 1

1

0

1 1 1

0 0 0

1 1 1 1

0 0 0 0

1 1 1 1

0 0 0 0

0

0

0

0

0

1

1

0

1

0

1 1 1

0 0 0

1 1 1 1

0 0 0 0

1 1 1 1

0 0 0 0

0

0

0

0

1

1

0

1

1

0

1 1 1

0 0 0

1 1 1 1

0 0 0 0

1 1

0 0

1

0

1

0

0

0

0

1

1

0

1

0

1

0

1 1 1

0 0 0

1 1 1 1

0 0 0 0

1 1

0 0

1

0

1

0

0

0

1

1

0

0

0

1

1

0

1 1 1

0 0 0

1 1 1 1

0 0 0 0

1 1

0 0

1

0

1

0

1 1

0 0 0

1 1 1 1

:

:

:

0 0 0 0

0 0 0

1 1 1

15

1 1

1 1

0 0

A3 A2 A1 A0

1 1 1 1

0 0

Hex

Address

Range

0000H

to

0FFFH

1000H

to

1FFFH

2000H

to

2FFFH

3000H

to

3FFFH

4000H

to

4FFFH

5000H

to

5FFFH

F000H

to

FFFFH

Table 3.5: Memory Map

The 74LS138 decoder has three input pins marked as CBA when all these three

pins are 0 then the output pin O0 will be activated i.e. O0 becomes zero. When CBA is

001 the O1 will be activated and all other output pins will be at high state. i.e. any one of

the output pins O0 to O7 is selected based on the input A, B and C and this will happen

only if the control pins G1, G2 and G3 are properly activated. Table 3.5 shows that

address line A15 is always zero for the address range 0000H to 6FFFH. So this can be

connected to G3 pin of the 74LS138. The output pins of 74LS138 must be selected only

for memory operations. During memory operations IO/M = 0. So IO/ M is connected to

G2 pin of the 74LS138 and hence for any IO operation the chip 74LS138 will not

activate any of the output pins. The pin G1 is connected to +5V through a resistor to

enable 74LS138.

The O0 pin of 74LS138 is connected to the chip select (CS) signal of the 4K

EPROM. This allows selecting this EPROM chip when the microprocessor sends

address in the range 0000H to 0FFFH. Similarly O1 pin of 74LS138 is connected to the

CS of 4K RAM. Since no memory chip is connected in the address range 2000H to

3FFFH, the output pin Q2 is left free. The 8K RAM requires address from 4000H to

Copyright 2008 by Dr.K.K.Thyagharajan

17

5FFFH and these addresses are covered by Q4 and Q5 pins. So these two pins are

connected to a two input AND gate. The output of the AND gate is connected to the chip

select pin of the RAM and this CS will be activated (active low) if either Q4 or Q5 is low.

i.e. the output of the AND gate will be 0 for the addresses 4000H to 5FFFH and hence the

8K RAM chip is selected for this address range.

C B

0 0

0 0

0 1

0 1

1 0

1 0

1 1

1 1

A

0

1

0

1

0

1

0

1

Output pin Activated

O0

O1

O2

O3

O4

O5

O6

O7

Table 3.1: Function Table of 74LS138

The address lines A0 to A11 of 8085 MPU must be connected to the corresponding

address pins of the memory chip and the data lines D0 to D7 of MPU must be connected

to the corresponding data pins of all the memory chips. Since 8K RAM has 13 address

lines in addition to the twelve address lines (A0 to A11) A12 of MPU must also be

connected to the A12 pin of the 8K RAM. You note that bus contention is not addressed in

this circuit.

A

A12

Y0

0000 - 0FFF

A13

Y1

1000 - 1FFF

A14

Y2

2000 -2FFF

Y3

3000 - 3FFF

+5V

74LS138

IO/M

A15

Y4

4000 - 4FFF

G1

Y5

5000 - 5FFF

G2

Y6

6000 - 6FFF

Y7

7000 - 7FFF

G3

From MPU

Address Bus A11 . . . A0

CS

4K

EPROM

From MPU

CS

4K

RAM

Data Bus D7 . . . D0

Figure3.15: Memory Interfacing

A12

CS

8K

RAM

Copyright 2008 by Dr.K.K.Thyagharajan

3.3

18

Interfacing low speed memory

To avoid bus contention, the RD or WR signal of the microprocessor is used

along with the address decoding to produce the CS signal for the memory. The RD or

WR signal starts approximately in the middle of the T2 state and available up to the end

T3 state. If the microprocessor operates at 3 MHz, these signals are available for

approximately 1.5 T state or 500 ns (1.5 / 3 MHz = 0.5 micro seconds) and hence the

memory access time should be less than 500 ns. If the memory access time is more than

this value the data cannot be read. If a low speed memory has access time greater than

this value, Wait cycles are introduced between T2 and T3. In such a case, the CS select

signal need not be delayed until RD or WR signals are issued by the microprocessor. The

memory can decode the address as soon as it gets the address from the microprocessor. In

this case the total delay introduced will be equal to the sum of the delays introduced by

the decoder, wait cycles and the delay introduced due to memory access time. For

example 2716 EPROM has access time of 450 ns and therefore it can be directly

interfaced with 3 MHz 8085, but one wait cycle is necessary if it is interfaced with a

microprocessor operating at 5 MHz. A low speed memory can also be interfaced with a

high speed processor by using low frequency crystal but this will slow down not only the

memory read/write operation but all activities of the processor.

The READY pin of 8085 processor is used to introduce wait states. For normal

operations of the processor this pin should be connected to logic high. When this pin is

made low, the processor will enter into wait state until it is made high again. A special

circuitry called Wait State Generator as shown in figure 3.16 is required for this purpose.

This circuit will introduce a wait state equal to one T-state of the processor cycle as

shown in figure 3.17. The ALE signal fed to the clock input of the first D-type flip-flop

will transfer the logic high input (+5V) placed on its D0 pin to Q0 during its positive edge.

The Q0 output is connected to D1 input of the second flip-flop. So, the logic high output

on Q0 will be transferred to the output Q1 of the second flip-flop during the positive edge

of T2 state. The complement value of Q1 is available on Q1 pin of the second flip-flop.

This will reset the first flip-flop i.e. Q0 will become logic 0 as shown in figure 3.17. At

the same time since Q1 has been connected to the READY pin of the processor, the

processor enters into wait state. It will remain in that state until Q1 becomes high. This

extends the length of the RD signal as shown in figure 3.17 and allows memory to take

one more clock period time to place the contents on the bus. The logic 0 placed on D1 pin

during this time will be transferred to Q1 in the positive edge of the next clock cycle (T3

state). This will make Q1 logic high and hence the READY signal becomes high and the

processor continues its work. It should be noted that wait state can be introduced in any

machine cycle of 8085 except in bus idle cycle. The 8085 checks the READY signal at

the second T-state of every machine cycle.

Copyright 2008 by Dr.K.K.Thyagharajan

D Flip-Flop

+5V

ALE

D Flip-Flop

Q0

D0

19

Q1

D1

CLK

CLK

Q0

Q1

To READY

Pin of 8085

CLKOUT from 8085

Figure 3.16: Wait State Generator

Memory Read

T1

T2

Memory Read

T3

TWAIT

POSITIVE OR LEADING EDGE OF THE CLOCK CYCLE

CLK

A15

A8

AD7

AD0

41H

High-Order Memorry Address

Low-Order address

00H

Data

Delayed Data

4FH

+VE EDGE

ALE

Q0

READY/ Q1

RD

EXTENDED READ SIGNAL

Figure 3.17: Timing Diagram with Wait State

T1

Copyright 2008 by Dr.K.K.Thyagharajan

3.4

20

Interfacing More than 64K Memory

The 8085 microprocessor can address only 64K memory at a time, if you want to

interface more than 64K memory; you can use a jumper or an IO port bit as shown in

figure 3.18. the chip select signal CS3 will select RAM 2 if the jumper connects B and C

and it will select RAM 3 if the jumper connects A and B. Similarly CS4 will select RAM

4 if the port bit is zero and RAM 5 if the port bit is one. The main difference between

jumper selection and port bit selection is the manual selection in the first case and

automatic or program activated selection in the second case.

CS1

A14

Y0

A15

Y1

CS2

Y2

CS3

+5V

74LS138 Y3

CS4

Y4

IO/M

G1

Y5

G2

Y6

G3

Y7

CS

PORT BIT

16K

RAM 5

CS

16K

RAM 4

CS

CS

16K

RAM 3

16K

RAM 2

CS

16K

RAM1

CS

16K

EPROM

A0 - A13 Address Bus

Figure 3.4: Memory Interface Diagram

Figure 3.18: Interfacing more than 64 K Memory

Summary

A microprocessor has address space for memory. Any memory chip that is being

interfaced with processor must fit into this memory space. A memory map diagram

shows the address boundary for each memory chip interfaced with the processor and an

address decoder decides the address range for each chip. There are two types of address

decoding viz absolute address decoding and linear select address decoding. When high

speed memories are interfaced with slow processors bus contention may occur and when

a low speed memory is to be accessed by a fast processors wait state must be introduced

using external circuitry.

You might also like

- Basic Concepts of Memory Interfacing - ComputerSCDocument7 pagesBasic Concepts of Memory Interfacing - ComputerSCParamartha BanerjeeNo ratings yet

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- Mupi 2 MarksDocument11 pagesMupi 2 Marksveeyesyes08No ratings yet

- Memory InterfacingDocument14 pagesMemory InterfacingSusmita Sau100% (3)

- Lec - A-03 - Introduction To Digital Logic and Boolean Algebra 1920Document112 pagesLec - A-03 - Introduction To Digital Logic and Boolean Algebra 1920hbfagfjafasebaNo ratings yet

- Arm Program ModelDocument4 pagesArm Program ModelvlkumashankardeekshithNo ratings yet

- Chapter 2.1-Introduction To 8085 Instruction SetDocument47 pagesChapter 2.1-Introduction To 8085 Instruction SetBulbula KumedaNo ratings yet

- Microprocessors & Interfacing For GITAM University ECEDocument118 pagesMicroprocessors & Interfacing For GITAM University ECEDr Sreenivasa Rao Ijjada100% (1)

- Difference Between RISC and CISC Architectures and Its ApplicationsDocument10 pagesDifference Between RISC and CISC Architectures and Its ApplicationsAnonymous U8awvgZ3pDNo ratings yet

- Microprocessors & Interfacing Techniques Assignment No. 2Document2 pagesMicroprocessors & Interfacing Techniques Assignment No. 2Abdullah Nasir100% (4)

- Scheme E - Digital Techniques and Microprocessor Sample Question PaperDocument3 pagesScheme E - Digital Techniques and Microprocessor Sample Question PaperHarshal DevadeNo ratings yet

- Basic Computer Model and Units ExplainedDocument15 pagesBasic Computer Model and Units ExplainedsheetalNo ratings yet

- Question Bank - 150504 - Session - 19 - 20Document14 pagesQuestion Bank - 150504 - Session - 19 - 20Aashutosh TiwariNo ratings yet

- BSNL Data AnkitDocument30 pagesBSNL Data Ankitguptaekta20No ratings yet

- Lec - A-01 - Number Systems and CodesDocument97 pagesLec - A-01 - Number Systems and Codescys96No ratings yet

- Optimize DMA Controller Data TransferDocument25 pagesOptimize DMA Controller Data Transfersatyanarayana12No ratings yet

- DE09 SolDocument157 pagesDE09 SolRakesh KumarNo ratings yet

- Microcontrollers: Introduction to 8051 and MSP430Document124 pagesMicrocontrollers: Introduction to 8051 and MSP430ManojKumarNo ratings yet

- Assembly Language Program With 8085 MicroprocessorDocument22 pagesAssembly Language Program With 8085 MicroprocessorSithija AlwisNo ratings yet

- UNIT-5: Task CommunicationDocument30 pagesUNIT-5: Task CommunicationFarheenNo ratings yet

- Cpu BusDocument31 pagesCpu BusK.R.RaguramNo ratings yet

- Rev MidtermDocument17 pagesRev MidtermraqibappNo ratings yet

- Minimum and Maximum Modes of 8086Document3 pagesMinimum and Maximum Modes of 8086Riya Chaudhary100% (1)

- 8085 Microprocessor Timing DiagramDocument29 pages8085 Microprocessor Timing DiagramgokulchandruNo ratings yet

- Microprocessor Lab ManualDocument97 pagesMicroprocessor Lab ManualSOWKATHKUTHBUDEEN_J14100% (2)

- EC6503-Transmission Lines and WaveguidesDocument15 pagesEC6503-Transmission Lines and WaveguidesAnonymous lt2LFZH100% (1)

- Computer Organization-Basic Processing UnitDocument48 pagesComputer Organization-Basic Processing Unitwww.entcengg.com100% (2)

- Microprocessors, Micro Controller Assembly LanguageDocument60 pagesMicroprocessors, Micro Controller Assembly LanguageRikesh BhattacharyyaNo ratings yet

- ECE 513 - PART1-Introduction To PIC16F84ADocument46 pagesECE 513 - PART1-Introduction To PIC16F84AMitch100% (1)

- Microcontroller Based Digital Code Lock: Submitted By: C. Theja DeepakDocument31 pagesMicrocontroller Based Digital Code Lock: Submitted By: C. Theja DeepakDeepak Tej100% (3)

- IT1402 Nov Dec+2009Document20 pagesIT1402 Nov Dec+2009piccoloashNo ratings yet

- 8255Document39 pages8255Mohit VermaNo ratings yet

- 8051 Enhanced)Document58 pages8051 Enhanced)Vinay Nagnath Jokare100% (1)

- Unit5-8051 4th Sem Anna University CseDocument21 pagesUnit5-8051 4th Sem Anna University CseVijayashree VenkatNo ratings yet

- Microprocessor and Architecture Solution PDFDocument23 pagesMicroprocessor and Architecture Solution PDFKarmaveer Bhaurao Patil CollegeNo ratings yet

- 8085 Programming Examples - CollegeekDocument6 pages8085 Programming Examples - CollegeekH Aries OñaNo ratings yet

- Microprocessor and AssemblyDocument85 pagesMicroprocessor and AssemblyMilan BhandariNo ratings yet

- 8051 Questions and Answers For Freshers - SanfoundryDocument4 pages8051 Questions and Answers For Freshers - SanfoundrySumit SrivastavaNo ratings yet

- Pipelining in Computer ArchitectureDocument46 pagesPipelining in Computer ArchitectureMag CreationNo ratings yet

- Question Bank-Microprocessor and ApplicaionDocument38 pagesQuestion Bank-Microprocessor and Applicaionchandrasekar100% (5)

- Traffic Light Controller Using 8085 MicroprocessorDocument6 pagesTraffic Light Controller Using 8085 MicroprocessorChristo100% (1)

- Microcontrollers and Embedded SystemsDocument35 pagesMicrocontrollers and Embedded SystemsTarek BarhoumNo ratings yet

- Antennas at Cell SiteDocument14 pagesAntennas at Cell SiteMark Abadies100% (1)

- Motor m49sp 1 eDocument2 pagesMotor m49sp 1 eRené Isaac Martínez OlivaNo ratings yet

- Instruction PipelineDocument27 pagesInstruction PipelineEswin AngelNo ratings yet

- Answers of Microprocessor (8085) & Electronics FAQDocument21 pagesAnswers of Microprocessor (8085) & Electronics FAQsoumyadev100% (23)

- 8085 NotesDocument60 pages8085 NotesDavid TalamNo ratings yet

- Dac Interface To 8051 PDFDocument4 pagesDac Interface To 8051 PDFRAVI100% (1)

- BJT (Bipolar Junction Transistor) : Level-1Document25 pagesBJT (Bipolar Junction Transistor) : Level-1kalyanNo ratings yet

- A Presentation On Semiconductor Memories PDFDocument112 pagesA Presentation On Semiconductor Memories PDFSarthak RoyNo ratings yet

- Lecture2 ThirdmicroprocessorcDocument22 pagesLecture2 Thirdmicroprocessorcxkurt358792100% (2)

- Embedded Systems Chapter 13: ADC, DAC and Sensor InterfacingDocument33 pagesEmbedded Systems Chapter 13: ADC, DAC and Sensor Interfacingsumbal_iqbal100% (1)

- Answers 3Document5 pagesAnswers 3Carl SigaNo ratings yet

- Ec7101-Telecommunication Switching Circuits & NetworksDocument8 pagesEc7101-Telecommunication Switching Circuits & NetworksAbhijeet BishtNo ratings yet

- Microcontroller and Embedded SystemsDocument2 pagesMicrocontroller and Embedded SystemsIndranilNo ratings yet

- Chapter Five PDFDocument34 pagesChapter Five PDFtesfuNo ratings yet

- Rohini College of Engineering & TechnologyDocument5 pagesRohini College of Engineering & TechnologyDarshan BysaniNo ratings yet

- Microprocessor Microcontroller EXAM 2021 MGDocument11 pagesMicroprocessor Microcontroller EXAM 2021 MGRene EBUNLE AKUPANNo ratings yet

- Interfacing Devices Memory Devices and Interfacing Interfacing DevicesDocument14 pagesInterfacing Devices Memory Devices and Interfacing Interfacing DevicesShilpa ShettyNo ratings yet

- Microprocessor For Memory Mapping and Instruction Set For GATE 2018 PDFDocument79 pagesMicroprocessor For Memory Mapping and Instruction Set For GATE 2018 PDFfastest raviNo ratings yet

- Ee6301 Digital Logic CircuitsDocument19 pagesEe6301 Digital Logic CircuitsKandan DhivyaNo ratings yet

- AntennaDocument19 pagesAntennajohn2collins-6No ratings yet

- HGH VSWR - 19-01-18Document1 pageHGH VSWR - 19-01-18Sachin PalNo ratings yet

- HGH VSWR - 19-01-18Document1 pageHGH VSWR - 19-01-18Sachin PalNo ratings yet

- 7th Sem Syllabus UEMJ-1Document38 pages7th Sem Syllabus UEMJ-1Sachin PalNo ratings yet

- L20 SharmaDocument28 pagesL20 SharmaVishnu Vardhan ReddyNo ratings yet

- Main Paper EC-306Document2 pagesMain Paper EC-306Sachin PalNo ratings yet

- Gautam Buddha University Microelectronics ExamDocument2 pagesGautam Buddha University Microelectronics ExamSachin PalNo ratings yet

- AntennaDocument19 pagesAntennajohn2collins-6No ratings yet

- Main Paper EC-306Document2 pagesMain Paper EC-306Sachin PalNo ratings yet

- Main Paper - CS-572Document1 pageMain Paper - CS-572Sachin PalNo ratings yet

- Limitation of CT - NptelDocument16 pagesLimitation of CT - NptelDrSneha SharmaNo ratings yet

- Back Paper EC 306Document2 pagesBack Paper EC 306Sachin PalNo ratings yet

- Main Paper EC-306Document2 pagesMain Paper EC-306Sachin PalNo ratings yet

- Embedded Systems Exam QuestionsDocument1 pageEmbedded Systems Exam QuestionsSachin PalNo ratings yet

- CS A PDFDocument31 pagesCS A PDFSachin PalNo ratings yet

- 03 EDCBJTUnivofcalifornia PPTs Lesson 03Document117 pages03 EDCBJTUnivofcalifornia PPTs Lesson 03anishadandaNo ratings yet

- Main Paper - EC101Document3 pagesMain Paper - EC101Sachin PalNo ratings yet

- S. No. Enrolment No. NameDocument1 pageS. No. Enrolment No. NameSachin PalNo ratings yet

- Syllabus Microcontroller (NEC 022)Document1 pageSyllabus Microcontroller (NEC 022)Sachin PalNo ratings yet

- Back Paper EC 306Document2 pagesBack Paper EC 306Sachin PalNo ratings yet

- Microcontroller and Its Appl (NEC 022-Is)Document1 pageMicrocontroller and Its Appl (NEC 022-Is)Sachin PalNo ratings yet

- Microcontroller and Its Appl (NEC 022-IiS)Document1 pageMicrocontroller and Its Appl (NEC 022-IiS)Sachin PalNo ratings yet

- n-MOSFET (D) :: (I-V) Equations: Cut Off ModeDocument6 pagesn-MOSFET (D) :: (I-V) Equations: Cut Off ModeJo KontNo ratings yet

- International Journal of Electronics and Communications (AEÜ)Document6 pagesInternational Journal of Electronics and Communications (AEÜ)Sachin PalNo ratings yet

- n-MOSFET (D) :: (I-V) Equations: Cut Off ModeDocument6 pagesn-MOSFET (D) :: (I-V) Equations: Cut Off ModeJo KontNo ratings yet

- Microcontroller and Its Appl (NEC 022-Is)Document1 pageMicrocontroller and Its Appl (NEC 022-Is)Sachin PalNo ratings yet

- Microcontroller and Its Appl (NEC 022-IiS)Document1 pageMicrocontroller and Its Appl (NEC 022-IiS)Sachin PalNo ratings yet

- 1 s2.0 S0304885316303304 MainDocument10 pages1 s2.0 S0304885316303304 MainSachin PalNo ratings yet