Professional Documents

Culture Documents

BJT - Device.model - pp.9 To 17.

Uploaded by

Tom Wu0 ratings0% found this document useful (0 votes)

27 views21 pagesBJTs

Original Title

BJT.device.model.pp.9 to 17.

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentBJTs

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

27 views21 pagesBJT - Device.model - pp.9 To 17.

Uploaded by

Tom WuBJTs

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 21

4.4. Classification of Device Models 14

1 Review of Device Models

In this chapter, we review the models we will be using for BJTs and MOSFETs. We begin by character=

izing different classes of models, including:

‘+ Tinea, nonlinear, and incremental models

+ static and dynamic models

We then summarize the static models for BITs and MOSFETs, indicating how we will employ them for

‘hand analysis.

1.1 Classification of Device Models

Models for BITs and MOS devices are often classified as being either Jarge-signal ot small-signal.

These terms, while in common use, are imprecise. How large is “large”? How small is “small”? In what fol-

lows, we will define some terms that will be used to describe different classes of device models.

1.1.1. Linear, Nonlinear, and Incremental Models

‘We begin by considering a “black box” with an input x and output y, as shown in Figure 1-1. The output

is some fimetion of the input, ie. y = fix)

Figure 1-1. “black box” with one input and one outpat.

The “black box” may be a BIT, with the input being base-emitter voltage and the output being collector

current. Itmay bea very complex circuit with a large number of BITs or MOS devices. It may be an intereon-

cction of mechanical rather electrical components. Such a black box” is generally referred to as a “system”.

The relation y = flx) describes the operation of the system and thus is in some sense “models” the operation

of the system.

A system is linear if the following conditions hold:

1. If the input is scaled by a constant a, the output is a times the outpnt due to the unscaled input. That is:

flax) = aftx) Gia)

2. If the input is the sum of two components, say x, and x, the output is equal to the sum of the outputs

due to cach component individually. That is:

fay +x) = A) +f) (1b)

‘Acsystem thatis not linearis nonlinear. A nonlinear system may be linear about some point x ~ X and

y = ¥. This will be the ease ifthe two equations above are satisfied with x, x; . and x) replaced by fix),

‘flay —X). aud f(s —X), respectively, and with Y = f(D).

DRAFT 19:2 on 5 January 2004

12 1. Review of Device Models

‘A nonlinear system can be linearized about some point x

theTaylor series expansion of f(x) about this point. With Ax

» el (ax) +f

aly

Y, with ¥ = fl). Consider

ay

and keep in mind that ¥ = f(X) and that y—f(X) = y-Y = Ay

If the contribution of the quadratic and higher power terms in Ax is sufficiently small compared to that

of the first term on the tight hand side, we have the following “linearized model” of the system about the point

x=Xandy = ¥,

Ay = 4ax a3)

witere 4 is the first derivative off with respect to x evaluated atthe point x = X and y = Y, and is thus a con-

stant that depends on the values of X and F. This equation is said to represent an incremental model of the

system about the operating point x = X and y = Y. The operating point is also referred to as the quiescent

condition (or Q-point) for the system. The model is called “incremental” because it relates an increment Ay

in the output y (from Y) to an inerement Ax in the input x (from 4). Itis easily seen that Equation (1.3) repre=

sents a linear input-output relationship, with Av as the input and Ay asthe output, An example is shown in

Figure 1-2.

Figure 12, An incremental model for a nonlinear system about an operating point, The incremental model is character-

{ed by the tzngent tothe nonlinear system equation ) = f(t) atthe operating point x = andy = T-

Before we proceed further, we note thatthe discussion so far is easily extended to systems with several

inputs and several outputs. For example, we view BJTs as “systems” with two inputs and two outputs. The

‘equations describing the operation of BITS are such that the “inputs” (independent variables) are voltages and

the “outputs” (dependent variables) are curents.

Electronic devices are inherently nonlinear. A BIT is sometimes referred to as an exponential law

device, because the current in each junction is related to the exponential of the voltage across thejunction. A

MOSFET is sometimes called a square law device, because the drain current is related to the square of the

‘gate-source or drain-source voltage, To accurately describe device operation for arbitrary terminal voltages

and currents, the nonlinear device equations must be employed. These equations represent mathematical mod-

cls for particular physical systems, namely semiconductor devices, and are therefore referred to as nonlinear

‘models for the devices. In some cases, we can draw circuit models, using simpler nonlinear deviees, that sat-

isfy these same nonlinear relatiouships between terminal voltages and cwreats. The so-called nonlinear

DRAFT 13:2 0n 6 January 2008

4.4 Classification of Device Models 13

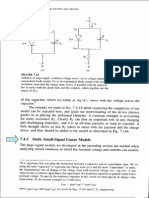

hybrid-1 model for the BIT, shown in Figure 1-10 on page 1-10, is an example of such @ nonlinear circuit

suedel (or nonlinear equivalent circuit). However, itis important to keep in mind that for nonlinear models, the

nonlinear equations (i... the mathematical model) represent the real nonlinear model; any equivalent nonline

car circuit model we can draw is just a convenience.

Clearly, it is possible to linearize the nonlinear equations describing a BIT or MOSFET about some

appropriate operating point. Following the discussion above, what results is an incremental model for the

device about the operating point. This incremental model is a linear model that relates changes from the oper=

ating-point values of the outputs to changes from the opersting-point values of the inputs. As noted above, the

{neremental model is an accurate representation of device operation for changes from the operating-point input

and output values only as long as these changes are sufficiently small. Also, because the ineremental model is

linear, it’s mathematical form is completely equivalent toa linear circuit model, which is also called the “incre-

mental model”.

‘We see immediately, then, that an incremental model is a small-signal model, and that we have at least

some idea how to go about determining how small is “small”, By the same token we would say that a nonlin

‘ear model is a large-signal model.

The term “incremental” may on occasion be applied to ceriain ciseuit properties of an incremental

model, For example, the incremental resistance seen between two nodes in a circuit is the equivalent resis-

tance seen between these nodes with all devices replaced by their incremental models atthe eireuit’s operating

point.

Finally, it is important to remember that obtaining the incremental model of a device at an operating

point requires finding the operating point itself. The operating point is a solution point of the nonlinear equa-

tions for the device as connected with other circuit components. Thus, these nonlinear equations must be

solved to find the operating point. While this can often be done for MOS devices without too much difficulty,

it is often impossible for BJTs without a computer. However, an approximate solution for the operating point

can be obtained using a piecewise linear model. This differs from the incremental model in that it is con=

stmcted so as to apply over a wide range of device voltages and currents. An example of a piecewise linear

‘model is shown below in Figure 1-5 on page 1-6.

‘As can be seen from the figure, a piecewise linear model may represent a fairly coarse approximation to

the nonlinear device characteristic. However, such models are often usefil in estimating device operating

points, and also in obtaining approximate solutions to problems in which incremental models eannot be used.

‘We will see examples of such problems later on.

1.4.2 Static and Dynamic Models

BITs and MOS devices incorporate charge storage mechanisms. In BITS, there is charge stored in the

junction depletion regions: the injected minority carriers resulting from forward biased junctions also repre-

sents stored charge. In MOSFETs, the conduetor-oxide-channel “sandwich” represents an explicit capaci-

tance; in addition, there are a variety of parasitic charge storage elements associated with junction depletion

regions (c.g., between the substrate and the source and drain contact regions), and with overlap of the gate

oxide with the source and drain contact regions. The charge stored in any one of these BJT and MOSFET ele-

ments is 2 nonlinear function of device voltages and cwreats.

Device models that do not take device charge stores into account are static models. They arc typically

‘lid for voltages and currents with frequencies up 10KFiz or so, depending on the type of device and type of

cireuit. Device models that do take device charge stores into account are dynamic models. Even dynamic

DRAFT 13:2.0n § January 2004

14 1_ Review of Device Models

‘models have upper frequency limits for which they are valid, because of approximations involved in modeling

the real physical processes that take place in semiconductor devices.

‘The incremental model that results from linearization of a static nonlinear model is a static incremental

‘model. Similarly, the incremental mode] that results from from linearization of a dynamic nonlinear model is @

dynamic incremental model. A static incremental model includes no capacitances associated with device

charge stores. A dynamic incremental model does include such capacitances. ‘These capacitances are incre-

‘mental capacitances, which result from linearization of the nonlinear charge vs. voltage relationships for the

charge stores, evaluated at the device operating point.

1.1.3 Notation

In Eqn. (1.2), we find the following categories of quantities:

1. x and y, which may represent the terminal voltages and/or eurrents of a device: x and y may vary with

time.

2. Xand ¥, which sepresent the values of x and y, respectively, at an operating point; when we consider an

operating point, we take the values and Fat the operating point to be fixed and not changing with time.

3. Ax and Ay, which represent changes of x and y from their operating point values; Ax and Ay may

vary with time,

For voltages and currents in a circuit containing electronic devices, we use a particular convention to

distinguish between these categories. We desoribe it here for voltage, but it applies identically for current.

+ Lower-case 1; upperease subscript: This represents a “total” voltage, ic. in the first category listed

above. This voltage is generally a funtion of time.

+ Upper-ease I upper-case subseript: This represents the value of voltage at an operating point

+ Lower-case v, lower-case subscript: This represents the incremental voltage, generally a function of

time, about some operating point.

‘The use of this notation, as well as the application of the modeling concepts outlined above, are indi«

cated in the example that follows.

1.1.4 An Example — The pn Diode

Figure 1-3 shows the cireuit symbol for a pr-diode. In this example we consider static nonlinear, inere-

‘mental, and piecewise linear models for the diode. The voltage across the diode (from p-side to m-side) is

shown in the figure as vp, and the current through the diode in the direction of this voltage is shown as ip,

Following the convention defined above, vp and iz are “total” quantities; that is, they are quantities associ-

ated with the nonlinear diode model:

vo/kT

ip = Ile -1) ay

Figuel3._Aprdiode,

DRAFT 13:2.0n 6 January 2004

1.1 Classification of Device Models 15

In Eqn. (1.4), Ie is the scale current (sometimes called the reverse saturation current) of the diode, q is

the magnitude of charge on an electron (1,602 x 10” "C)), kis Boltzmann’s constant (1.381 x 10 'J/°K), T

is absolute temperature (in °K), and 9, is the so-called ideality factor of the diode (dependent on the junction

material: n= 2 forsilicon). The quantity (ET/q) is sometimes called the volt equivalent of temperature, and

is approximately 2SmV at room temperature (295°K).

‘We can consider an operating point at which the diode voltage is Vp, and the diode current is Jy. with

these quantities of course being related by Eqa. (1.4). Such an operating point could be established by by cone

necting a DC voltage source equal to V> or a DC current souree equal to Ip across the device.

‘We construct an incremental model at this operating point by differentiating Eqn. (1.4):

tin a (00

= L162"

oe ) as)

To evaluate the derivative at the operating point as in Eqn. (1.2), we set vp = Vy in Eqn. (1.5). Com

paring the result with Jp, we find

> Hilo+t) a6

By definition, the incremental diode current i, and the incremental diode voltage vg. at the specified

operating point (Vy. Ip), satisfy

Votvy ip =Iptiy

‘Now, following Eqns. (1.2) and (1.3), we can relate the incremental diode current Zp to the incremental

diode voltage vp at the specified operating point, as follows:

iy= 8%, with 83> Teed) an

Itis clear from this relation that the incremental model represents the diode as a linear resistor with resis-

tance 1/¢,, for sufficiently small changes from te operating point. This is shown in Figure 1-4.

Figure 14, Incremental model of apr-diode. The incremental conductance gis the slope ofthe tangent line tthe operat-

ing point.

DRAFT 13:2 on 5 January 2004

16 1_ Review of Device Models

Finally, note with respect to Eqa (1.7) that this model is most often employed when the diode is forward

biased, so that Jy » J, for example as shown in Figure 1-4. Thus we generally negleet J, when computing

Sa:

‘We can also construct a piecewise linear model of the diode, as shown in Figure 1-5. We do so based on

ihe observation that the diode has two regions of operation: an off region, in which the diode current remains

approximately zero; and an on region, in which the diode current increases exponentially with the diode volt-

age. That there is an apparent boundary between these two regions can be seen in the plot ofthe diode charac-

teristic in Figure 1-4 (repeated on the left in Figure 1-5(a)). ‘This voltage is called the cut-in voltage, usually

denoted by V,, and is equal to about 0.5V for a silicon diode at room temperature. In the piecewise linear

model, as shown on the left in Figure 1-5(a), the diode characteristic is approximated in the on region by a

straight line with steep slope and in the off region by a straight line whose slope is approximately zero. The

model is constructed so that the lines intersect at vp = Voy and ip = 0, with Voy perhaps 100mvV above

V,. The parameters of the model, namely gy, andthe resistances Ry and R, , can be chosen so thatthe piece-

whe linear approximation isa reasonably good fit to the nonlinear diode characteristic. However, since the

approximation is at best rather coarse, it is often sufficient to take Ry = 0 and R,—> 0, with Voy, equal to

about 0.6V for a silicon diode at room temperature,

From an equivalent cireuit perspective, each of the two line segments in the piecewise linear approxima-

tion in Figure 1-5(a) comesponds to a linear circuit model consisting of @ resistor and 2 voltage souree. The cit-

cuit model for the on region is shown in Figure 1-5(b) while that for the off region is shown in Figure 1-5(c).

Note that both circuit models are valid atthe intersection point of the two line segments, ic. at the boundary

‘between the on and off regions. Note also that this boundary, which is slightly fuzzy in the nonlinear model

(ic. “in the real world”), is defined very precisely in the piecewise linear approximation as follows:

20 oy and fy 20; diode on

(1

ypSVoy and ipS0; diode off 0

Figure LS. Piecewise-limear model of ap-diode. The approximation is shown graphically im (a). The eiruit mode fo the

‘approximation fa the on xegion is showwa in (0). ad the model forthe approtimation ia the of region fs shown ia

©.

DRAFT 13:2 on 5 January 2004

1.1 Classification of Device Models 17

+

a. >

Rak

v,=svtt

Figure 1.6. A simple diode circuit

We cau illustrate some of the concepts discussed above using the citcuit shown in Figure 1-6. The diod=

in the figure has J, = 107A and 1 = 1. A reasonable piecewise linear approximation is found to have

O6V, Rp= 100, and R,>0. The only excitation in the circuit is the DC voltage source

SV. We ate to find the resulting DC diode voltage Vy and current Jp, and the incremental model for

the diode at this operating point.

We can write a simple loop equation for the circnit and then substitute in the nonlinear volt-ampere sela-

tionship for the diode from Eqn. (1.4). We would obtain

a/R

V5 = Vp tIRse

1)

[etums out that this equation cannot be solved in closed form, We can use a computer to solve it iteratively, or

to solve the circuit directly using SPICE (or the equivalent). We ean, however, obtain an approximate solution

bby hand analysis using the piecewise linear model for the diode. ‘The only problem now is that there are two

possible circuits in Figure 1-5; which is the right one to use here?

The technique we employ proceeds as follows:

1, Assume the diode is operating in a particular region.

2. Solve the circuit using the corresponding model for the diode.

3. Verify that the solution is consistent with all the operating conditions for the diode in the assumed re-

gion, ie. as given in Eqn. (1.8).

To see how this works, let's assume that the diode in Figure 1-6 is off. The circuit is redrawn in

Figure 1-7(a) with the diode replaced by the off model from Figure 1-5(¢). Solving the cirouit, we quieldy sez

that, because R, 22, Jp = 0 and Vp = Vz = SV. Clearly, Vp > Voy, and the condition in Equ. (1.8) for

the diode to be off is violated. Consequently, our assumption that the diode is off must be wrong. So, let’s

assume instead that the diode is on. Writing a loop equation, we find

Figure 17. Use of the piecevisetinear diode model. . In (a), the diode i assumed tobe off; in (0), the diode is assumed to be

‘oa. The oxgizal cucuitis ia Figure 1-6

DRAFT 19:2 on § January 2004

18 1_ Review of Device Models

Figure 18.__A simple diode circuit with an ac voltage source.

¥ 5 Yo:

b=

ID

Rt Ry

436mA: Vp = VoytIp

This solution is consistent with the condition in Eqn. (1.8) for the diode to be on. Thus the sofution is correct

and the diode is indeed on.

The solution found using the nonlinear model (for example, using SPICE) is fy = 4.33mA and

Vp = 670mV. The solution can also be obtained graphically, using techniques to be described in the next

chapter.

‘The incremental model for the diode is a conductance g as in Eqn. (1.7). Using I) = 4.33mA in this

cquation, we find g, = 0.173A/V: the corresponding resistance is rg = 1/gy = 5.770

Consider now the addition of an ac voltage source fo the cireuit of Figure 1-6, as shown in Figure 1-8.

‘We will assume that the magnitude of the ac source is sufficiently small for the incremental model to be valid

in finding the circuit’s response to this source. The linearization process summarized in Eqns. (1.2) and (1.3)

implies that the circuit in Figure 1-8 can be represented in two different ways:

1. as acircuit with only constant excitations, whose solution represents what we have called the operating

point (or quiescent conditions) and is found using the nonlinear model or the piecewise linear model for

the device;

2. asa circuit with only “small” incremental cxeitations, whose solution is found with the device replaced

by its incremental model

The total response of the circuit to all excitations is the sum (ic. the superposition) of the responses.

found using these two representations. Representation (1) of the cigcuit in Figure 1-8 is in fact the circuit

shown in Figure 1-6 that we have already solved. Representation (2) of the circuit is shown in Figure 1-9.

‘With te incremental conductance of the diode given by Eqn. (1.7), we ean easily solve this cireuit:

Figure 1.9. Theineremental representation of a simple diode circuit. The DC source /, does not appear in this circuit

‘because its incremental value is zero; a ze10-valued voltage soute i a short ctchit.

DRAFT 19:2 on S January 2004

1.2 Bipolar Transistor Models 19

1

“TE Rsg,

Continuing the example above, let's take v, to bea sinusoid with a frequency of Ikfiz and an amplitude

of S00mY; ie. v,(r) = 0.Ssin2a10°rV. Substituting the values from the example above:

yy(t) = 0.576sin2n10°r mV

volt) = Vy +v,{t) = 670mV+0.576sin2x10°r mV

1.2 Bipolar Transistor Models

In this section, we summarize the models for bipolar transistors as they will be used in this course. We

focus here on static models; dynamic models will be dealt with in a later chapter.

1.2.1 Nonlinear Model

We use the so-called nonlinear hybrid-x model. For npn BITs, the model equations are:

Qgp/AT avg c/ KT

~e

igg = Ife

os eet fact (9)

igg = BT 1); ge = SE -1)

Be Ba

Fo = Toga Igg ig = Ipg* inc

cal T

em )

Tg abyg/tT Ig abce/#T

Is oes Is ce

igg — Sle “Ys igo = Se -1) to

Br Be

ios icctiscs i= -ise tino)

For both npn and pnp devices, we also have the following node and loop equations:

vee = Ysz-"se aay

igtig*

Corresponding nonlinear circuit models are shown in Figure 1-10. The circuit models in the figure satisfy the

equations above, if we take the diode shown between base and emitter to have seale enrrent equal to /s/Br

and that shown between base and collector to have scale current equal to Je/By. As noted earlier, the eixcuit

‘model is artificial; itis the mathematical model, derived from the physies ofthe device, that is fundamental.

Referring to the model equations above, the quantity J is the scale current of the BIT. A findomental

‘property of this parameter is that it is proportional to the area of the base-emitter junction. For Bp and By we

find

DRAFT 13:2 on 6 January 2004

440 1 Review of Device Models

®

z

-_(2) shows the apn mode: (b) shows the pnp model.

2)

Additionally,

Pao a3)

with

ap-—| a4)

c|

vc“ 0 hep=0

‘The model outlined in this section is a form of the so-called Ebers-Moll model for the BIT. It is usually

referred to as the Gummel-Poon model.

1 For the nonlinear model as outlined here, the differences between the Ebers Moll and Gummel-Pooa models are ia the underlying

‘ommolation of the model and ia how certain second-order effects age taken into account.

DRAFT 19:2 on § January 2006

1.2 _Bipolar Transistor Models 144

1.2.2 Regions of Operation

For a BIT, each of the two junctions may be either forward or reverse biased. This gives rise to four

regions of operation, as indicated in Table 1-1. In the table, “BEJ” refers to the base-emitter junction, while

“BCI” refers to the base-collector junction.

Table 1-1 BIT Regions of Operation

Region BEJbias | BCJ bias

cutott Tovorso Tovorse,

forward active forward reverse

reverse active reverse forward

“saturation ——SSSS*|S forward | forward

Recall that a junction is considered to be forward biased if the measured voltage across it (from the

prside to the neside) is greater than its eut-in voltage V,; it is considered to be reverse biased if this voltage is

less than or equal to zero. In the region between 0 and ,, the junction is essentially non-conducting, but the

‘very small current that does flow is a forward current. In our work here we will take the boundary between for-

ward and reverse bias to be at V,. Fora silicon integrated BIT at room temperature, V, is about 0.5V for the

‘base-emitter junction and about 0.4V for the base-collector junction.

1.2.3 Simplified Nonlinear Model

‘Simplification of the nonlinear model is possible in certain regions of operation.

12.3.1 Cutoff

In the cutoff region, both junctions are reverse biased. Since the current through a reverse biased

‘pn-junetion is essentially zeto, itis reasonable to use

(15)

in the cutoff region.

1.2.3.2. Forward Active

In the forward active region, te base-collector junction is severse biased.

“We consider frst the special case vac = 0. Substituting this condition into the model equations (1.9)

and (1.10), we find that ie. = 0 and

ovne/T aer/tT

ig = Ble — tyson (pn)

Wpg/bT Wp5/AT

—Dese (pnp) (116)

to

p= it

5” Br

DRAFT 13:2.0n 6 January 2004

1412 1_ Review of Device Models

In the more general ease, with non-zero reverse voltage on the base-collector junction, we take the expo-

nentials in vg in Eqn. (1.9) and those in veg in Eqn. (1.10) to be approximately zero. Following through

with the algebra, we would find that Eqns. (1.16) remain good approximations.

The forward active region is often referred to simply as the active region.

1.2.3.3 Reverse Active

The reverse active region is in some sense the complement of the forward active region. We could fol-

low the reasoning outlined above to construct approximations for the reverse active region that correspond to

Eqns. (1.16).

1.2.3.4 Saturation

In saturation, both junctions are condueting. Since none of the exponential terms in Eqns. (1.9)

and (1.10) can be neglected, a simplified set of nonlinear equations cannot be constructed. We can, however,

obtain from the model equations a fundamental condition that distinguishes operation in saturation from oper-

ation in the forward active region, namely

old am

Be

1.2.3.5 AFinal Note

‘With the simplified model, we actually have a different model for each region of operation. We're thns

confronted with the need to verify that the solution obtained using a particular model is consistent with opera-

tion in the corresponding region, We will see this again for the piecewise linear model in Section 1.2.6. The

criteria for verifying solution consistency are the same for both the simplified nonlinear model and the piece-

‘wise inear model; they are given in Section Seetion 1.2.6 below.

1.2.4 Output Characteristics

Figure 1-11 shows common-emitter output characteristics for npn and pnp BITS, based on the nonlinear

‘model as outlined above. Note that in the active region, the collector current is shown independent of Vee for

constant base current. This is consistent with Eqns. (1.16).

@ ©

5 : 5

fp E BH 2

~ lh A

vee be Po ree

12. 3. 4S Toe

Figure 1-11. BJT common-emitter output characteristics (2) npn: (b) pnp. Operation i the reverse active region 15 not

showa, The dotted lies mask the Loundary between the forwasd-setve and satastion regions according (0

Eqn. (1.17).

DRAFT 19:2 on 5 January 2004

1.2__Bipolar Transistor Models 4.43

1.2.5 Second-Order Effects

1s implicitly assumed in the equations above that the device parameters (Js, Bz, Bz) are constant for

any given device, This isin fact not the case.

1.2.5.1 Variation of beta with current

‘The value of By (equal to the ratio i¢/ig at Vgc = 0) varies with J, the value of ig at which it is

measured. The behavior is depicted in Figure 1-12. At low values of Jp. Br is reduced because of recombi=

‘nation in the base-emitter depletion region. This is the effect that gives rise to the “ideality factor” in the

diode equation (1.4). Because this effect is handled in the BJT model through variation of Piz, there is no

need to introduce 7 into the BIT model. Finally, at very high currents, By is reduced because of high-level

injection and so-called “base push-out” effects. In this course, the variation of i; with collector current will

bbe ignored

The value of Bp (equal tothe ratio ip/tp at Ve

sured, Because Bp is generally small to begin with,

) varies with Ip, the value of iz at which itis mea-

variation is not usually of interest.

1.2.5.2 Base-Width Modulation (“Early effect”)

In the forward active region, the width of the base-collector junction depletion region varies with the

severse voltage applied to the junction. This in turn causes the width of the base itself to vary. Since I, and

Bp depend on base width, these parameters become functions of base-colleetor voltage. The functional rela-

tionship is characterized by an additional parameter, the so-called Early voltage V,. For base-collector volt-

age Vac:

Is= tf +

where Iso and Bro are the values of I, and Bp, respectively, at Vgc = 0. By convention, V’, is positive for

both npn and pnp devices

‘ac|

v; V;

es) be = Br +|42

4

) ais)

150200

80.

cH cea

oe 0 OOF 04 a8 08 110

Figure 1-12 Variation of forward beta with collector current In ({), loz/- and logl, 2e plotted vs. Vgg_ The vertical

istance between the curves in (b) indicated by the arows, is log: atthe particular pg. Peak forward beta for

this device is 200.

DRAFT 13:2 on § January 2004

4-44 1. Review of Device Models

®

0

increasing fy

Figure 1-13. Common-emitter output characteristics of an npn BIT taking base-width modulation into account. The

characesstes shown i (2), when extended linearly backwards fiom Vy. = 0, will all tend to intessect the hosi-

‘zontal asis at about Vgg = —T/, 28 shown in (0),

Eqn. (1.18) indicates that both I, and B- increase with increasing reverse voltage on the base-collector

jnetion. The major consequence of this behavior can be seen by considering Eqns. (1.16) in the light of

Eqns. (1.18), namely that in the active-region collector current increases with |Vzc| (and thus with ea ) for

constant base current or base-emitter voltage. This is shown in Figure 1-13. Comparison of this figure with

Figure 1-11 indicates that base-width modulation results in the BJT’s active-region output resistance being

finite.

In this course, we will generally consider base-width modulation only with respect to the output condne-

tance of the device, as part of the device’s incremental model (see Section 1.2.7 below).

1.2.5.3 Ohmic Resistances

There is an chmie resistance between the contact to each of the three regions in a BIT (emitter, base,

collector) and the place in the region where the “action” takes place (as modeled inthe equations given above).

These are denoted by ry... and r, for base, emitter, and collector, respectively.

In this course, we will take into account only the base resistanee 7, and then only as part of the BIT

incremental model (see Section 1.2.7 below).

1.2.5.4 Temperature Effects

‘There are several temperature dependencies in the BIT model. These include:

+ [y increases with temperature. As a ule of thumb, fora silicon device I; approximately doubles for ev-

ery 5°C increase in temperature.

+ The gz required to maintain the collector eurrent at a specific constant value decreases by about mV

to 2.5m per degree increase in temperature. The cutin voltage V,, for a pn-junction also displays this

behavior.

DRAFT 19:2 on 5 January 2004

1.2 Bipolar Transistor Models 115

+ Br increases with temperature. A typical temperature coefficient for By for an integrated silicon BIT is

about +7000 parts per million per degree C.

1.2.5.5 Processing Tolerances

BIT device parameters such as J; and By are strongly dependent on the device fabrication processes.

Process variations lead to relatively large tolerances in the absolute values of these parameters. For example,

values of Bp can range from one-half to twice the nominal value across a population of supposedly identica!

devices, fabricated on different wafers. However, marching of device parameters such as J, and By between

adjacent or nearby devices on a die is possible within very tight tolerances, perhaps a few petoent. We will see

ccxamples of many circuits that take advantage of this matching.

1.2.6 Piecewise Linear Model

It is often impossible to use even the simplified nonlinear model of Section 1.2.3 without recourse to a

computer. We do, however, have the following coarse but useful piecewise linear model, based on the nonlin-

cear model and the fact that the forward voltage on a pr-junction remains approximately constant.

There is a different model for each region of operation. Criteria for verifying solution consistency are

given along with the models.

1.2.6.1 Cutoff

As in the simplified nonlinear model:

ig = ip =ip-0 aig)

To verify operation in the cutoff region, we must have both junctions reverse biased.

1.2.6.2 Forward Active

i

Yaz ~ Vasheice® ta = Be (120)

For silicon at room temperature,

(Vaz) active = 9-5V (npn); OP sz)active = ~O-OV (pnp) 21

To verify operation in the forward active region, we mnst have forward base current (i >0 for mpm;

ig <0 for pnp). and the base-collector junction reverse biased,

1.2.6.3 Saturation

Because both junetions are forward biased in saturation, thebase-emitter junction voltage is slightly

higher in magnitude than in the active region. We have:

var Vath? Yor = eel a2)

For silicon at room temperature,

DRAFT 13:2 0n 5 January 2004

1-16 1_ Review of Device Models.

(Vez) = 0-7V (apn): (V5z),, = -0-7V (pnp)

(1.23)

Cezaye ~ 92N (0p0); cpg = -02V (mp)

To verify operation in the saturation region, we must have forward base current (i5>0 for npn; ip <0

for pnp), and the inequality in Eqn (1.17) satisfied.

1.2.6.4 Reverse Active

‘A model analogous to that for the forward active region in Section 1.2.6.2 can be constructed for the

reverse active region.

1.2.6.5 Boundary Conditions

Boundaries between regions are taken 2s follows:

+ Between cutoff and forward active:

ig = tp = ig = 0

a

Vgp =F, (opa): — vpy = ¥, (oa)

+ Between forward active and saturation:

vag = Vaz ese [rea = [Yee ea] SOV: is (25)

where the polarity of v¢g is positive for npn and negative for pnp.

1.2.6.6 AFinal Note

Its important to keep in mind that the junction voltages in the piecewise linear model represent simple

approximations useful for hand calculations. The 100m differences between Vgz in forward active and satu-

ration and between cz in saturation and at the boundary of forward active may appear insignificant, but they

can be sometimes critical in establishing the limits of a design. Computer simulation is generally required to

obtain precise answers.

1.2.7 Incremental Model

The BIT incremental model is derived by applying the power series expansion as in Eqn. (1.2) to the

nonlinear hybrid-r model in Eqns. (1.9) and (1.10), taking into account the appropriate second-order effects

mentioned in Section 1.2.5. The resulting incremental hybrider static model is shown in Figure 1-14. The

values of the circuit elements in the incremental model depend on device parameters and the operating point as

follows:

Figure 1-14, _ Static incremental hybrid-x model for a BYT. The models for np and pnp devices ae identical.

DRAFT 13:2 0n 6 January 2004

1.3 MOS Transistor Models 1417

(1.26)

where

dig|

ai,

8,

a2

lop pt

Note that if By is independent of collector current, then Br = B,. We will take this to be the case throughout

this course.

In terms of the resistances shown in the model in Figure 1-14, we have r, = 1/g, andr, = 1/8,

Finally, r; is a device parameter wiose value must be specified independently.

1.3 MOS Transistor Models

In this section, we summarize the models for MOSFETS as they will be used in this course. As with the

BITs, we focus here on static models; dynamic models will be dealt with in a later chapter. Circuit symbols

for MOS transistors are shown in Figure 1-15.

All models used for MOSFETs have different forms in the different regions of operation. Therefore, we

first review the characteristics of these regions as well as MOS device types

1.3.1 Enhancement and Depletion Mode Devices

‘An enhancement mode MOSFET is a device in which there is no condueting path between the souree

and drain contacts with the gate at zero bias (ves = 0, assuming the source is connected to the substrate).

Once vgs exceeds the rhreshold voltage Vz. an inversion layer is created under the gate oxide that acts as a

conducting channel between the source and drain electrodes. For an n-channel (NMOS) device, V,> 0, and

the inversion layer exists when the voltage between gate and channel is more positive then 7p. Fora p-chan-

nel (PMOS) device, V-< 0. and the inversion layer exists when the voltage between gate and channel is more

negative than V;

‘A depletion mode MOSFET is a device in which there is a conducting path between the source and drain

contacts with the gate at zero bias. This channel can be made to conduct more heavily by forward biasing the

gate (positive gate-to-channel voltage for n-channel, negative gate-to-channel voltage for p-channel). The

channel can be depleted by reverse biasing the gate. If the reverse gate bias “exceeds” the threshold voltage

Vy (gate-to-channel voltage more negative than V;<0 for n-channel, or more positive than 7;>0 for

‘p-channel), then the channel is “pinched off”, with its conduetivity reduced to zero.

ols

Figure 1.15. Circuit syinbols for MOS transistors. (2) NMOS enhancement mode; (b) PMOS enancement mode:

(NMOS depletion mode, (d) PMOS depletion made.

DRAFT 19:2 0n 6 January 2004

118 1_ Review of Device Models.

Referring to Figure I-15, the gate-to-source voltage vgs is the voltage from the gate to the source-end

of the channel, while the gate-to-drain voltage vg is the voltage from the gate to the drain-end of the channel.

In addition, we note the loop equation

Yps = "G+ Yes = yg +s

and the fact thatthe gate current 7 is always zero for static operation, so that is ~ ~Zp

1.3.2. Regions of Operation

The operating region for a MOS transistor is determined by how the voltage at each end of the channel

compares with the threshold voltage

Tn cutoff,

ves¥r — Yen>Vz — (PMOS)

In the ohmic region, sometimes referred to as “non-soturation”,

ves>Vr — Yep>Vp (NMOS) ax»

vesVp — (PMOS)

The boundary between cutoff and saturation is taken to be vgs ~ Vp, with vgn satisfying the condi-

tions of Eqns. (1.28) and (1.30),

The boundary between saturation and the obmic region is taken to be Yep = Vp. with vgs satisfying

the conditions of Eqns. (1.29) and (1.30).

Operation of 2 MOS transistor in saturation is analogous to operation of a BIT in the active region.

Operation of 2 BIT in saturation is anzlogous to operation of 2 MOS transistor in the chmie region (“non-satu-

ration”). This confusion of terminology is unfortunate but unavoidable.

1.3.3. Nonlinear Model

In cutoff,

ip =0 a3n

In the ohmic region,

a.32)

res

DRAFT 13:2 0n 6 January 2004

120 1_ Review of Device Models

@

4

E pa 1 ps

on

Figure 1-17. Common-source output characteristics of an NMOS transistor taking channel-length modulation into

account. The characteristics shovin i (@), when extended linearly backwatd fom Von = Vp. will all tend fo

intersect the horizontal axis at about vj = -1/2. as shown in ().

1.3.5.1 Gate Overlap

‘When fabrication of an MOS transistor is complete, the semiconductor regions whose function is to

contact the source and drain ends of the channel wind up extending very slightly underneath the gate oxide,

As aresult, the gate slightly “overlaps” the source and drain. One consequence is that the channel dimensions

(width and length) as fabricated are slightly reduced from their so-called “drawn” values. A more important

consequence is that an overlap capacitance is created between gate and drain; this will be discussed when we

consider dynamic MOSFET models.

1.3.5.2 Channel-Length Modulation

When a MOS transistor just becomes saturated (vey = Vp), the channel is depleted just at the drain

end. As the device becomes more heavily saturated (€.g. Vgp increasing beyond V; for an NMOS transistor),

the depletion region extends inereasingly farther back from the drain end towards the source end. This in tur

causes the actual length of the channel to be redueed. An approximate model of this phenomenon, called

channel-length modulation, is constructed by taking

Le

L.

at 35

od

where i the operating length of the channel to be used in Eqn. (1.33), La is the effective fabricated channel

length taking overlap into account, and A is a device parameter with units of V".

A comparison ofthis equation with those used to model base-width modulation forthe BIT (see Section

1.2.5.2) will show a strong similarity between the Early voltage 7, ofa BIT and 2", Indeed, the impact of

channel-length modulation on the operation of a MOS transistor is analogous to that of base-width modulation

on the operation of a BJT. Using Eqn. (1.38) in Eqn. (1.33), we find that the drain current in saturation

increases with |p| for constant gate-to-source voltage. This is shown in Figure 1-17. Comparison of this

figure with Figure 1-16 indicates that channel-length modulation results in the MOSFET’s saturation output

resistance being finite.

DRAFT 19:2 on § January 2004

1.3 MOS Transistor Models 41.21

In this course, we will generally consider channel-length modulation only with respect to the output con-

ductance of the device, as part of the device’s incremental model (sce Section :hdtef refid-mosim. below).

1.3.5.3, Body Effect

The nonlinear model equations in Section 1.3.3 show the operation of the device to be controlled to a

large extent by the gate-to-source voltage. In fact, more fundamental than Vg is the voltage between the ante

and the substrate (or bod), vgg. Ifthe source and the substrate are shorted together, then vgs ~ Vgp and the

‘model we have above is valid as is. Otherwise, the hady effect causes the threshold voltage V'; to depend on

the difference between these two voltages, ie. on the voltage vgs between the body and the source. The

‘threshold voltage V7 increases as v5 becomes more negative (for n-channel) or more positive (For p-chan-

nel).

In this course, we will consider the body effect only in terms of its impact on the MOSFET incremental

‘model, and then only briefly.

1.3.5.4 Short-Channel Effects

‘The analysis leading to the MOS model equations in Section 1.3.3 are based on the approximation that

‘the channel is “very long”. In currently available submicron MOS technologies (in which the drawn channel

Tength for the smallest MOS transistor is less than 1 micron), this approximation is not completely valid, and

several so-called “short-channel effects” must be taken into account. These effets are beyond the scope of

this conrse.

1.3.5.5 Temperature Effects

‘Temperature dependencies in the MOSFET model include:

+ The parameter # decreases with temperature, because of the corresponding decrease in effective mabil-

ity in the channel. This parameter is approximately proportional to I~” , where the value of m is be-

‘tween 1.5 and 2.0.

+ The threshold voltage V7 decreases almost linearly with temperature, ata rate between 0.SmV and 4mV

per degree depending on process parameters.

1.3.5.6 Processing Tolerances

MOS device parameters are strongly dependent of device fabrication processes. However, asin bipolar

technologies, excellent matching of parameter values and geometries (J and L) is possible for adjacent or

nearby devices.

1.3.5.7 Weak Inversion

The model summarized above assumes that there is a well-defined boundary between the range of vgs

for which no channel exists (no drain current possible) and the range of vg for which the device is in strong

inversion and Eqns. (1.32) and (1.33) hold. This well-defined boundary is the threshold voltage Fy.

In fact, there is an intermediate region in which the the device is in so-called weak inversion, and in

which a different nonlinear model must be used to characterize the relationship between drain current and ter~

minal voltages. We will not deal with operation in weak inversion in this course.

DRAFT 13:2 on 5 January 2004

1-22 4. Review of Device Models

‘gure 1-18. Static incremental model for'a MOS transistor. The models for n-channel and p-channel,enbiancement mode

‘and depletion mode, areal identical

1.3.6 Incremental Model

‘The MOSFET incremental model is derived by applying the power series expansion as in Eqn. (1.2) to

the nonlinear saturation-region model in Eqn. (1.33), taking into account tie appropriate second-order effects

mentioned in Seetion 1.3.5. The resulting incremental static model is shown in Figure 1-18.

The values ofthe cirouit elements in the incremental model depend on device parameters and the operat-

ing point as follows:

Kl

B= Tes“ Ya] Be

Io] Ems = "By 36)

The conductance g,, is the result of channel-length modulation; ¢g,,, results from the body effect. In

Eqn. (1.36), 11 isa body-effect parameter? defined by

Typically, the value of n lies between 0.03 and 0.1.

In terms of resistances shown in the model in Figure 1-18 and the quantities in Eqn. (1.36), we have

1g,

1.4 A Final Note

We will see examples of the use of nonlinear and incremental models for BJTs and MOS transistors

shortly.

2. The use here of the same symbol used fr the “ideality factor” ofa pride is unfortunate but customary.

DRAFT 13:2.0n 5 January 2004

You might also like

- ReadmerDocument79 pagesReadmersatyajtiNo ratings yet

- BJT - Device.model - pp.9 To 17.Document21 pagesBJT - Device.model - pp.9 To 17.Tom WuNo ratings yet

- Diode Background NotesDocument6 pagesDiode Background NotesTom WuNo ratings yet

- BJT - Device.model - pp.9 To 17.Document21 pagesBJT - Device.model - pp.9 To 17.Tom WuNo ratings yet

- Diode Small Signal ModelDocument5 pagesDiode Small Signal ModelTom WuNo ratings yet

- Solutions 5Document23 pagesSolutions 5Tom WuNo ratings yet

- BJT Background NotesDocument15 pagesBJT Background NotesTom WuNo ratings yet

- CD4011BCDocument9 pagesCD4011BCTom WuNo ratings yet

- Children of The Night The Lords of RavenloftDocument213 pagesChildren of The Night The Lords of RavenloftTom Wu100% (15)

- 1Document2 pages1Tom WuNo ratings yet

- ArduinoDocument13 pagesArduinoCabdiraxmaanmaxamed CabdiraxmaanmaxameddanNo ratings yet

- Even Though The Quality of This Document Is Not Very High, It Will Be AcceptedDocument1 pageEven Though The Quality of This Document Is Not Very High, It Will Be AcceptedTom WuNo ratings yet

- Mccloud, Understanding Comics PDFDocument30 pagesMccloud, Understanding Comics PDFTom WuNo ratings yet

- IV CharacteristicsDocument3 pagesIV CharacteristicsTom WuNo ratings yet

- Periodic TableDocument1 pagePeriodic TableTom WuNo ratings yet

- Curve FitDocument667 pagesCurve FitYuvarekha Senthilkumar100% (1)

- IV CharacteristicsDocument3 pagesIV CharacteristicsTom WuNo ratings yet

- Lecture 23jan15Document30 pagesLecture 23jan15Tom WuNo ratings yet

- DummyDocument1 pageDummyTom WuNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)