Professional Documents

Culture Documents

2k6 Ec 406 Digital Electronics

Uploaded by

Joseph JohnOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2k6 Ec 406 Digital Electronics

Uploaded by

Joseph JohnCopyright:

Available Formats

2K6 EC 406 : DIGITAL ELECTRONICS

3 hours lecture and 1 hour tutorial per week

Module I (12 hours)

Basic digital circuits - Review of number systems and Boolean algebra - Simplification of functions using

Karnaugh map and Quine McCluskey methods - Boolean function implementation - Code converters Encoders and decoders - Multiplexers and demultiplexers - ROMs - Combinational logic design using

decoders - Multiplexers and ROMs

Module II (12 hours)

Hazards in combination circuits static and dynamic.

Arithmetic circuits - Half and full adders and subtractors - Carry look ahead adders - BCD adder Multiplier and divider circuits - Sequential circuits - Latches and flip flops (RS, JK, D, T and Master Slave)

- Design and analysis of ripple counters - Shift registers - Johnson and ring counters

Module III (14 hours)

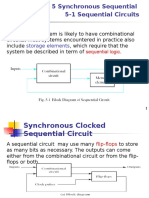

Design and analysis of sequential circuits - General model of sequential networks

Hazards in sequential networks - synchronous design method - clock skew asynchronous inputs - synchroniser failure and metastability

State diagrams Synchronous counter design - Analysis of sequential networks - Derivation of state graphs

and tables - Reduction of state table - Sequential network design

Module IV (14 hours)

Logic families - Fundamentals of RTL, IIL, DTL and ECL gates - TTL logic family - TTL transfer

characteristics - TTL input and output characteristics - Tristate logic - Shottkey and other TTL gates - MOS

gates - MOS inverter - CMOS inverter - Rise and fall time in MOS and CMOS gates - Speed power

product - Interfacing BJT and CMOS gates .

Text books

1. Roth C.H., Fundamentals of Logic Design, Jaico Pub.

2. Mano M.M., Digital Design, Prentice Hall of India

3. Taub B. & Schilling D., Digital Integrated Electronics, McGraw Hill

4. Jain R.P., Modern Digital Electronics, Tata McGraw Hill

5. John F. Wakerly, Digital Design: Principles and Practices", PHI Inc

Reference books

1. Morris R.L., Designing with TTL Integrated Circuits, McGraw Hill

2. Katz R.H., Contemporary Logic Design, Benjamin/Cummings Pub.

3. Lewin D. & Protheroe D., Design of Logic Systems, Chapman & Hall

Sessional work assessment

Assignments

2x10 = 20

2 tests

2x15 = 30

Total marks

= 50

University examination pattern

Q I - 8 short type questions of 5 marks, 2 from each module

Q II - 2 questions A and B of 15 marks from module I with choice to answer any one

Q III - 2 questions A and B of 15 marks from module II with choice to answer any one

Q IV - 2 questions A and B of 15 marks from module III with choice to answer any one

Q V - 2 questions A and B of 15 marks from module IV with choice to answer any one

You might also like

- Lecture PlanDocument1 pageLecture Planlaviniaandronicus9No ratings yet

- Ece103 Digital-logic-Design Eth 1.10 Ac29Document2 pagesEce103 Digital-logic-Design Eth 1.10 Ac29netgalaxy2010No ratings yet

- Digital Circuits and SystemsDocument3 pagesDigital Circuits and SystemsAayush JainNo ratings yet

- Syllabus For Applied ElectronicsDocument28 pagesSyllabus For Applied ElectronicsvinayakbondNo ratings yet

- Ec8392 Digital Electronics SyllabusDocument2 pagesEc8392 Digital Electronics SyllabusNandha KumarNo ratings yet

- Emb PT 08Document21 pagesEmb PT 08Anonymous IjquQOmNo ratings yet

- Cse106 Digital-Logic TH 2.00 Sc04Document1 pageCse106 Digital-Logic TH 2.00 Sc04netgalaxy2010No ratings yet

- Sampad Sir C1Document5 pagesSampad Sir C1Efaz AfnanNo ratings yet

- Syllabus CODocument7 pagesSyllabus COAshwini MateNo ratings yet

- Syllabus V Semester Engineering Mathematics - Iv 08.501 Complex Analysis and Linear Algebra (Ta)Document14 pagesSyllabus V Semester Engineering Mathematics - Iv 08.501 Complex Analysis and Linear Algebra (Ta)Jerrin Thomas PanachakelNo ratings yet

- An Ability To Understand The Basic Number Systems Used in Digital DesignDocument2 pagesAn Ability To Understand The Basic Number Systems Used in Digital DesignAnitha RaviNo ratings yet

- Digital Electronics-SyllabusDocument2 pagesDigital Electronics-Syllabussaravya RajNo ratings yet

- Computer Science 2006 Sem VI PDFDocument8 pagesComputer Science 2006 Sem VI PDFVarun Sankar SNo ratings yet

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Document2 pagesEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamNo ratings yet

- Cse1003 Digital-logic-And-Design Eth 1.1 47 Cse1003Document8 pagesCse1003 Digital-logic-And-Design Eth 1.1 47 Cse1003Shiva Charan0% (1)

- Digital Circuits and SystemsDocument2 pagesDigital Circuits and SystemsSuvdeep NayakNo ratings yet

- Computer Science 2006 Sem IVDocument8 pagesComputer Science 2006 Sem IVpp-shirazNo ratings yet

- AEM and DE SYLLABUS 3rd SEMESTERDocument1 pageAEM and DE SYLLABUS 3rd SEMESTERAR OFFICIALNo ratings yet

- MR3391 SyllabusDocument1 pageMR3391 Syllabusadmission1.gojanNo ratings yet

- Ec8392 Digital Electronics SyllabusDocument2 pagesEc8392 Digital Electronics SyllabusjeevaNo ratings yet

- CSE 1003 - DigitalLogicDesignDocument9 pagesCSE 1003 - DigitalLogicDesignTeja nNo ratings yet

- Calicut University - Viii Semester Ece Btech 2004 SyllabusDocument19 pagesCalicut University - Viii Semester Ece Btech 2004 SyllabusRakesh GopalanNo ratings yet

- Jawaharlal Nehru Technological University Anantapur B. Tech III-I Sem. (EEE) L T P C 3 1 0 3 15A04510 Digital Circuits and Systems (Moocs-I) Course OutcomesDocument2 pagesJawaharlal Nehru Technological University Anantapur B. Tech III-I Sem. (EEE) L T P C 3 1 0 3 15A04510 Digital Circuits and Systems (Moocs-I) Course Outcomesjeravi84No ratings yet

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- TNPSC Assistant System Engineer and Analyst SyllabusDocument10 pagesTNPSC Assistant System Engineer and Analyst SyllabussoundaryaNo ratings yet

- CS III and IV Sem SyllabusDocument31 pagesCS III and IV Sem Syllabusjoshituhina9No ratings yet

- VLSI DesignDocument1 pageVLSI Designडाँ सूर्यदेव चौधरीNo ratings yet

- Digital SystemsDocument675 pagesDigital SystemsvikramjhaNo ratings yet

- Digital SystemsDocument390 pagesDigital SystemsKetan PandeyNo ratings yet

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 pagesPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 pagesPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 pagesPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- GTU Digital ElectronicsDocument3 pagesGTU Digital Electronicssjbv.hardik582No ratings yet

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 pagesPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- Prerequisite:: VLSI Design (404201)Document2 pagesPrerequisite:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- RGPV Syllabus Cbgs Ec 3 Sem All SubjectsDocument8 pagesRGPV Syllabus Cbgs Ec 3 Sem All SubjectsAyushNo ratings yet

- Applied Electronics - 1st Semester SyllabusDocument21 pagesApplied Electronics - 1st Semester SyllabusSriNi VaSanNo ratings yet

- Deld SylubusDocument2 pagesDeld SylubusMary MorseNo ratings yet

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 pagesPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 pagesPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- EE204 Digital Electrncs N Logic DesignDocument3 pagesEE204 Digital Electrncs N Logic DesignsaniljayamohanNo ratings yet

- Total: 45 Periods: Objectives: The Student Should Be Made ToDocument1 pageTotal: 45 Periods: Objectives: The Student Should Be Made ToAdam WellsNo ratings yet

- Course Outcomes:: VLSI Design (404201)Document2 pagesCourse Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 pagesPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 pagesPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirNo ratings yet

- Syllabus DLDA DSLDocument4 pagesSyllabus DLDA DSLShirish RansingNo ratings yet

- Course File: ContentDocument27 pagesCourse File: ContentDinesh Sundar50% (2)

- EEE241-DLD Course OutlineDocument2 pagesEEE241-DLD Course OutlineZeeshan TahirNo ratings yet

- DSD SyllabusDocument2 pagesDSD SyllabusprasathvlsiNo ratings yet

- Jawaharlal Nehru Technological University Hyderabad M.Tech. Digital Electronics & Communication Systems Course Structure and SyllabusDocument12 pagesJawaharlal Nehru Technological University Hyderabad M.Tech. Digital Electronics & Communication Systems Course Structure and Syllabustejaswi.mNo ratings yet

- Ae IIDocument27 pagesAe IIAnbu SelvanNo ratings yet

- DPCO Syllabus (Theory Cum Practical)Document2 pagesDPCO Syllabus (Theory Cum Practical)yogeshwaran.r2022lcseNo ratings yet

- Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLFrom EverandIntroduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLNo ratings yet

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsFrom EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsNo ratings yet

- Ec352 Comprehensive Exam: Syllabus For Oral Exam Network TheoryDocument2 pagesEc352 Comprehensive Exam: Syllabus For Oral Exam Network TheoryJoseph JohnNo ratings yet

- Comm Synchronization enDocument45 pagesComm Synchronization enBeverly PamanNo ratings yet

- EC 201 Network TheoryDocument2 pagesEC 201 Network TheoryJoseph JohnNo ratings yet

- A) Differentiate Between Fan in and Fan Out: Question Bank For Series Test 2Document5 pagesA) Differentiate Between Fan in and Fan Out: Question Bank For Series Test 2Joseph JohnNo ratings yet

- Learning Material - DataCommunicationDocument139 pagesLearning Material - DataCommunicationishandpandeNo ratings yet

- Commsys 2 2012 6Document45 pagesCommsys 2 2012 6Joseph JohnNo ratings yet

- MW & Optical LabDocument1 pageMW & Optical LabJoseph JohnNo ratings yet

- s7 EC Syllabus PDFDocument23 pagess7 EC Syllabus PDFJoseph JohnNo ratings yet

- Module 3Document10 pagesModule 3Joseph JohnNo ratings yet

- Syllabus For S1 and S2 - KTUDocument61 pagesSyllabus For S1 and S2 - KTUJeas Grejoy AndrewsNo ratings yet

- Academic Audit ManualDocument16 pagesAcademic Audit ManualsajinirajithNo ratings yet

- Good On Analysis of Sequential Logic CircutDocument17 pagesGood On Analysis of Sequential Logic CircutrameshragalaNo ratings yet

- Toc MP & MCDocument3 pagesToc MP & MCJoseph JohnNo ratings yet

- Aictepayscale OrderDocument2 pagesAictepayscale OrderJoseph JohnNo ratings yet

- Programmable Dma Controller 8257Document9 pagesProgrammable Dma Controller 8257Joseph JohnNo ratings yet

- Government Engineering College Kozhikode-5: AI09 308 (P), ME09 307 (P)Document69 pagesGovernment Engineering College Kozhikode-5: AI09 308 (P), ME09 307 (P)nainesh goteNo ratings yet

- Chapter-5 Synchronous Sequential LogicDocument73 pagesChapter-5 Synchronous Sequential LogicJoseph JohnNo ratings yet

- Detection and Estimation:: Model of Digital Communication SystemDocument24 pagesDetection and Estimation:: Model of Digital Communication SystemJoseph JohnNo ratings yet

- Basic Processing Unit:: Fundamental ConceptsDocument35 pagesBasic Processing Unit:: Fundamental ConceptsJoseph JohnNo ratings yet

- Counters DesignDocument12 pagesCounters DesignSuresh Bharath100% (1)

- Sequential Circuits Analysis, State-Minimization, Assignment and Circuit ImplementationDocument33 pagesSequential Circuits Analysis, State-Minimization, Assignment and Circuit ImplementationJoseph JohnNo ratings yet

- Digital Circuits and Systems: Spring 2015 Week 1Document28 pagesDigital Circuits and Systems: Spring 2015 Week 1Akhil K RNo ratings yet

- 6 5SequentialTimingDocument13 pages6 5SequentialTimingJoseph JohnNo ratings yet

- Arithematic UnitDocument37 pagesArithematic UnitkumariNo ratings yet

- Computer Organisation Chapter - 1 Basic Structure of ComputersDocument11 pagesComputer Organisation Chapter - 1 Basic Structure of ComputersMurali DharanNo ratings yet

- Chapter - 03: Accessing I/O DevicesDocument42 pagesChapter - 03: Accessing I/O DevicesJoseph JohnNo ratings yet

- Organization of MicrocontrollerDocument5 pagesOrganization of MicrocontrolleradddataNo ratings yet

- Unit1 NRDocument8 pagesUnit1 NRRahul Abhay BhagtaniNo ratings yet

- APJ Abdul Kalam Technological University CET Campus, Thiruvananthapuram Kerala - 695016 India Academic Audit Report 2015 - 2016Document6 pagesAPJ Abdul Kalam Technological University CET Campus, Thiruvananthapuram Kerala - 695016 India Academic Audit Report 2015 - 2016Joseph JohnNo ratings yet

- Unit3 CRRDocument29 pagesUnit3 CRRadddataNo ratings yet