Professional Documents

Culture Documents

R09-Vlsi Technology and Design

Uploaded by

Amir WagdarikarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

R09-Vlsi Technology and Design

Uploaded by

Amir WagdarikarCopyright:

Available Formats

www.jntuworld.

com

R09

Code No: C0601, C5503, C7703, C6803, C5703, C7003, C4507, C3803

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

M.Tech I Semester Examinations, October/November-2011

VLSI TECHNOLOGY AND DESIGN

(COMMON TO DIGITAL SYSTEMS & COMPUTER ELECTRONICS, EMBEDDED

SYSTEMS, EMBEDDED SYSTEMS & VLSI DESIGN, VLSI & EMBEDDED SYSTEMS,

VLSI SYSTEM DESIGN, ELECTRONICS & COMMUNICATION ENGINEERING,

SYSTEMS & SIGNAL PROCESSING, DIGITAL ELECTRONICS & COMMUNICATION

SYSTEMS)

Time: 3hours

Max. Marks: 60

Answer any five questions

All questions carry equal marks

---

1.a)

b)

Derive the relevant expressions Ids versus Vds in the Non-Saturated and

Saturated regions.

Explain the pseudo-NMOS logic during the low to high transition.

[12]

D

L

2.a)

b)

Explain about various layout design and tools in VLSI design. With diagrams.

Design the layout for an n-diffusion wire connected to a p-diffusion wire. [12]

3.

Explain about 1 - clocking rules for flip-flops and 2 - clocking disciplines

for latches.

[12]

4.a)

b)

Explain how capacitive coupling lead to crosstalk.

Discuss graph model for path delay through combinational logic in the

combinational network delay.

[12]

5.a)

b)

Explain about off-chip connections related to floor planning in VLSI design.

Explain about the process sequence in the realization of CMOS Inverter. [12]

6.a)

Generate a set of sequential tests for the 01 string recognizer which tests for

all stuck at-0/1 faults, assuming you dont know the machines initial state.

Explain how the simple wiring plans in the data paths.

[12]

b)

R

O

W

U

T

N

7.a)

b)

Explain the structure of a Booth multiplier.

Design of an SRAM core cell and explain it briefly.

[12]

8.

a)

b)

Explain briefly on

Design validation and testing.

Placement and routing in floor planning.

[12]

******

www.jntuworld.com

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Pic Instruction SetDocument7 pagesPic Instruction Setdavid.mort6889No ratings yet

- Humidity & Temperature Controller Pro.Document41 pagesHumidity & Temperature Controller Pro.Amir WagdarikarNo ratings yet

- Vidya Vikas Pratishtan's Institute of Engineering & Technology Solapur DSP Unit Test IDocument1 pageVidya Vikas Pratishtan's Institute of Engineering & Technology Solapur DSP Unit Test IAmir WagdarikarNo ratings yet

- Faculty ProfileDocument1 pageFaculty ProfileAmir WagdarikarNo ratings yet

- MHRD India website overviewDocument2 pagesMHRD India website overviewAnkitSinghNo ratings yet

- EC2302Document81 pagesEC2302Kamal PandeyNo ratings yet

- R09-Vlsi Technology and DesignDocument1 pageR09-Vlsi Technology and DesignAmir WagdarikarNo ratings yet

- MatlabDocument11 pagesMatlabAmir WagdarikarNo ratings yet

- Lab9 - CRCDocument6 pagesLab9 - CRCAmir WagdarikarNo ratings yet

- The Fast Fourier TransformDocument20 pagesThe Fast Fourier TransformAmir WagdarikarNo ratings yet

- IETEJRes596709-1830821 050508Document10 pagesIETEJRes596709-1830821 050508Amir WagdarikarNo ratings yet

- Codes U18 TextDocument7 pagesCodes U18 TextAmir WagdarikarNo ratings yet

- Shapes, Materials of Tubes and Energy Absorption: 3.1 Circular TubeDocument2 pagesShapes, Materials of Tubes and Energy Absorption: 3.1 Circular TubeAmir WagdarikarNo ratings yet

- List of TYEJ Students Electronics & Telecommunication DepartmentDocument4 pagesList of TYEJ Students Electronics & Telecommunication DepartmentAmir WagdarikarNo ratings yet

- Shapes, Materials of Tubes and Energy Absorption: 3.1 Circular TubeDocument2 pagesShapes, Materials of Tubes and Energy Absorption: 3.1 Circular TubeAmir WagdarikarNo ratings yet

- Seminar Report2Document23 pagesSeminar Report2Amir WagdarikarNo ratings yet

- Automatic Dish WasherDocument13 pagesAutomatic Dish WasherAmir WagdarikarNo ratings yet

- Sep - 2010 - b5506 - Low Power Vlsi DsignDocument1 pageSep - 2010 - b5506 - Low Power Vlsi DsignvasuvlsiNo ratings yet

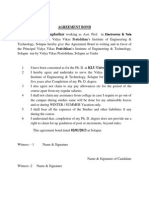

- Agreement Bond Electronics & Tele Communication, Dept. Vidya Vikas Pratishthan's Institute of Engineering &Document1 pageAgreement Bond Electronics & Tele Communication, Dept. Vidya Vikas Pratishthan's Institute of Engineering &Amir WagdarikarNo ratings yet

- Researchpaper Implementation of Possibilistic Fuzzy CMeans Clustering Algorithm in MatlabDocument9 pagesResearchpaper Implementation of Possibilistic Fuzzy CMeans Clustering Algorithm in MatlabAmir WagdarikarNo ratings yet

- Shapes, Materials of Tubes and Energy Absorption: 3.1 Circular TubeDocument2 pagesShapes, Materials of Tubes and Energy Absorption: 3.1 Circular TubeAmir WagdarikarNo ratings yet

- Datasheet of PCF8578Document46 pagesDatasheet of PCF8578Amir WagdarikarNo ratings yet

- Student performance report cardDocument2 pagesStudent performance report cardAmir WagdarikarNo ratings yet

- Presentation1 (MEMS)Document6 pagesPresentation1 (MEMS)Amir WagdarikarNo ratings yet

- #Region Using Using Using Using Using Using Using Using Using Using #Endregion Public Partial ClassDocument10 pages#Region Using Using Using Using Using Using Using Using Using Using #Endregion Public Partial ClassAmir WagdarikarNo ratings yet

- Datasheet of PCF8578Document46 pagesDatasheet of PCF8578Amir WagdarikarNo ratings yet

- 5 Arumugam Comparison Inverter29-35Document0 pages5 Arumugam Comparison Inverter29-35Amir WagdarikarNo ratings yet

- Presentation1 (MEMS)Document6 pagesPresentation1 (MEMS)Amir WagdarikarNo ratings yet

- How To BindDocument16 pagesHow To BindAmir WagdarikarNo ratings yet