Professional Documents

Culture Documents

Moree and More

Moree and More

Uploaded by

Albi AbaziOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Moree and More

Moree and More

Uploaded by

Albi AbaziCopyright:

Available Formats

www.fairchildsemi.

com

KA3525A

SMPS Controller

Features

Description

5V 1% Reference

Oscillator Sync Terminal

Internal Soft Start

Deadtime Control

Under Voltage Lockout

The KA3525A is a monolithic integrated circuit that

includes all of the control circuits necessary for a pulse width

modulating regulator. There are a voltage reference, an error

amplifier, a pulse width modulator, an oscillator, an under

voltage lockout, a soft start circuit, and the output driver in

the chip.

16-DIP

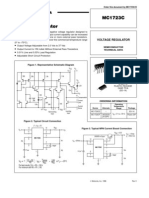

Internal Block Diagram

VC

13

VREF 16

BAND GAP

REF 5V

VCC 15

GND

12

EA(-)

EA(+)

EAOUT

C

(SOFT

START)

U.V.L.O.

11

OUTPUT A

ERR

AMP

+

_

LATCH

PWM

COMP

+

14

OUTPUT B

CT

5K

OSCILLATOR

F/F

10

SHUT DOWN

5K

Q

Q

7

DISCHARGE

3

SYNC

6

RT

4

OSC

OUTPUT

Rev. 1.0.1

2002 Fairchild Semiconductor Corporation

KA3525A

Absolute Maximum Ratings

Parameter

Symbol

Value

Unit

VCC

40

Collector Supply Voltage

VC

40

Output Current, Sink or Source

IO

500

mA

IREF

50

mA

ICHG(OSC)

mA

Supply Voltage

Reference Output Current

Oscillator Charging Current

Power Dissipation (TA = 25C)

PD

1000

m/W

Operating Temperature

TOPR

0 ~ +70

Storage Temperature

TSTG

-65 ~ +150

Lead Temperature (Soldering, 10sec)

TLEAD

+300

Electrical Characteristics

(VCC = 20V, TA = 0 to +70C, unless otherwise specified)

Parameter

Symbol

Conditions

Min.

Typ. Max.

Unit

5.0

5.1

5.2

REFERENCE SECTION

Reference Output Voltage

VREF

TJ = 25C

Line Regulation

VREF

VCC = 8 to 35V

20

mV

Load Regulation

VREF

IREF = 0 to 20mA

20

50

mV

VREF = 0, TJ = 25C

80

100

mA

4.95

5.25

20

50

mV

TJ = 125C ,1KHRS

20

50

mV

Short Circuit Output Current

ISC

Total Output Variation (Note1)

VREF

Temperature Stability (Note1)

STT

Long Term Stability (Note1)

ST

Line, Load and Temperature

-

OSCILLATOR SECTION

Initial Accuracy (Note1, 2)

ACCUR

TJ = 25C

Frequency Change With Voltage

f/VCC

VCC = 8 to 35V (Note1, 2)

Maximum Frequency

f(MAX)

RT = 2k, CT = 470pF

Minimum Frequency

f(MIN)

RT = 200k, CT = 0.1uF

Clock Amplitude (Note1, 2)

V(CLK)

Clock Width (Note1, 2)

tW(CLK)

Sync Threshold

Sync Input Current

TJ = 25C

-

VTH(SYNC)

II(SYNC)

Sync = 3.5V

0.8

400

430

kHz

60

120

Hz

0.3

0.6

1.2

2.8

1.3

2.5

mA

KA3525A

Electrical Characteristics (Continued)

(VCC = 20V, TA = 0 to +70C, unless otherwise specified)

Parameter

Symbol

Conditions

Min.

VIO

IBIAS

IIO

Typ. Max. Unit

ERROR AMPLIFIER SECTION (VCM = 5.1V)

Input Offset Voltage

Input Bias Current

Input Offset Current

Open Loop Voltage Gain

GVO

1.5

10

mV

10

0.1

RL 10M

60

80

dB

Common Mode Rejection Ratio

CMRR

VCM = 1.5 to 5.2V

60

90

dB

Power Supply Rejection Ratio

PSRR

VCC = 8 to 3.5V

50

60

dB

PWM COMPARATOR SECTION

Minimum Duty Cycle

D(MIN)

Maximum Duty Cycle

D(MAX)

45

49

Input Threshold Voltage (Note2)

VTH1

Zero Duty Cycle

0.7

0.9

Input Threshold Voltage (Note2)

VTH2

Max Duty Cycle

3.2

3.6

ISOFT

VSD = 0V, VSS = 0V

25

51

80

0.3

0.7

0.9

1.3

1.7

SOFT-START SECTION

Soft Start Current

Soft Start Low Level Voltage

VSL

Shutdown Threshold Voltage

VTH(SD)

Shutdown Input Current

VSD = 25V

-

IN(SD)

VSD = 2.5V

0.3

mA

Low Output Voltage I

VOL I

ISINK = 20mA

0.1

0.4

Low Output Voltage II

VOL II

ISINK = 100mA

0.05

High Output Voltage I

VCH I

ISOURCE = 20mA

18

19

High Output Voltage II

VCH II

ISOURCE = 100mA

17

18

OUTPUT SECTION

Under Voltage Lockout

VUV

V8 and V9 = High

Collector Leakage Current

ILKG

VCC = 35V

80

200

Rise Time (Note1)

tR

CL = 1uF, TJ = 25C

80

600

ns

Fall Time (Note1)

tF

CL = 1uF, TJ = 25C

70

300

ns

VCC = 35V

12

20

mA

STANDBY CURRENT

Supply Current

ICC

Note :

1. These parameters. although guaranteed over the recommended operating conditions, are not 100% tested in production

2. Tested at fOSC=40kHz (RT =3.6K, CT =0.01uF, RI = 0)

KA3525A

Test Circuit

16

3k

Vcc

BAND GAP

REF 5V

15

0.1

RWM

ADJ

U.V.L.O.

13

12

10k

_

ERR

AMP

1.5K

OUT A

LATCH

S

S R

ERR

AMP

10K

SOFT START

11

10k

OSCILLATOR

0.01

+

VC

0.1

3 6

10k

F/F

5.0uF

14

CLOCK

5.0k

10

OUT B

5.0k

VREF

5.0k

SHUTDOWN

CT

100

RAMP

DEAD

TIME

RT

0.001

+

0.009

0.1

3.6k

KA3525A

Mechanical Dimensions

Package

16-DIP

#9

7.62

0.300

2.54

0.100

1.50 0.10

0.059 0.004

#8

0.46 0.10

0.018 0.004

#16

19.80

MAX

0.780

#1

19.40 0.20

0.764 0.008

0.81

)

0.032

6.40 0.20

0.252 0.008

3.25 0.20

0.128 0.008

5.08

MAX

0.200

0.38

MIN

0.014

3.30 0.30

0.130 0.012

+0.10

0~15

0.25 0.05

+0.004

0.010 0.002

KA3525A

Ordering Information

Product Number

Package

Operating Temperature

KA3525A

16-DIP

0 ~ +70C

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER

DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, and (c) whose failure to

perform when properly used in accordance with

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

2. A critical component in any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

10/2/02 0.0m 001

Stock#DSxxxxxxxx

2002 Fairchild Semiconductor Corporation

You might also like

- ARC 164 Manual PDFDocument140 pagesARC 164 Manual PDFJoão Pedro Almeida100% (2)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Wire Set OPT-1 Reference Guide: HT-3 H/LDocument9 pagesWire Set OPT-1 Reference Guide: HT-3 H/LJoão Pedro AlmeidaNo ratings yet

- UC3525Document9 pagesUC3525Roger FollanoNo ratings yet

- UC3842A/UC3843A: SMPS ControllerDocument8 pagesUC3842A/UC3843A: SMPS ControllerjosephsnadaNo ratings yet

- LM350 DatasheetDocument12 pagesLM350 DatasheetOmarVelasquezC.No ratings yet

- L5970DDocument10 pagesL5970Droozbehxox100% (1)

- DatasheetDocument8 pagesDatasheetSyed AliNo ratings yet

- Uc3843a PDFDocument8 pagesUc3843a PDFKang JadiJaya OtodidakNo ratings yet

- KA7500CDocument8 pagesKA7500CGiannis StratourisNo ratings yet

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocument10 pagesSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNo ratings yet

- Green Current Mode PWM Controller: Features DescriptionDocument12 pagesGreen Current Mode PWM Controller: Features Descriptionceny123No ratings yet

- MC34063A/MC33063A: SMPS ControllerDocument8 pagesMC34063A/MC33063A: SMPS ControllerroozbehxoxNo ratings yet

- KA7552A Power Supply UtechDocument6 pagesKA7552A Power Supply UtechHeriberto Flores AmpieNo ratings yet

- MC1723 PDFDocument9 pagesMC1723 PDFOsman KoçakNo ratings yet

- MC34063AMDocument16 pagesMC34063AMSajjad4434No ratings yet

- DatasheetDocument24 pagesDatasheetMarcelo RaulNo ratings yet

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocument14 pagesMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsVũ TưởngNo ratings yet

- 12V DC To 40V DC Converter Circuit DiagramDocument10 pages12V DC To 40V DC Converter Circuit DiagramAhdiat Darmawan LubisNo ratings yet

- 7824 Data SheetDocument34 pages7824 Data Sheethjkhj4219No ratings yet

- 8205Document16 pages8205sonytinNo ratings yet

- MC34063ADocument15 pagesMC34063AAlfredo Valencia RodriguezNo ratings yet

- Ap 34063Document10 pagesAp 34063Hoang LeNo ratings yet

- FAN8082 (KA3082N) : Bi-Directional DC Motor DriverDocument13 pagesFAN8082 (KA3082N) : Bi-Directional DC Motor DriverFrancisco Hernandez MartinezNo ratings yet

- Document - SG3525A DDocument10 pagesDocument - SG3525A Donlinerahul823405No ratings yet

- Regulating Pulse Width Modulators: Features DescriptionDocument7 pagesRegulating Pulse Width Modulators: Features DescriptionkkaytugNo ratings yet

- MC 34152Document12 pagesMC 34152dcastrelos2000No ratings yet

- Datasheet Controlaor CiDocument17 pagesDatasheet Controlaor Cineta123abcNo ratings yet

- UC3845Document13 pagesUC3845roozbehxoxNo ratings yet

- UC3843 DatasheetDocument13 pagesUC3843 DatasheetBigbrain99No ratings yet

- KA34063Document6 pagesKA34063KJ AlfafaraNo ratings yet

- Driver Bobina de Encendido VB326SPDocument9 pagesDriver Bobina de Encendido VB326SPteroplasNo ratings yet

- LM339 LM239 LM2901 DatasheetDocument8 pagesLM339 LM239 LM2901 DatasheetEza RezaNo ratings yet

- ST3232 Data SheetDocument12 pagesST3232 Data SheetcredioNo ratings yet

- Ka3082 Controlador de Motores CCDocument12 pagesKa3082 Controlador de Motores CCshibatoyanNo ratings yet

- 7555 CNDocument9 pages7555 CNdsdsds4No ratings yet

- Iramx 16 Up 60 ADocument17 pagesIramx 16 Up 60 AJandfor Tansfg ErrottNo ratings yet

- LM 339Document11 pagesLM 339Adi PamungkasNo ratings yet

- HCF4016B: Quad Bilateral SwitchDocument10 pagesHCF4016B: Quad Bilateral SwitchDai Lam MocNo ratings yet

- CS2841BD14Document10 pagesCS2841BD14giapy0000No ratings yet

- LTC 1625Document24 pagesLTC 1625Sakura KunNo ratings yet

- Compuerta and 74HC08Document9 pagesCompuerta and 74HC08Elio GranadosNo ratings yet

- DC To DC Converter Controller: DescriptionDocument9 pagesDC To DC Converter Controller: DescriptionMick NimalNo ratings yet

- 7 M 0880Document18 pages7 M 0880Mahmoued YasinNo ratings yet

- MAX038Document16 pagesMAX038fabirznNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNo ratings yet

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Some Power Electronics Case Studies Using Matlab Simpowersystem BlocksetFrom EverandSome Power Electronics Case Studies Using Matlab Simpowersystem BlocksetNo ratings yet

- Antenna Details: ShipboardDocument70 pagesAntenna Details: ShipboardJoão Pedro AlmeidaNo ratings yet

- OpAmp Reference SheetDocument5 pagesOpAmp Reference SheetJoão Pedro AlmeidaNo ratings yet

- Opt-1 V2 PDFDocument9 pagesOpt-1 V2 PDFJoão Pedro AlmeidaNo ratings yet

- RMS PDFDocument4 pagesRMS PDFJoão Pedro AlmeidaNo ratings yet

- UPS Transformer Winding E140166 XPB-5Document1 pageUPS Transformer Winding E140166 XPB-5João Pedro AlmeidaNo ratings yet

- Long-Term Storage of Components, Subassemblies and Devices: Guidelines For TheDocument32 pagesLong-Term Storage of Components, Subassemblies and Devices: Guidelines For TheJoão Pedro AlmeidaNo ratings yet

- PP1990 Power Supply: Replacement For The DY103 Dynamotor in The ARC34Document1 pagePP1990 Power Supply: Replacement For The DY103 Dynamotor in The ARC34João Pedro AlmeidaNo ratings yet

- Dpi 610 PDFDocument8 pagesDpi 610 PDFJoão Pedro AlmeidaNo ratings yet

- MRO Hangar: One Simple, Low Cost SolutionDocument17 pagesMRO Hangar: One Simple, Low Cost SolutionJoão Pedro AlmeidaNo ratings yet

- AIC-18 Spec PDFDocument2 pagesAIC-18 Spec PDFJoão Pedro AlmeidaNo ratings yet

- Aims Power Invertors Gain Market ForceDocument2 pagesAims Power Invertors Gain Market ForceJoão Pedro AlmeidaNo ratings yet

- Solutions For Long-Term Storage of Electronic Components and CompositionsDocument3 pagesSolutions For Long-Term Storage of Electronic Components and CompositionsJoão Pedro AlmeidaNo ratings yet

- Gray Code Generator and Decoder: by Carsten Kristiansen Napier University November 2004Document21 pagesGray Code Generator and Decoder: by Carsten Kristiansen Napier University November 2004João Pedro AlmeidaNo ratings yet

- MC14066B Quad Analog Switch/Quad Multiplexer: Marking DiagramsDocument12 pagesMC14066B Quad Analog Switch/Quad Multiplexer: Marking DiagramsJoão Pedro AlmeidaNo ratings yet

- Amateur Radio Magazin 01 - January - 1975 PDFDocument164 pagesAmateur Radio Magazin 01 - January - 1975 PDFJoão Pedro AlmeidaNo ratings yet

- Inverters & Voltage ConvertersDocument28 pagesInverters & Voltage ConvertersJoão Pedro AlmeidaNo ratings yet

- Gillham Code: Altitude EncoderDocument1 pageGillham Code: Altitude EncoderJoão Pedro AlmeidaNo ratings yet

- Inverters & Voltage ConvertersDocument28 pagesInverters & Voltage ConvertersJoão Pedro AlmeidaNo ratings yet

- Ucc 28056Document52 pagesUcc 28056João Pedro AlmeidaNo ratings yet

- Dimensions in MM (Inches) .: TO3 (TO204AA) PinoutsDocument1 pageDimensions in MM (Inches) .: TO3 (TO204AA) PinoutsJoão Pedro AlmeidaNo ratings yet

- Philips B4ln16a-35 Radio 1962 SMDocument8 pagesPhilips B4ln16a-35 Radio 1962 SMJoão Pedro AlmeidaNo ratings yet

- For Sliding Gates: EN - Instructions and Warnings For Installation and UseDocument28 pagesFor Sliding Gates: EN - Instructions and Warnings For Installation and UseJoão Pedro AlmeidaNo ratings yet

- KT 79 Pilot's ManualDocument6 pagesKT 79 Pilot's ManualJoão Pedro AlmeidaNo ratings yet

- Model Freq. (GHZ) Output Power (W) Duty Factor (%) Mech. Tuning Range (MHZ) Filament Voltage (V) Plate Voltage (V) Plate Current (Ma) FeaturesDocument2 pagesModel Freq. (GHZ) Output Power (W) Duty Factor (%) Mech. Tuning Range (MHZ) Filament Voltage (V) Plate Voltage (V) Plate Current (Ma) FeaturesJoão Pedro AlmeidaNo ratings yet

- KLN 94 InstallDocument156 pagesKLN 94 InstallJoão Pedro AlmeidaNo ratings yet

- Cdpe6320 Candy ProgramingDocument51 pagesCdpe6320 Candy ProgramingJoão Pedro AlmeidaNo ratings yet