Professional Documents

Culture Documents

Sant Baba Bhag Singh University: 2 Semester 2015-2016 (Test-1) M.Tech (ECE)

Uploaded by

Abhishek SainiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sant Baba Bhag Singh University: 2 Semester 2015-2016 (Test-1) M.Tech (ECE)

Uploaded by

Abhishek SainiCopyright:

Available Formats

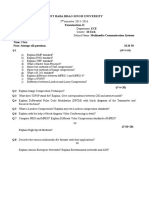

SANT BABA BHAG SINGH UNIVERSITY

2nd semester 2015-2016 (Test-1)

M.Tech(ECE)

Institute: UIET

Department: ECE

Time: 3 hrs.

Note: Attempt all questions.

Subject: Advanced Microprocessor & Embedded System

Subject Code: ECE-510

M.M 50

Q.1

(10*1=10)

a)

b)

c)

d)

e)

f)

How the 20-bit effective address is calculated in 8086 processor?

What do you mean by pipelining in 8086?

Which addressing mode often addresses a 2-D array of memory data?

Draw the format of 8086 flag register?

What is the use of BIU in 8086?

What are the advantages of memory segmentation?

g)

Why is a Capacitor connected between Reset and

h)

i)

Which interrupts are used for critical events?

The instruction MOV CL, [BX+4] shows which addressing mode?

j)

What is the size of 8086 instruction? What is meant by instruction queue?

V cc pin?

(5*4=20)

Q.2 The original contents of AX, BL word-sized memory location SUM, and carry flag CF are 1234H, ABH,

00CDH, and 0H, respectively. Describe the results of executing the following sequence of instructions:

ADD AX,[SUM]

ADC BL, 05H

INC WORD PTR [SUM]

Q.3 Explain the instruction a) DAA b)LEA c)RCL d)LAHF e)SAHF f)LDS g) ROR h) TEST

Q.4 Explain the function of various flags of 8086 microprocessor?

Q.5 Describe any five addressing modes with suitable example?

Q.6 Explain 8284 clock generator and draw its block diagram?

(2*10=20)

Q.7 Describe Intel 8086 microprocessor architecture in detail?

Or

Write an ALP in 8086 to add two 16 bit hexadecimal numbers?

Q.8 With appropriate pin diagrams explain the minimum and maximum mode operations of 8086?

Or

Distinguish between a memory read and write machine cycle. Draw the timing diagrams in minimum and

maximum modes of operation?

You might also like

- Multidimensional Signal, Image, and Video Processing and CodingFrom EverandMultidimensional Signal, Image, and Video Processing and CodingNo ratings yet

- CS2402 QB mpc2Document10 pagesCS2402 QB mpc2Prabhavathi AadhiNo ratings yet

- MUltimedia Compression Techniques Question PaperDocument2 pagesMUltimedia Compression Techniques Question PaperPurush Jayaraman100% (1)

- Question Papers of Computer Communication NetworksDocument32 pagesQuestion Papers of Computer Communication NetworksRajathSharma100% (2)

- CCNA Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesFrom EverandCCNA Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNo ratings yet

- Sant Baba Bhag Singh University Examination-II: 2 Semester 2015-2016Document1 pageSant Baba Bhag Singh University Examination-II: 2 Semester 2015-2016Abhishek SainiNo ratings yet

- 5.nov 2012 PDFDocument2 pages5.nov 2012 PDFkarthickamsecNo ratings yet

- 3.nov 2011 PDFDocument2 pages3.nov 2011 PDFkarthickamsecNo ratings yet

- HPCN QuestionsDocument2 pagesHPCN Questionssmsekar100% (1)

- Name: .. Bishop Jerome Institute Eighth Semester B.Tech First Series Examination FEB 2018Document2 pagesName: .. Bishop Jerome Institute Eighth Semester B.Tech First Series Examination FEB 2018BJI ALUMNINo ratings yet

- 1.nov 2010 PDFDocument2 pages1.nov 2010 PDFkarthickamsecNo ratings yet

- B.E./B.Tech Degree Examination April/May 2011: Maximum: 100 MarksDocument2 pagesB.E./B.Tech Degree Examination April/May 2011: Maximum: 100 MarksJagan MuthusamyNo ratings yet

- 15 1507012 Computer NetworkDocument2 pages15 1507012 Computer Networkakhorasiya5815100% (1)

- B.E./B.Tech Degree Examination April/May 2011Document2 pagesB.E./B.Tech Degree Examination April/May 2011karthickamsecNo ratings yet

- CT1037N CW MCQ 2Document8 pagesCT1037N CW MCQ 2Nelson Naval CabingasNo ratings yet

- rr310503 Data CommunicationsDocument4 pagesrr310503 Data CommunicationsSrinivasa Rao GNo ratings yet

- 10bt6120sdasd2-Computer Networks 2Document1 page10bt6120sdasd2-Computer Networks 2ABILASHNo ratings yet

- Assignment (5BCA MDU) : DEBCA-501 (Data Communication & Networks)Document1 pageAssignment (5BCA MDU) : DEBCA-501 (Data Communication & Networks)Saurabh MishraNo ratings yet

- Anna Univ May - June Model Questions High Performance Computer Networks Question Paper June 2011-2013 - Anna University Results 2013 - Anna Univ Updates PDFDocument2 pagesAnna Univ May - June Model Questions High Performance Computer Networks Question Paper June 2011-2013 - Anna University Results 2013 - Anna Univ Updates PDFMurali DharanNo ratings yet

- Networking Fundamentals AssignmentDocument10 pagesNetworking Fundamentals AssignmentHategekimana ErnestNo ratings yet

- Data Communication AssignmentDocument4 pagesData Communication Assignmentakash chaudharyNo ratings yet

- Behala College Gen Test 2017Document1 pageBehala College Gen Test 2017Ln Amitav BiswasNo ratings yet

- M.E Advanced Radiation Systems Question PaperDocument2 pagesM.E Advanced Radiation Systems Question PaperArun ShanmugamNo ratings yet

- Sessional Examination, 2015-2016: Latches and Flip FlopDocument1 pageSessional Examination, 2015-2016: Latches and Flip FlopdhananjayNo ratings yet

- Bscit 503Document2 pagesBscit 503api-3782519No ratings yet

- Computer Networks 2020-21Document5 pagesComputer Networks 2020-21nawejakhatar10063No ratings yet

- III Semester B.C.A. Examination, May 2012 Data CommunicationDocument2 pagesIII Semester B.C.A. Examination, May 2012 Data CommunicationvigveluNo ratings yet

- 07A4EC08 Object Oriented ProgrammingDocument1 page07A4EC08 Object Oriented ProgrammingsivabharathamurthyNo ratings yet

- 2204sep22 1Document1 page2204sep22 1Raj KumarNo ratings yet

- B.E./B.Tech Degree Examination May/June 2012Document2 pagesB.E./B.Tech Degree Examination May/June 2012karthickamsecNo ratings yet

- Computer NetworksDocument4 pagesComputer NetworksSavari RajNo ratings yet

- BTCS 403Document2 pagesBTCS 403sakibhussain036No ratings yet

- 4th YearDocument65 pages4th YearDattaprasad EkavadeNo ratings yet

- Model Exam Year/Sem: III/V Hours: 3hrs Total Marks: 100 PART - A (10 X 2 20 Marks)Document2 pagesModel Exam Year/Sem: III/V Hours: 3hrs Total Marks: 100 PART - A (10 X 2 20 Marks)aishu sillNo ratings yet

- BSC Itim May 2013BSC IT Prevoues Question PaperDocument28 pagesBSC Itim May 2013BSC IT Prevoues Question PaperPurushothama KilariNo ratings yet

- JanuaryFebruary 2023Document2 pagesJanuaryFebruary 2023Pokala ShekerNo ratings yet

- HW DVBDocument6 pagesHW DVBPrasetya AnggiNo ratings yet

- 52 FjbjfeDocument2 pages52 FjbjfeDiboresh SahaNo ratings yet

- Data Communication Networks Nec 702B PDFDocument2 pagesData Communication Networks Nec 702B PDFomenderNo ratings yet

- CS9211-Computer Architecture QuestionDocument7 pagesCS9211-Computer Architecture Questionrvsamy80No ratings yet

- Computer Communication & Networking (Ec602) : Group ADocument3 pagesComputer Communication & Networking (Ec602) : Group Asg1983No ratings yet

- Seventh Semester B TEC IN Ering Degree Examination December 2010Document1 pageSeventh Semester B TEC IN Ering Degree Examination December 2010Abhishek EkNo ratings yet

- Network TheoryDocument1 pageNetwork Theorypardeep4372No ratings yet

- Answer ALL Questions. PART A - (10 2 20 Marks)Document2 pagesAnswer ALL Questions. PART A - (10 2 20 Marks)Dhanusha Chandrasegar Sabarinath0% (1)

- (MCQ) Computer Communication Networks - LMTDocument18 pages(MCQ) Computer Communication Networks - LMTraghad mejeedNo ratings yet

- Etec 406 AsnDocument1 pageEtec 406 AsnHimanshiNo ratings yet

- Satthyabama-Isem-Data Comunication and Computer Networks 6C0500-7C0500Document2 pagesSatthyabama-Isem-Data Comunication and Computer Networks 6C0500-7C0500ShankarNo ratings yet

- WWW - Manaresults.Co - In: Set No. 1Document4 pagesWWW - Manaresults.Co - In: Set No. 1Vishant ChaudharyNo ratings yet

- Set No: 1: Code No: V3224/R07Document4 pagesSet No: 1: Code No: V3224/R07jitendra28No ratings yet

- Answer ALL QuestionsDocument15 pagesAnswer ALL QuestionsSathyanarayana YogendranNo ratings yet

- 13A05601 Computer NetworksDocument1 page13A05601 Computer NetworksJaya SankarNo ratings yet

- Jntuworld: R07 Set No. 2Document4 pagesJntuworld: R07 Set No. 2Ram KrishnaNo ratings yet

- Answer ALL Questions: PART B (5 X 16 80)Document17 pagesAnswer ALL Questions: PART B (5 X 16 80)Ahmed Eid Abd ElRaoufNo ratings yet

- D G1071 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesD G1071 Pages: 2: Answer Any Two Full Questions, Each Carries 15 Markschristopher pNo ratings yet

- II Semester M.Sc. (I.T.) Examination, December 2009/january 2010 Software Quality and Testing (Repeater)Document8 pagesII Semester M.Sc. (I.T.) Examination, December 2009/january 2010 Software Quality and Testing (Repeater)amitukumarNo ratings yet

- J2EE IIIsem 583305 ITE03Document2 pagesJ2EE IIIsem 583305 ITE03ShankarNo ratings yet

- Computer Network BankDocument2 pagesComputer Network BankAyushiNo ratings yet

- Digital Video Distribution in Broadband, Television, Mobile and Converged Networks: Trends, Challenges and SolutionsFrom EverandDigital Video Distribution in Broadband, Television, Mobile and Converged Networks: Trends, Challenges and SolutionsNo ratings yet

- Optimizers For NeuralNetworksDocument13 pagesOptimizers For NeuralNetworksAbhishek SainiNo ratings yet

- Communication Channel Design Using MATLAB SimulationDocument30 pagesCommunication Channel Design Using MATLAB SimulationAbhishek SainiNo ratings yet

- Artificial Intelligence - IntroductionDocument40 pagesArtificial Intelligence - IntroductionAbhishek SainiNo ratings yet

- Natural Language ProcessingDocument27 pagesNatural Language ProcessingAbhishek SainiNo ratings yet