Professional Documents

Culture Documents

Co 2007 Vlsi

Uploaded by

Wajahat Mirza0 ratings0% found this document useful (0 votes)

4 views1 pageREVISED COURSE OUTLINE FOR THE SUBJECT Batch 2007, computer engineering department. ICs Advantages / disadvantages of ICs Scales of integration Moore's law IC Economics - Yield, Faults and Defects. Programmable Logic devices: SPLD and CPLD Programmable switch technologies Implementing logic circuits in CMOS logic.

Original Description:

Original Title

CO-2007-VLSI

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentREVISED COURSE OUTLINE FOR THE SUBJECT Batch 2007, computer engineering department. ICs Advantages / disadvantages of ICs Scales of integration Moore's law IC Economics - Yield, Faults and Defects. Programmable Logic devices: SPLD and CPLD Programmable switch technologies Implementing logic circuits in CMOS logic.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

4 views1 pageCo 2007 Vlsi

Uploaded by

Wajahat MirzaREVISED COURSE OUTLINE FOR THE SUBJECT Batch 2007, computer engineering department. ICs Advantages / disadvantages of ICs Scales of integration Moore's law IC Economics - Yield, Faults and Defects. Programmable Logic devices: SPLD and CPLD Programmable switch technologies Implementing logic circuits in CMOS logic.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

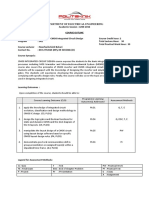

REVISED COURSE OUTLINE FOR THE SUBJECT

VLSI DESIGN TECHNIQUES (CE-410)

COURSE COORDINATOR: SAQIB HUSSAIN SIDDIQUI COURSE TEACHERS: MUHAMMAD NASEEM, HASAN RAZA NAQVI, MUHAMMAD ZEESHAN AHMED KARIM

Batch 2007, Computer Engineering Department

Weeks 1 & 2: Discrete and Integrated Circuits Advantages/disadvantages of ICs IC terminology Scales of integration Moores law IC Economics Yield, Faults and Defects Weeks 3 & 4: Introduction to electronic switch MOS transistor Introduction Types Working as a switch Week #5: Introduction to CMOS logic Implementing logic circuits in CMOS logic Weeks 6 & 7: IC Design Processes Week #8: MID-TERM TEST Weeks 9, 10 & 11: Step-by-step fabrication of a CMOS inverter Week #12: Programmable Logic devices: SPLD & CPLD Programmable switch technologies Implementing logic circuits using SPLDs Week #13: Semiconductor Memories Storage cells of: ROM PROM EPROM EEPROM Flash EPROM SRAM DRAM

Weeks #14: ASICs Advantages of ASICs Types of ASICs ASIC Design cycle Week #15: Programmable Logic implementation: Multiplexer Lookup Tables Weeks #16: Physical design Placement & Routing (P&R) algorithm Future trends in VLSI technology (optional)

COURSE BOOKS:

TEXT: ASICs By: Michael John Sebastian Smith REFERENCE: VLSI DESIGN TECHNIQUES ANALOG & DIGITAL CIRCUITS By: Randall / Geiger / Strader

FOR

Sessional grading: (excluding Practical side)

Best one of two assignments: 10 marks x 1 Best two of three quizzes: 05 Marks x 2 Mid-term (regular): 10 marks Mid-term (compensation): 7.5 marks

You might also like

- The System Designer's Guide to VHDL-AMS: Analog, Mixed-Signal, and Mixed-Technology ModelingFrom EverandThe System Designer's Guide to VHDL-AMS: Analog, Mixed-Signal, and Mixed-Technology ModelingRating: 5 out of 5 stars5/5 (1)

- ChipedgeDocument4 pagesChipedgeMhappyCuNo ratings yet

- CMOS VLSI and Aspect of ASIC DesignDocument3 pagesCMOS VLSI and Aspect of ASIC DesignBittU BhagatNo ratings yet

- EE 523-VLSI Design-Dr. Shahid Masud PDFDocument2 pagesEE 523-VLSI Design-Dr. Shahid Masud PDFSohail MashwaniNo ratings yet

- Modern Component Families and Circuit Block DesignFrom EverandModern Component Families and Circuit Block DesignRating: 5 out of 5 stars5/5 (1)

- Ec 544Document2 pagesEc 544Surbhi SinghNo ratings yet

- On-Chip Communication Architectures: System on Chip InterconnectFrom EverandOn-Chip Communication Architectures: System on Chip InterconnectNo ratings yet

- Course Contents of VLSIDocument2 pagesCourse Contents of VLSIOmer KhanNo ratings yet

- MicroelectronicsDocument39 pagesMicroelectronicsArun Av0% (1)

- Vlsi DesignDocument2 pagesVlsi DesignShribala NagulNo ratings yet

- Introduction EE603Document6 pagesIntroduction EE603Wazir ZafranNo ratings yet

- Analog Layout DesignDocument2 pagesAnalog Layout DesignRajesh Kumar Patjoshi100% (1)

- EEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Document2 pagesEEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Harsha DuttaNo ratings yet

- Course Pre-Requisite: BE Electronics Engineering (R-2012)Document24 pagesCourse Pre-Requisite: BE Electronics Engineering (R-2012)Hannan SatopayNo ratings yet

- 21ec503 Vlsi Design Unit 1Document110 pages21ec503 Vlsi Design Unit 1santhoshiniNo ratings yet

- BECE303LDocument3 pagesBECE303LKAVIYA DIASNo ratings yet

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Document2 pagesEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamNo ratings yet

- Ece MT SylDocument79 pagesEce MT Sylpermiable permissionNo ratings yet

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsDocument122 pagesSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsRAAJ KISHOR R HNo ratings yet

- Mtech Electronics Syllabus VTUDocument48 pagesMtech Electronics Syllabus VTUmuqeetmmaNo ratings yet

- EE412 Course OutlineDocument2 pagesEE412 Course OutlineFaiq GhawashNo ratings yet

- VlsiDocument3 pagesVlsiMayank Karwa 16BEC0067No ratings yet

- VLSI ModulesDocument28 pagesVLSI Modulessai_karthik89No ratings yet

- ECE3002Document2 pagesECE3002Ritayan PatraNo ratings yet

- Vlsi NotesDocument5 pagesVlsi NotesDiwakar TiwaryNo ratings yet

- VLSI OutlineDocument4 pagesVLSI OutlineMuhammad Kamran AkramNo ratings yet

- DEE6113 Course Outline Jun2016Document4 pagesDEE6113 Course Outline Jun2016FonzBahariNo ratings yet

- Lec 1Document45 pagesLec 1Abdullah MadniNo ratings yet

- Semester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)Document19 pagesSemester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)Sneha NargundkarNo ratings yet

- Vlsi PT 1st Year SyllabusDocument17 pagesVlsi PT 1st Year SyllabusMANGAL KUMAR MOHAPATRANo ratings yet

- OutlineDocument1 pageOutlineVarg VikernesNo ratings yet

- M.Tech 2nd SemesterDocument14 pagesM.Tech 2nd SemesterSivaramsharma RupavathamNo ratings yet

- Digital ElectronicsDocument228 pagesDigital ElectronicsMujeeb AbdullahNo ratings yet

- UntitledDocument2 pagesUntitledDr. M Kiran KumarNo ratings yet

- Vlsi SyllabusDocument3 pagesVlsi SyllabusmadhurNo ratings yet

- NIT 1 4 7040 Lecture 1 VLSI EC601Document26 pagesNIT 1 4 7040 Lecture 1 VLSI EC601SANDIP PODDARNo ratings yet

- Course Work SyllabusDocument4 pagesCourse Work SyllabusKiruba KaranNo ratings yet

- Vlsi Design ECE5014Document5 pagesVlsi Design ECE5014SriramNo ratings yet

- 21ec503 Vlsi Design Unit IIIDocument100 pages21ec503 Vlsi Design Unit IIIsanthoshiniNo ratings yet

- 2022 Ch0-Course IntroductionDocument10 pages2022 Ch0-Course IntroductionSư LưuNo ratings yet

- Ece3002 Vlsi-system-Design Eth 1.2 49 Ece3002 41Document2 pagesEce3002 Vlsi-system-Design Eth 1.2 49 Ece3002 41SMNo ratings yet

- VLSI Design Lab NewDocument48 pagesVLSI Design Lab NewJubin JainNo ratings yet

- Syllabus EC-312Document2 pagesSyllabus EC-312U Rama KrishnaNo ratings yet

- Vlsi 1Document24 pagesVlsi 1hrrameshhrNo ratings yet

- Btech New SyllabusDocument8 pagesBtech New SyllabusDrBhoopal RaoNo ratings yet

- r19 Mtech Emb Full-10-19Document10 pagesr19 Mtech Emb Full-10-19saikanna427No ratings yet

- Gujarat Technological University: W.E.F. AY 2018-19Document3 pagesGujarat Technological University: W.E.F. AY 2018-19bakoliy218No ratings yet

- Vlsi DesignDocument3 pagesVlsi Designkumarrajivranjan440No ratings yet

- Lec 01-02Document26 pagesLec 01-02Basem HeshamNo ratings yet

- Skill Lab Report Group-B (HK)Document12 pagesSkill Lab Report Group-B (HK)Harsh KumarNo ratings yet

- Sem5 EJ5EDocument38 pagesSem5 EJ5EAjit SinghNo ratings yet

- VLSI Technology and DesignDocument2 pagesVLSI Technology and DesignJigar PatelNo ratings yet

- EC NotesDocument2 pagesEC Noteshanumantha12No ratings yet

- Vlsi Design: Text BooksDocument2 pagesVlsi Design: Text BooksAshutoshBhattNo ratings yet

- VLSI Design Syllabus - 2018 SchemeDocument2 pagesVLSI Design Syllabus - 2018 SchemeShivansh BhartiNo ratings yet

- Vlsi DesignDocument3 pagesVlsi DesignGokulNo ratings yet

- 3-2 Syllabus (1) - MergedDocument14 pages3-2 Syllabus (1) - Mergededucational9hubNo ratings yet

- Sem1 EmbbededDocument9 pagesSem1 Embbededvishwanath cNo ratings yet

- Computer Science: A Concise IntroductionFrom EverandComputer Science: A Concise IntroductionRating: 4.5 out of 5 stars4.5/5 (14)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)From EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Rating: 5 out of 5 stars5/5 (1)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyFrom EverandChip War: The Quest to Dominate the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (227)

- Chip War: The Fight for the World's Most Critical TechnologyFrom EverandChip War: The Fight for the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (82)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XFrom EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XRating: 3 out of 5 stars3/5 (2)

- Amazon Web Services (AWS) Interview Questions and AnswersFrom EverandAmazon Web Services (AWS) Interview Questions and AnswersRating: 4.5 out of 5 stars4.5/5 (3)

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertFrom EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertRating: 3.5 out of 5 stars3.5/5 (6)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102From EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Rating: 5 out of 5 stars5/5 (2)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxFrom EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNo ratings yet

- Programming with STM32: Getting Started with the Nucleo Board and C/C++From EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Rating: 3.5 out of 5 stars3.5/5 (3)

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XFrom EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XRating: 5 out of 5 stars5/5 (1)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideFrom EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideRating: 1 out of 5 stars1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002From EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Rating: 5 out of 5 stars5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]From EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Rating: 5 out of 5 stars5/5 (2)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFFrom EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFNo ratings yet

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)