Professional Documents

Culture Documents

Intel 8085 Reference Card

Intel 8085 Reference Card

Uploaded by

Niranjan NeruCopyright:

Available Formats

You might also like

- Behringer Xenyx 1622fx SchematicsDocument12 pagesBehringer Xenyx 1622fx SchematicsJoaquim Dos Santos Veras Maia100% (1)

- 8085 OpcodesDocument3 pages8085 OpcodesSwapna PriyaNo ratings yet

- D&D 5 Ext Mini GamesDocument4 pagesD&D 5 Ext Mini GamesLucasNo ratings yet

- Resistance Training Program DesignDocument30 pagesResistance Training Program DesignKostas LiougkosNo ratings yet

- Z80PCRDDocument2 pagesZ80PCRDTấn Phát TrầnNo ratings yet

- Z80PCRDDocument2 pagesZ80PCRDKhánh NguyễnNo ratings yet

- Machine CodesDocument5 pagesMachine CodesSarah ShermanNo ratings yet

- Hex CodeDocument1 pageHex CodeShaorya Vijay0% (1)

- Instruction Set of 8085Document2 pagesInstruction Set of 8085mmasliniaNo ratings yet

- Esque MaDocument1 pageEsque MaAlexander PerdomoNo ratings yet

- SCH TPM 4250 6250 8250 30-01-08 PDFDocument22 pagesSCH TPM 4250 6250 8250 30-01-08 PDFJosé Benavides0% (2)

- Bahan Kuliah 8 Tabel Instruksi Set 8085Document9 pagesBahan Kuliah 8 Tabel Instruksi Set 8085FaJriNo ratings yet

- 8086 NotesDocument10 pages8086 Notesmiker00lzNo ratings yet

- W375 L3 V1.2 SchemDocument3 pagesW375 L3 V1.2 SchemAdrian PeterNo ratings yet

- x03/x04/x06 Version 2.40-2.4x: Pcu Command SummaryDocument6 pagesx03/x04/x06 Version 2.40-2.4x: Pcu Command Summaryemorillo2No ratings yet

- Sony Vaio Mbx-126 - Quanta Je5.1Document36 pagesSony Vaio Mbx-126 - Quanta Je5.1nunoq171No ratings yet

- SRT 4155 and SRT4355 - ServicemanualDocument40 pagesSRT 4155 and SRT4355 - ServicemanualMohamed MakiNo ratings yet

- Car Monitoring System Team IPA: Kirill Belyayev Amjad Chaudhry Arush Dhawan Aditya Kaundinya Bilal YousufiDocument42 pagesCar Monitoring System Team IPA: Kirill Belyayev Amjad Chaudhry Arush Dhawan Aditya Kaundinya Bilal YousufiSaleh AlsaqerNo ratings yet

- Daewoo DVG 6000DDocument12 pagesDaewoo DVG 6000DOssian Valera PinedaNo ratings yet

- Spock: Power Serial I/ODocument5 pagesSpock: Power Serial I/OSanyi Ocsai100% (2)

- LCD 2x16 Spec-29045Document30 pagesLCD 2x16 Spec-29045kerblaNo ratings yet

- WH1602W Tmi JTDocument29 pagesWH1602W Tmi JTscribe72No ratings yet

- Schematic DiagramDocument13 pagesSchematic DiagramSas WajiNo ratings yet

- TM 7043Document13 pagesTM 7043Radek KurekNo ratings yet

- 8085 Instruction SetDocument4 pages8085 Instruction SetZahidNo ratings yet

- 8085 Formula FYITDocument3 pages8085 Formula FYITJoe ChristyNo ratings yet

- Mk7a25p v06Document53 pagesMk7a25p v06אור מהללאל בן השםNo ratings yet

- Schem AnticDocument1 pageSchem Anticthanhv_25100% (1)

- Labx 1 SCHDocument2 pagesLabx 1 SCHercervantesNo ratings yet

- LAB-X1 SchematicDocument2 pagesLAB-X1 SchematicRenato MirandaNo ratings yet

- Schematics PDFDocument7 pagesSchematics PDFCristian GonzalezNo ratings yet

- Ak1 MB 1213aDocument30 pagesAk1 MB 1213aAshok JangraNo ratings yet

- 7-1 Overall Block DiagramDocument4 pages7-1 Overall Block DiagramCraig KalinowskiNo ratings yet

- Ecs 2uzDocument1 pageEcs 2uzjemalizNo ratings yet

- Cpu Logic DiagramDocument0 pagesCpu Logic DiagramMauricio RaúlNo ratings yet

- BB Top Level Vilbet 03-Jan-07 Tkoivusa 18-Aug-03 Dd-Mmm-Yy IljarvinDocument32 pagesBB Top Level Vilbet 03-Jan-07 Tkoivusa 18-Aug-03 Dd-Mmm-Yy IljarvinJuan Daniel Angeles AnguloNo ratings yet

- PSR-S700 S900 Lsi CDocument13 pagesPSR-S700 S900 Lsi CAdriano CamocardiNo ratings yet

- Propeller Clock at Mega 32Document1 pagePropeller Clock at Mega 32diego140bpm100% (2)

- Ecs 1VDDocument1 pageEcs 1VDMortada AlsonniNo ratings yet

- Pass DooorDocument1 pagePass DooorSHAHID_71No ratings yet

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- Interrupt Control: Serial I/O ControlDocument15 pagesInterrupt Control: Serial I/O ControlnagpalanishNo ratings yet

- Sony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICDocument36 pagesSony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICvideoson0% (1)

- AD7895Document1 pageAD7895M Namir HasanNo ratings yet

- 2Document7 pages2Socnho Kit100% (1)

- SchematicdjfcykhgdhydfgbDocument1 pageSchematicdjfcykhgdhydfgbKumar GorlaNo ratings yet

- Mach Ngly Sim300czDocument2 pagesMach Ngly Sim300czViet Bui QuocNo ratings yet

- MIPS Green CardDocument2 pagesMIPS Green Cardkokio787No ratings yet

- Cab LageDocument2 pagesCab LageSalah DahouathiNo ratings yet

- U6 U11B J3: BaudclkDocument2 pagesU6 U11B J3: BaudclkxxxdanielsssNo ratings yet

- 20065819114669071Document58 pages20065819114669071Andrei BistriceanuNo ratings yet

- 8255 Programmable Peripheral InterfaceDocument8 pages8255 Programmable Peripheral InterfacecrsarinNo ratings yet

- Week 8Document1 pageWeek 8zzzsamuraizzzNo ratings yet

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Luxury Car MagazineDocument44 pagesLuxury Car Magazinenalixor100% (5)

- Mansions of Madness Monster Reference v6 SerpentDocument2 pagesMansions of Madness Monster Reference v6 SerpentMartin Baxter100% (1)

- Table Tennis TerminologyDocument2 pagesTable Tennis TerminologyAngeline Joyce RamirezNo ratings yet

- Force and MotionDocument68 pagesForce and MotionKim Zairyl FernandezNo ratings yet

- National Club Golfer - July 2019 PDFDocument166 pagesNational Club Golfer - July 2019 PDFebt555No ratings yet

- GA Power Capsule For SBI Clerk Mains 2024 Current Affairs July To DecemberDocument229 pagesGA Power Capsule For SBI Clerk Mains 2024 Current Affairs July To Decemberbemiciv676No ratings yet

- Career Testing Services Pakistan: Government of Baluchistan Secondary Education DepartmentDocument33 pagesCareer Testing Services Pakistan: Government of Baluchistan Secondary Education DepartmentAsif MengalNo ratings yet

- 14264A Construction Mechanic Basic Chapters 11 PDFDocument44 pages14264A Construction Mechanic Basic Chapters 11 PDFAnonymous QiMB2lBCJLNo ratings yet

- Standard Pipe DataDocument15 pagesStandard Pipe DataSathish LingamNo ratings yet

- Cummins QSB6.7 119 KW (162 HP) at 2,200 RPM 108kW (147 HP) at 2,200 RPM 14,000 KG 2.5 M 129 KN 2,880 MMDocument2 pagesCummins QSB6.7 119 KW (162 HP) at 2,200 RPM 108kW (147 HP) at 2,200 RPM 14,000 KG 2.5 M 129 KN 2,880 MMAbo Achraf LaalawiNo ratings yet

- Audi History 80sDocument15 pagesAudi History 80sAlejandro Miniaci GuitarLoopsNo ratings yet

- Excel TestDocument29 pagesExcel TestDivya RaghuvanshiNo ratings yet

- 2021-05-21 Student Register of SponsorsDocument69 pages2021-05-21 Student Register of SponsorsAbdurrahman MassNo ratings yet

- The Complete Guide To Liwa DRAFT PDFDocument2 pagesThe Complete Guide To Liwa DRAFT PDFElle CruzabraNo ratings yet

- 0708Document35 pages0708pyoon1100% (1)

- Main Bearing CrankshaftDocument2 pagesMain Bearing CrankshaftJebrodNo ratings yet

- Escort F 15 Frana CraneDocument2 pagesEscort F 15 Frana CraneMusaifkhanNo ratings yet

- Intervertebral Disc ProlapseDocument81 pagesIntervertebral Disc ProlapsePriya PawarNo ratings yet

- Writing Practice For The Final ExamDocument4 pagesWriting Practice For The Final ExamJoaquin100% (5)

- Physical EducationDocument6 pagesPhysical EducationkartikNo ratings yet

- Indice EuropeusDocument65 pagesIndice EuropeuskrilinX0No ratings yet

- Spotlight On First Phonics 4 Flash CardDocument89 pagesSpotlight On First Phonics 4 Flash Cardteacher1100% (1)

- Booklet (04 05 2017)Document40 pagesBooklet (04 05 2017)karthi_kuttyNo ratings yet

- JAAA Qualification Trials - 2/27/2021 Jamaica College Results Girls 11-13 200 Meter Dash Class 4Document11 pagesJAAA Qualification Trials - 2/27/2021 Jamaica College Results Girls 11-13 200 Meter Dash Class 41k subs before quarantine endsNo ratings yet

- Nsco Type F PDFDocument4 pagesNsco Type F PDFantonNo ratings yet

- MEP Pupil Text 4Document5 pagesMEP Pupil Text 4Gloria García-MataNo ratings yet

- Wwe Champions Tier ListDocument1 pageWwe Champions Tier ListJosh Eisbrenner100% (1)

- Aggregate Spreaders - Product - HANTA MACHINERY Co.,LtdDocument2 pagesAggregate Spreaders - Product - HANTA MACHINERY Co.,Ltdihsan10082014ameliaNo ratings yet

Intel 8085 Reference Card

Intel 8085 Reference Card

Uploaded by

Niranjan NeruOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Intel 8085 Reference Card

Intel 8085 Reference Card

Uploaded by

Niranjan NeruCopyright:

Available Formats

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 28 29 2A 2B

NOP LXI B,d STAX B INX B INR B DCR B MVI B,b RLC [DSUB] * DAD B LDAX B DCX B INR C DCR C MVI C,b RRC [AHRL] LXI D,d STAX D INX D INR D DCR D MVI D,b RAL [RDEL]CY,V DAD D LDAX D DCX D INR E DCR E MVI E,b RAR RIM LXI H,d SHLD a INX H INR H DCR H MVI H,b DAA * [LDHI] DAD H LHLD a DCX H

2C 2D 2E 2F 30 31 32 33 34 35 36 37 38 39 3A 3B 3C 3D 3E 3F 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57

INR L DCR L MVI L,b CMA SIM LXI SP,d STA a INX SP INR M DCR M MVI M,b STC [LDSI] DAD SP LDA a DCX SP INR A DCR A MVI A,b CMC MOV B,B MOV B,C MOV B,D MOV B,E MOV B,H MOV B,L MOV B,M MOV B,A MOV C,B MOV C,C MOV C,D MOV C,E MOV C,H MOV C,L MOV C,M MOV C,A MOV D,B MOV D,C MOV D,D MOV D,E MOV D,H MOV D,L MOV D,M MOV D,A

58 59 5A 5B 5C 5D 5E 5F 60 61 62 63 64 65 66 67 68 69 6A 6B 6C 6D 6E 6F 70 71 72 73 74 75 76 77 78 79 7A 7B 7C 7D 7E 7F 80 81 82 83

MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV HLT MOV MOV MOV MOV MOV MOV MOV MOV MOV ADD ADD ADD ADD

E,B E,C E,D E,E E,H E,L E,M E,A H,B H,C H,D H,E H,H H,L H,M H,A L,B L,C L,D L,E L,H L,L L,M L,A M,B M,C M,D M,E M,H M,L M,A A,B A,C A,D A,E A,H A,L A,M A,A B * C * D * E *

83 84 85 86 87 88 89 8A 8B 8C 8D 8E 8F 90 91 92 93 94 95 96 97 98 99 9A 9B 9C 9D 9E 9F A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 AA AB AC AD AE

ADD ADD ADD ADD ADD ADC ADC ADC ADC ADC ADC ADC ADC SUB SUB SUB SUB SUB SUB SUB SUB SBB SBB SBB SBB SBB SBB SBB SBB ANA ANA ANA ANA ANA ANA ANA ANA XRA XRA XRA XRA XRA XRA XRA

E H L M A B C D E H L M A B C D E H L M A B C D E H L M A B C D E H L M A B C D E H L M

* * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * *

AF B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 BA BB BC BD BE BF C0 C1 C2 C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 DA

XRA A ORA B ORA C ORA D ORA E ORA H ORA L ORA M ORA A CMP B CMP C CMP D CMP E CMP H CMP L CMP M CMP A RNZ POP B JNZ a JMP a CNZ a PUSH B ADI b RST 0 RZ RET JZ a [RSTV] CZ a CALL a ACI b RST 1 RNC POP D JNC a OUT b CNC a PUSH D SUI b RST 2 RC [SHLX] JC a

* * * * * * * * * * * * * * * * *

DB DC DD DE DF E0 E1 E2 E3 E4 E5 E6 E7 E8 E9 EA EB EC ED EE EF F0 F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

b = byte data d = 16b data a = 16b address flags: * = affects all = carry only = all but carry

IN b CC a [JNUI] SBI b RST 3 RPO POP H JPO a XTHL CPO a PUSH H ANI b RST 4 RPE PCHL JPE a XCHG CPE a [LHLX] XRI b RST 5 RP POP PSW JP a DI CP a PUSH PSW ORI b RST 6 RM SPHL JM a EI CM a [JUI] CPI b RST 7

Data Transfer MOV rd,rs 4 MOV M,r 7 MOV r,M 7 XCHG 4 MVI r 7 MVI M 10 LXI x 10 Load/Store LDAX x 7 LDA 13 STAX x 7 SHLD 16 STA 13 Arith & Logic ADD r 4 ADD M 7 ADC r 4 ADC M 7 SUB r 4 SUB M 7 SBB r 4 SBB M 7 INR R 4 INR M 10 DCR r 4 DCR M 10 ANA r 4 ANA M 7 XRA r 4 XRA M 7 ORA r 4 ORA M 7

Instruction Timing (T States)

CMP r CMP M 4 7 16 bit DAD x INX x DCX x Rotate RLC RRC RAL RAR Immediate ADI ACI SUI SBI ANI XRI ORI CPI Specials DAA CMA STC CMC I/O OUT IN RIM SIM

10 6 6 4 4 4 4 7 7 7 7 7 7 7 7 4 4 4 4 10 10 4 4

Control DI EI NOP HLT Stack PUSH POP Branch RST x JMP Jx CALL Cx RET Rx T-State CPU f 8.0MHz 6.0 5.0 4.0 3.58 3.125 3.072 3.0 2.5 2.0 1.25 1.2 1.0 0.75

Accumulator Operations

4 4 4 5 12 10 12 10 7/10 18 9/18 10 6/12 Time tCYC 125nS 166.7 200 250 279 320 325.5 333.3 400 500 800 833.3 1000 1333 Instruction Code Function XRA A AF Clear A and Clear Carry CMA 2F Complement Accumulator ORA A B7 Clear Carry CMC 3F Complement Carry STC 37 Set Carry RLC 7 Rotate Left, MSB=CY RRC 0F Rotate Right, LSB=>CY RAL 17 Rotate Ledt Thru Carry RAR 1F Rotate Right Thru Carry After RIM: SID SID Ix.5 IE Mx.5 = = = = I7.5 I6.5 I5.5 Serial In Interrupt Interrupt Interrupt IE M7.5 M6.5 M5.5 Data Pending Enable Flag Masks for external lines

* *

Before SIM: SOD SOE --R7.5 MSE M7.5 M6.5 M5.5 SOD = Serial Out Data SOE = Serial Out Enable (enable SOD output) R7.5= Reset (clear) RST 7.5 Interrupt MSE = Mask Set Enable (1 to set new masks) Mx.5= New RSTx.5 Mask Setting (1 to enable) Note: RST5.5, RST6.5, RST7.5 are masked by default. Masks must be cleared before use. Visit http://saundby.com/ for more 8085 info.

Intel 8085 Reference Card

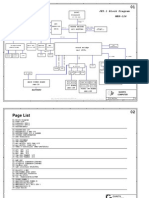

X1 X2 RESET OUT SOD SID TRAP RST 7.5 RST 6.5 RST 5.5 INTR /INTA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 VSS 1

Data Transfer Instruction Group

MOV A, A, A, A, A, A, A, A, B, B, B, B, B, B, B, B, C, C, C, C, C, C, C, C, D, D, D, D, D, D, D, D, A B C D E H L M A B C D E H L M A B C D E H L M A B C D E H L M 7F 78 79 7A 7B 7C 7D 7E 47 40 41 42 43 44 45 46 4F 48 49 4A 4B 4C 4D 4E 57 50 51 52 53 54 55 56 MOV E, E, E, E, E, E, E, E, H, H, H, H, H, H, H, H, L, L, L, L, L, L, L, L, M, M, M, M, M, M, M, A B C D E H L M A B C D E H L M A B C D E H L M A B C D E H L 5F 58 59 5A 5B 5C 5D 5E 67 60 61 62 63 64 65 66 6F 68 69 6A 6B 6C 6D 6E 77 70 71 72 73 73 75 MVI A, B, C, D, E, H, L, M, XCHG LXI B, d D, d H, d SP,d b b b b b b b b 3E 06 0E 16 1E 26 2E 36 EB 01 11 21 31

Arithmetic & Logical Instruction Group

ADD* A B C D E H L M ADC* A B C D E H L M SUB* A B C D E H L M SBB* A B C D E H L M 87 80 81 82 83 84 85 86 8F 88 89 8A 8B 8C 8D 8E 97 90 91 92 93 94 95 96 9F 98 99 9A 9B 9C 9D 9E INR A B C D E H L M DCR A B C D E H L M ANA* A B C D E H L M XRA* A B C D E H L M 3C 04 0C 14 1C 24 2C 34 3D 05 0D 15 1D 25 2D 35 A7 A0 A1 A2 A3 A4 A5 A6 AF A8 A9 AA AB AC AD AE ORA* A B C D E H L M CMP* A B C D E H L M 16 Bit DAD B D H SP INX B D H SP DCX B D H SP [DSUB]

Arith & Logic continued -->

Intel 8085

Vcc: 5.0V10% VIH: 2.0 Vcc+0.5V VIL: -0.5V0.8V VOH: 0.45V VOL: 2.4V Icc: 200mA tclk max: 2uS tclk min: 125320nS Icc and tclk vary by version.

VCC HOLD HLDA CLK OUT /RESET IN READY IO/M S1 /RD /WR ALE S0 A15 A14 A13 A12 A11 A10 A9 A8

B7 B0 B1 B2 B3 B4 B5 B6 BF B8 B9 BA BB BC BD BE 09 19 29 39 03 13 23 33 0B 1B 2B 3B [08]

Rotate RLC RRC RAL RAR [AHRL]

Arith & Logic

07 0F 17 1F [10]

MOV

MOV

saundby.com

MOV

MOV

Load/Store LDAX B 0A LDAX D 1A LHLD a 2A LDA a 3A [LHLX] [ED] STAX B STAX D SHLD a STA a [SHLX] 02 12 22 32 [D9]

Immediate ADI b C6 ACI b CE SUI b D6 SBI b DE ANI b E6 XRI b EE ORI b F6 CPI b FE [LDHI b][28] [LDSI b][38] Specials DAA* CMA STC CMC OUT IN RIM SIM Control DI EI NOP HLT b b 27 2F 37 3F D3 DB 20 30 F3 FB 00 76

PUSH B D H PSW POP B D H PSW* XTHL SPHL

Stack

C5 D5 E5 F5 C1 D1 E1 F1 E3 F9

I/O & Control

Register Organization

A(8) F(8) PSW(16) Flags S Z [UI] AC - P [V] C Sign Zero [UI] Aux Carry Parity [V] Carry B(8) D(8) H(8) Stack Pointer C(8) B/C(16) E(8) D/E(16) L(8) H/L(16) SP (16)

MOV

MOV

arguments:

b = byte data d = 16b data a = 16b address

Program Counter PC (16)

flags:

* = affects all = carry only = all but carry

Note: [ ]=Undocumented/80C85B only

Restart RST 0 C7 RST 1 CF RST 2 D7 RST 3 DF RST 4 E7 RST 5 EF RST 6 F7 RST 7 FF [RST V] [CB] Restart Vector RST 0 0000H RST 1 0008H RST 2 0010H RST 3 0018H RST 4 0020H TRAP 0024H RST 5 0028H RST 5.5 002CH RST 6 0030H RST 6.5 0034H RST 7 0038H RST 7.5 003CH

Branch

Jump JMP a JNZ a JZ a JNC a JC a JPO a JPE a JP a JM a PCHL [JNUI] [JUI] Call CALL CNZ CZ CNC CC CPO CPE CP CM a a a a a a a a a

Branch

C3 C2 CA D2 DA E2 EA F2 FA E9 [DD] [FD] CD C4 CC D4 DC E4 EC F4 FC C9 C0 C8 D0 D8 E0 E8 F0 F8

Return RET RNZ RZ RNC RC RPO RPE RP RM

Intel 8085 Reference Card

X1 X2 RESET OUT SOD SID TRAP RST 7.5 RST 6.5 RST 5.5 INTR /INTA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 VSS 1

Data Transfer Instruction Group

MOV A, A, A, A, A, A, A, A, B, B, B, B, B, B, B, B, C, C, C, C, C, C, C, C, D, D, D, D, D, D, D, D, A B C D E H L M A B C D E H L M A B C D E H L M A B C D E H L M

E H L M A B C D E H L M A B C D E H L M A B C D E H L M A B C D E H L M A B C D E H L M

* * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * *

Arithmetic & Logical Instruction Group

b b b b b b b b 3E 06 0E 16 1E 26 2E 36 EB 01 11 21 31 ADD* A B C D E H L M ADC* A B C D E H L M SUB* A B C D E H L M SBB* A B C D E H L M 87 80 81 82 83 84 85 86 8F 88 89 8A 8B 8C 8D 8E 97 90 91 92 93 94 95 96 9F 98 99 9A 9B 9C 9D 9E INR A B C D E H L M DCR A B C D E H L M ANA* A B C D E H L M XRA* A B C D E H L M 3C 04 0C 14 1C 24 2C 34 3D 05 0D 15 1D 25 2D 35 A7 A0 A1 A2 A3 A4 A5 A6 AF A8 A9 AA AB AC AD AE ORA* A B C D E H L M CMP* A B C D E H L M 16 Bit DAD B D H SP INX B D H SP DCX B D H SP [DSUB]

Arith & Logic continued -->

Intel 8085

Vcc: 5.0V10% VIH: 2.0 Vcc+0.5V VIL: -0.5V0.8V VOH: 0.45V VOL: 2.4V Icc: 200mA tclk max: 2uS tclk min: 125320nS Icc and tclk vary by version.

VCC HOLD HLDA CLK OUT /RESET IN READY IO/M S1 /RD /WR ALE S0 A15 A14 A13 A12 A11 A10 A9 A8

7F 78 79 7A 7B 7C 7D 7E 47 40 41 42 43 44 45 46 4F 48 49 4A 4B 4C 4D 4E 57 50 51 52 53 54 55 56

MOV

E, E, E, E, E, E, E, E, H, H, H, H, H, H, H, H, L, L, L, L, L, L, L, L, M, M, M, M, M, M, M,

A B C D E H L M A B C D E H L M A B C D E H L M A B C D E H L

5F 58 59 5A 5B 5C 5D 5E 67 60 61 62 63 64 65 66 6F 68 69 6A 6B 6C 6D 6E 77 70 71 72 73 73 75

MVI A, B, C, D, E, H, L, M, XCHG

B7 B0 B1 B2 B3 B4 B5 B6 BF B8 B9 BA BB BC BD BE 09 19 29 39 03 13 23 33 0B 1B 2B 3B [08]

Rotate RLC RRC RAL RAR [AHRL]

Arith & Logic

07 0F 17 1F [10]

MOV

MOV

LXI B, d D, d H, d SP,d

saundby.com

MOV

MOV

Load/Store LDAX B 0A LDAX D 1A LHLD a 2A LDA a 3A [LHLX] [ED] STAX B STAX D SHLD a STA a [SHLX] 02 12 22 32 [D9]

Immediate ADI b C6 ACI b CE SUI b D6 SBI b DE ANI b E6 XRI b EE ORI b F6 CPI b FE [LDHI b][28] [LDSI b][38] Specials DAA* CMA STC CMC OUT IN RIM SIM Control DI EI NOP HLT b b 27 2F 37 3F D3 DB 20 30 F3 FB 00 76

PUSH B D H PSW POP B D H PSW* XTHL SPHL

Stack

C5 D5 E5 F5 C1 D1 E1 F1 E3 F9

I/O & Control

Register Organization

A(8) F(8) PSW(16) Flags S Z [UI] AC - P [V] C Sign Zero [UI] Aux Carry Parity [V] Carry B(8) D(8) H(8) Stack Pointer C(8) B/C(16) E(8) D/E(16) L(8) H/L(16) SP (16)

MOV

MOV

arguments:

b = byte data d = 16b data a = 16b address

Program Counter PC (16)

flags:

* = affects all = carry only = all but carry

Note: [ ]=Undocumented/80C85B only

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 28 29 2A 2B NOP LXI B,d STAX B INX B INR B DCR B MVI B,b RLC [DSUB] * DAD B LDAX B DCX B INR C DCR C MVI C,b RRC [AHRL] LXI D,d STAX D INX D INR D DCR D MVI D,b RAL [RDEL]CY,V DAD D LDAX D DCX D INR E DCR E MVI E,b RAR RIM LXI H,d SHLD a INX H INR H DCR H MVI H,b DAA * [LDHI] DAD H LHLD a DCX H 2C 2D 2E 2F 30 31 32 33 34 35 36 37 38 39 3A 3B 3C 3D 3E 3F 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57 INR L DCR L MVI L,b CMA SIM LXI SP,d STA a INX SP INR M DCR M MVI M,b STC [LDSI] DAD SP LDA a DCX SP INR A DCR A MVI A,b CMC MOV B,B MOV B,C MOV B,D MOV B,E MOV B,H MOV B,L MOV B,M MOV B,A MOV C,B MOV C,C MOV C,D MOV C,E MOV C,H MOV C,L MOV C,M MOV C,A MOV D,B MOV D,C MOV D,D MOV D,E MOV D,H MOV D,L MOV D,M MOV D,A 58 59 5A 5B 5C 5D 5E 5F 60 61 62 63 64 65 66 67 68 69 6A 6B 6C 6D 6E 6F 70 71 72 73 74 75 76 77 78 79 7A 7B 7C 7D 7E 7F 80 81 82 83 MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV HLT MOV MOV MOV MOV MOV MOV MOV MOV MOV ADD ADD ADD ADD E,B E,C E,D E,E E,H E,L E,M E,A H,B H,C H,D H,E H,H H,L H,M H,A L,B L,C L,D L,E L,H L,L L,M L,A M,B M,C M,D M,E M,H M,L M,A A,B A,C A,D A,E A,H A,L A,M A,A B * C * D * E * 83 84 85 86 87 88 89 8A 8B 8C 8D 8E 8F 90 91 92 93 94 95 96 97 98 99 9A 9B 9C 9D 9E 9F A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 AA AB AC AD AE

Restart RST 0 C7 RST 1 CF RST 2 D7 RST 3 DF RST 4 E7 RST 5 EF RST 6 F7 RST 7 FF [RST V] [CB] Restart Vector RST 0 0000H RST 1 0008H RST 2 0010H RST 3 0018H RST 4 0020H TRAP 0024H RST 5 0028H RST 5.5 002CH RST 6 0030H RST 6.5 0034H RST 7 0038H RST 7.5 003CH

Branch

Jump JMP a JNZ a JZ a JNC a JC a JPO a JPE a JP a JM a PCHL [JNUI] [JUI] Call CALL CNZ CZ CNC CC CPO CPE CP CM a a a a a a a a a

Branch

C3 C2 CA D2 DA E2 EA F2 FA E9 [DD] [FD] CD C4 CC D4 DC E4 EC F4 FC C9 C0 C8 D0 D8 E0 E8 F0 F8

Return RET RNZ RZ RNC RC RPO RPE RP RM

ADD ADD ADD ADD ADD ADC ADC ADC ADC ADC ADC ADC ADC SUB SUB SUB SUB SUB SUB SUB SUB SBB SBB SBB SBB SBB SBB SBB SBB ANA ANA ANA ANA ANA ANA ANA ANA XRA XRA XRA XRA XRA XRA XRA

AF B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 BA BB BC BD BE BF C0 C1 C2 C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 DA

XRA A ORA B ORA C ORA D ORA E ORA H ORA L ORA M ORA A CMP B CMP C CMP D CMP E CMP H CMP L CMP M CMP A RNZ POP B JNZ a JMP a CNZ a PUSH B ADI b RST 0 RZ RET JZ a [RSTV] CZ a CALL a ACI b RST 1 RNC POP D JNC a OUT b CNC a PUSH D SUI b RST 2 RC [SHLX] JC a

* * * * * * * * * * * * * * * * *

DB DC DD DE DF E0 E1 E2 E3 E4 E5 E6 E7 E8 E9 EA EB EC ED EE EF F0 F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

b = byte data d = 16b data a = 16b address flags: * = affects all = carry only = all but carry

IN b CC a [JNUI] SBI b RST 3 RPO POP H JPO a XTHL CPO a PUSH H ANI b RST 4 RPE PCHL JPE a XCHG CPE a [LHLX] XRI b RST 5 RP POP PSW JP a DI CP a PUSH PSW ORI b RST 6 RM SPHL JM a EI CM a [JUI] CPI b RST 7

Data Transfer MOV rd,rs 4 MOV M,r 7 MOV r,M 7 XCHG 4 MVI r 7 MVI M 10 LXI x 10 Load/Store LDAX x 7 LDA 13 STAX x 7 SHLD 16 STA 13 Arith & Logic ADD r 4 ADD M 7 ADC r 4 ADC M 7 SUB r 4 SUB M 7 SBB r 4 SBB M 7 INR R 4 INR M 10 DCR r 4 DCR M 10 ANA r 4 ANA M 7 XRA r 4 XRA M 7 ORA r 4 ORA M 7

Instruction Timing (T States)

CMP r CMP M 4 7 16 bit DAD x INX x DCX x Rotate RLC RRC RAL RAR Immediate ADI ACI SUI SBI ANI XRI ORI CPI Specials DAA CMA STC CMC I/O OUT IN RIM SIM

10 6 6 4 4 4 4 7 7 7 7 7 7 7 7 4 4 4 4 10 10 4 4

Control DI EI NOP HLT Stack PUSH POP Branch RST x JMP Jx CALL Cx RET Rx T-State CPU f 8.0MHz 6.0 5.0 4.0 3.58 3.125 3.072 3.0 2.5 2.0 1.25 1.2 1.0 0.75

Accumulator Operations

4 4 4 5 12 10 12 10 7/10 18 9/18 10 6/12 Time tCYC 125nS 166.7 200 250 279 320 325.5 333.3 400 500 800 833.3 1000 1333 Instruction Code Function XRA A AF Clear A and Clear Carry CMA 2F Complement Accumulator ORA A B7 Clear Carry CMC 3F Complement Carry STC 37 Set Carry RLC 7 Rotate Left, MSB=CY RRC 0F Rotate Right, LSB=>CY RAL 17 Rotate Ledt Thru Carry RAR 1F Rotate Right Thru Carry After RIM: SID SID Ix.5 IE Mx.5 = = = = I7.5 I6.5 I5.5 Serial In Interrupt Interrupt Interrupt IE M7.5 M6.5 M5.5 Data Pending Enable Flag Masks for external lines

* *

Before SIM: SOD SOE --R7.5 MSE M7.5 M6.5 M5.5 SOD = Serial Out Data SOE = Serial Out Enable (enable SOD output) R7.5= Reset (clear) RST 7.5 Interrupt MSE = Mask Set Enable (1 to set new masks) Mx.5= New RSTx.5 Mask Setting (1 to enable) Note: RST5.5, RST6.5, RST7.5 are masked by default. Masks must be cleared before use.

Visit http://saundby.com/ for more 8085 info.

You might also like

- Behringer Xenyx 1622fx SchematicsDocument12 pagesBehringer Xenyx 1622fx SchematicsJoaquim Dos Santos Veras Maia100% (1)

- 8085 OpcodesDocument3 pages8085 OpcodesSwapna PriyaNo ratings yet

- D&D 5 Ext Mini GamesDocument4 pagesD&D 5 Ext Mini GamesLucasNo ratings yet

- Resistance Training Program DesignDocument30 pagesResistance Training Program DesignKostas LiougkosNo ratings yet

- Z80PCRDDocument2 pagesZ80PCRDTấn Phát TrầnNo ratings yet

- Z80PCRDDocument2 pagesZ80PCRDKhánh NguyễnNo ratings yet

- Machine CodesDocument5 pagesMachine CodesSarah ShermanNo ratings yet

- Hex CodeDocument1 pageHex CodeShaorya Vijay0% (1)

- Instruction Set of 8085Document2 pagesInstruction Set of 8085mmasliniaNo ratings yet

- Esque MaDocument1 pageEsque MaAlexander PerdomoNo ratings yet

- SCH TPM 4250 6250 8250 30-01-08 PDFDocument22 pagesSCH TPM 4250 6250 8250 30-01-08 PDFJosé Benavides0% (2)

- Bahan Kuliah 8 Tabel Instruksi Set 8085Document9 pagesBahan Kuliah 8 Tabel Instruksi Set 8085FaJriNo ratings yet

- 8086 NotesDocument10 pages8086 Notesmiker00lzNo ratings yet

- W375 L3 V1.2 SchemDocument3 pagesW375 L3 V1.2 SchemAdrian PeterNo ratings yet

- x03/x04/x06 Version 2.40-2.4x: Pcu Command SummaryDocument6 pagesx03/x04/x06 Version 2.40-2.4x: Pcu Command Summaryemorillo2No ratings yet

- Sony Vaio Mbx-126 - Quanta Je5.1Document36 pagesSony Vaio Mbx-126 - Quanta Je5.1nunoq171No ratings yet

- SRT 4155 and SRT4355 - ServicemanualDocument40 pagesSRT 4155 and SRT4355 - ServicemanualMohamed MakiNo ratings yet

- Car Monitoring System Team IPA: Kirill Belyayev Amjad Chaudhry Arush Dhawan Aditya Kaundinya Bilal YousufiDocument42 pagesCar Monitoring System Team IPA: Kirill Belyayev Amjad Chaudhry Arush Dhawan Aditya Kaundinya Bilal YousufiSaleh AlsaqerNo ratings yet

- Daewoo DVG 6000DDocument12 pagesDaewoo DVG 6000DOssian Valera PinedaNo ratings yet

- Spock: Power Serial I/ODocument5 pagesSpock: Power Serial I/OSanyi Ocsai100% (2)

- LCD 2x16 Spec-29045Document30 pagesLCD 2x16 Spec-29045kerblaNo ratings yet

- WH1602W Tmi JTDocument29 pagesWH1602W Tmi JTscribe72No ratings yet

- Schematic DiagramDocument13 pagesSchematic DiagramSas WajiNo ratings yet

- TM 7043Document13 pagesTM 7043Radek KurekNo ratings yet

- 8085 Instruction SetDocument4 pages8085 Instruction SetZahidNo ratings yet

- 8085 Formula FYITDocument3 pages8085 Formula FYITJoe ChristyNo ratings yet

- Mk7a25p v06Document53 pagesMk7a25p v06אור מהללאל בן השםNo ratings yet

- Schem AnticDocument1 pageSchem Anticthanhv_25100% (1)

- Labx 1 SCHDocument2 pagesLabx 1 SCHercervantesNo ratings yet

- LAB-X1 SchematicDocument2 pagesLAB-X1 SchematicRenato MirandaNo ratings yet

- Schematics PDFDocument7 pagesSchematics PDFCristian GonzalezNo ratings yet

- Ak1 MB 1213aDocument30 pagesAk1 MB 1213aAshok JangraNo ratings yet

- 7-1 Overall Block DiagramDocument4 pages7-1 Overall Block DiagramCraig KalinowskiNo ratings yet

- Ecs 2uzDocument1 pageEcs 2uzjemalizNo ratings yet

- Cpu Logic DiagramDocument0 pagesCpu Logic DiagramMauricio RaúlNo ratings yet

- BB Top Level Vilbet 03-Jan-07 Tkoivusa 18-Aug-03 Dd-Mmm-Yy IljarvinDocument32 pagesBB Top Level Vilbet 03-Jan-07 Tkoivusa 18-Aug-03 Dd-Mmm-Yy IljarvinJuan Daniel Angeles AnguloNo ratings yet

- PSR-S700 S900 Lsi CDocument13 pagesPSR-S700 S900 Lsi CAdriano CamocardiNo ratings yet

- Propeller Clock at Mega 32Document1 pagePropeller Clock at Mega 32diego140bpm100% (2)

- Ecs 1VDDocument1 pageEcs 1VDMortada AlsonniNo ratings yet

- Pass DooorDocument1 pagePass DooorSHAHID_71No ratings yet

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- Interrupt Control: Serial I/O ControlDocument15 pagesInterrupt Control: Serial I/O ControlnagpalanishNo ratings yet

- Sony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICDocument36 pagesSony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICvideoson0% (1)

- AD7895Document1 pageAD7895M Namir HasanNo ratings yet

- 2Document7 pages2Socnho Kit100% (1)

- SchematicdjfcykhgdhydfgbDocument1 pageSchematicdjfcykhgdhydfgbKumar GorlaNo ratings yet

- Mach Ngly Sim300czDocument2 pagesMach Ngly Sim300czViet Bui QuocNo ratings yet

- MIPS Green CardDocument2 pagesMIPS Green Cardkokio787No ratings yet

- Cab LageDocument2 pagesCab LageSalah DahouathiNo ratings yet

- U6 U11B J3: BaudclkDocument2 pagesU6 U11B J3: BaudclkxxxdanielsssNo ratings yet

- 20065819114669071Document58 pages20065819114669071Andrei BistriceanuNo ratings yet

- 8255 Programmable Peripheral InterfaceDocument8 pages8255 Programmable Peripheral InterfacecrsarinNo ratings yet

- Week 8Document1 pageWeek 8zzzsamuraizzzNo ratings yet

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Luxury Car MagazineDocument44 pagesLuxury Car Magazinenalixor100% (5)

- Mansions of Madness Monster Reference v6 SerpentDocument2 pagesMansions of Madness Monster Reference v6 SerpentMartin Baxter100% (1)

- Table Tennis TerminologyDocument2 pagesTable Tennis TerminologyAngeline Joyce RamirezNo ratings yet

- Force and MotionDocument68 pagesForce and MotionKim Zairyl FernandezNo ratings yet

- National Club Golfer - July 2019 PDFDocument166 pagesNational Club Golfer - July 2019 PDFebt555No ratings yet

- GA Power Capsule For SBI Clerk Mains 2024 Current Affairs July To DecemberDocument229 pagesGA Power Capsule For SBI Clerk Mains 2024 Current Affairs July To Decemberbemiciv676No ratings yet

- Career Testing Services Pakistan: Government of Baluchistan Secondary Education DepartmentDocument33 pagesCareer Testing Services Pakistan: Government of Baluchistan Secondary Education DepartmentAsif MengalNo ratings yet

- 14264A Construction Mechanic Basic Chapters 11 PDFDocument44 pages14264A Construction Mechanic Basic Chapters 11 PDFAnonymous QiMB2lBCJLNo ratings yet

- Standard Pipe DataDocument15 pagesStandard Pipe DataSathish LingamNo ratings yet

- Cummins QSB6.7 119 KW (162 HP) at 2,200 RPM 108kW (147 HP) at 2,200 RPM 14,000 KG 2.5 M 129 KN 2,880 MMDocument2 pagesCummins QSB6.7 119 KW (162 HP) at 2,200 RPM 108kW (147 HP) at 2,200 RPM 14,000 KG 2.5 M 129 KN 2,880 MMAbo Achraf LaalawiNo ratings yet

- Audi History 80sDocument15 pagesAudi History 80sAlejandro Miniaci GuitarLoopsNo ratings yet

- Excel TestDocument29 pagesExcel TestDivya RaghuvanshiNo ratings yet

- 2021-05-21 Student Register of SponsorsDocument69 pages2021-05-21 Student Register of SponsorsAbdurrahman MassNo ratings yet

- The Complete Guide To Liwa DRAFT PDFDocument2 pagesThe Complete Guide To Liwa DRAFT PDFElle CruzabraNo ratings yet

- 0708Document35 pages0708pyoon1100% (1)

- Main Bearing CrankshaftDocument2 pagesMain Bearing CrankshaftJebrodNo ratings yet

- Escort F 15 Frana CraneDocument2 pagesEscort F 15 Frana CraneMusaifkhanNo ratings yet

- Intervertebral Disc ProlapseDocument81 pagesIntervertebral Disc ProlapsePriya PawarNo ratings yet

- Writing Practice For The Final ExamDocument4 pagesWriting Practice For The Final ExamJoaquin100% (5)

- Physical EducationDocument6 pagesPhysical EducationkartikNo ratings yet

- Indice EuropeusDocument65 pagesIndice EuropeuskrilinX0No ratings yet

- Spotlight On First Phonics 4 Flash CardDocument89 pagesSpotlight On First Phonics 4 Flash Cardteacher1100% (1)

- Booklet (04 05 2017)Document40 pagesBooklet (04 05 2017)karthi_kuttyNo ratings yet

- JAAA Qualification Trials - 2/27/2021 Jamaica College Results Girls 11-13 200 Meter Dash Class 4Document11 pagesJAAA Qualification Trials - 2/27/2021 Jamaica College Results Girls 11-13 200 Meter Dash Class 41k subs before quarantine endsNo ratings yet

- Nsco Type F PDFDocument4 pagesNsco Type F PDFantonNo ratings yet

- MEP Pupil Text 4Document5 pagesMEP Pupil Text 4Gloria García-MataNo ratings yet

- Wwe Champions Tier ListDocument1 pageWwe Champions Tier ListJosh Eisbrenner100% (1)

- Aggregate Spreaders - Product - HANTA MACHINERY Co.,LtdDocument2 pagesAggregate Spreaders - Product - HANTA MACHINERY Co.,Ltdihsan10082014ameliaNo ratings yet