Professional Documents

Culture Documents

Cy2 Fpga Starter Board Schematic

Cy2 Fpga Starter Board Schematic

Uploaded by

odiliovieirafilhoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cy2 Fpga Starter Board Schematic

Cy2 Fpga Starter Board Schematic

Uploaded by

odiliovieirafilhoCopyright:

Available Formats

5

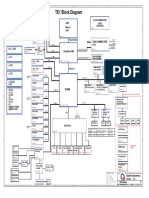

Altera Cyclone II FPGA Starter Board

D

SCHEMATIC

TOP AUDIO DISPLAY EP2C20 INPUT MEMORY POWER BLASTER

CONTENT

COVER PAGE , TOP WM8731 VGA , 7SEGMENT ,LED EP2C20 BANK1..BANK8 , POWER , CONFIG CLOCK , PS2 , RS232 , KEY , SWITCH , CONNECT SRAM , DRAM , FLASH , SD CARD POWER USB BLASTER

PAGE

01 04 05 08 13 18 20 21 ~ ~ ~ ~ ~ ~ ~ ~ 03 04 07 12 17 19 20 21

Title Altera Cyclone II Starter Board Size B Date:

5 4 3 2

Document Number COVER PAGE Tuesday, October 03, 2006 Sheet

1

Rev 1.1A 1 of 21

DC 7.5V

USB BLASTER

LINE LINE MIC IN OUT IN

VGA OUTPUT

RS232

PS2 KEYBORAD

WM8731 FT245

4BIT RGB GPIO_0 GPIO_1

M3128

C C

EP2C20

EPCS4

SD CARD

SDRAM

B

SRAM

FLASH

B

EXT CLK HEX3 HEX2 HEX1 HEX0

LED17

LED16

LED15

LED14

LED13

LED12

LED11 KEY0

KEY3

KEY2

KEY1

LED10

LED9

LED8

LED7

LED6

LED5

LED4

LED3

LED2

LED1

LED0

SW9

SW8

SW7

SW6

SW5

SW4

SW3

SW2

SW1

SW0

Title Altera Cyclone II Starter Board Size B Date: Document Number PLACEMENT Tuesday, October 03, 2006 Sheet

1

Rev 1.1A 2 of 21

EP2S35 AUDIO AUD_BCLK AUD_DACDAT AUD_ADCLRCK AUD_DACLRCK

D

EP2C20

PAGE 4 AUD_ADCDAT AUD_ADCDAT AUD_ADCDAT AUD_BCLK AUD_DACDAT AUD_ADCLRCK AUD_DACLRCK I2C_SDAT I2C_SCLK AUD_XCK AUD_ADCDAT AUD_BCLK AUD_DACDAT AUD_ADCLRCK AUD_DACLRCK I2C_SDAT I2C_SCLK AUD_XCK HEX0_D[0..6] HEX1_D[0..6] HEX2_D[0..6] HEX3_D[0..6] VGA_R[0..3] VGA_G[0..3] VGA_B[0..3] VGA_VSYNC VGA_HSYNC LED[0..17] UART_RXD UART_TXD 27MHZ 50MHZ EXT_CLOCK PS2_DAT PS2_CLK KEY[0..3] SW[0..2] SW[3..6] SW[7..9] GPIO_B[0..71] 24MHZ DATA0 DCLK ASDO NCSO NCE NCONFIG CONF_DONE NSTATUS TCK TDI TDO TMS LINK_D0 LINK_D1 LINK_D2 LINK_D3 24MHZ DATA0 DCLK ASDO NCSO NCE NCONFIG CONF_DONE NSTATUS TCK TDI TDO TMS LINK_D0 LINK_D1 LINK_D2 LINK_D3 DATA0

D

AUD_BCLK AUD_DACDAT AUD_ADCLRCK AUD_DACLRCK I2C_SCLK AUD_XCK

PWR

PAGE 20

I2C_SCLK AUD_XCK

I2C_SDAT

I2C_SDAT

DISPLAY HEX0_D[0..6] HEX1_D[0..6] HEX2_D[0..6] HEX3_D[0..6] VGA_R[0..3] VGA_G[0..3] VGA_B[0..3] VGA_VSYNC VGA_HSYNC LED[0..17]

C

PAGE 5-6

HEX0_D[0..6] HEX1_D[0..6] HEX2_D[0..6] HEX3_D[0..6] VGA_R[0..3] VGA_G[0..3] VGA_B[0..3] VGA_VSYNC VGA_HSYNC LED[0..17]

HEX0_D[0..6] HEX1_D[0..6] HEX2_D[0..6] HEX3_D[0..6] VGA_R[0..3] VGA_G[0..3] VGA_B[0..3] VGA_VSYNC VGA_HSYNC LED[0..17]

USB BLASTER DATA0

PAGE 21 24MHZ DCLK ASDO NCSO NCE 24MHZ DCLK ASDO NCSO NCE NCONFIG CONF_DONE NSTATUS TCK TDI TMS LINK_D0 LINK_D1 LINK_D2

TDO

TDO

NCONFIG CONF_DONE NSTATUS TCK TDI TMS LINK_D0 LINK_D1 LINK_D2

UART_RXD UART_TXD 27MHZ 50MHZ EXT_CLOCK

INPUT UART_TXD PS2_CLK PS2_DAT GPIO_B[0..35] GPIO_B[36..71] UART_TXD PS2_CLK PS2_DAT GPIO_B[0..35] GPIO_B[36..71]

IN/OUT UART_RXD 27MHZ 50MHZ EXT_CLOCK KEY[0..3] SW[0..9] UART_RXD 27MHZ 50MHZ EXT_CLOCK KEY[0..3] SW[0..9] PS2_DAT PS2_CLK KEY[0..3] SW[0..2] SW[3..6] SW[7..9] GPIO_B[0..71]

LINK_D3

LINK_D3

MEMORY

B

PAGE 18-19

FLASH_D[0..7] FLASH_RESET FLASH_WE FLASH_CE FLASH_OE FLASH_A[0..21] DRAM_D[0..15] DRAM_CLK DRAM_CKE DRAM_CS DRAM_WE DRAM_CAS DRAM_RAS DRAM_LDQM DRAM_UDQM DRAM_BA0 DRAM_BA1 DRAM_A[0..11] SRAM_D[0..15] SRAM_WE SRAM_CE SRAM_OE SRAM_LB SRAM_UB SRAM_A[0..17] SD_DAT SD_CLK SD_CMD SD_DAT3

FLASH_RESET FLASH_WE FLASH_CE FLASH_OE FLASH_A[0..21] DRAM_CLK DRAM_CKE DRAM_CS DRAM_WE DRAM_CAS DRAM_RAS DRAM_LDQM DRAM_UDQM DRAM_BA0 DRAM_BA1 DRAM_A[0..11] SRAM_WE SRAM_CE SRAM_OE SRAM_LB SRAM_UB SRAM_A[0..17]

FLASH_D[0..7] FLASH_RESET FLASH_WE FLASH_CE FLASH_OE FLASH_A[0..21] DRAM_D[0..15] DRAM_CLK DRAM_CKE DRAM_CS DRAM_WE DRAM_CAS DRAM_RAS DRAM_LDQM DRAM_UDQM DRAM_BA0 DRAM_BA1 DRAM_A[0..11] SRAM_D[0..15] SRAM_WE SRAM_CE SRAM_OE SRAM_LB SRAM_UB SRAM_A[0..17] SD_DAT SD_CLK SD_CMD SD_DAT3

FLASH_RESET FLASH_WE FLASH_CE FLASH_OE FLASH_A[0..21] DRAM_CLK DRAM_CKE DRAM_CS DRAM_WE DRAM_CAS DRAM_RAS DRAM_LDQM DRAM_UDQM DRAM_BA0 DRAM_BA1 DRAM_A[0..11] SRAM_WE SRAM_CE SRAM_OE SRAM_LB SRAM_UB SRAM_A[0..17] SD_CLK SD_CMD SD_DAT3

FLASH_D[0..7]

FLASH_D[0..7]

DRAM_D[0..15]

DRAM_D[0..15]

SRAM_D[0..15]

SRAM_D[0..15]

SD_CLK SD_CMD SD_DAT3

SD_DAT

SD_DAT Title Altera Cyclone II Starter Board Size B Date: Document Number TOP LEVEL Tuesday, October 03, 2006 Sheet

1

Rev 1.1A 3 of 21

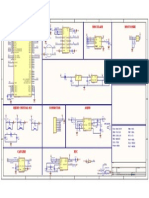

J2 VCC33 R2

D

LINEIN

VCC33 R3 2K

C1 1U C2 R4 4.7K 1U R5 4.7K R6 4.7K AGND AGND AGND J1 R7 330 C3 R8 TC21 MBIAS VMID AGND AVDD ROUT LOUT HPGND 21 20 19 18 17 16 15 100U/6V C5 A_VCC33 1000P R9 47K J3 AGND AGND AGND LINEOUT AGND 680 1U NCL R NCR L GND MICIN NCL R NCR L GND 5 2 4 1 3 R1 4.7K

2K I2C_SCLK I2C_SDAT

I2C ADDRESS READ IS 0x34 I2C ADDRESS WRITE IS 0x35

I2C_SDAT I2C_SCLK

SCLK SDIN CSB MODE LLINEIN RLINEIN MICIN

5 2 4 1 3

U1

28 27 26 25 24 23 22

A_VCC33

DACDAT DACLRCK ADCDAT ADCLRCK HPVDD LHPOUT RHPOUT

1 2 3 4 5 6 7

8 9 10 11 12 13 14

TC22 100U/6V AUD_XCK AUD_BCLK AUD_DACDAT AUD_DACLRCK AUD_ADCDAT AUD_ADCLRCK A_VCC33 TC23 100U/6V A_VCC33 R10 47K BC1 R12 0 AGND AGND Title Altera Cyclone II Starter Board Size A Date:

5 4 3

5 2 4 1 3

NCL R NCR L GND

XTI/MCLK XTO DCVDD DGND DBVDD CLKOUT BCLK

WM8731

AGND

R11 47K

BC2 0.1U

BC3 0.1U

BC4 AGND AGND 0.1U

A

0.1U

Document Number AUDIO Tuesday, October 03, 2006

2

Rev 1.1A Sheet 4

1

of

21

RN1 J4

D

6 11 1

10 15 5

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 VGA

R G B GND RG BG GG GND HS VS

5 6 7 8 2K RN2 1 2 3 4 1K RN3 5 6 7 8

4 3 2 1

VGA_R0 VGA_R1 VGA_R2 VGA_R3

8 7 6 5

17

16

4 3 2 1 2K RN4

VGA_G0 VGA_G1 VGA_G2 VGA_G3

G 1 2 3 4

8 7 6 5 1K

RN5 5 6 7 8 B 1 2 3 4 1K H V R13 R14 120 120 VGA_HSYNC VGA_VSYNC 2K RN6 8 7 6 5 4 3 2 1 VGA_B0 VGA_B1 VGA_B2 VGA_B3

VGA_R[0..3] VGA_G[0..3] VGA_B[0..3] VGA_HSYNC VGA_VSYNC

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number VGA Tuesday, October 03, 2006

2

Rev 1.1A Sheet 5

1

of

21

HEX0_D0 HEX0_D1 HEX0_D2 HEX0_D3

D

1 2 3 4 RN7 1K

8 7 6 5

A0 B0 C0 D0

HEX0_D[0..6] HEX1_D[0..6] HEX2_D[0..6] HEX3_D[0..6]

D

HEX0_D4 HEX0_D5 HEX0_D6 HEX1_D0

1 2 3 4 RN8 1K

8 7 6 5

E0 F0 G0 A1 A0 B0 C0 D0

HEX0 10 A 9 B 8 C 5 D 4 E E0 F0 G0 2 F 3 G 7 DP 7Segment Display 1 6 E1 F1 G1 VCC33 A1 B1 C1 D1

HEX1 10 A 9 B 8 C 5 D 4 E 2 F 3 G 7 DP 7Segment Display

C

VCC33

HEX1_D1 HEX1_D2 HEX1_D3 HEX1_D4

1 2 3 4 RN9 1K

8 7 6 5

B1 C1 D1 E1

1 6

HEX1_D5 HEX1_D6 HEX2_D0 HEX2_D1

1 2 3 4 RN10 1K

8 7 6 5

F1 G1 A2 B2

HEX2_D2 HEX2_D3 HEX2_D4 HEX2_D5

1 2 3 4 RN11 1K

8 7 6 5

C2 D2 E2 F2

HEX2 10 A A2 B2 C2 D2 9 B 8 C 5 D 4 E E2 F2 G2 2 F 3 G 7 DP 7Segment Display 1 6 E3 F3 G3 VCC33 A3 B3 C3 D3

HEX3 10 A 9 B 8 C 5 D 4 E 2 F 3 G 7 DP 7Segment Display 1 6

B

VCC33

HEX2_D6 HEX3_D0 HEX3_D1 HEX3_D2

1 2 3 4 RN12 1K

8 7 6 5

G2 A3 B3 C3

HEX3_D3 HEX3_D4 HEX3_D5 HEX3_D6

1 2 3 4 RN13 1K

8 7 6 5

D3 E3 F3 G3

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number 7 SEGMENT Tuesday, October 03, 2006

2

Rev 1.1A Sheet 6

1

of

21

LEDR0 LED[0..17] RN15 LED0 LED1 LED2 LED3 1 2 3 4 330 8 7 6 5 LEDR1 LEDR2 LEDR3

LEDR LEDR LEDR LEDR

LEDR4 RN16 LED4 LED5 LED6 LED7 1 2 3 4 330 8 7 6 5 LEDR5 LEDR6 LEDR7

LEDR LEDR LEDR LEDR

C

RN17 LED8 LED9 1 2 3 4 330 RN18 LED10 LED11 LED12 LED13 1 2 3 4 330 8 7 6 5 8 7 6 5

LEDR8 LEDR9

LEDR LEDR

LEDG0 LEDG1 LEDG2 LEDG3

LEDG LEDG LEDG LEDG

B

LEDG4 RN19 LED14 LED15 LED16 LED17

A

LEDG LEDG LEDG LEDG Title Altera Cyclone II Starter Board Size A Date: Document Number LED Tuesday, October 03, 2006

2

LEDG5 8 7 6 5 LEDG6 LEDG7

1 2 3 4 330

Rev 1.1A Sheet 7

1

of

21

DRAM_D[0..15] DRAM_A[0..11] SW[7..9]

U2A

HEX0_D[0..6] HEX1_D[0..6] HEX2_D[0..6] HEX3_D[0..6] U2B HEX0_D0 HEX0_D1 HEX0_D2 HEX0_D3 HEX0_D4 HEX0_D5 HEX0_D6 HEX1_D0 HEX1_D1 HEX1_D2 HEX1_D3 HEX1_D4 HEX1_D5 HEX1_D6 HEX2_D0 HEX2_D1

DRAM_A3 DRAM_A2 DRAM_A0 DRAM_A10 DRAM_D7 DRAM_D6 DRAM_D5 DRAM_D4 DRAM_CS DRAM_RAS DRAM_D3 DRAM_D2 DRAM_A4 DRAM_A5 DRAM_D1 DRAM_D0 DRAM_D15 DRAM_D14 DRAM_D13 DRAM_D12 DRAM_A6 DRAM_A7 DRAM_LDQM DRAM_WE DRAM_A9 DRAM_CKE DRAM_D11 DRAM_D10 DRAM_D9 DRAM_D8 DRAM_UDQM

Y4 Y3 W4 W3 Y2 Y1 W2 W1 T6 T5 V2 V1 R6 R5 U2 U1 T2 T1 R2 R1 P6 P5 R7 R8 N4 N3 P2 P1 N2 N1 M6 M5

LVDS0n LVDS0p LVDS1n LVDS1p LVDS2n LVDS2p LVDS3n LVDS3p LVDS4n LVDS4p LVDS5n LVDS5p LVDS6n LVDS6p LVDS7n LVDS7p LVDS8n LVDS8p LVDS9n LVDS9p LVDS10n LVDS10p LVDS11n LVDS11p LVDS12n LVDS12p LVDS13n LVDS13p LVDS14n LVDS14p LVDS15n LVDS15p

J2 J1 H2 H1 F2 F1 E2 E1 H6 H5 H4 G3 D2 D1 G5 G6 C2 C1 E4 E3 D4 D3

BANK1

N6 T3 W5 P3 U3 M2 M1 V4 U4 DRAM_A11 DRAM_CAS DRAM_A1 DRAM_A8 DRAM_BA0 SW7 SW8 DRAM_BA1 DRAM_CLK

LVDS16n LVDS16p LVDS17n LVDS17p LVDS18n LVDS18p LVDS19n LVDS19p LVDS20n LVDS20p LVDS21n LVDS21p LVDS22n LVDS22p LVDS23n LVDS23p LVDS24n LVDS24p LVDS25n LVDS25p LVDS26n LVDS26p

IO1_0 IO1_1 IO1_2 VREFB1N0 VREFB1N1 CLK3/LVDSCLK1n CLK2/LVDSCLK1p PLL1_OUTn PLL1_OUTp

HEX2_D2 HEX2_D3 HEX2_D5 HEX2_D4 HEX3_D6 HEX2_D6

BANK2

F3 J4 L8 F4 H3 L2 L1 D6 D5 HEX3_D5 HEX3_D3 HEX3_D4 HEX3_D0

B

IO2_0 IO2_1 IO2_2 VREFB2N0 VREFB2N1 CLK1/LVDSCLK0n CLK0/LVDSCLK0p PLL3_OUTn PLL3_OUTp

SW9 50MHZ HEX3_D2 HEX3_D1

CYCLONE II EP2C20

CYCLONE II EP2C20

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number EP2C20 BANK1 AND BANK 2 Tuesday, October 03, 2006

2

Rev 1.1A Sheet 8

1

of

21

VGA_R[0..3] VGA_G[0..3] VGA_B[0..3] U2C I2C_SDAT I2C_SCLK AUD_XCK AUD_BCLK AUD_DACDAT AUD_DACLRCK AUD_ADCDAT AUD_ADCLRCK

GPIO_B[0..15] GPIO_B[36..51] U2D GPIO_B1 GPIO_B0 GPIO_B3 GPIO_B2 GPIO_B44 UART_TXD GPIO_B5 GPIO_B4 GPIO_B7 GPIO_B6 UART_RXD GPIO_B45 GPIO_B40 GPIO_B47 GPIO_B9 GPIO_B8 GPIO_B39 GPIO_B42 GPIO_B48 GPIO_B46 GPIO_B38 PS2_DAT GPIO_B49 GPIO_B41 GPIO_B43 PS2_CLK GPIO_B11 GPIO_B10 GPIO_B13 GPIO_B12 GPIO_B15 GPIO_B14 GPIO_B51 GPIO_B50

B3 A3 B4 A4 B5 A5 B6 A6 G7 H7

LVDS27n/DEV_CLRn LVDS27p LVDS28n LVDS28p LVDS29n LVDS29p LVDS30n LVDS30p LVDS31n LVDS31p LVDS32n LVDS32p LVDS33n LVDS33p LVDS34n LVDS34p LVDS35n LVDS35p LVDS36n LVDS36p LVDS37n LVDS37p LVDS38n LVDS38p LVDS39n LVDS39p LVDS40n LVDS40p LVDS41n LVDS41p

LVDS42n LVDS42p LVDS43n LVDS43p LVDS44n LVDS44p

H11 G11 E11 D11 B11 A11

VGA_B1 VGA_VSYNC VGA_HSYNC

B13 A13 B14 A14 F12 G12 B15 A15 B16 A16 F14 F13 E14 D14 B17 A17 G15 F15 D15 C14 H14 J14 D16 E15 G16 H15 B18 A18 B19 A19

LVDS45n LVDS45p LVDS46n LVDS46p LVDS47n LVDS47p LVDS48n LVDS48p LVDS49n LVDS49p LVDS50n LVDS50p LVDS51n LVDS51p LVDS52n LVDS52p LVDS53n LVDS53p LVDS54n LVDS54p LVDS55n LVDS55p LVDS56n LVDS56p LVDS57n LVDS57p LVDS58n LVDS58p LVDS59n LVDS59p

LVDS60n LVDS60p LVDS61n LVDS61p

B20 A20 C18 C17

LINK_D1 VGA_R1 LINK_D0 VGA_R3 VGA_R2 VGA_G0 VGA_G3 VGA_R0 VGA_G2 VGA_B0

F8 G8 D8 C9 F9 E8 B7 A7 B8 A8 E9 D9 H10 H9 B9 A9 F11 F10 B10 A10

BANK3

D7 E7 H8 C10 C7 D12 E12 LINK_D3

BANK4

IO3_0 IO3_1 IO3_2 VREFB3N0 VREFB3N1 CLK10/LVDSCLK5n CLK11/LVDSCLK5p

IO4_0 IO4_1 VREFB4N0 VREFB4N1 CLK8/LVDSCLK4n CLK9/LVDSCLK4p

H12 H13 C16 C13 B12 A12

GPIO_B36 GPIO_B37

VGA_G1 LINK_D2 27MHZ

24MHZ

B

VGA_B3 VGA_B2

CYCLONE II EP2C20

CYCLONE II EP2C20

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number EP2C35 BANK3 AND BANK 4 Tuesday, October 03, 2006

2

Rev 1.1A Sheet 9

1

of

21

SW[0..2] GPIO_B[16..35] GPIO_B[52..71] U2E GPIO_B54 GPIO_B55 GPIO_B52 GPIO_B53 GPIO_B16 GPIO_B17 GPIO_B56 GPIO_B57 GPIO_B62 GPIO_B61 GPIO_B18 GPIO_B19 GPIO_B20 GPIO_B21 GPIO_B65 GPIO_B63 GPIO_B22 GPIO_B23 GPIO_B24 GPIO_B25 GPIO_B34 GPIO_B35

LED[0..17] KEY[0..3] U2F

D19 D20 C19 C20 C21 C22 E20 F20 G17 G18 D21 D22 E21 E22 H18 H17 F21 F22 G21 G22 J17 H16 J19 J18 J20 H19 J21 J22 K21 K22

LVDS62n LVDS62p LVDS63n LVDS63p LVDS64n LVDS64p LVDS65n LVDS65p LVDS66n LVDS66p LVDS67n LVDS67p LVDS68n LVDS68p LVDS69n LVDS69p LVDS70n LVDS70p LVDS71n LVDS71p LVDS72n LVDS72p LVDS73n LVDS73p LVDS74n LVDS74p LVDS75n LVDS75p LVDS76n LVDS76p

LVDS77n LVDS77p

L19 L18

GPIO_B67 GPIO_B66 GPIO_B68 GPIO_B69 KEY1 KEY0 KEY3 KEY2 GPIO_B70 GPIO_B71 LED8 LED1 LED11 LED10 LED13 LED12 LED17 LED16 GPIO_B64 GPIO_B60 GPIO_B33 SW1 SW0 GPIO_B59 GPIO_B58 LED15 LED14 LED2 SD_CLK LED3 SD_CMD LED5 SD_DAT

M19 M18 N21 N22 P15 N15 R21 R22 T21 T22 P17 P18 R18 R19 U21 U22 V21 V22 Y21 Y22 W21 W22 U19 V20 Y19 Y20 V19 W20

LVDS78n LVDS78p LVDS79n LVDS79p LVDS80n LVDS80p LVDS81n LVDS81p LVDS82n LVDS82p LVDS83n LVDS83p LVDS84n LVDS84p LVDS85n LVDS85p LVDS86n LVDS86p LVDS87n LVDS87p

BANK5

BANK6

GPIO_B30 GPIO_B32 GPIO_B31 GPIO_B26 GPIO_B27 GPIO_B28 GPIO_B29

IO5_0 VREFB5N0 VREFB5N1 CLK5/LVDSCLK2n CLK4/LVDSCLK2p PLL2_OUTn PLL2_OUTp

J15 G20 K20 L21 L22 E18 E19

LVDS88n LVDS88p LVDS89n LVDS89p LVDS90n LVDS90p LVDS91n/INIT_DONE LVDS91p/nCEO

IO6_0 IO6_1 VREFB6N0 VREFB6N1 CLK7/LVDSCLK3n CLK6/LVDSCLK3p PLL4_OUTn PLL4_OUTp

R17 Y18 R20 U20 M21 M22 U18 T18

LED9 LED6 LED0 SD_DAT3 EXT_CLOCK SW2 LED7 LED4

B

CYCLONE II EP2C20

CYCLONE II EP2C20

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number EP2C20 BANK5 AND BANK 6 Tuesday, October 03, 2006

2

Rev 1.1A Sheet 10

1

of

21

FLASH_A[0..21] FLASH_D[0..7] SW[3..6] U2G FLASH_A17 FLASH_A0 FLASH_D7 FLASH_D6 FLASH_A6 FLASH_A5 FLASH_A13 FLASH_A14 FLASH_A15 FLASH_A16

SRAM_D[0..15] SRAM_A[0..17] U2H SRAM_A6 SRAM_A7 SRAM_WE SRAM_A5 SRAM_A8 SRAM_A9 SRAM_A10 SRAM_A11 SRAM_D6 SRAM_D7 SRAM_D4 SRAM_D5 SRAM_D12 SRAM_A14 SRAM_A13 SRAM_D11 SRAM_D9 SRAM_D8 SRAM_D2 SRAM_D3 SRAM_D10 SRAM_D13 SRAM_UB SRAM_D14 SRAM_D0 SRAM_D1 SRAM_A15 SRAM_OE SRAM_A4 SRAM_CE SRAM_A16 SRAM_A17 SRAM_A2 SRAM_A3 SRAM_A0 SRAM_A1

AA20 AB20 AA19 AB19 W16 Y17 V15 U15

LVDS92n LVDS92p LVDS93n LVDS93p LVDS94n LVDS94p LVDS95n LVDS95p LVDS96n LVDS96p LVDS97n LVDS97p LVDS98n LVDS98p LVDS99n LVDS99p LVDS100n LVDS100p LVDS101n LVDS101p LVDS102n LVDS102p LVDS103n LVDS103p LVDS104n LVDS104p LVDS105n LVDS105p LVDS106n LVDS106p

LVDS107n LVDS107p LVDS108n LVDS108p

AA13 AB13 AA12 AB12

AA11 AB11 AA10 AB10 V11 W11 R11 T11 AA9 AB9 AA8 AB8 R9 R10 U10 U9 W9 Y9 AA7 AB7 V9 W8 W7 V8 AA6 AB6 P8 P9 T7 T8

LVDS109n LVDS109p LVDS110n LVDS110p LVDS111n LVDS111p LVDS112n LVDS112p LVDS113n LVDS113p LVDS114n LVDS114p LVDS115n LVDS115p LVDS116n LVDS116p LVDS117n LVDS117p LVDS118n LVDS118p LVDS119n LVDS119p LVDS120n LVDS120p LVDS121n LVDS121p LVDS122n LVDS122p LVDS123n LVDS123p

LVDS124n LVDS124p LVDS125n LVDS125p LVDS126n LVDS126p LVDS127n LVDS127p

AA5 AB5 Y6 Y5 AA4 AB4 AA3 AB3

T16 R16 FLASH_D5 AA18 FLASH_D4 AB18 FLASH_A3 R15 FLASH_A8 R14 FLASH_A7 W15 FLASH_WE Y14 FLASH_A4 T15 FLASH_A18 U14 FLASH_D3 AA17 FLASH_D2 AB17 FLASH_A19 V14 FLASH_RESET W14 FLASH_D1 AA16 FLASH_D0 AB16 FLASH_OE FLASH_CE FLASH_A1 FLASH_A12 FLASH_A20 FLASH_A11 AA15 AB15 AA14 AB14 U13 T12

BANK7

IO7_0 IO7_1 VREFB7N0 VREFB7N1 CLK12/LVDSCLK6n CLK13/LVDSCLK6p R12 R13 Y16 Y13 V12 W12 FLASH_A10 FLASH_A21 FLASH_A2 FLASH_A9 SW3 SW4

BANK8

IO8_0 VREFB8N0 VREFB8N1 CLK14/LVDSCLK7n CLK15/LVDSCLK7p

U8 Y10 Y7 U12 U11

SRAM_D15 SRAM_A12 SRAM_LB SW5 SW6

CYCLONE II EP2C20

CYCLONE II EP2C20

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number EP2C20 BANK7 AND BANK 8 Tuesday, October 03, 2006

2

Rev 1.1A Sheet 11

1

of

21

VCCIO

VCCINT VCCIO AA22 T19 P16 M20 AB21 Y12 W17 V13 T14 J10 J11 J12 J13 K9 K14 L9 L14 M9 M14 N9 N14 P10 P11 P12 P13

G14 E13 D17 C12 A21

L20 J16 G19 B22

AA1 T4 P7 M3

U2I

AB2 Y11 W6 V10 T9

G9 E10 C11 C6 A2

L3 J7 B1

BC13 0.1U VCCINT

BC14 0.1U

BC15 0.1U

BC16 0.1U

BC17 0.1U

BC18 0.1U

VCCIO1 VCCIO1 VCCIO1 VCCIO1

VCCIO2 VCCIO2 VCCIO2

VCCIO3 VCCIO3 VCCIO3 VCCIO3 VCCIO3

VCCIO4 VCCIO4 VCCIO4 VCCIO4 VCCIO4

VCCIO5 VCCIO5 VCCIO5 VCCIO5

VCCIO6 VCCIO6 VCCIO6 VCCIO6

VCCIO7 VCCIO7 VCCIO7 VCCIO7 VCCIO7

VCCIO8 VCCIO8 VCCIO8 VCCIO8 VCCIO8

G1 G2 H21 H22 J3 J5 J6 J8 J9 K8 K15 K17 K18 L7 L15 L16 L17 M7 M8 M15 M16 N5 N8 P4 P14 P19 P20 P21 P22 R4 W18

NC0 NC1 NC2 NC3 NC4 NC5 NC6 NC7 NC8 NC9 NC10 NC11 NC12 NC13 NC14 NC15 NC16 NC17 NC18 NC19 NC20 NC21 NC22 NC23 NC24 NC25 NC26 NC27 NC28 NC29 NC30

VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT

VCCD_PLL1 VCCD_PLL2 VCCD_PLL3 VCCD_PLL4 VCCA_PLL1 VCCA_PLL2 VCCA_PLL3 VCCA_PLL4

U6 F17 E5 U17 U7 F16 E6 U16

VCCIO

BC19 0.1U

BC20 0.1U

BC21 0.1U

BC22 0.1U

BC23 0.1U

BC24 0.1U

BC25 0.1U

BC26 0.1U

VCC33

Power and GND

GNDA_PLL1 GNDA_PLL2 GNDA_PLL3 GNDA_PLL4 GND_PLL1 GND_PLL1 GND_PLL2 GND_PLL2 GND_PLL3 GND_PLL3 GND_PLL4 GND_PLL4 GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND V7 E16 F7 V16 V5 U5 E17 F18 F5 F6 V18 T17

BC27 0.1U

BC28 0.1U

BC29 0.1U

BC30 0.1U

BC31 0.1U

BC32 0.1U

VCC33

BC33 0.1U

BC34 0.1U

BC35 0.1U

BC36 0.1U

BC37 0.1U

BC38 0.1U

A1 A22 B2 B21 C5 C8 C15 D10 D13 D18 F19 G4 G10 G13 H20 K3 K7 K10 K11 K12 K13 K16 K19 L10 L11 L12 L13 M4 M10 M11 M12 M13 N7 N10 N11 N12 N13 N16 N19 R3 T10 T13 T20 V3 V6 V17 W10 W13 W19 Y8 Y15 AA2 AA21 AB1 AB22

CYCLONE II EP2C20

VCCINT

BC5

B

BC6 0.1U

BC7 0.1U

BC8 0.1U

BC9 0.1U

BC10 0.1U

BC11 0.1U

BC12 0.1U

B

0.1U

U2J VCCINT VCCIO

ASDO NCSO TDI TCK TMS TDO DCLK DATA0 NCONFIG NCE CONF_DONE NSTATUS

C4 C3 K5 K2 K6 L5 L6 K4 L4 K1 N18 N20 M17 N17

ASDO nCSO TDI TCK TMS TDO DCLK DATA0 nCONFIG nCE CONF_DONE nSTATUS MSEL0 MSEL1

C15 1U

C16 1U

C17 1U

C18 1U

C19 1U

C20 1U

C21 1U

C22 1U

Crotrol Signal

CYCLONE II EP2C20

Title Altera Cyclone II Starter Board Size B Date: Document Number EP2C20 POWER AND CONFIG Tuesday, October 03, 2006 Sheet

1

Rev 1.1A 12 of 21

VCC33

BC41 0.1U 1 2

Y1 EN GND 50MHZ VCC OUT 4 3 EXT_CLOCK

50MHZ

C C

J5 VCC33 EXT CLOCK R15 BC45 0.1U 1 2 Y2 EN GND 27MHZ

B B

VCC OUT

4 3

1K

27MHZ

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number CLOCK Tuesday, October 03, 2006

2

Rev 1.1A Sheet 13

1

of

21

RN20

D

UART_RXD RXD TXD VCC33 UART_TXD LEDR LEDG

1 2 3 4 330

8 7 6 5

RXD

U4 13 8 11 10 1 3 4 5 2 6 R1IN R2IN T1IN T2IN C+ C1C2+ C2V+ VMAX232 C8 1U C9 1U VCC33 BC42 0.1U VCC5 R16 2K VCC5 R17 2K R1OUT R2OUT T1OUT T2OUT 12 9 14 7 1 6 2 7 3 8 4 9 5

J6

C6 1U C7 1U

C

VCC GND

16 15

VCC33

RS232

C

PS2_DAT PS2_CLK

R18 R19

120 120 J7 VCC5 DAT1 2 GND 3 VCC5 CLK 6 8 8 5 2 1 PS2

TOP

10 11

6 3

D1 BAT54S 1 2 1 2

D2 BAT54S

BC46 0.1U

9 10 11

VCC33

VCC33

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number PS2 AND RS232 Tuesday, October 03, 2006

2

Rev 1.1A Sheet 14

1

of

21

KEY[0..3] SW[0..9]

RN21 1 2 3 4 100K 10 KEYIN0 KEYIN1 KEYIN2 KEYIN3 KEY0 4 1 PBSW 3 2 4 1 PBSW KEY1 3 2 4 1 PBSW KEY2 3 2 4 1 PBSW KEY3 3 2 C10 1U C11 1U C12 1U C13 1U VCC33 9 8 7 6 5 4 3 2 1 8 7 6 5 VCC33

U5 GND A8 A7 A6 A5 A4 A3 A2 A1 DIR B8 B7 B6 B5 B4 B3 B2 B1 OE VCC 11 12 13 14 15 16 17 18 19 20 8 7 6 5 120 RN22 1 2 3 4 KEY0 KEY1 KEY2 KEY3

VCC33

74HC245 SW0 4 1 2 3 5 DPDT SW SW8 4 1 2 3 5 DPDT SW GND VCC33 SW8 GND GND GND VCC33 SW0 GND GND SW1 4 1 2 3 5 DPDT SW SW9 4 1 2 3 5 DPDT SW GND VCC33 SW9 GND GND BC43 0.1U BC44 0.1U GND VCC33 SW1 GND GND SW2 4 1 2 3 5 DPDT SW GND VCC33 SW2 GND GND SW3 4 1 2 3 5 DPDT SW VCC33 GND VCC33 SW3 GND GND SW4 4 1 2 3 5 DPDT SW GND VCC33 SW4 GND GND SW5 4 1 2 3 5 DPDT SW GND VCC33 SW5 GND GND SW6 4 1 2 3 5 DPDT SW GND VCC33 SW6 GND GND SW7 4 1 2 3 5 DPDT SW GND VCC33 SW7 GND GND

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number KEY AND SWITCH Tuesday, October 03, 2006

2

Rev 1.1A Sheet 15

1

of

21

GPIO_B[0..35]

RN23 GPIO_B0 GPIO_B1 GPIO_B2 GPIO_B3 1 2 3 4 47 RN26 GPIO_B12 GPIO_B13 GPIO_B14 GPIO_B15

C

RN24 8 7 6 5 IO_A0 IO_A1 IO_A2 IO_A3 GPIO_B4 GPIO_B5 GPIO_B6 GPIO_B7 1 2 3 4 47 RN27 8 7 6 5 IO_A12 IO_A13 IO_A14 IO_A15 GPIO_B16 GPIO_B17 GPIO_B18 GPIO_B19 1 2 3 4 47 RN30 8 7 6 5 IO_A24 IO_A25 IO_A26 IO_A27 GPIO_B28 GPIO_B29 GPIO_B30 GPIO_B31 1 2 3 4 47 8 7 6 5 IO_A28 IO_A29 IO_A30 IO_A31 GPIO_B32 GPIO_B33 GPIO_B34 GPIO_B35 1 2 3 4 8 7 6 5 IO_A16 IO_A17 IO_A18 IO_A19 GPIO_B20 GPIO_B21 GPIO_B22 GPIO_B23 1 2 3 4 8 7 6 5 IO_A4 IO_A5 IO_A6 IO_A7 GPIO_B8 GPIO_B9 GPIO_B10 GPIO_B11 1 2 3 4

RN25 8 7 6 5 47 RN28 8 7 6 5 47 RN31 8 7 6 5 47 IO_A32 IO_A33 IO_A34 IO_A35 IO_A20 IO_A21 IO_A22 IO_A23

C

IO_A8 IO_A9 IO_A10 IO_A11

1 2 3 4 47 RN29

GPIO_B24 GPIO_B25 GPIO_B26 GPIO_B27

1 2 3 4 47

(GPIO 0)

JP1

B

IO_A0 IO_A2 IO_A4 IO_A6 IO_A8 VCC5 IO_A10 IO_A12 IO_A14 IO_A16 IO_A18 IO_A20 IO_A22 IO_A24 IO_A26 IO_A28 IO_A30 IO_A32 IO_A34

VCC33

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40

IO_A1 IO_A3 IO_A5 IO_A7 IO_A9 IO_A11 IO_A13 IO_A15 IO_A17 IO_A19 IO_A21 IO_A23 IO_A25 IO_A27 IO_A29 IO_A31 IO_A33 IO_A35 Title Altera Cyclone II Starter Board Size A Date: Document Number CONNECT A Tuesday, October 03, 2006

2

BOX Header 2X20M

Rev 1.1A Sheet 16

1

of

21

GPIO_B[36..71]

RN32 GPIO_B36 GPIO_B37 GPIO_B38 GPIO_B39 1 2 3 4 47 RN35 GPIO_B48 GPIO_B49 GPIO_B50 GPIO_B51 1 2 3 4 47 RN38 8 7 6 5 IO_B12 IO_B13 IO_B14 IO_B15 GPIO_B52 GPIO_B53 GPIO_B54 GPIO_B55 1 2 3 4 8 7 6 5 IO_B0 IO_B1 IO_B2 IO_B3 GPIO_B40 GPIO_B41 GPIO_B42 GPIO_B43 1 2 3 4

RN33 8 7 6 5 47 RN36 8 7 6 5 47 RN39 8 7 6 5 IO_B24 IO_B25 IO_B26 IO_B27 GPIO_B64 GPIO_B65 GPIO_B66 GPIO_B67 1 2 3 4 47 8 7 6 5 IO_B28 IO_B29 IO_B30 IO_B31 GPIO_B68 GPIO_B69 GPIO_B70 GPIO_B71 1 2 3 4 IO_B16 IO_B17 IO_B18 IO_B19 GPIO_B56 GPIO_B57 GPIO_B58 GPIO_B59 1 2 3 4 IO_B4 IO_B5 IO_B6 IO_B7 GPIO_B44 GPIO_B45 GPIO_B46 GPIO_B47 1 2 3 4

RN34 8 7 6 5 47 RN37 8 7 6 5 47 RN40 8 7 6 5 47 IO_B32 IO_B33 IO_B34 IO_B35 IO_B20 IO_B21 IO_B22 IO_B23 IO_B8 IO_B9 IO_B10 IO_B11

GPIO_B60 GPIO_B61 GPIO_B62 GPIO_B63

1 2 3 4 47

(GPIO 1)

JP2 IO_B0 IO_B2 IO_B4 IO_B6 IO_B8 VCC5 IO_B10 IO_B12 IO_B14 IO_B16 IO_B18 IO_B20 IO_B22 IO_B24 IO_B26 IO_B28 IO_B30 IO_B32 IO_B34 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 IO_B1 IO_B3 IO_B5 IO_B7 IO_B9 IO_B11 IO_B13 IO_B15 IO_B17 IO_B19 IO_B21 IO_B23 IO_B25 IO_B27 IO_B29 IO_B31 IO_B33 IO_B35

VCC33

BOX Header 2X20M

A A

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number CONNECT B Tuesday, October 03, 2006

2

Rev 1.1A Sheet 17

1

of

21

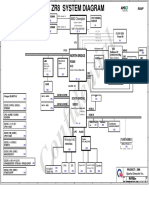

R_VCC33 DRAM_D[0..15] DRAM_A[0..11] 1 14 27 3 9 43 49 U6 SRAM_D[0..15] SRAM_A[0..17] U7 SRAM_A0 SRAM_A1 SRAM_A2 SRAM_A3 SRAM_A4 SRAM_A5 SRAM_A6 SRAM_A7 SRAM_A8 SRAM_A9 SRAM_A10 SRAM_A11 SRAM_A12 SRAM_A13 SRAM_A14 SRAM_A15 SRAM_A16 SRAM_A17 SRAM_CE SRAM_OE SRAM_WE SRAM_LB SRAM_UB NC 40 1 2 3 4 5 18 19 20 21 22 23 24 25 26 27 42 43 44 28 6 41 17 39 40

R_VCC33

VDD VDD VDD

VDDQ VDDQ VDDQ VDDQ

DRAM_A0 DRAM_A1 DRAM_A2 DRAM_A3 DRAM_A4 DRAM_A5 DRAM_A6 DRAM_A7 DRAM_A8 DRAM_A9 DRAM_A10 DRAM_A11 DRAM_CLK DRAM_CKE DRAM_LDQM DRAM_UDQM DRAM_WE DRAM_CAS DRAM_RAS DRAM_CS DRAM_BA0 DRAM_BA1

23 24 25 26 29 30 31 32 33 34 22 35 36 38 37 15 39 16 17 18 19 20 21

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CLK CKE LDQM UDQM nWE nCAS nRAS nCS BA0 BA1

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

2 4 5 7 8 10 11 13 42 44 45 47 48 50 51 53

DRAM_D0 DRAM_D1 DRAM_D2 DRAM_D3 DRAM_D4 DRAM_D5 DRAM_D6 DRAM_D7 DRAM_D8 DRAM_D9 DRAM_D10 DRAM_D11 DRAM_D12 DRAM_D13 DRAM_D14 DRAM_D15

SDRAM 1Mx16x4

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 SRAM 256Kx16 nCE nOE nWE nLB nUB 12 34 GND GND

VCC VCC

11 33

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

7 8 9 10 13 14 15 16 29 30 31 32 35 36 37 38

SRAM_D0 SRAM_D1 SRAM_D2 SRAM_D3 SRAM_D4 SRAM_D5 SRAM_D6 SRAM_D7 SRAM_D8 SRAM_D9 SRAM_D10 SRAM_D11 SRAM_D12 SRAM_D13 SRAM_D14 SRAM_D15

VSSQ VSSQ VSSQ VSSQ

VSS VSS VSS

6 12 46 52

28 41 54

SRAM_CE DRAM_CS

R20 R21

4.7K 4.7K

R_VCC33

R_VCC33

BC47

A

BC48 0.1U

BC49 0.1U

BC50 0.1U

BC51 0.1U

BC52 0.1U

BC53 0.1U

BC54

A

0.1U

0.1U Title Altera Cyclone II Starter Board Size A Date: Document Number SDRAM AND SRAM Tuesday, October 03, 2006

2

Rev 1.1A Sheet 18

1

of

21

FLASH_D[0..7] FLASH_A[0..21] U8 SD_DAT3 SD_CMD R22 SD_CLK SD_DAT R23 4.7K 9 1 2 3 4 5 6 7 8 10 11 DAT2 DAT3 CMD VSS VCC CLK VSS DAT0 DAT1 SW0 SW1 SD FLASH_A0 FLASH_A1 FLASH_A2 FLASH_A3 FLASH_A4 FLASH_A5 FLASH_A6 FLASH_A7 FLASH_A8 FLASH_A9 FLASH_A10 FLASH_A11 FLASH_A12 FLASH_A13 FLASH_A14 FLASH_A15 FLASH_A16 FLASH_A17 FLASH_A18 FLASH_A19 FLASH_A20 FLASH_A21 FLASH_WE FLASH_RESET BC55 0.1U BC56 0.1U BC57 0.1U F_VCC33 R24 4.7K FLASH_CE FLASH_OE

U9 45 25 24 23 22 21 20 19 18 8 7 6 5 4 3 2 1 48 17 16 9 10 13 11 12 14 15 26 28 47 DQ15/A-1 A0 VCC A1 A2 A3 DQ0 A4 DQ1 A5 DQ2 A6 DQ3 A7 DQ4 A8 DQ5 A9 DQ6 A10 DQ7 A11 DQ8 A12 DQ9 A13 DQ10 A14 DQ11 A15 DQ12 A16 DQ13 A17 DQ14 A18 A19 A20 A21FLASH 4Mx8 WE# RESET# WP#ACC RY/BY# CE# OE# BYTE#

37 29 31 33 35 38 40 42 44 30 32 34 36 39 41 43

F_VCC33 FLASH_D0 FLASH_D1 FLASH_D2 FLASH_D3 FLASH_D4 FLASH_D5 FLASH_D6 FLASH_D7

F_VCC33

4.7K F_VCC33

F_VCC33

F_VCC33

B

12 13 14 15

VSS VSS

27 46

Title Altera Cyclone II Starter Board Size A Date:

5 4 3

Document Number FLASH AND SD Tuesday, October 03, 2006

2

Rev 1.1A Sheet 19

1

of

21

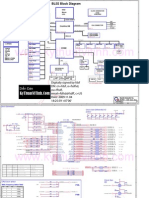

D3 SW11 D4 J8

D

1 5 6 4 2 USB5V 3 POWER SW TC1 TC2 100U/16V BC59 0.1U U18 1 INPUT GND OUTPUT 3 USB5V 1 U10 INPUT GND OUTPUT 3

SS14 D5 SS14 LM7805-0.8A BC60 0.1U D11 SS14 LM7805-0.8A

5V0 VCC5

VCC5

1 2 3 DC_7.5V

SS14 D6 SS14 D7 SS14 D8 SS14 BC58 0.1U

TC5 100U/16V

TC6 100U/16V

100U/16V

TC3 100U/16V

TC4 100U/16V

3V3 VCC33 VCC33 U17 VCC5 3 LM1117-3.3-0.8A ADJ/GND VOUT 4 R28 TC7 100U/6V BC64 0.1U TC8 120 100U/6V POWER LEDB BC61 0.1U TC10 100U/6V BC62 0.1U TC11 100U/6V BC63 0.1U TC12 100U/6V 100U/6V 100U/6V VCC33 R25 0 F_VCC33 VCC33 R26 0 R_VCC33 VCC33 R27 0 A_VCC33 TC19 TC9

C

INPUT

VCC33 U11 3 LM1117-1.2-0.8A ADJ/GND VOUT 4 INPUT

1V2 VCC12

VCC12 VCC12 R29 0

VCCINT

VCC33 R30 0

VCCIO

TC16 100U/6V

BC65 0.1U

TC17 100U/6V

C4 1U

R31 330

TC14 100U/6V

TC13 100U/6V

TC18 100U/6V

TC15 100U/6V

GND1 GND

GND2 GND

GND3 GND

GND4 GND

MH1 GND

1 MH2 GND

MH3 GND

MH4 GND

MH5 GND

MH6 GND

FID1 FIDUCIAL

FID2 FIDUCIAL

FID3 FIDUCIAL

FID4 FIDUCIAL

FID5 FIDUCIAL

FID6 FIDUCIAL

Title Altera Cyclone II Starter Board Size B Date:

5 4 3 2

Document Number POWER Tuesday, October 03, 2006 Sheet

1

Rev 1.1A 20 of 21

24MHZ

USB5V BC68 BC70 BC71 0.1U BC72 13 30 3 26 0.1U U12 0.1U BC69 0.1U FP3V U13

L1 L2

D

BEAD BEAD

USB5V

0.1U BC73 0.1U J9 USB TYPE B

D+ D-

IO-A2 IO-A3 IO-A4 IO-A5 IO-A6 GNDIO IO-A7 IO-A8 IO-A9 VCCINT INPUT/OE2/GCLK2 INPUT/GCLRn INPUT/OE1 INPUT/GCLK1 GNDINT IO-H8 IO-H7 IO-H6 VCCIO IO-H5 IO-H4 IO-H3 GNDIO IO-H2 IO-H1

VCCIO AVCC VCC VCC

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76

PWRON USBON

R32

330

FP3V

6 R33 1.5K 22 22 5 7 8 27 28

3V3OUT RSTOUT# USBDP USBDM XTIN XTOUT RESET# EEDATA EESK EECS TEST

3 2 1 4

USB_DP USB_DM

R34 R35

GND VBUS

D0 D1 D2 D3 D4 D5 D6 D7 RD# WR TXE# RXF#

25 24 23 22 21 20 19 18 16 15 14 12

ULED 6MHZ ISPTDI UD0 UD1 UD2 UD3 UD4 UD5 GND UD6 UD7 ISPTMS

D9 BAT54S 1 2 1 2

D10 BAT54S R36 100K nRESET

USB5V USB5V USB5V 6MHZ R37 22 C14

C

4 2 1 32 31

AGND GND GND

SI/WU PWREN#

11 10

47P

USB5V U14 3 BC74 0.1U LM1117-3.3-0.8A ADJ/GND VOUT 4 TC20 100U/6V

USB3V FP3V R38 120

29 9 17

FT245BM

LOAD ULED LEDB

INPUT

BC75 0.1U

BC76 0.1U

BC77 0.1U R39 1.5K 8 7 6 5 120 RN42 1 2 3 4 EEPCS 1 EEPCLK 2 EEPDI 3 EEPDO 4 U15 CS VCC CLK NC DI ORG DO GND 93LC46B 8 7 6 5

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

GNDIO IO-D8 IO-D7 IO-D6 IO-D5 IO-D4 IO-D3 GNDIO VCCIO IO-D2 IO-D1 IO-D0 GNDINT VCCINT IO-E0 IO-E1 IO-E2 GNDIO IO-E3 IO-E4 IO-E5 IO-E6 IO-E7 IO-E8 IO-E9

URD UWR TXE RXF

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

IO-A1 IO-A0 VCCIO TDI IO-B8 IO-B7 IO-B6 IO-B5 IO-B4 IO-B3 GNDIO IO-B2 IO-B1 IO-B0 TMS IO-C8 IO-C7 VCCIO IO-C6 IO-C5 IO-C4 IO-C3 IO-C2 IO-C1 IO-C0

EPM3128AT

IO-H0 GNDIO TDO IO-G7 IO-G6 IO-G5 IO-G4 IO-G3 IO-G2 VCCIO GNDIO IO-G1 IO-G0 TCK IO-F7 IO-F6 GNDIO IO-F5 IO-F4 IO-F3 IO-F2 IO-F1 GNDIO IO-F0 VCCIO

75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

ISPTDO FPTDI FPNCSO FPTCK FPNST

RN41 1 2 3 4 120 FP3V TDO TCK ISPTCK TMS TDI TRGDCLK TRGASDO TRGNCS TRGNST

C

8 7 6 5

LINK_D0 LINK_D1 LINK_D2 LINK_D3

FP3V USB5V

TRGOE

BC78 0.1U

CONF_DONE NSTATUS

R49 R50

10K 10K

VCC33

NCONFIG TCK NCE

RN43 5 6 7 8

10K 4 3 2 1

RN44 VCC33 USB3V 8 7 6 5 1 2 3 4 EEPDI ISPTCK ISPTDO ISPTMS EEPDO ISPTDI

Q2 JP3 1 3 5 7 9 2 4 6 8 10 EEPCLK EEPCS USB3V VCC5 VCC33

8550 FP3V USB3V

Q3

8550 FP3V

USB5V R40 1K R41 10K R45 PWRON USBON 4.7K Q1 8050 Q4 8050 R48 1K R42 1K R43 10K

TDI TMS TDO

RN45 10K 4 5 3 6 2 7 1 8

VCC33

SW12 10K 4 1 NCE 2 VCC33 3 TRGOE R46 5 SW-Slide

CPLD ISP R44 VCC5 4.7K 1.5K TRGNCS TRGNST VCC33 GND FP3V 1 2 3 4 U16 nCS DATA VCC GND EPCS4 VCC VCC DCLK ASDI 8 7 6 5 VCC33 VCC33 TRGDCLK TRGASDO BC79 0.1U R47 1K

DCLK ASDO NCSO DATA0 LINK_D0 LINK_D1 LINK_D2 LINK_D3 24MHZ

RN46 120 8 1 7 2 6 3 5 4

TRGDCLK TRGASDO TRGNCS TRGNST

RUN/PROG

Y3 4 3 VCC OUT 24MHZ EN GND 1 2

BC80 0.1U BC81 0.1U BC82 0.1U

FP3V

A

BC83 0.1U

BC84 0.1U

BC85 0.1U

BC86 0.1U Title Altera Cyclone II Starter Board Size B Date: Document Number USB BLASTER Tuesday, October 03, 2006 Sheet

1

Rev 1.1A 21 of 21

You might also like

- It3000 Manual TecnicoDocument132 pagesIt3000 Manual TecnicoBraulio100% (2)

- Self Compacting ConcreteDocument21 pagesSelf Compacting ConcreteSujay Raghavendra N86% (36)

- OV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicDocument1 pageOV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicMuhammad Alfiansyah100% (3)

- 'Yahoo - HTM'.TXT (Recovered)Document40 pages'Yahoo - HTM'.TXT (Recovered)Tasha GiNo ratings yet

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocument67 pagesAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaNo ratings yet

- Complete PCB Design Using OrCAD Capture and PCB EditorFrom EverandComplete PCB Design Using OrCAD Capture and PCB EditorRating: 5 out of 5 stars5/5 (1)

- Liebherr Cbpes 3656 Cbpes 4056Document18 pagesLiebherr Cbpes 3656 Cbpes 4056NightMystNo ratings yet

- Chapter 3 - Decision MakingDocument18 pagesChapter 3 - Decision MakingNur Liza HazlinNo ratings yet

- DE0 ReleaseDocument19 pagesDE0 Releasedoniz30No ratings yet

- LAB-X1 SchematicDocument2 pagesLAB-X1 SchematicRenato MirandaNo ratings yet

- Labx 1 SCHDocument2 pagesLabx 1 SCHercervantesNo ratings yet

- P+5V P+5V: Power On MuteDocument8 pagesP+5V P+5V: Power On MuteuyrikNo ratings yet

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- Spock: Power Serial I/ODocument5 pagesSpock: Power Serial I/OSanyi Ocsai100% (2)

- CECL08D Datasheet Mp3-PlayerDocument1 pageCECL08D Datasheet Mp3-PlayerGlauber CostaNo ratings yet

- Isp C v5Document2 pagesIsp C v5Francis TaisantNo ratings yet

- M300 U400Document38 pagesM300 U400Sebastian FrancisNo ratings yet

- rqqhfwlrqvehwzhhq5) Dqg%%0Rgxohv: &&67Hfkqlfdo'Rfxphqwdwlrq 6Fkhpdwlfv/D/Rxwv') Ybd 1$0Document9 pagesrqqhfwlrqvehwzhhq5) Dqg%%0Rgxohv: &&67Hfkqlfdo'Rfxphqwdwlrq 6Fkhpdwlfv/D/Rxwv') Ybd 1$0anjirponselNo ratings yet

- Hws 13642Document3 pagesHws 13642dhieward100% (2)

- PS2134 64 Schematic Kingston DTDocument3 pagesPS2134 64 Schematic Kingston DTluis_may22No ratings yet

- LG r480 - Quanta Ql3 Preso-II - Rev 1a PDFDocument39 pagesLG r480 - Quanta Ql3 Preso-II - Rev 1a PDFJosé Da Silva MataNo ratings yet

- Cpu Logic DiagramDocument0 pagesCpu Logic DiagramMauricio RaúlNo ratings yet

- PE4H VER24 SchematicDocument2 pagesPE4H VER24 SchematicB Huerta MuñozNo ratings yet

- Noblex - RCD - 138Document8 pagesNoblex - RCD - 138pablo190381No ratings yet

- LCR Metar - Sve ShemeDocument7 pagesLCR Metar - Sve ShemeKarlo MužinićNo ratings yet

- ®MCI Electronics WWW - Olimex.cl: 3V3 3V3 RssiDocument1 page®MCI Electronics WWW - Olimex.cl: 3V3 3V3 Rssiefx8100% (1)

- Toshiba Satellite M300 M305 Quanta TE1 Laptop SchematicsDocument40 pagesToshiba Satellite M300 M305 Quanta TE1 Laptop SchematicsErick RodriguezNo ratings yet

- 07 Schematic Diagram EDocument6 pages07 Schematic Diagram EGiovanni Mendoza100% (1)

- Can Bus SCHDocument1 pageCan Bus SCHhoangdai100% (3)

- Packard-Bell Easynote Ml65 Vesurio Pb5 Pb6 Quanta Pb5 Pb6 Rev 1a SCHDocument35 pagesPackard-Bell Easynote Ml65 Vesurio Pb5 Pb6 Quanta Pb5 Pb6 Rev 1a SCHAloui ZakariaNo ratings yet

- Acer 5553g M B Quanta Zr8 - Da0zr8mb8e0Document49 pagesAcer 5553g M B Quanta Zr8 - Da0zr8mb8e0tuner12No ratings yet

- Acer I5 47501306462469980Document67 pagesAcer I5 47501306462469980fdsaq12No ratings yet

- TF 117 Circuit DiagramDocument9 pagesTF 117 Circuit DiagramFrancis TaisantNo ratings yet

- Abit - M621 Schematics: Title Sheet ModifyDocument33 pagesAbit - M621 Schematics: Title Sheet Modify775i945GZ100% (1)

- 8I845PE PRO Rev.1.01 SCHDocument38 pages8I845PE PRO Rev.1.01 SCHJurgita GecieneNo ratings yet

- HP Envy 15 (Quanta SP7)Document42 pagesHP Envy 15 (Quanta SP7)efeln1No ratings yet

- Scheme HP Compaq Cq61 Quanta Op8Document40 pagesScheme HP Compaq Cq61 Quanta Op8Alija SirotanovićNo ratings yet

- Toshiba Satellite A300Document37 pagesToshiba Satellite A300Nagy József100% (1)

- Q9T4 FP91G Interface BDDocument5 pagesQ9T4 FP91G Interface BDax63naNo ratings yet

- Schematic DiagramDocument13 pagesSchematic DiagramSas WajiNo ratings yet

- Wistron JV50-PU Rev SB PDFDocument61 pagesWistron JV50-PU Rev SB PDFalbugNo ratings yet

- DELL VOSTRO-3500 Winery15 PDFDocument91 pagesDELL VOSTRO-3500 Winery15 PDFronaldovieiraNo ratings yet

- Helio Board SCH v1.22Document26 pagesHelio Board SCH v1.22nanostallmannNo ratings yet

- HP Pavilion Dv6 Quanta Ut3 Ut5 Rev PV SCHDocument43 pagesHP Pavilion Dv6 Quanta Ut3 Ut5 Rev PV SCHOtto OctavianNo ratings yet

- HP Pavilion Dv6000 Dv6500 Dv6600 Dv6700 Dv9000 Dv9500 - DA0AT3MB8F0 - QUANTA AT3 - SC (Intel) - Rev 1ADocument48 pagesHP Pavilion Dv6000 Dv6500 Dv6600 Dv6700 Dv9000 Dv9500 - DA0AT3MB8F0 - QUANTA AT3 - SC (Intel) - Rev 1Agbouret0% (1)

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- High-Performance GM LS-Series Cylinder Head GuideFrom EverandHigh-Performance GM LS-Series Cylinder Head GuideRating: 4.5 out of 5 stars4.5/5 (2)

- Exploring Arduino: Tools and Techniques for Engineering WizardryFrom EverandExploring Arduino: Tools and Techniques for Engineering WizardryRating: 4.5 out of 5 stars4.5/5 (5)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Engineering Service Revenues World Summary: Market Values & Financials by CountryFrom EverandEngineering Service Revenues World Summary: Market Values & Financials by CountryNo ratings yet

- sc10mnx 104h8075 r290 220v 50hz 06-2023 DsDocument4 pagessc10mnx 104h8075 r290 220v 50hz 06-2023 Dsangel1573065412No ratings yet

- SAE J518 Bolt FlangeDocument15 pagesSAE J518 Bolt FlangejoanNo ratings yet

- 30G 5W Wiring DiagramDocument51 pages30G 5W Wiring DiagramFrancisco AlvarezNo ratings yet

- Application of Conductors in Daily LifeDocument2 pagesApplication of Conductors in Daily LifeFranly Amai80% (5)

- Assignment-Report Writing FormatDocument2 pagesAssignment-Report Writing FormattanyaNo ratings yet

- KBA Instruction ManualDocument7 pagesKBA Instruction ManualFILIN VLADIMIRNo ratings yet

- 9783 en Be v1 Astrigma LR PDFDocument12 pages9783 en Be v1 Astrigma LR PDFhugodanielsousaNo ratings yet

- Appendix C: Analysis of Generic Spans For Formula B TrucksDocument120 pagesAppendix C: Analysis of Generic Spans For Formula B TrucksAmanuel Q. MulugetaNo ratings yet

- Unit 4Document66 pagesUnit 4Martin Sebastian Gomez GalizziNo ratings yet

- 07 - 373 - Salib, Abdel-Sayed - Dynamic Behaviour and Seismic Response of FRP Light Poles in High SeismDocument8 pages07 - 373 - Salib, Abdel-Sayed - Dynamic Behaviour and Seismic Response of FRP Light Poles in High SeismAnonymous EVM4dONo ratings yet

- Chronicle 11-11-09 EditionDocument16 pagesChronicle 11-11-09 EditionmjchronicleNo ratings yet

- Final Report 2015 March B5-C6.26.CompressedDocument139 pagesFinal Report 2015 March B5-C6.26.Compressedfrodo frodoNo ratings yet

- CAT - C7 (All Others) .Prefix KAL or SAP1-3955Document9 pagesCAT - C7 (All Others) .Prefix KAL or SAP1-3955Phil B.No ratings yet

- R REC SM.329!12!201209 I!!PDF E (Unwanted Emissions)Document41 pagesR REC SM.329!12!201209 I!!PDF E (Unwanted Emissions)Asuncion SarmientoNo ratings yet

- Quanto RmedDocument4 pagesQuanto RmedXimena Pilar Rios HerediaNo ratings yet

- Plastic MoneyDocument19 pagesPlastic MoneyMuhammad Talha Khan75% (4)

- WD Caviar SE: Desktop Hard DrivesDocument2 pagesWD Caviar SE: Desktop Hard DrivesZoran ŠušakNo ratings yet

- Virtualization Administration Guide-En-USDocument191 pagesVirtualization Administration Guide-En-USmani_588No ratings yet

- C PuzzlesDocument20 pagesC Puzzlesapi-3721375100% (1)

- LEMTEK45E English Version Rev1Document35 pagesLEMTEK45E English Version Rev1ambiya086114No ratings yet

- Fieldwork No. 3 - Determining The Area of A Tract of LandDocument5 pagesFieldwork No. 3 - Determining The Area of A Tract of LandaaarrNo ratings yet

- Mobile Printer SPP-R210 BixolonDocument2 pagesMobile Printer SPP-R210 BixolonBixolonGlobalNo ratings yet

- Strategic Audit of A Commercial WebsiteDocument18 pagesStrategic Audit of A Commercial WebsiteMaelia BianchiNo ratings yet

- TracexDocument787 pagesTracexCelek KamuNo ratings yet

- Otto Diesel and Dual CycleDocument2 pagesOtto Diesel and Dual CycleRavi ParikhNo ratings yet