Professional Documents

Culture Documents

Xilinx9.2 Procedure

Uploaded by

Amal RajCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Xilinx9.2 Procedure

Uploaded by

Amal RajCopyright:

Available Formats

PROCEDURE FOR XILINX

ISE

SIMULATOR

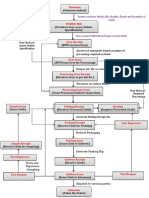

GENERAL: (SIMULATION & KIT) 1. Open Xilinx9.2 software. 2. Go to File menu New project create New project Type file name click Next Device properties window will open. Specify family-SPARTAN 3 Device XC3S400 3. Click new source Select VHDL Module & Type a file name (Diff) Define Port pinsClick NextFinishYesNext New project summary wizard window will openFinish. Filename.vhd file & Design summary will be created 4. In .vhd file type the program after begin and save it. 5. Go to Processes window Synthesis-XST Check Syntax View synthesis report FOR SIMULATION: 6. Go to Source window Right click on file name (Behavioral) New sourceSelect TEST BENCH WAVEFORMType the file name (Diff) Next Next Finish. Initial Timing and Clock Wizard window will open. 7. Set the clock i/p. If no clock i/p for the program, select combinatorial button & Click Finish. 8. Set the inputs by Clicking & save it. 9. Go to Source window select Behavioral Simulation. 10. Go to Process window Select Xilinx ISE simulator simulate Behavioral model. Output window will open. Check the Output. FOR KIT IMPLEMENTATION: 6. Go to Source Window Synthesis/Implementation. 7. Go to Processes Window User ConstraintsAssign Package pins. PACE window will be opened. 8. Set i/p and o/p pin numbers by seeing the kit & save it. Then minimize the PACE window. 9. Click Implementation DesignGenerate Programming file. Gen Programming file window will be opened. 10. Click Configure Device Impact window will open. Click Finish. 11. Assign New Configure File window will open. Select Filename.bit and open.

12. Go to boundary scanRight clickprogram Apply OK. Check the output in the kit.

You might also like

- Unctional Equirements Ocument: Project or System NameDocument28 pagesUnctional Equirements Ocument: Project or System NameAmal RajNo ratings yet

- BSL Functional Flow DiagramDocument2 pagesBSL Functional Flow DiagramAmal RajNo ratings yet

- Can You Explain The PDCA Cycle and Where Testing Fits In?Document8 pagesCan You Explain The PDCA Cycle and Where Testing Fits In?Amal RajNo ratings yet

- Test ExercisesDocument6 pagesTest ExercisesAmal RajNo ratings yet

- User Stories: Project "Arogya Bhagya Yojane" ABYDocument9 pagesUser Stories: Project "Arogya Bhagya Yojane" ABYAmal RajNo ratings yet

- Validation For A Login PageDocument2 pagesValidation For A Login PageAmal RajNo ratings yet

- In Case of NACH Name of The Bank & Branch: ICICI BANK &Document1 pageIn Case of NACH Name of The Bank & Branch: ICICI BANK &Amal RajNo ratings yet

- Devi Mahatmyam Durga Saptasati Chapter 1 in Tamil PDFDocument11 pagesDevi Mahatmyam Durga Saptasati Chapter 1 in Tamil PDFAmal RajNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5796)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (589)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)