Professional Documents

Culture Documents

Phase-Locked Loops With Applications: ECE 5675/4675 Lecture Notes Fall 2004

Phase-Locked Loops With Applications: ECE 5675/4675 Lecture Notes Fall 2004

Uploaded by

Vladimir VojinovicOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Phase-Locked Loops With Applications: ECE 5675/4675 Lecture Notes Fall 2004

Phase-Locked Loops With Applications: ECE 5675/4675 Lecture Notes Fall 2004

Uploaded by

Vladimir VojinovicCopyright:

Available Formats

Phase-Locked

Loops with

Applications

ECE 5675/4675 Lecture Notes

Fall 2004

20022004

Mark A. Wickert

F(s)

K

v

/s

.

Chapter 1

Course Introduction/Overview

Contents

1.1 Lecture Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2 This Course and the Phase-Locked Loop Landscape . . . . . . . . . . . . . . 1-4

1.2.1 General PLL Perspective . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.2 Course Topics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.3 Course Perspective in the Comm/DSP Area of ECE . . . . . . . . . . . . . . 1-6

1.4 The Role of Computer Analysis/Simulation Tools . . . . . . . . . . . . . . . . 1-8

1.5 Instructor Policies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.6 Course Syllabus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.7 Required Student Background . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.8 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.9 PLL Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.9.1 Classication of PLLs . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.9.2 LPLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.9.3 DPLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

1.9.4 ADPLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

1.9.5 SPLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

1.10 Applications Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

1.10.1 Synchronization for Digital Communications . . . . . . . . . . . . . . . 1-19

1.10.2 Frequency Synthesis Applications . . . . . . . . . . . . . . . . . . . . . 1-26

1.11 Simulation Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-29

1-1

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

.

1-2 ECE 5675 Phase-Lock Loops with Applications

1.1. LECTURE OUTLINE

1.1 Lecture Outline

This Course and the PLL Landscape

General PLL perspective

Course Topics

Course perspective in the comm/DSP area of ECE

The role of computer analysis/simulation tools

Instructor policies

Course syllabus

Required student background

References

Books

Reports

Journals

PLL introduction and applications overview

ECE 5675 Phase-Lock Loops with Applications 1-3

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

1.2 This Course and the Phase-Locked Loop Landscape

1.2.1 General PLL Perspective

The focus of this course is phase-lock loops (PLLs) and appli-

cations

At rst this may seem like a very narrow course of study, but the

PLL has many applications and many implementation variations

The use of PLLs for frequency synthesis, i.e., creating a stable

yet tuneable local oscillator for radio transmitters and receivers

is one traditional application area

In communication systems in general the PLL is widely used

Carrier phase and frequency tracking

Symbol (bit) synchronization

Chip synchronization is spread-spectrum systems (this in-

cludes GPS receivers)

Clock recovery (same class of problems as symbol sync)

The implementation may be:

All analog electronics (microwave/RF/baseband)

A hybrid of analog and digital electronics

A hybrid of analog and software

Pure software

The implementation technology may be:

Board level using RF and baseband devices

Single chip with a few off-chip or maybe no off-chip parts

1-4 ECE 5675 Phase-Lock Loops with Applications

1.2. THIS COURSE AND THE PHASE-LOCKED LOOP LANDSCAPE

Custom ASIC or FPGA

A combination of RF and baseband analog with the remain-

der in software via a real-time digital signal processing

Entirely real-time DSP approach if signal samples are ac-

quired somewhere else

1.2.2 Course Topics

PLL fundamentals

Loop components

Loop response

Loop stability

Transient response

Modulation response

Acquisition

Unaided

Aided

Analog PLL lab experiment

Performance in noise

Input noise

Phase noise

Nonlinear behavior and cycle slipping

Digital PLLs

Communication applications

ECE 5675 Phase-Lock Loops with Applications 1-5

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

1.3 Course Perspective in the Comm/DSP Area of ECE

\

C

o

m

m

u

n

i

c

a

t

i

o

n

s

/

D

S

P

C

o

u

r

s

e

O

f

f

e

r

i

n

g

s

U

n

d

e

r

g

r

a

d

u

a

t

e

E

l

e

c

t

r

i

c

a

l

E

n

g

i

n

e

e

r

i

n

g

C

u

r

r

i

c

u

l

u

m

U

C

C

S

S

e

n

i

o

r

/

1

s

t

T

i

e

r

G

r

a

d

u

a

t

e

S

i

g

n

a

l

s

&

S

y

s

t

e

m

s

C

o

u

r

s

e

s

U

C

C

S

2

n

d

T

i

e

r

G

r

a

d

.

S

i

g

n

a

l

s

&

S

y

s

t

e

m

s

C

o

u

r

s

e

s

L

i

n

e

a

r

S

y

s

t

e

m

s

L

i

n

e

a

r

S

y

s

t

e

m

s

I

n

t

r

o

t

o

D

S

P

I

n

t

r

o

t

o

D

S

P

E

n

P

r

o

b

&

S

t

a

t

s

.

E

n

P

r

o

b

&

S

t

a

t

s

.

.

.

.

C

o

m

m

S

y

s

I

C

o

m

m

S

y

s

I

M

o

d

e

r

n

D

S

P

M

o

d

e

r

n

D

S

P

R

a

n

d

o

m

S

i

g

n

a

l

s

R

a

n

d

o

m

S

i

g

n

a

l

s

S

a

t

e

l

l

i

t

e

C

o

m

m

S

a

t

e

l

l

i

t

e

C

o

m

m

C

o

m

m

N

e

t

w

o

r

k

s

C

o

m

m

N

e

t

w

o

r

k

s

D

e

t

e

c

t

/

E

s

t

i

m

.

D

e

t

e

c

t

/

E

s

t

i

m

.

E

s

t

i

m

&

A

d

a

p

F

i

l

t

E

s

t

i

m

&

A

d

a

p

F

i

l

t

S

p

e

c

t

r

a

l

E

s

t

i

m

.

S

p

e

c

t

r

a

l

E

s

t

i

m

.

R

a

d

a

r

S

y

s

t

e

m

s

R

a

d

a

r

S

y

s

t

e

m

s

S

p

r

e

a

d

S

p

e

c

t

r

u

m

S

p

r

e

a

d

S

p

e

c

t

r

u

m

I

n

f

o

r

m

/

C

o

d

i

n

g

I

n

f

o

r

m

/

C

o

d

i

n

g

C

o

m

m

T

o

p

i

c

s

C

o

m

m

T

o

p

i

c

s

P

L

L

s

&

F

r

e

q

S

y

n

P

L

L

s

&

F

r

e

q

S

y

n

I

m

a

g

e

P

r

o

c

I

m

a

g

e

P

r

o

c

O

p

t

i

c

a

l

C

o

m

m

O

p

t

i

c

a

l

C

o

m

m

U

C

C

S

O

t

h

e

r

G

r

a

d

.

S

i

g

n

a

l

s

&

S

y

s

t

e

m

s

C

o

u

r

s

e

s

O

n

D

e

m

a

n

d

/

I

n

d

.

S

t

u

d

y

R

e

a

l

T

i

m

e

D

S

P

R

e

a

l

T

i

m

e

D

S

P

C

o

m

m

S

y

s

I

I

C

o

m

m

S

y

s

I

I

W

i

r

e

l

e

s

s

/

M

b

l

C

o

m

W

i

r

e

l

e

s

s

/

M

b

l

C

o

m

D

e

f

i

n

e

d

M

S

E

E

C

o

u

r

s

e

s

F

a

l

l

S

p

r

i

n

g

1-6 ECE 5675 Phase-Lock Loops with Applications

1.4. THE ROLE OF COMPUTER ANALYSIS/SIMULATION TOOLS

1.4 The Role of Computer Analysis/Simulation Tools

In working homework problems pencil and paper type solutions

will work for most problems

Often times solutions can be enhanced through the use of com-

puter analysis and simulation tools

At least one computer project will be assigned which involves

both mathematical modeling and simulation

Most often MATLAB will sufce for modeling and simulation

The use of Spice with behavioral level modeling capabilities

may also be useful, e.g., XSpice or PSpice

Block level simulation environments are particularly convenient

for PLL simulations

MATLAB Simulink: very powerful block simulation envi-

ronment, most capable for PLL work when expanded with

DSP blockset and the Comm block set; limited PLL specic

blocks even in Comm block set

VisSim/Comm (included with the student version of Math-

cad: A friendly block simulation environment, which with

the Comm library is very good at complex baseband simula-

tion; PLL components are also included

Elanix SystemView(used the last time the course was taught):

free student version which has a RF and Comm block set

with some PLL specic oriented blocks

ECE 5675 Phase-Lock Loops with Applications 1-7

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

1.5 Instructor Policies

Working homework problems will be a very important aspect of

this course

Each student is to his/her own work and be diligent in keeping

up with problem assignments

If work travel keeps you from attending class on some evening,

please inform me ahead of time so I can plan accordingly, and

you can make arrangements for turning in papers

The course web site

http://eceweb.uccs.edu/wickert/ece5675/

will serve as an information source in between weekly class

meetings

Please check the web site updated course notes, assignments,

hints pages, and other important course news

1-8 ECE 5675 Phase-Lock Loops with Applications

1.6. COURSE SYLLABUS

1.6 Course Syllabus

ECE 5675/4675 Phase-Locked Loops,

Synchronization, and Frequency Synthesis

Fall Semester 2004

Instructor: Dr. Mark Wickert Office: EB-226 Phone: 262-3500

wickert@eas.uccs.edu Fax: 262-3589

http://eceweb.uccs.edu/wickert/

Office Hrs: Tue. 10:45 am12:00 pm, 3:154:15 pm and after 7:05 pm as needed, others by

appointment. Note: These hours may be adjusted if needed.

Required

Texts:

W. F. Egan, Phase-Lock Basics, Wiley, 1998. Optional text: B. Razavi, Mono-

lithic Phase-Locked Loops and Clock Recovery Circuits, IEEE Press 1996.

Optional

Software:

MATLAB Student Version 7.x, Simulink 5.x, and Symbolic Math Toolbox (no

matrix size limits). An interactive numerical analysis, data analysis, and graph-

ics package for Windows/Linux/Mac OSX $99.95. The signal processing and

control toolboxes will be helpful at $29.95 each. Order both from

www.mathworks.com/student. Note: The ECE PC Lab has the full ver-

sion of MATLAB and Simulink for windows (ver. 7.0) with many toolboxes.

Other tools of interest include VisSim/Comm (www.vissim.com/)

Grading: 1.) Graded homework assignments totaling 40%.

2.) Mid-term Exam worth 25%.

3.) Analog PLL Laboratory 10%.

4.) Final Project/Exam worth 25%.

Requirements: A background in basic communication theory, probability and random variables, and basic digital

signal processing, i.e. sampling theory would be desired. Please contact Dr. Wickert if you are considering this

course, but are in doubt as to whether you have adequate background

Topics Text Chapters

Session

(wks)

1. Introduction/Overview 1, 10 1.0

2. Phase-Locked Loop Fundamentals (including basic synthesizers) 2, 3, 4, 5, 6, 7 3.0

3. PLL Tracking Performance in Noise (including phase noise) 11, 12, 13, 14, 15,

16, 17, 18, 19

2.0

4. Unaided and Aided Acquisition 8, 9 2.0

5. Analog PLL Lab Experiment Handout 2.0

6. Digital signal processing Based PLLs Notes only 2.0

7. Real-time DSP PLL Experiment (if time permits or just simulation) Handout 1.0

8. Specific synchronization techniques in Comm Systems (DSP based?) Notes, 10 0.5

ECE 5675 Phase-Lock Loops with Applications 1-9

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

1.7 Required Student Background

Basic linear systems theory is a must

Random variables is needed for noise analysis

A brief introduction to random processes will be provided if

needed

Basic modulation theory is also assumed

A knowledge of digital communication systems is desirable

Abasic understanding of digital signal processing would be help-

ful, but is not required

Knowledge of sampling theory is needed for digital loop con-

cepts

Knowledge of z-domain concepts is desirable, but again a brief

introduction will be given if needed

The ability to program using MATLAB is important for simula-

tion aspects

The ability to build Spice circuit models is also desirable

1-10 ECE 5675 Phase-Lock Loops with Applications

1.8. REFERENCES

1.8 References

The following list of references is not exhaustive by any means, but

is a list core of books I have in my library or have been recommended

to me. Some of these books are hard to nd since they are now out-

of-print.

General PLL

1. Heinrich Meyr and Gerd Ascheid, Synchronization in Digital Communica-

tions, Volume 1, John Wiley, 1990.

This text is basically concerned with analog PLLs (including charge-

pump) starting from the very basic concepts all the way through very

detailed nonlinear analysis with noise

The text also includes material on automatic frequency control (AFC)

and automatic gain control (AGC)

The book is clearly telecommunications based since PLL synthesizers

are not considered at all

Used as the course text the last time the course was taught

2. Roland E. Best, Phase-Locked Loops, Theory Design, and Applications, fourth

edition, McGraw Hill, 1999.

3. Alain Blanchard, Phase-Locked Loops: Application to Coherent Receiver

Design, Wiley, New York,1976. Original course text, but now unavailable.

4. Floyd M. Gardner, Phaselock Techniques, 2nd ed., Wiley, New York, 1979.

5. Dan Wolaver, Phase-Locked Loop Circuit Design, Prentice Hall, New Jersey,

1991.

6. Jack K. Holmes, Coherent Spread Spectrum Systems, John Wiley, 1982.

7. Jacob Klapper and John T. Frankle, Phase-Locked and Frequency-Feedback

Systems, Academic Press, New York, 1972.

8. William C. Lindsey and Marvin K. Simon, Telecommunication Systems En-

gineering, Prentice-Hall, Englewood Cliffs, New Jersey, 1973.

ECE 5675 Phase-Lock Loops with Applications 1-11

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

9. A. J. Viterbi, Principles of Coherent Communications, McGraw-Hill, New

York, 1966.

10. Rodger E. Ziemer and Roger L. Peterson, Digital Communications and Spread

Spectrum Systems, Macmillan, New York, 1985.

Frequency Synthesizers

1. William F. Egan, Frequency Synthesis by Phase Lock, second edition, Wiley,

New York, 2000.

2. Venceslav F. Kroupa, Frequency Synthesis: Theory, Design, and Applica-

tions, Wiley, New York, 1973.

3. Vadim Manassewitsch, Frequency Synthesizers: Theory and Design, 3rd ed.,

Wiley, New York, 1987.

4. W. P. Robbins, Phase Noise in Signal Sources (Theory and Applications),

Peter Peregrinus Ltd., London, UK., 1982.

5. Ronald C. Stirling, Microwave Frequency Synthesizers, Prentice-Hall, Engle-

wood Cliffs, New Jersey, 1987.

Synchronization

1. Umberto Mengali and Aldo N. DAndrea, Synchronization Techniques for

Digital Receivers, Plenum Press, New York, 1997.

2. Heinrich Meyr, Marc Moeneclaey, and Stefan Fechtel, Digital Communica-

tion Receivers: Synchronization, Channel Estimation, and Signal Processing,

Prentice Hall, New Jersey, 1998. This is volume II of of Meyr and Ascheid.

Reports

1. L. Bogusch, Digital Communications in Fading Channels: Tracking and

Synchronization, AFWL-TR-90-15, Weapons Laboratory, Kirkland AFB,

NM, 1990.

Journals

1. IEEE Transactions on Communications.

2. IEEE Journal on Select Areas in Communications.

1-12 ECE 5675 Phase-Lock Loops with Applications

1.9. PLL INTRODUCTION

1.9 PLL Introduction

The history of the phase-locked loop dates back to as early as 1932.

According to author Dr. Rolland Best, the French engineer de Belle-

size is the inventor of coherent communication. Current applications

of the phase-locked loop (PLL) in-clude more than just coherent

communications. Frequency synthesis is currently a very important

PLL application area. The emphasis of this course will however be

for the most part on basic PLL theory and telecommunication ap-

plications. A discussion of various synthesizer types will also be

included at some point.

1.9.1 Classication of PLLs

In this course the intention is to discuss four basic classes of PLLs.

Using the notation of Best

1

these classes are:

Analog or Linear PLL (LPLL)

Digital PLL (DPLL)

All digital PLL (ADPLL)

Software PLL (SPLL)

1.9.2 LPLL

The LPLL (Best) or analog PLL is the classical form of PLL. All

components in the LPLL operate in the continuous-time domain. A

LPLL block diagram is shown below:

1

Roland E. Best, Phase Locked-Loops: Theory, Design, and Applications, fourth edition, McGraw Hill, 1999

ECE 5675 Phase-Lock Loops with Applications 1-13

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

The phase detector is typically some form of analog multiplier,

either a double-balanced mixed (DBM) or an active four-quadrant

multiplier

The phase error function is of the form

(t ) = K

m

K

1

A

. ,, .

K

D

sin

_

(t )

(t )

_

small error

K

D

_

(t )

(t )

_

Phase

Detector

Loop

Filter

Voltage

Controlled

Oscillator

Analog Multiplier Lowpass Filter

2A

0

t t ( ) + [ ] sin

2A

0

t

t ( ) + [ ] cos

Phase Error

Control voltage

~demod freq.modulation

Tracked input carrier

Classical analog PLL

The loop lter may be active or passive, but it typically results

in the loop being either rst-order or second-order

The design/analysis of the loop lter makes use of the Laplace

transform

Loop lter system functions, F(s), include:

Loop Order Filter F(s)

1 1

2(perfect integrator)

1+s

2

s

1

2(imperfect integrator)

1+s

2

1+s

1

2(lag or lowpass)

1

1+s

1-14 ECE 5675 Phase-Lock Loops with Applications

1.9. PLL INTRODUCTION

1.9.3 DPLL

The digital PLL is really just an analog PLL with a digital phase

detector.

The DPLL is really a hybrid system

The DPLL is very popular in synthesizer applications

In the above gure the optional digital divider, and variations on

it, are used in frequency synthesis applications

Popular types of digital phase detectors include:

Exclusive or gate (EXOR)

Edge-triggered JK-ipop

Phase frequency detector (PFD)

Optional

Freq. Divide

by N

2A

0

t t ( ) + [ ] sin

2A

0

t

t ( ) + [ ] cos

Digital

Phase

Detector

VCO

2A N

0

t N

t ( ) + [ ] cos

F s ( )

Classical digital PLL (digital phase detector)

1.9.4 ADPLL

The all-digital PLL (classical all-digital) is distinctly different from

the rst two PLLs mentioned thus far.

The ADPLL is a digital loop in two senses:

ECE 5675 Phase-Lock Loops with Applications 1-15

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

All digital components

All digital (discrete-time) signals

There are many ADPLL building blocks, and many variations

on putting them together

The ADPLL is also closely related to the SPLL

The VCO is replaced by a digitally controlled oscillator (DCO)

or also called a numerically controlled oscillator (NCO)

J

K

Q

K counter

INC DEC

counter N

Incr/Decr

Counter

XOR

74HC/HCT297

Carry

Borrow

Unused

Phase

Detector

Input

CP

Output

ID

out

Mf

0

K clock

ID clock

2Nf

0

N Control

K Modulus Control

Nominally at f

0

All-digital PLL as implemented in the part 74xx297

1-16 ECE 5675 Phase-Lock Loops with Applications

1.9. PLL INTRODUCTION

1.9.5 SPLL

The SPLL can be viewed as a discrete-time implementation of either

the LPLL or the DPLL. The block diagram of a generic SPLL is

shown below.

The implementation of the loop lter is typically a difference

equation

The design/analysis of the loop lter is done using the z-transform

The SPLL is feasible due to the availability of digital signal pro-

cessing (DSP) oriented microprocessors

A DSP processor features a Harvard architecture (separate

data and program memories)

Pipelined instruction capabilities

The computer hardware requirements are relatively high, but the

exibility is also very great

By designing the SPLL to closely match say an LPLL we can

effectively simulate analog PLL designs using software tools

Digitally

Controlled

Oscillator

2A

0

t t [ ] + ( ) sin

Phase

Detector

ADC

Discrete-

Time

Loop Filter

2A

0

t

t [ ] + ( ) cos

f

s

A software or discrete-time signals based PLL

ECE 5675 Phase-Lock Loops with Applications 1-17

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

The SPLL is very popular in digital communication applications

For complex baseband systems a popular phase detector is again

the sinusoidal phase detector, but nowit takes the following form

Ae

j

0

n n [ ] + ( )

K

1

e

j

0

n

n [ ] + ( )

K

1

Ae

j n [ ]

n [ ] ( )

Im { }

K

1

A n [ ]

n [ ] ( ) sin

Complex

signal path

Complex signal form of SPLL

1.10 Applications Overview

1.10.1 Synchronization for Digital Communications

In digital communications various levels of synchronization are

required

Systems that only operate at baseband typically require fewer

total function than those at passband or RF

The synchronization problem can viewed as one of parameter

estimation from waveforms

The three parameters most often referred to are, carrier frequency,

f

0

, carrier phase, , and symbol timing,

Taken jointly they form a parameter vector with three compo-

nents

1-18 ECE 5675 Phase-Lock Loops with Applications

1.10. APPLICATIONS OVERVIEW

Matched

Filter

Symbol

Detect

Freq.

Recovery

Phase

Recovery

e

j2v

t

e

j

r t ( ) r t ( )

x t ( ) x k [ ]

Sample at

kT +

c

k

counter-rotate

to remove

freq. error

counter-rotate

to remove

phase error

Timing

Recovery

Synchronization in digital communications using complex signals

The gure above depicts analog signal processing, but in prac-

tice combinations of analog and digital signal processing are re-

quired

Parameter tracking can be implemented using feedback, as in

PLL based techniques

Feed-forward methods are also possible

Some block diagrams of synchronization systems are shown next

Coherent Carrier Reference Generation

BPF

at f

0

( )

2

BPF

at 2f

0

Loop

Filter

VCO

Divide

by Two

Input

Signal

Output

Carrier

Reference

Squaring loop for suppressed carrier modulation

ECE 5675 Phase-Lock Loops with Applications 1-19

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

Power

Splitter

VCO

Loop

Filter

90

LPF at

Bit Rate

LPF at

Bit Rate

Input

Signal

In-phase

Output

Quadrature

Output

Costas loop which performs at baseband the operation of the squaring

loop

BPF

at f

0

( )

M

BPF

at Mf

0

Loop

Filter

VCO

Divide

by M

Input

Signal

Output

Carrier

Reference

Mth-power loops for M-ary phase shift keying

A DSP Based Mth Power and Decision Directed Approach

In bandpass digital communication systems the carrier frequency

is generated from a local timing reference

At the receiver coherent demodulation requires that the same

carrier frequency (or a translated version) and phase be used for

demodulation

1-20 ECE 5675 Phase-Lock Loops with Applications

1.10. APPLICATIONS OVERVIEW

A coherent carrier recovery system, which tracks the frequency

and phase of the carrier at the receiver, is used for this purpose

The received signal (noiseless) is of the form

x(t ) = Re

_

s(t )e

j [

c

t +(t )]

_

Consider a complex baseband information carrying waveform

given by (here pulse amplitude modulation PAM)

y(t ) = e

j [

c

t +(t )]

m=

A

m

p(t mT)

where A

m

is the data, p(t ) is the transmit pulse shape, T is the

symbol period, and q(t ) is the frequency offset and phase jitter

We need to form an estimate of the received carrier phase q(t )

so that the above signal can be demodulated with

e

j [

c

t +

(t )]

In a digital (DSP) based receiver we may sample the signal at

the symbol rate (or a submultiple), the product of the carrier

estimate with the input to obtain

y[n] = e

j [(nT)

(nT)]

m=

A

m

p(nT mT)

Assuming that p(nT mT) = (n) the samples we obtain are

of the form

y[n] = e

j ([n]

[n])

A

n

ECE 5675 Phase-Lock Loops with Applications 1-21

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

( )

M

NCO

Im{ }

Loop

Filter

F z ( )

e

j

0

nT

n [ ] + ( )

x n [ ]

Mth Power Loop

NCO

Measure Angle

x n [ ]

e

j

0

nT

n [ ] + ( )

Loop

Filter

F z ( )

y n [ ] A

n

Hard BIt

Decisions

Phase Detector

Decision Directed Loop

1-22 ECE 5675 Phase-Lock Loops with Applications

1.10. APPLICATIONS OVERVIEW

Symbol/Bit Synchronization

VCO

Loop

Filter

F s ( )

Delay

LPF

Delay and Multiply Nonlinearity

Clock Output

x t ( )

Nonlinear lter clock recovery using a delay and multiply circuit

Abs( )

Loop

Filter

F s ( )

VCO

Abs( )

x t ( )

-

+

Sample

& Hold

Sample

& Hold

( ) t d

T

I & D

( ) t d

T

I & D

Early Clock

Late Clock

Early-late gate timing recovery

ECE 5675 Phase-Lock Loops with Applications 1-23

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

Interpolation

x mT

s

( )

T

s

sample spacing

1

f

s

--- = =

Matched

Filter

Control

Loop

Filter

F z ( )

Timing

Estim.

y mT

s

( ) y

I

t

n

( )

To Data

Detector

T < symbol period =

Non-synchronous

sampled signal

A DSP based non-synchronous clock recovery loop

Spread Spectrum Code Synchronization

Splitter

Loop

Filter

F s ( )

VCO

Spreading

Code Gen.

-

+

Early Code

Late Code

Input s(t)

Prompt Code

Spreading

Code Clock

Delay-Lock

Discriminator

Delay-lock Loop

1-24 ECE 5675 Phase-Lock Loops with Applications

1.10. APPLICATIONS OVERVIEW

1.10.2 Frequency Synthesis Applications

In wireless applications frequency synthesizers provide local os-

cillators for up and down conversion of modulated signals

Any radio based electronics that operates over multiple frequen-

cies, likely incorporates a frequency synthesizer

The transmitter and receiver of a cellular telephony handset is

shown below

D

u

p

l

e

x

e

r

BPF

UHF

PLL

LO

Power

Ampl.

Driver

90

VHF

PLL

LO

F

r

o

m

D

A

C

s

IF IQ Modulator

VGA

Isolator

RF Mixer

Image

Reject

Filter

90

T

o

A

D

C

s

IF IQ Demodulator

LPF

LPF

BPF

LNA

RF Mixer

VGA

Frequency

Synthesizers

Wireless handset transmitter and receiver RF signal processing

Direct Synthesis

Use mixing (multiplication) to build up the desired frequency

and a division of a single reference frequency

ECE 5675 Phase-Lock Loops with Applications 1-25

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

Rapid switching time is one of the features

Bulky rf hardware (switches, mixers, lters) is a disadvan-

tage

Spurious frequency generation can be a big problem

Indirect Synthesis

Indirect synthesis is another name for PLL frequency synthesis

A basic PLL synthesizer is the following

Loop

Filter

F s ( )

VCO

N

1

N

2

Reference

Oscillator

f

ref

f

ref

N

1

-------

f

out

N

2

--------

f

out

f

out

f

ref

N

2

N

1

------

=

General indirect synthesis using a DPLL

With indirect synthesis all by itself, large divide ratios are re-

quired to obtain ne resolution

Being able to set the divide ratio to a fractional, non-integer

value would solve this problem

The basis of the fractional-N method is to alter the divide ratio

N

2

between two values

Direct Digital Synthesis (DDS)

DDS is a DSP based method of using an N-bit accumulator to

generate a phase ramp corresponding to one clock cycle

1-26 ECE 5675 Phase-Lock Loops with Applications

1.10. APPLICATIONS OVERVIEW

The accumulator increments the phase by an equivalent amount

of each clock cycle

The output frequency is given by

f

out

=

N

i

2

N

f

ref

where N

i

corresponds to the phase step size

The minimum frequency change is

f =

f

ref

2

N

Accumulator

N - Bits

Memory (LUT)

of cos()

DAC LPF

Address of

Shift

Out

Invert

Accumulate

Input Clock at f

ref

f

ref

A simple direct digital synthesis scheme

Hybrid Methods

To meet various design goals combinations of the above method

may be employed

Several PLL synthesizers can be combined to create a multi-

loop synthesizer

DDS and a PLL can be combined to achieve ne step sizes,

yet the wide tuning range of a PLL

ECE 5675 Phase-Lock Loops with Applications 1-27

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

1.11 Simulation Examples

In this section several working PLL based circuits/systems will be

demonstrated using a variety of software tools. The intent is to give

a avor of what options are available in the way of simulation ap-

proaches for PLL based designs.

Example 1.1: Behavioral Level Modeling using XSpice

Analog circuit designers are well acquainted with Spice. The

challenge with PLL designs is to effectively make use of behavioral

modeling capabilities of modern Spice implementations. One such

extension to Spice is XSpice, developed at Georgia Tech.

We will soon learn that the full simulation of a PLL is numer-

ically intensive because waveform delity at the VCO level is

required, yet the bandwidth of the closed loop tracking system

is much smaller than the VCO quiescent frequency

In this example full waveform delity is preserved, but behav-

ioral models, as opposed to detailed circuit models, are used for

most of the loop

The VCO quiescent frequency is chosen to be just 5000 Hz and

the PLL closed-loop noise equivalent bandwidth is 100 Hz

1-28 ECE 5675 Phase-Lock Loops with Applications

1.11. SIMULATION EXAMPLES

0

V1

0.8836u

C1

AFM_Source

in1

in2

out

APhase_Det

AVCO

in out

AD_Freq_LPF

8.488k

R1

15

V3

15

V2

XLoop_Filt

10k

R2

VCO_Input

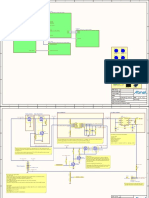

Analog PLL (LPLL) schematic using XSpice behavioral modeling

The input signal source and VCO are both created using a volt-

age controlled sinusoid generator

The phase detector is an ideal multiplier and to remove the dou-

ble frequency term following the phase detector, a transfer func-

tion behavioral level model is used

The transfer function associated with the block AD FREQ LPF

is H(s) = 1000/(s + 1000), a lowpass lter with cutoff fre-

quency f

c

= 1000/(2) = 159.15 Hz

A loop lter of the form F(s) = (1 +s

2

)/(s

1

) is implemented

in circuit form using an Op-amp

The input sinusoid is initially at 5000 Hz and the VCO quiescent

frequency is also at 5000 Hz

At 40 ms the input frequency is stepped to 5100 Hz, a 100 Hz

frequency step, (the VCO gain is K

v

= 100 Hz/v)

ECE 5675 Phase-Lock Loops with Applications 1-29

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

Input and VCO Signals

Time (s)

+39.600m +39.800m +40.000m +40.200m +40.400m +40.600m

(V)

-1.000

-500.000m

0.0

+500.000m

TIME_SimRes1 -805.637m Input +569.939m VCO Output +1.136e+039

D(TIME_SimRes1) -1.107 D(VCO Output) +1.136e+039

90

o

up to t = 40 ms Input initially 100 Hz faster than VCO

The input sinusoid and the VCO output near t = 40 ms

The loop breaks lock and acquires in both frequency and phase-

lock via the nonlinear pull-in process

In about 70 ms the loop has settled (t = 110 ms)

In addition to transient or time domain modeling, Spice can be

used in the AC analysis mode to characterize open and closed

loop magnitude and phase response of linearized loops

The AC analysis mode also provides for detailed noise analysis

and the incorporation of phase noise models of the input source

oscillator and VCO

Ultimately closed-loop phase noise performance can be obtained

using actual circuit elements mixed with behavioral level models

1-30 ECE 5675 Phase-Lock Loops with Applications

1.11. SIMULATION EXAMPLES

VCO Control Voltage During 100 Hz Frequency Step

Time (s)

0.0 +20.000m +40.000m +60.000m +80.000m +100.000m +120.000m +140.000m

(V)

-200.000m

0.0

+200.000m

+400.000m

+600.000m

+800.000m

+1.000

+1.200

TIME +1.047e-306 v(VCO_Input) -1.000 D(TIME) +1.047e-306

D(v(VCO_Input)) -1.000

100 Hz Frequency

Step at 40 ms

Loop has ~settled

Input and VCO

both at 5000 Hz,

but locking at 90

o

VCO control voltage in response to a 100 Hz frequency step at t = 40 ms

Example 1.2: Baseband PLL in XSpice

In this example high frequency modeling, e.g., the individual wave-

formcycles of the input and VCOare removed by abstracting to what

is known as a baseband PLL model. This model will be developed

in Chapter 2 of the course notes.

The multiplier phase detector is replaced by the phase difference

block followed by a nonlinearity, here a sin function

To model a frequency step an integrator at the input converts

frequency to phase with a 2 factor times a frequency deviation

constant

ECE 5675 Phase-Lock Loops with Applications 1-31

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

The VCO, which is like a frequency modulator, is modeled as

an integrator with gain constant 2 K

v

, where K

v

= 100 Hz/v

in this case

Freq. Step

Input

Integrate -->

Phase Ramp

VCO = Integrator

Gain = 2*pi*Kv

Nonlinear source:

v = sin(v(8))

0

V1

0.8836u

C1

B1

1

2

out +

A1

in out

A2_INTEGRATE

in out

A1_INTEGRATE

8.488k

R1

15

V3

15

V2

XLoop_Filt

10k

R2

VCO_Input

1K

R3

in out

A_LPF

Node 8

Baseband analog PLL schematic using XSpice behavioral modeling

A 100 Hz frequency step is applied at the input at t = 40 ms as

in the previous example

Loop transient pull-in response is slightly different than be-

fore, but the total time required to settle is very similar

The waveform plotted is the VCO control voltage inverted to

account for the + sign in the summer block, and then scaled by

100 to scale the waveform to instantaneous frequency deviation

in Hz

1-32 ECE 5675 Phase-Lock Loops with Applications

1.11. SIMULATION EXAMPLES

VCO Input with 100 Hz Frequency Step

Time (s)

0.0 +20.000m +40.000m +60.000m +80.000m +100.000m +120.000m +140.000m

Frequency

0.0

+50.000

+100.000

+150.000

TIME -1.000 Inverted VCO Input -1.000 D(TIME) -2.970e+222

D(Inverted VCO Input) -1.000

Transient is

slightly different,

but very sensitive

to parameters

100 Hz

Step ~settled

VCO input in response to a 100 Hz frequency step

Example 1.3: Analog PLL Modeling in MATLAB Simulink

Spice is useful for modeling certain aspects of PLL circuits, but

there are times when a complete abstraction to the system level is the

most efcient means to validate a design. In this example Simulink,

which is an odd-on to MATLAB (included with the student version)

is used.

The Egan text includes MATLAB m-les for complete com-

mand line nonlinear PLL simulation

Simulink is a block diagram simulation environment, so PLL

simulation here is more visual

ECE 5675 Phase-Lock Loops with Applications 1-33

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

Simulink alone does not provide direct support for PLLs and

synchronization

If you add to Simulink the Signal Processing toolbox, the

DSP blockset, the Communication toolbox, and nally the

Communication blockset, you have some basic PLL building

blocks, e.g. a VCO

With the basic Simulink library that comes with the stu-

dent version of Simulink PLL simulation requires a bit more

work, but is possible

In the example given here Simulink is used to model a band-

pass analog PLL with 5 kHz center frequency and 100 Hz loop

bandwidth, as in Example 1.1

VCO

Voltage-Controlled

Oscillator

7.5e-3s+1

8.836e-3s

Transfer Fcn1

1000

s+1000

Transfer Fcn

lpf_output

To Workspace1

vco_input

To Workspace

Step

Product

VCO

FM Source with

f0 = 5000 Hz

MATLAB Simulink model of an analog PLL at 5 kHz

The rst-order lowpass lter following the multiplier phase de-

tector is used to remove the double frequency term at 10 kHz

A 100 Hz frequency step is applied to the input at 40 ms

Results very similar to the XSpice model of Example 1.1 are

obtained

1-34 ECE 5675 Phase-Lock Loops with Applications

1.11. SIMULATION EXAMPLES

0 20 40 60 80 100 120

0.2

0

0.2

0.4

0.6

0.8

1

1.2

Time in ms

V

o

l

t

a

g

e

VCO Input in Response to a 100 Hz Frequency Step

Step applied at 40 ms

~settled

VCO input in response to a 100 Hz frequency step

A small amount of noise can be seen on the VCO control signal

This noise in reality is the double frequency term, at 10 kHz,

leaking through the loop lter

This leakage will modulate the VCO and produce annoying FM

sidebands or spurs

This leakage is even more evident at the output of the lowpass

lter

ECE 5675 Phase-Lock Loops with Applications 1-35

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

0 20 40 60 80 100 120

0.5

0.4

0.3

0.2

0.1

0

0.1

0.2

0.3

0.4

0.5

Time in ms

V

o

l

t

a

g

e

LPF Output in Response to a 100 Hz Frequency Step

Waveform is noisy due

to double frequency

term (10kHz) still present

f

c

5000 Hz =

Phase detector lowpass lter output showing 10 kHz leakage

Example 1.4: Analog PLL Modeling in VisSim

In this example we consider the block diagram modeling tool Vis-

Sim/Comm from Visual Solutions Inc. With the readily available

Communications library support for PLL simulation is very conve-

nient.

VisSim is similar to Simulink in that it is a block environment

for dynamic system simulation

With the VisSim/Comm many powerful communications blocks

are available, and complete complex baseband simulation blocks

are also dened

1-36 ECE 5675 Phase-Lock Loops with Applications

1.11. SIMULATION EXAMPLES

VisSim also has an interface with MATLAB, so results can be

directly imported in to MATLAB, or MATLAB can perform cal-

culations

Standard loop lters can be dened using loop lter blocks which

directly calculate the required time constants, e.g.,

1

and

2

fromsystemlevel specications, e.g., loop bandwidth and damp-

ing factor

In this rst VisSim example we repeat the original XSpice ex-

ample of an analog PLL at center frequency of 5000 Hz and loop

bandwidth of 100 Hz

sig

ph

VCO

sig

ph

VCO

*

Loop Filter

2nd Order PLL

1

1000

s+1000

FM Source

Fc = 5 kHz, 100 Hz/v

VisSim/Comm model of an analog PLL at 5 kHz

ECE 5675 Phase-Lock Loops with Applications 1-37

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

The VCO input signal (voltage) is measured when a 100 Hz fre-

quency step is applied at 40 ms

The results are consistent with the previous XSpice and Simulink

results

Note also that in VisSim the block diagram and graph windows

are wired together

VCO Input

VCO Input 100 Hz Step Response

Time (sec)

0 .01 .02 .03 .04 .05 .06 .07 .08 .09 .1 .11 .12

-.1

.1

.3

.5

.7

.9

1.1

1.3

Step applied at 40 ms

~settled

VCO input in response to a 100 Hz frequency step

Example 1.5: Complex Baseband PLL Modeling in VisSim

In digital signal processing based implementations, common place

in digital communications, the PLL is likely top operate on complex

signals, i.e., complex baseband. VisSim supports this via a complex

VCO block and other complex processing blocks. In this example a

complex baseband analog PLL is constructed.

1-38 ECE 5675 Phase-Lock Loops with Applications

1.11. SIMULATION EXAMPLES

A complex baseband PLL has the advantages of the baseband

PLL of Example 1.1, but takes complex signal inputs of the form

s(t ) = Ae

j ]2 f

c

t +(t )]

not phase inputs

In this example a 2nd-order loop is constructed with center fre-

quency at f

c

= 0 (DC) having a loop bandwidth of 25 Hz

A frequency step of 50 Hz is applied at t = 0 and both the sinu-

soidal phase detector output and VCO input signals are observed

The entire VisSimsimulation block diagramand plots are shown

below

Z

ph

VCO

Z1

Z2

Z

Cplx

Mult

Z

ph

VCO

Complex Baseband Analog PLL

Phase Det ect or Out put

Time (msec)

0 50 100 150 200 250 300 350 400 450 500 550 600 650 700 750 800

V

o

l

t

a

g

e

-1.00

-.75

-.50

-.25

0

.25

.50

.75

1.00

Z

re

im

Cplx t o

Re/Im

Z Z

Cplx

Conj

Loop Filt er

2nd Order PLL

Complex Baseband Analog PLL

VCO Input

Time (msec)

0 50 100 150 200 250 300 350 400 450 500 550 600 650 700 750 800

-.1

0

.1

.2

.3

.4

.5

.6

50 Hz Freq.

Step

25 Hz

Bandwidth

Complex baseband PLL with a 50 Hz frequency step input

ECE 5675 Phase-Lock Loops with Applications 1-39

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

Example 1.6: Bit Synch Modeling in VisSim

Clock recovery in baseband digital communications frequency em-

ploys a PLL.

In this simulation example the assumed bit rate is 100 bps

A delay and multiply (D&M) circuit is used to generate a spec-

tral line from the NRZ (non-return-to-zero) binary bit stream

The power spectrum of the D&M output is also computed

ck

sy m

ck

Random

Sym (2)

2*$1-1

*

Delay (0.005 sec)

Trg

Z

Trg

Mag

Ph

f req

1024 pt. (x20)

Power Spectral

Density(dBm/Hz)

re

im

Z

Re/Im

to Cplx

Impulse

t= 0.

sig

ph

VCO

*

5th Order 1 Hz

Butterworth Lowpass

Loop Filter

2nd Order PLL

+

+

sig

ph

VCO

crossDetect

Delay & Multiply

Nonlinearity

Averaged Periodogram

Spectrum Analyzer to Observe

D&M Output

2nd-Order PLL to

Track the Clock

Frequency

Loop

Frequency

Disturbance

Frequency Step

to the Clock of the

NRZ Random

Bit Stream

Filter D&M Self Noise

Delay-and-multiply bit synch block diagram

1-40 ECE 5675 Phase-Lock Loops with Applications

1.11. SIMULATION EXAMPLES

A 2nd-order PLL with loop bandwidth of 1 Hz is congured

with the D&M output as the input signal source

To test the acquisition and tracking of the bit synch a 1 Hz fre-

quency step is applied as a loop disturbance

Delay and Multiply Bit Synch

D&M Power Sprctrum

-400 -300 -200 -100 0 100 200 300 400

P

S

D

i

n

d

B

-40

-30

-20

-10

0

10

Delay and Multiply Bit Synch

VCO Input

Time (sec)

0 5 10 15 20 25 30

-.050

-.025

0

.025

.050

.075

.100

.125

Frequency in Hz

1 Hz Step Applied

Initial

Acquisition

Desired Clock

Spectral Line

R

b

100 bps =

D&M output PSD and VCO input for a frequency step

ECE 5675 Phase-Lock Loops with Applications 1-41

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

Example 1.7: Carrier Tracking in VisSim

In this example a complex baseband implementation of carrier

phase tracking is described.

The modulation scheme is binary phase-shift keying (BPSK)

with square-root raised cosine (SRC) pulse shaping

Pulse shaping lter FIR coefcients are imported from MAT-

LAB, but could also be designed directly in the VisSim/Comm

environment

The bit rate is 10 bps and the carrier frequency is nominally 0

Hz

To eliminate clutter a hierarchical block diagram is created

Trg

Z

Trg

Mag

Ph

freq

1024 pt . (x14)

Power Spect ral

Densit y(dBm/Hz)

Impulse

t = 0.

Z

ph

VCO

Z1

Z2

Z

Cplx

Mult

re

im

Z

Re/Im

t o Cplx

Shaped PAM

File FIR

..\src10_35.dat

Carrier

Recovery

Shaped BPSK with Costas carrier phase tracking

The modulator sub-block (Shaped PAM) is created to handle

the pulse shaping

1-42 ECE 5675 Phase-Lock Loops with Applications

1.11. SIMULATION EXAMPLES

The Carrier Recovery block houses a complex baseband Costas

loop having a 2nd-order loop lter with loop bandwidth of 0.5

Hz

A 0.5 Hz frequency step is applied 2 seconds into the simulation

The carrier recovery block contains a graphical display showing

how the loop acquires lock following the frequency step

Z

ph

VCO

Z1

Z2

Z

Cplx

Mult

Z Z

Cplx

Conj

Z

re

im

Cplx t o

Re/Im

Loop Filt er

2nd Order PLL

*

Plot

Time (sec)

0 2.5 5 7.5 10 12.5 15 17.5 20 22.5 25

-.02

-.01

0

.01

.02

.03

.04

.05

.06

5t h Order 1 Hz

But t erwort h Lowpass

Carrier recovery block showing the VCO input signal

A matched lter having an identical SRC lter coefcients are

applied to the received signal following carrier recovery

Shown below is an eye plot at the output of this lter

The transmitted power spectrum is also computed

ECE 5675 Phase-Lock Loops with Applications 1-43

CHAPTER 1. COURSE INTRODUCTION/OVERVIEW

Eye Plot

Time (sec)

0 .02 .04 .06 .08 .1 .12 .14 .16 .18 .2

-20

-15

-10

-5

0

5

10

15

20

PSD in dBm/Hz

-40 -35 -30 -25 -20 -15 -10 -5 0 5 10 15 20 25 30 35 40

-20

-15

-10

-5

0

5

10

15

20

25

Eye plot of the received BPSK and the transmit PSD

1-44 ECE 5675 Phase-Lock Loops with Applications

You might also like

- BS en 15380-5Document22 pagesBS en 15380-5rohita kumar dahNo ratings yet

- Circuits I Have KnownDocument189 pagesCircuits I Have Knownjack266No ratings yet

- ADPLL All Digital Phase Locked Loop CircuitsDocument27 pagesADPLL All Digital Phase Locked Loop CircuitsSteven YuNo ratings yet

- Parallel Port Interfacing Using Assembly LanguageDocument21 pagesParallel Port Interfacing Using Assembly Languageamon_abilar100% (1)

- Cavallo - Using Matlab Simulink and Control Toolbox - ToC (1996)Document7 pagesCavallo - Using Matlab Simulink and Control Toolbox - ToC (1996)hindukusc80No ratings yet

- Ezwave UrDocument738 pagesEzwave Urshakespirit100% (1)

- IVCAD MT930M1M2A OM HEMT ModelDocument65 pagesIVCAD MT930M1M2A OM HEMT ModellotfiNo ratings yet

- Test Taker Score Report: July 25, 2020 Test Date Scores ScoresDocument2 pagesTest Taker Score Report: July 25, 2020 Test Date Scores Scoresfrederic sateraNo ratings yet

- Embedded DSP Processor Design: Application Specific Instruction Set ProcessorsFrom EverandEmbedded DSP Processor Design: Application Specific Instruction Set ProcessorsNo ratings yet

- RF Analog Impairments Modeling for Communication Systems Simulation: Application to OFDM-based TransceiversFrom EverandRF Analog Impairments Modeling for Communication Systems Simulation: Application to OFDM-based TransceiversNo ratings yet

- 16 IIR Filter DesignDocument23 pages16 IIR Filter DesignManisman ParidaNo ratings yet

- A Fully Differential Phase-Locked Loop With Reduced Loop Bandwidth VariationDocument248 pagesA Fully Differential Phase-Locked Loop With Reduced Loop Bandwidth Variationreshmii_123No ratings yet

- ADPLLDocument17 pagesADPLLsurajdash100% (1)

- High-Speed Serial I/O Made Simple: A Designers' Guide, With FPGA ApplicationsDocument210 pagesHigh-Speed Serial I/O Made Simple: A Designers' Guide, With FPGA ApplicationseliomayNo ratings yet

- DSP Basics ManualDocument70 pagesDSP Basics ManualpavithraNo ratings yet

- OSCILLATORSDocument8 pagesOSCILLATORSapi-26100966100% (2)

- Tutorial On Parallel Port InterfacingDocument7 pagesTutorial On Parallel Port InterfacingVasilis TsekourasNo ratings yet

- Feedback CircuitsDocument47 pagesFeedback CircuitsPatrick SerandonNo ratings yet

- Introduction To DSPDocument59 pagesIntroduction To DSPSiony BelloNo ratings yet

- DSP Lab Manual Upto 3 Cycles PDFDocument45 pagesDSP Lab Manual Upto 3 Cycles PDFDinesh PalavalasaNo ratings yet

- 0471317780Document21 pages0471317780haribabu448No ratings yet

- Colpitts Oscillator Using Op Amp PDFDocument2 pagesColpitts Oscillator Using Op Amp PDFStewartNo ratings yet

- Z TransformsDocument25 pagesZ TransformsSujesh ShettyNo ratings yet

- Phillips D.image Processing With CDocument816 pagesPhillips D.image Processing With Capi-3701770100% (2)

- MOS+Op Amp+DesignDocument14 pagesMOS+Op Amp+Designaravind2612krishnaNo ratings yet

- Phase Locked LoopDocument11 pagesPhase Locked LoopLadmirIllitchenNo ratings yet

- Filter DesignDocument42 pagesFilter DesignShivanshu Trivedi100% (1)

- Digital PLLDocument6 pagesDigital PLLPeter Podhoranský100% (1)

- Charge Pump Low Voltage Op AmpDocument2 pagesCharge Pump Low Voltage Op Ampappropose100% (1)

- Design of Analog Filters ShauumanDocument7 pagesDesign of Analog Filters ShauumanReem El-Adawi50% (4)

- Microwave Differential Circuit Design Using Mixed-Mode S-Parameters William R. Eisenstadt, Bob Stengel, Bruce M. ThompsonDocument247 pagesMicrowave Differential Circuit Design Using Mixed-Mode S-Parameters William R. Eisenstadt, Bob Stengel, Bruce M. Thompsondndmicrowave100% (1)

- Pico C (English) - Part1Document6 pagesPico C (English) - Part1RenéNo ratings yet

- Ads Circuit Design CookbookDocument124 pagesAds Circuit Design CookbookThiên LuânNo ratings yet

- CDR Linear ModelDocument139 pagesCDR Linear ModelMohamed MegahedNo ratings yet

- Sigma Delta Modulator NutshellDocument5 pagesSigma Delta Modulator NutshellZubair MohammedNo ratings yet

- Parallel PortDocument113 pagesParallel Portapi-3701797100% (6)

- Effect of Sigma Delta Modulator On The Phase Noise of PLL2Document12 pagesEffect of Sigma Delta Modulator On The Phase Noise of PLL2Hossein Rahmanian KooshkakiNo ratings yet

- Analog Circuit DesignDocument9 pagesAnalog Circuit DesignTony VuNo ratings yet

- Digital Signal Processing NotesDocument189 pagesDigital Signal Processing NotesAkshansh Chaudhary67% (3)

- Fixed Point Signal Processing by W PaddgetDocument133 pagesFixed Point Signal Processing by W Paddgettest mail100% (1)

- Comparative Analysis of Different Architectures of CMOS ComparatorDocument4 pagesComparative Analysis of Different Architectures of CMOS Comparatorj4everNo ratings yet

- Inverse Laplace Transform of A ConstantDocument4 pagesInverse Laplace Transform of A Constanttutorciecle1230% (1)

- SAMD21 Xplained Pro Design Documentation Release Rev2Document16 pagesSAMD21 Xplained Pro Design Documentation Release Rev2Dimas Agung DwiparonaNo ratings yet

- Design and Simulation of Power ConvertersDocument48 pagesDesign and Simulation of Power ConvertersHoang NgoNo ratings yet

- Modern Arm Assembly Language Programming: Covers Armv8-A 32-bit, 64-bit, and SIMDFrom EverandModern Arm Assembly Language Programming: Covers Armv8-A 32-bit, 64-bit, and SIMDNo ratings yet

- Practical System Programming with C: Pragmatic Example Applications in Linux and Unix-Based Operating SystemsFrom EverandPractical System Programming with C: Pragmatic Example Applications in Linux and Unix-Based Operating SystemsNo ratings yet

- Digital Signal Processing Systems: Implementation Techniques: Advances in Theory and ApplicationsFrom EverandDigital Signal Processing Systems: Implementation Techniques: Advances in Theory and ApplicationsNo ratings yet

- Millimeter-Wave Digitally Intensive Frequency Generation in CMOSFrom EverandMillimeter-Wave Digitally Intensive Frequency Generation in CMOSNo ratings yet

- ASUS ExpertCenter D500MA DatasheetDocument3 pagesASUS ExpertCenter D500MA Datasheetscoci jarmenNo ratings yet

- Web DevelopmentDocument28 pagesWeb DevelopmentRajnish 008No ratings yet

- Haipick A42T: Telescopic Lift ACRDocument2 pagesHaipick A42T: Telescopic Lift ACRKit WooNo ratings yet

- DatabaseDocument23 pagesDatabasegemechu gebisaNo ratings yet

- A Challenge Called Boot Time - WitekioDocument5 pagesA Challenge Called Boot Time - Witekiomrme44No ratings yet

- DL Slides 1Document63 pagesDL Slides 1ABI RAJESH GANESHA RAJANo ratings yet

- Blessing Komponen Accesories 08 Nop 2021Document229 pagesBlessing Komponen Accesories 08 Nop 2021BayuNo ratings yet

- Hybrid Synchronous / Asynchronous DesignDocument115 pagesHybrid Synchronous / Asynchronous DesignMalka RavikrishnaNo ratings yet

- Book of Abstracts SIAS 2018Document69 pagesBook of Abstracts SIAS 2018adereNo ratings yet

- CH 08 Exception HandlingDocument24 pagesCH 08 Exception HandlingTabassum MaktumNo ratings yet

- CodingBat AnswersDocument12 pagesCodingBat Answersblueb3rryi3No ratings yet

- Textbook Ebook Using R For Data Analysis in Social Sciences A Research Project Oriented Approach Li All Chapter PDFDocument43 pagesTextbook Ebook Using R For Data Analysis in Social Sciences A Research Project Oriented Approach Li All Chapter PDFclarence.trites149100% (6)

- Bangladesh Public Service Commission: 35th BCS Examination 2014Document2 pagesBangladesh Public Service Commission: 35th BCS Examination 2014ParthaSharathiSarkarNo ratings yet

- Ieee-80 Standard Substation Grid Calculation ExamplesDocument16 pagesIeee-80 Standard Substation Grid Calculation ExamplesAditya PundirNo ratings yet

- COMM1030 Shakira Semester1 2021 2022Document15 pagesCOMM1030 Shakira Semester1 2021 2022aina safiyyaNo ratings yet

- Ocean ProtocolDocument8 pagesOcean ProtocolmariusNo ratings yet

- Emu LogDocument6 pagesEmu LogSuresh KumarNo ratings yet

- BrahMos Recruitment 2023Document3 pagesBrahMos Recruitment 2023SammyNo ratings yet

- Oracle WebLogic ServerDocument20 pagesOracle WebLogic ServerIrfan AhmadNo ratings yet

- Unit 10 LOs and Criteria TableDocument2 pagesUnit 10 LOs and Criteria TableIfu QueenNo ratings yet

- Pfsense LoadbalanceDocument25 pagesPfsense LoadbalanceArieClaassens100% (1)

- GPFS CommandsDocument2 pagesGPFS CommandsAndrés HernándezNo ratings yet

- Steganography & Biometrics: Lakshmi Narayana Inampudi, M.Tech, (PHD)Document40 pagesSteganography & Biometrics: Lakshmi Narayana Inampudi, M.Tech, (PHD)deepthi aluriNo ratings yet

- Frontend Handbook - React - Testing Best PracticesDocument18 pagesFrontend Handbook - React - Testing Best PracticeszentropiaNo ratings yet

- Eth Account Readthedocs Io en StableDocument28 pagesEth Account Readthedocs Io en StableFery FerdiansyahNo ratings yet

- Computer Graphics MCQ - BDocument6 pagesComputer Graphics MCQ - BAmbika JaiswalNo ratings yet

- 3.tabel & Form Kredit Aeon MultiteknoDocument13 pages3.tabel & Form Kredit Aeon MultiteknoI'am SeNoNo ratings yet

- C++ Session 01 DocumentDocument321 pagesC++ Session 01 DocumentArun KumarNo ratings yet