Professional Documents

Culture Documents

Pcmcia Amd D-Series LF

Uploaded by

Jesus Lozano0 ratings0% found this document useful (0 votes)

31 views35 pagesC-ONE PCMCIA SERIES-D FLASH MEMORY CARD ii Documentation History Version Description Date Written By 1. New Issue Aug. 2006 Greg Liu.

Original Description:

Original Title

Pcmcia Amd D-series Lf

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentC-ONE PCMCIA SERIES-D FLASH MEMORY CARD ii Documentation History Version Description Date Written By 1. New Issue Aug. 2006 Greg Liu.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

31 views35 pagesPcmcia Amd D-Series LF

Uploaded by

Jesus LozanoC-ONE PCMCIA SERIES-D FLASH MEMORY CARD ii Documentation History Version Description Date Written By 1. New Issue Aug. 2006 Greg Liu.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 35

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

i

LINEAR FLASH MEMORY CARD

SERIES-D (FxDxxx)

Product Specification

Preliminary

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

ii

Documentation History

Version Description Date Written By

1.0 New Issue Aug. 2006 Greg Liu

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

iii

Contents

1. FEATURES....................................................................................................................................................................................... 1

2. GENERAL DESCRIPTION............................................................................................................................................................ 1

3. PRODUCT LIST.............................................................................................................................................................................. 3

4. BLOCK DIAGRAM......................................................................................................................................................................... 4

5. PIN CONFIGURATION (C1FLA32M5) ....................................................................................................................................... 5

6. PIN DESCRIPTION......................................................................................................................................................................... 5

7. PIN LOCATION............................................................................................................................................................................... 6

8. RECOMMENDED OPERATING CONDITIONS........................................................................................................................ 6

9. ABSOLUTE MAXIMUM RATING * ............................................................................................................................................ 6

10. COMMON MEMORY FUNCTION TABLE................................................................................................................................ 7

11. ATTRIBUTE MEMORY FUNCTION TABLE............................................................................................................................ 7

12. COMMAND DEFINITION............................................................................................................................................................. 8

13. EMBEDDED MODE ERASE / PROGRAM ALGORITHM..................................................................................................... 11

14. DATA POLLING ALGORITHM................................................................................................................................................ 12

15. TOGGLE BIT ALGORITHM...................................................................................................................................................... 13

16. BYTE-WIDE PROGRAMMING ALGORITHM...................................................................................................................... 14

17. BYTE-WIDE ERASE ALGORITHM.......................................................................................................................................... 16

18. WORD-WIDE PROGRAMMING ALGORITHM..................................................................................................................... 18

19. WORD-WIDE ERASE ALGORITHM........................................................................................................................................ 20

20. TUPLE INFORMATION FOR SERIES-D FLASH CARD....................................................................................................... 22

21. DC ELECTRICAL CHARACTERISTICS.................................................................................................................................. 24

22. AC ELECTRICAL CHARACTERISTICS.................................................................................................................................. 25

23. READ CYCLE (COMMON MEMORY) ..................................................................................................................................... 25

24. WRITE/ERASE CYCLE (COMMON MEMORY) .................................................................................................................... 25

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

iv

25. WRITE/ERASE CYCLE (COMMON MEMORY) (CE* CONTROLLED)............................................................................ 26

26. READ CYCLE TIMING DIAGRAM (COMMON MEMORY)................................................................................................ 27

27. WRITE CYCLE TIMING DIAGRAM (COMMON MEMORY) ............................................................................................. 28

28. AC ELECTRICAL CHARACTERISTICS ( ATTRIBUTE MEMORY ) ................................................................................ 29

29. READ CYCLE ( ATTRIBUTE MEMORY ) ............................................................................................................................... 29

30. WRITE CYCLE ( ATTRIBUTE MEMORY )............................................................................................................................. 29

31. READ CYCLE TIMING DIAGRAM ( ATTRIBUTE MEMORY ) ( REG*=VIL , WE*=VIH )........................................... 30

32. WRITE CYCLE TIMING DIAGRAM ( ATTRIBUTE MEMORY ) ( REG*=VIL ).............................................................. 30

33. OUTLINE DIMENSIONS (UNIT : MM)..................................................................................................................................... 31

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 1/30 9611V2

Features

PCMCIA / J EIDA standard Block structure

Memory Capacity : 4, 8, 16MB - 64KB / block for 8-bit operation

Byte(x8) / word(x16) data bus selectable - 64KW / block for 16-bit operation

Single 5V for erase/write/read operation 100000 write/erase cycles per block

Fast access time : 150ns (maximum) Automatic erase/write

Optional attribute memory : 8KB bytes EEPROM - 1 second per single memory block erase

Data polling and toggle bit feature for detection - random-address write to previously erased byte

of program or erase completion (8 s/byte)

Built-in write protect switch Credit card size : 54.0 x 85.6 x 3.3 (mm)

Commercial / Industrial grade

General Description

C-ONE's high performance PCMCIA series-D FLASH memory cards conform to the PCMCIA / J EIDA international

standard and consist of multiple AMD's or FUJ ITSU's 5V only 16M bits FLASH memory devices and decoder IC

mounted on a very thin printed circuit board using surface mounting technology.

This series Flash memory cards contain 64 to 512 independent device blocks. Each block can be individually erasable.

To support PCMCIA-compatible byte-wide operation , the flash array is divided into 64K x 8 bits device blocks. To

support PCMCIA-compatible word-wide operation , the devices are paired so that each accessible memory block is

64K words.

This series Flash memory cards offer portable , reprogrammable and nonvolatile solid-state storage media and can be

used for flexible integration into various system platforms with PCMCIA/J EIDA interface. With the extra and optional

8K bytes "attribute memory" space , the Card Information Structure (CIS) can be written into it by C-ONE or by

customer with standard format or customized requirements.

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 2/30 9611V2

Product Number Definition

X1 X2 X3 X4X5X6

Card Type

F =FLASH

A/M

N : No A/M

6 : With 8KB Read/Write A/M

9 : With 8KB Read Only A/M

Card Series

D =Series D

Memory Capacity

004 : 4MB

008 : 8MB

016 : 16MB

Note: A/M means attribute memory.

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 3/30 9611V2

Product List

Item Part Number Memory Capacity Attribute Memory

No. Bytes Words Size Status

1. FND004 4M 2M None None

2. FND008 8M 4M

3. FND016 16M 8M

4. F6D004 4M 2M 8KB E

2

PROM Readable /

5. F6D008 8M 4M Writable

6. F6D016 16M 8M 8

7. F9D004 4M 2M 8KB E

2

PROM Read only

8. F9D008 8M 4M

9. F9D016 16M 8M

Table 1 Cards with optional 8KB attribute memory

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 4/30 9611V2

Block Diagram

A0~A24

D0~D15

CE1*

CE2*

WE*

OE*

REG*

RDY/BSY*

BVD1*

BVD2*

VCC

Write protect switch

A1~A11

CE0*~CE15*

optional

Decoder

Address & I/O

Buffer

WP

Common memory

AMD (Fujitsu) 29F016 Flash memory IC

x2 (or x4, or x6, or x8, or x10, or x12,

or x14, or x16)

WE*

OE*

A0~A20

D0~D15

Attribute memory

CE*

WE*

OE*

A0~A10

D0~D7

Figure 1 Cards with optional 8KB attribute memory

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 5/30 9611V2

Pin Configuration (C1FLA32M5)

17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 Pin no.

V R W A A A A A O A C D D D D D G Pin Name

C Y E 1 1 8 9 1 E 1 E 7 6 5 4 3 N

C / * 4 3 1 * 0 1 D

B *

Y

*

34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 Pin No.

G

N

D

W

P

D

2

D

1

D

0

A

0

A

1

A

2

A

3

A

4

A

5

A

6

A

7

A

1

2

A

1

5

A

1

6

N

C

Pin Name

51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 Pin No.

V A A A A A N N N C D D D D D C G Pin Name

C 2 2 1 1 1 C C C E 1 1 1 1 1 D N

C 1 0 9 8 7 2 5 4 3 2 1 1 D

* *

68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 Pin No.

G C D D D B B R N N N N N A A A N Pin Name

N D 1 9 8 V V E C C C C C 2 2 2 C

D 2 0 D D G 4 3 2

* 1 2 *

* *

Table 2

Note :

*

mean low active

C1FLA04M5 series : A24, A23, A22 =NC

C1FLA06M5, C1FLA08M5 series : A24, A23 =NC

C1FLA12M5, C1FLA16M5 series : A24 =NC

for cards without attribute memory : pin16 , 61 =NC

Pin Description

Symbol Function I/O

A0-A24 Addresses I

D0-D15 Data Inputs/Outputs I/O

CE1*/CE2* Card Enable I

OE* Output Enable I

WE* Write Enable I

REG* Attribute Memory Enable I

WP Write-protect status Detect O

BVD1*/BVD2* Battery Voltage Detect O

RY/BY* Ready/Busy status O

CD1*/CD2* Card Detect (tied to GND internally) O

VCC +5 Volt Power Supply -

GND Ground -

NC No Connection -

Table 3

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 6/30 9611V2

Pin Location

Figure 2 Bottom View (Connector Side)

Recommended Operating Conditions

Parameter Symbol Min. Max. Unit

V

CC

Supply Voltage V

CC

4.5 5.5 V

Input High Voltage V

IH

2.4 VCC +0.3 V

Input Low Voltage V

IL

-0.3 0.8 V

Operating Temperature(Commercial) T

OPR

0 70 C

Operating Temperature(Industrial) T

OPR

-40 85 C

Table 4

Absolute Maximum Rating *

Parameter Symbol Value Unit

V

CC

Supply Voltage V

CC

-0.5 to +6.0 V

Input Voltage V

IN

-0.5 to V

CC

+0.3(6V max.) V

Output Voltage V

OUT

-0.5 to +6.0 V

Operating Temperature (Commercial) T

OPR

0 to +70 C

Operating Temperature (Industrial) T

OPR

-40 to +85 C

Storage Temperature T

STR

-40 to +125 C

Relative Humidity (non-condensing) H

UM

95(maximum) %

Table 5

*Comments

Stress above those listed under " Absolute Maximum Ratings " may cause permanent damage to the products. These

are stress rating only. Functional operation of these products at these or any other conditions above those indicated in

the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect product reliability.

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 7/30 9611V2

Common Memory Function Table

Function REG* CE2* CE1* A0 OE* WE* D15-D8 D7-D0

Standby X H H X X X High-Z High-Z

Byte Read H H L L L H High-Z Even Byte Data Out

H H L H L H High-Z Odd Byte Data Out

Word Read H L L X L H Odd Byte Data Out Even Byte Data Out

Odd Byte Only Read H L H X L H Odd Byte Data Out High-Z

Byte Write H H L L H L X Even Byte Data In

H H L H H L X Odd Byte Data In

Word Write H L L X H L Odd Byte Data In Even Byte Data In

Odd Byte Only Write H L H X H L Odd Byte Data In X

Table 6

Attribute Memory Function Table

Function REG* CE2* CE1* A0 OE* WE* D15-D8 D7-D0

Standby X H H X X X High-Z High-Z

Byte Read L H L L L H High-Z Even Byte Data Out

L H L H L H High-Z Invalid Data Out

Word Read L L L X L H Invalid Data Out Even Byte Data Out

Odd Byte Only Read L L H X L H Invalid Data Out High-Z

Byte Write L H L L H L X Even Byte Data In

L H L H H L X X

Word Write L L L X H L X Even Byte Data In

Odd Byte Only Write L L H X H L X X

Table 7

Notes :

1. L=V

IL

; H=V

IH

; X=don't care , can be either V

IH

or V

IL

.

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 8/30 9611V2

Command Definition

Embedded Bus First Bus Second Bus Third Bus Fourth Bus Fifth Bus Sixth Bus

Command Write Write Cycle Write Cycle Write Cycle Read / Write Write Cycle Write Cycle

Sequence Cycles Cycle

Req Addr* Data Addr* Data Addr* Data Addr* Data Addr* Data Addr* Data

Reset/Read 4 XXXXH AAH XXXXH 55H XXXXH F0H RA RD

Autoselect 4 XXXXH AAH XXXXH 55H XXXXH 90H 00H/02H 01H/3DH

Byte Write 4 XXXXH AAH XXXXH 55H XXXXH A0H PA PD

Segment Erase 6 XXXXH AAH XXXXH 55H XXXXH 80H XXXXH AAH XXXXH 55H XXXXH 10H

Block Erase 6 XXXXH AAH XXXXH 55H XXXXH 80H XXXXH AAH XXXXH 55H SA 30H

Block Erase Suspend Erase can be suspended during Block erase with Addr (don't care) , Data (B0H)

Block Erase Resume Erase can be resumed after suspend with Addr (don't care) , Data (30H)

Table 8 Even Byte Command Definitions

*Address for Memory Segment 0 (S0) only. Address for the higher even memory segments (S2-S16) =(Addr) +

(N/2)* 400000H where N =Memory Segment number (0) for 4Mbyte, N =(0, 2) for 8Mbyte, N =(0, 2, 4) for12

Mbyte, N =(0, 2, 4, 6) for 16 Mbyte, N =(0, 2, 4, 6, 8) for 20 Mbyte, N =(0, 2, 4, 6, 8, 10) for 24 Mbyte, N =

(0...12) for 28 Mbyte, N =(0...14) for 32 Mbyte.

Embedded Bus First Bus Second Bus Third Bus Fourth Bus Fifth Bus Sixth Bus

Command Write Write Cycle Write Cycle Write Cycle Read / Write Write Cycle Write Cycle

Sequence Cycles Cycle

Req Addr* Data Addr* Data Addr* Data Addr* Data Addr* Data Addr* Data

Reset/Read 4 XXXXH AAH XXXXH 55H XXXXH F0H RA RD

Autoselect 4 XXXXH AAH XXXXH 55H XXXXH 90H 00H/02H 01H/3DH

Byte Write 4 XXXXH AAH XXXXH 55H XXXXH A0H PA PD

Segment Erase 6 XXXXH AAH XXXXH 55H XXXXH 80H XXXXH AAH XXXXH 55H XXXXH 10H

Block Erase 6 XXXXH AAH XXXXH 55H XXXXH 80H XXXXH AAH XXXXH 55H SA 30H

Block Erase Suspend Erase can be suspended during Block erase with Addr (don't care) , Data (B0H)

Block Erase Resume Erase can be resumed after suspend with Addr (don't care) , Data (30H)

Table 9 Odd Byte Command Definitions

*Address for Memory Segment 1 (S1) only. Address for the higher odd memory segments (S3-S15) =(Addr) +((N-

1)/2)* 400000H +200000H where N =Memory Segment number (1) for 4Mbyte, N =(1, 3) for 8Mbyte, N =(1, 3,

5) for 12 Mbyte, N =(1...7) for 16 Mbyte, N =(1...9) for 20 Mbyte, N =(1...11) for 24 Mbyte, N =(1...13) for 28

Mbyte, N =(1...15) for 32 Mbyte.

Notes :

1. Address bit =X =Don't Care for all address commands except for Program Address (PA), Read Address (RA) and

Block Address (SA).

2. RA =Address of the memory location to be read.

PA =Address of the memory location to be programmed. Addresses are latched on the falling edge of the WE pulse.

SA =Address of the block to be erased. The combination of A17, A18, A19, A20, A21 will uniquely select any block

of a segment.

3. RD =Data read from location RA during read operation.

PD =Data to be programmed at location PA. Data latched is on the rising edge of the WE pulse.

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 9/30 9611V2

Embedded Bus First Bus Second Bus Third Bus Fourth Bus Fifth Bus Sixth Bus

Command Write Write Cycle Write Cycle Write Cycle Read / Write Write Cycle Write Cycle

Sequence Cycles Cycle

Req Addr* Data Addr* Data Addr* Data Addr* Data Addr* Data Addr* Data

Reset/Read 4 XXXXH AAAA XXXXH 5555 XXXXH F0F0 RA RW

Autoselect 4 XXXXH AAAA XXXXH 5555 XXXXH 9090 00H/02H 0101/3D3D

Byte Write 4 XXXXH AAAA XXXXH 5555 XXXXH A0A0 PA PW

Segment Erase 6 XXXXH AAAA XXXXH 5555 XXXXH 8080 XXXXH AAAA XXXXH 5555 XXXXH 1010

Block Erase 6 XXXXH AAAA XXXXH 5555 XXXXH 8080 XXXXH AAAA XXXXH 5555 SA 3030

Block Erase Suspend Erase can be suspended during block erase with Addr (don't care) , Data (B0H)

Block Erase Resume Erase can be resumed after suspend with Addr (don't care) , Data (30H)

Table 10 Word Byte Command Definitions

Notes :

1. Address bit =X =Don't Care for all address commands except for Program Address (PA), and Block Address

(SA).

2. RA =Address of the memory location to be read.

PA =Address of the memory location to be programmed. Addresses are latched on the falling edge of the WE pulse.

SA =Address of the block to be erased. The combination of A17, A18, A19, A20, A21 will uniquely select any

block of a segment.

3. RW =Data read from location RA during read operation.(Word Mode).

PW=Data to be programmed at location PA. Data latched is on the rising edge of the WE pulse. (Word Mode).

4. Address for Memory Segment Pair 0 (S0 and S1) only. Address for the higher odd memory segments Pair (S2, S3

=Pair 1, S4, S5 =Pair 2, S6, S7 =Pair 3 ....) is equal to (Addr) +M*( 40000H) where M =Memory Segment Pair

number.

5. Word =2 bytes =odd byte and even byte.

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 10/30 9611V2

Block A20 A19 A18 A17 A16 Address Range

0 0 0 0 0 0 000000H-00FFFFH

1 0 0 0 0 1 010000H-01FFFFH

2 0 0 0 1 0 020000H-02FFFFH

3 0 0 0 1 1 030000H-03FFFFH

4 0 0 1 0 0 040000H-04FFFFH

5 0 0 1 0 1 050000H-05FFFFH

6 0 0 1 1 0 060000H-06FFFFH

7 0 0 1 1 1 070000H-07FFFFH

8 0 1 0 0 0 080000H-08FFFFH

9 0 1 0 0 1 090000H-09FFFFH

10 0 1 0 1 0 0A0000H-0AFFFFH

11 0 1 0 1 1 0B0000H-0BFFFFH

12 0 1 1 0 0 0C0000H-0CFFFFH

13 0 1 1 0 1 0D0000H-0DFFFFH

14 0 1 1 1 0 0E0000H-0EFFFFH

15 0 1 1 1 1 0F0000H-0FFFFFH

16 1 0 0 0 0 100000H-10FFFFH

17 1 0 0 0 1 110000H-11FFFFH

18 1 0 0 1 0 120000H-12FFFFH

19 1 0 0 1 1 130000H-13FFFFH

20 1 0 1 0 0 140000H-14FFFFH

21 1 0 1 0 1 150000H-15FFFFH

22 1 0 1 1 0 160000H-16FFFFH

23 1 0 1 1 1 170000H-17FFFFH

24 1 1 0 0 0 180000H-18FFFFH

25 1 1 0 0 1 190000H-19FFFFH

26 1 1 0 1 0 1A0000H-1AFFFFH

27 1 1 0 1 1 1B0000H-1BFFFFH

28 1 1 1 0 0 1C0000H-1CFFFFH

29 1 1 1 0 1 1D0000H-1DFFFFH

30 1 1 1 1 0 1E0000H-1EFFFFH

31 1 1 1 1 1 1F0000H-1FFFFFH

Table 11 Memory Block Address Table for Memory Segment S0

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 11/30 9611V2

Embedded Mode Erase / Program Algorithm

Start

Write Embedded Mode Erase

Command Sequence

Data Poll from Device

Erasure Complete

Figure 3 Embedded Mode Erase Algorithm

Start

Write Embedded Mode Write

Command Sequence

Data Poll Device

Erasure Complete

Verify Byte

Last

Address

Increment Address

Y

Y

N

N

Figure 4 Embedded Mode Programing Algorithm in Byte-Wide Mode

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 12/30 9611V2

Data Polling Algorithm

Read Byte

(D0-D7)

Addr =VA

D7 =Data ?

D5 =1 ?

Y

Y

N

N

Start

Read Byte

(D0-D7)

Addr =VA

D7 =Data ?

Fail

Pass

Y

N

VA =Valid Address

VA =Byte addr for Write operation

VA =Any segment address during

segment erase operation

Figure 5

t

CH

t

OE

t

OEH

t

CE

t

DF

t

OH

High Z

D0 - D7

Valid Data

D0 - D6 =Invalid

D7 D7 = Valid Data

t

WHWH3 or 4

D0 - D6

D7

WE*

OE*

CE*

*D7 =Valid Data (The device has completed the Embedded operation).

*

Figure 6

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 13/30 9611V2

Toggle bit Algorithm

Read Byte

(D0-D7)

Addr ="don't care"

D6 =Toggle ?

D5 =1 ?

Y

Y

N

N

Start

Read Byte

(D0-D7)

Addr ="don't care"

D6 =Toggle ?

Fail

Pass

Y

N

Figure 7

t

OE

t

OEH

D0 - D7

Valid Data

D6 = Stop Toggling

WE*

OE*

CE*

Note:

*D6 stops toggling (The device has completed the Embedded operation).

D6 = Toggle D6 = Toggle

Data

(D0-D7)

*

Figure 8

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 14/30 9611V2

Byte-Wide Programming Algorithm

Begin

Programming

Initialization :

EF =0

Write PGM

Get ADRS/PD

VDAT =PD

Write ADRS/PGM

Write ADRS/VDAT

Wait 8 s

Read ADRS/FMD

FMD =VDAT

Begin software polling

subroutine (figure 10)

More Data

Program Complete

FMD =VDAT

Program Error

N

N

Y

Y

Y

N

Initialize Programming Variables :

EF =Error Flag

PGM =Embedded Byte Write Command

Sequence Cycle #1 - #3

ADRS =Appropriate address for memory segment

PD =Program Data

VDAT =Valid Data

FMD =Flash Memory Data

EF =0 =No Programming error

EF =1 =Programming error

Figure 9

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 15/30 9611V2

Read Byte

(D0-D7)

Addr =VA

D7 =Data ?

D5 =1 ?

Y

Y

Note 1

N

Recommend 8 s

time out from previous

data polling

Read Byte

(D0-D7)

Addr =VA

D7 =Data ?

Device Passed

Y

N

Start

Subroutine

Deviced failed

to program

EF =1

N

VA =Byte Address for Programming

N =Program time not exceeded limit

Y =Program time exceed limit, device failed

EF =Error Flag

Subroutine

Return

Note: 1. D7 is checked even if D5 =1 because D7 may have changed simultaneously with D5 or immediately after D5.

Figure 10 Byte-wide software polling for programming subroutine

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 16/30 9611V2

Byte-Wide erase Algorithm

Begin

Erase

Initialization :

EF =0

SEG ADRS =0

Write ERS cycle

#1 to #5

Write SEGADRS/ERS

CYCLE #6

Wait 2 seconds

Read SEG

ADRS/FMD

FMD =FFH

Begin software

polling subroutine

(figure 12)

Increment SEG ADRS

FMD =FFH

Last Segment

Address

Erase Complete

Erase Error

ERS =Erase Command Sequence

Segment Address =0

Error Flag =0

2 seconds memory segment erase time.

FMD =Flash Memory Data

Erased Flash Memory Data =FFH

Y

N

Y

N

N

Y

Figure 11

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 17/30 9611V2

Read Byte

(D0-D7)

Addr =X

D7 =1 ?

D5 =1 ?

Y

Y

N

N

Read Byte

(D0-D7)

Addr =X

D7 =1 ?

Device failed

to erase

EF =2

Device Passed

Y

N

D7 =1

Y =Erase Complete

N =Erase not Complete

Start

Subroutine

Subroutine

Return

Y

N

D5 =1

Y =Erase time exceeded limit, device failed

N =Erase time has not exceeded limit

X =Don't Care

Figure 12 Byte-wide software polling erase subroutine

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 18/30 9611V2

Word-Wide Programming Algorithm

Begin Programming

Initialization :

EF =0

Get ADRS/PDW

VWDAT =PDW

Write PGM

Write ADRS/PDW

Wait 16s

Read ADRS/FMD

FMD =VWDAT

Begin software

polling subroutine

(figure 14)

FMD =VWDAT

More Data Program Error

Program Complete

Y

N

N

N

Y

Y

Initialize Programming Variables :

PGM =Embedded Word Write Command

Sequence cycle #1 - #3

EF =Error Flag

ADRS =Appropriate address for Memory

Segment (cycle #4)

PDW =Program Data Word

VWDAT =Valid Word Data

EF =Error Flag

EF =0 =No failure

EF =1 =Low byte program error

EF =2 =High byte program error

EF =3 =Word-wide program error

Figure 13

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 19/30 9611V2

Read Byte

(D0-D7)

Addr =VA

D7 =V

data

? D5 =1 ?

Y

N

Begin

Subroutine

Subroutine

Return

Read Byte

(D8-D15)

Addr =VA

Read Byte

(D0-D7)

Addr =VA

D7 =V

data

?

D15 =V

data

? D13=1 ?

Read Byte

(D8-D15)

Addr =VA

D15 =V

data

?

Low byte program

time exceeded limit,

EF =1

N

N

N

N

N

Y

Y

Y Y

Y

VA =Word Address for Programming

V

data

=Valid data

D5 / 13 =1 ?

Y =Erase time has exceeded limit, device failed

N =Erase time has not exceeded limit

High byte program

time exceeded limit,

EF =2 +EF

Figure 14 Word-wide software polling for programming subroutine

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 20/30 9611V2

Word-Wide Erase Algorithm

Begin

Erase

Initialization :

SEG ADRS =0

EF =0

Write ERS cycle

#1 to #5

Wait 2 seconds

Read SEG

ADRS/FMD

FMD =FFFFH

Begin software

polling subroutine

(figure 16)

INC SEG ADRS

FMD =FFFFH

Last Segment

Address

Erase Complete

Erase Error

ERS =Segment Erase Command Sequence

SEG ADRS =Segment Address

Error Flag =0

EF =Error Flag

EF =0 =No failure

EF =1 =Low byte Erase error

EF =2 =High byte Erase error

EF =3 =Word-wide Erase error

FMD =Flash Memory Data

Y

N

Y

N

N

Y

Write ERS

cycle #6 :

SEG ADRS

Figure 15

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 21/30 9611V2

Read Byte

(D0-D7)

D7 =1? D5 =1 ?

Y

N

Begin

Subroutine

Subroutine

Return

Read Byte

(D8-D15)

Read Byte

(D0-D7)

D7 =1 ?

D15 =1 ? D13=1 ?

Read Byte

(D8-D15)

Addr =VA

D15 =1?

Low byte erase

time exceeded limit,

EF =1

N

N N

N

N

Y

Y

Y

Y

Y

D7 / 15 =1

Y =Erase Complete

N =Erase not Complete

High byte erase

time exceeded limit,

EF =2 +EF

Read Byte

(D8-D15)

D5 / 13 =1

Y =Erase time has exceeded limit, device failed

N =Erase time has not exceeded limit

Figure 16 Word-wide software polling for erase subroutine

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 22/30 9611V2

Tuple Information for Series-D FLASH Card

ADDRESS DATA(Hex) DESCRIPTION

00 01 CISTPL_DEVICE

02 03 TPL_LINK

04 53 FLASH card 150ns speed with WP switch

06 0E card size = 4MB

1E 8MB

2E 12MB

3E 16MB

4E 20MB

5E 24MB

6E 28MB

7E 32MB

08 FF END OF TUPLE LIST

0A 15 CISTPL_VERS_1

0C 26 TPL_LINK

0E 04 TPLLV1_MAJ OR

10 01 TPLLV1_MINOR(for PCMCIA release 2.0)

12 20 ASCII code of blank space

14 43 ASCII code of C

16 2D ASCII code of - (dash)

18 4F ASCII code of O

1A 4E ASCII code of N

1C 45 ASCII code of E

1E 00 Termination of the manutacturer name

20 20 ASCII code of blank space

22 53 ASCII code of S

24 45 ASCII code of E

26 52 ASCII code of R

28 49 ASCII code of I

2A 45 ASCII code of E

2C 53 ASCII code of S

2E 2D ASCII code of - (dash)

30 44 ASCII code of D

32 20 ASCII code of blank space

34 20 ASCII code of blank space

31 ASCII code of 1

32 ASCII code of 2

33 ASCII code of 3

36 30 ASCII code of 0

32 ASCII code of 2

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 23/30 9611V2

ADDRESS DATA(Hex) DESCRIPTION

34 ASCII code of 4

36 ASCII code of 6

38 ASCII code of 8

38 4D ASCII code of M

3A 42 ASCII code of B

3C 20 ASCII code of blank space

3E 46 ASCII code of F

40 4C ASCII code of L

42 41 ASCII code of A

44 53 ASCII code of S

46 48 ASCII code of H

48 20 ASCII code of blank space

4A 43 ASCII code of C

4C 41 ASCII code of A

4E 52 ASCII code of R

50 44 ASCII code of D

52 00 Termination of product name

54 00 Termination of lot number(no information)

56 00 Termination of programming condition

58 FF END OF TUPLE LIST

5A 18 CISTPL_JEDEC_C

5C 02 TPL_LINK

5E 01(04) J EDEC ID of AMD (FUJ ITSU)

60 A4 J EDEC ID of 29F040

62 1E CISTPL_DEVICE_GEO

64 06 TPL_LINK

66 02 DGTPL_BUS

68 11 DGTPL_EBS

6A 01 DGTPL_RBS

6C 01 DGTPL_WBS

6E 01 DGTPL_PART=1

70 01 DGTPL_HWIL=1(non-interleaved card)

72 21 CISTPL_FUNCID

74 02 TPL_LINK

76 01 TPLFID_ FUNCTION(PC Card is memory card)

78 00 TPLFID_SYSINIT (none)

7A FF CISTPL_END

7C FF END

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 24/30 9611V2

DC Electrical Characteristics

(recommended operating conditions unless otherwise noted)

Symbol Parameter 8-Bit Mode 16-Bit Mode Unit Test Condition

min max min max

ILI Input Leakage Current -10 10 -10 10 uA VIN =0V to VCC (Note 1)

-70 10 -70 10 uA VIN =0V to VCC (Note 2)

ILO Output Leakage Current -10 10 -10 10 uA CE1* =CE2* =VIH or

OE* =VIH , VOUT =0V

to VCC (Note 3)

VIH Input High Voltage 2.4 VCC+0.3 2.4 VCC+0.3 V

VIL Input Low Voltage -0.3 0.8 -0.3 0.8 V

VOH Output High Voltage 3.8 3.8 V IOH =-2.0mA (Note 4)

VOL Output Low Voltage 0.4 0.4 V IOL =3.2mA (Note 4)

ICCR VCC Read Current 45 90 mA Min. cycle , IOUT =0mA

ICCW VCC Write /Erase Current 65 130 mA Write/erase in progress

VLKO Low VCC Lock-out Voltage 3.2 4.2 3.2 4.2 V

Table 12

Note : 1.) Except CE1* , CE2* , WE* , REG* pins.

2.) For CE1* , CE2* , WE* , REG* pins.

3.) Except BVD1* , BVD2* , CD1* , CD2* pins.

4.) Except CD1* , CD2* pins.

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 25/30 9611V2

AC Electrical Characteristics

(recommended operating conditions unless otherwise noted)

Read Cycle (Common Memory)

Symbol Parameter Min Max Unit Notes

t

AVAV

t

RC

Read Cycle Time 150 ns

t

ELQV

t

CE

Card Enable Access Time 150 ns

t

AVQV

t

ACC

Address Access Time 150 ns

t

GLQV

t

OE

Output Enable Access Time 75 ns

t

ELQX

t

LZ

Card Enable to Output in Low-Z 5 ns

t

EHQZ

t

DF

Card Disable to Output in High-Z 75 ns

t

GLQX

t

OLZ

Output Enable to Output in Low-Z 5 ns

t

GHQZ

t

DF

Output Disable to Output in High-Z 75 ns

t

AXQX

t

OH

Output Hold From First of Address,

CE*, or OE* Change

5 ns

t

WHGL

Write Recovery Time Before Read 6 s

Table 13

Write/Erase Cycle (Common Memory)

Symbol Parameter Min Max Unit Notes

t

AVAV

t

WC

Write Cycle Time 150 ns

t

AVWL

t

AS

Address Setup Time 20 ns

t

WLAX

t

AH

Address Hold Time 55 ns

t

DVWH

t

DS

Data Setup Time 50 ns

t

WHDX

t

DH

Data Hold Time 20 ns

t

OEH

Output Enable Hold Time for

Embedded Algorithm

20 ns

t

WHGL

t

WR

Write Recovery Time before Read 6 s

t

GHWL

Read Recovery Time before Write 0 s

t

WLOZ

Output in High-Z from Write Enable 5 ns

t

WHOZ

Output in Low-Z from Write Enable 60 ns

t

ELWL

t

CS

CE* Setup Time 0 us

t

WHEH

t

CH

CE* Hold Time 20 sec

t

WLWH

t

WP

Write Pulse Width 45 ns

t

WHWL

t

WPH

Write Pulse Width HIGH 50 ns

t

WHWH3

Embedded Mode Programming

Operation

2 ms 1

t

WHWH4

Embedded Mode Erase Operation for

each 64K Byte Memory Block

s 2

t

VCS

V

CC

Setup Time CE* LOW s 3

Table 14

Note: 1. 8s typical 2. 1 seconds typical 3. 50s typical

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 26/30 9611V2

Write/Erase Cycle (Common Memory) (CE* Controlled)

Symbol Parameter Min Max Unit Notes

t

AVAV

t

WC

Write Cycle Time 150 ns

t

AVEL

t

AS

Address Setup Time 20 ns

t

ELAX

t

AH

Address Hold Time 55 ns

t

DVEH

t

DS

Data Setup Time 50 ns

t

EHDX

t

DH

Data Hold Time 20 ns

t

GLDV

t

OE

Output Enable Hold Time for

Embedded Algorithm

20 ns

t

GHEL

Read Recovery Time before Write 0 s

t

WLEL

t

WS

WE* Setup Time before CE* 0 ns

t

EHWH

t

WH

WE* Hold Time 0 ns

t

ELEH

t

CP

CE* Pulse Width 65 ns

t

EHEL

t

CPH

CE* Pulse Width HIGH 50 ns

t

EHEH3

Embedded Mode Programming

Operation

8 s

2 ms

t

EHEH4

Embedded Mode Erase Operation for

each 64K Byte Memory Block

1 s

t

VCS

V

CC

Setup Time To Write Enable

LOW

50 s

Table 15

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 27/30 9611V2

Read Cycle Timing Diagram (Common Memory)

t

RC

High-Z

Output Valid

High-Z

Address Stable

t

ACC

t

OE

t

CE

t

OH

t

DF

Address

CE1* or/and

CE2*

OE*

WE*

Outputs

Figure 17

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 28/30 9611V2

Write Cycle Timing Diagram (Common Memory)

t

AH

Address

CE*

OE*

WE*

Data

V

CC

t

GHWL

t

WP

t

WPH

t

DH

t

CS

t

DS

t

VCS

t

AS

XXXXH XXXXH XXXXH XXXXH XXXXH SA

AAH 55H 80H AAH 55H 10H/30H

Figure 18 Segment / Block byte erase

t

AH

Address

CE*

Data

V

CC

t

GHWL

t

WP

t

WPH

t

DH

t

CS

t

DS

t

VCS

t

AS

XXXXH PA PA

A0H PD D7 D

OUT

t

WC

t

WHWH3

t

CE

t

OH

t

DF

t

OE

t

RC

Notes :

1. Figure indicates last two bus cycles of four bus cycle sequence.

2. PA is address of the memory location to be programmed.

3. PD is data to be programmed at byte address.

4. D7 is the output of the complement of the data written to the device.

5. D

OUT

is the output of the data written to the device.

OE*

WE*

Figure 19 Byte write

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 29/30 9611V2

AC Electrical Characteristics ( Attribute Memory )

( recommended operating conditions unless otherwise noted )

Read Cycle ( Attribute Memory )

Symbol Parameter Min. Max. Unit Test Condition

t

cr

Read Cycle Time 300 ns

t

a

(A) Address Access Time 300 ns

t

a

(CE)

Card Select Access Time 300 ns

t

a

(OE)

Output Enable Access Time 150 ns

t

dis

(CE) Output Disable Time (from CE*) 100 ns

t

dis

(OE) Output Disable Time (from OE*) 100 ns

t

en

(CE)

Output Enable Time (from CE*) 5 ns

t

en

(OE) Output Enable Time (from OE*) 5 ns

t

v

(A) Data Hold Time (from address changed) 0 ns

Table 16

Write Cycle ( Attribute Memory )

Symbol Parameter Min. Max. Unit Test Condition

t

cw

Write Cycle Time 1 ms

t

AS

Address Setup Time 30 ns

t

AH

Address Hold Time 50 ns

t

WP

Write Pulse Width 120 ns

t

CS

Card Enable Time to WE* 15 ns

t

CH

Card Enable Hold Time from WE* High 0 ns

t

DS

Data Setup Time 70 ns

t

DH

Data Hold Time 30 ns

t

OES

OE* Setup Time 30 ns

t

OEH

OE* Hold Time 30 ns

Table 17

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 30/30 9611V2

Read Cycle Timing Diagram ( Attribute Memory ) ( REG*=VIL , WE*=VIH )

Address

tcr

t

t

t

t

t

t

DATA VALID

t

t

Data Out

OE*

CE2*

CE1* or/and

(A1-A11)

en(CE)

en(OE)

a(OE)

a(CE)

a(A)

dis(OE)

dis(CE)

v(A)

Figure 20

Write Cycle Timing Diagram ( Attribute Memory ) ( REG*=VIL )

Address

OE*

CE2*

CE1* or/and

DATA INPUT VALID

WE*

Data In

(A1-A11)

tAH

tAS

tWP

tOEH

t

tOES

tDS

h(D)

tCS

tCH

Figure 21

C-ONE

PCMCIA SERIES-D FLASH MEMORY CARD

;[[[;[, 31/30 9611V2

Outline Dimensions (Unit : mm)

You might also like

- Msi ms-7310 Rev 1.0 SCHDocument30 pagesMsi ms-7310 Rev 1.0 SCHSebastian QuaroneNo ratings yet

- Foxconn 915m08 Rev 2.1 SCHDocument40 pagesFoxconn 915m08 Rev 2.1 SCHiskenderbeyNo ratings yet

- Nf4st-A2b (CK804) Rev 1.2Document48 pagesNf4st-A2b (CK804) Rev 1.2Flickk AnhuiiNo ratings yet

- PSD834 F 2Document129 pagesPSD834 F 2Тестер ХелперовNo ratings yet

- Msi MS-7673 Rev 2.0Document39 pagesMsi MS-7673 Rev 2.0ВолодимирNo ratings yet

- MSI7680Document37 pagesMSI7680王米特No ratings yet

- Motherboard Manual Ga-965gm-s2 eDocument88 pagesMotherboard Manual Ga-965gm-s2 eGiorgisNo ratings yet

- Motherboard Manual k8nf-9 eDocument80 pagesMotherboard Manual k8nf-9 eMarincov RaduNo ratings yet

- Msi MS-7680 Rev 3.2Document34 pagesMsi MS-7680 Rev 3.2Петро ДуманськийNo ratings yet

- MSI MS-6382 SchematicDocument42 pagesMSI MS-6382 SchematicTanja IkalovicNo ratings yet

- Roland Fantom s88Document51 pagesRoland Fantom s88harryoliff2672100% (1)

- Sony Vaio Vgn-Ns Series Foxconn m790!1!01 Rev 1.0 SCHDocument54 pagesSony Vaio Vgn-Ns Series Foxconn m790!1!01 Rev 1.0 SCHCarlos Henrique RibasNo ratings yet

- Motherboard Manual Ga-M61sme-S2 2Document80 pagesMotherboard Manual Ga-M61sme-S2 2Mohd Asri TaipNo ratings yet

- m-ATX: 245 X 215mm: TitleDocument37 pagesm-ATX: 245 X 215mm: TitlespotNo ratings yet

- Embeddedmb Manual e Mbbz1ai 1201Document52 pagesEmbeddedmb Manual e Mbbz1ai 1201mauro yanayaco atencioNo ratings yet

- 8050QRDocument121 pages8050QRcjarekNo ratings yet

- Epox 8RDA3i Mainboard English ManualDocument90 pagesEpox 8RDA3i Mainboard English ManualDan BanNo ratings yet

- Controlador ST90T40 Com Eeprom RAM e A D ConversorDocument57 pagesControlador ST90T40 Com Eeprom RAM e A D ConversorMarcio EmersonNo ratings yet

- 113 Service Manual - Travelmate 2200 2700 Aspire 1670Document137 pages113 Service Manual - Travelmate 2200 2700 Aspire 1670Soporte Tecnico Buenos AiresNo ratings yet

- Msi b85m Pro-Vd (Ms-7a01) Rev 1.1Document34 pagesMsi b85m Pro-Vd (Ms-7a01) Rev 1.1Angel RuizNo ratings yet

- MSI MS-7823 Rev 3.2 PDFDocument33 pagesMSI MS-7823 Rev 3.2 PDFHACSNo ratings yet

- HP Dv1 - Flex Computing H210ua1 - Hpmh-40gab6000-C000 - Rev CDocument28 pagesHP Dv1 - Flex Computing H210ua1 - Hpmh-40gab6000-C000 - Rev CCarolineAlvesNo ratings yet

- HP Pavilion Dv7 - Quanta Up6 7 Jones Cujo 2.0 Dis - Rev 1.0 26out2009Document42 pagesHP Pavilion Dv7 - Quanta Up6 7 Jones Cujo 2.0 Dis - Rev 1.0 26out2009Hans PeterNo ratings yet

- T-Core User ManualDocument65 pagesT-Core User ManualJosué Peña CarrilloNo ratings yet

- Gigabyte Ga-K8ne Rev 2.0 SCH PDFDocument33 pagesGigabyte Ga-K8ne Rev 2.0 SCH PDFDa ElNo ratings yet

- Sony MBX-189 - M760 - REV 1.0Document89 pagesSony MBX-189 - M760 - REV 1.0pepegotera4540% (1)

- SBC82611Document82 pagesSBC82611xavier dupontNo ratings yet

- Clevo, 71r A14HV6 T840Document40 pagesClevo, 71r A14HV6 T840Jonathan BiondiNo ratings yet

- Foxconn m851 UnlockedDocument69 pagesFoxconn m851 UnlockedLisandro Martinez DominguezNo ratings yet

- MT48LC64M4A2Document86 pagesMT48LC64M4A2nhv_lhNo ratings yet

- MSI H310M Pro-M2 Plus MSI MS-7C08 r1.0 PDFDocument53 pagesMSI H310M Pro-M2 Plus MSI MS-7C08 r1.0 PDFjorge mendozaNo ratings yet

- MS-7B49-1.1 (Intel - Coffeelake Plamform Z370)Document65 pagesMS-7B49-1.1 (Intel - Coffeelake Plamform Z370)Carlos GomesNo ratings yet

- Manual Placa Mae Ga 945gcmx-s2 6.6Document72 pagesManual Placa Mae Ga 945gcmx-s2 6.6luisb3toNo ratings yet

- Quanta Computer Inc. 650 System Block DiagramDocument35 pagesQuanta Computer Inc. 650 System Block DiagramWilgen GarciaNo ratings yet

- Msi Ms-7a54 Rev 1.1Document62 pagesMsi Ms-7a54 Rev 1.1Rody CaceresNo ratings yet

- Manual k8ns eDocument96 pagesManual k8ns eGeorgescu BogdanNo ratings yet

- Motherboard Manual Ga-Ma69vm-S2 eDocument88 pagesMotherboard Manual Ga-Ma69vm-S2 evantuird100% (1)

- Sony Vaio VGN-FJ Series - Quanta Rd1 - Rev 1aDocument32 pagesSony Vaio VGN-FJ Series - Quanta Rd1 - Rev 1aJose A LachiondoNo ratings yet

- NEC EXPRESS5800/R320d-M4 Configuration Guide: Windows Server 2008 R2 ModelDocument21 pagesNEC EXPRESS5800/R320d-M4 Configuration Guide: Windows Server 2008 R2 ModelVinoth KumararajaNo ratings yet

- MS-7549 Ver:1.1: TitleDocument34 pagesMS-7549 Ver:1.1: TitlechokNo ratings yet

- 64Gbit NAND Flash Memory SpecificationDocument56 pages64Gbit NAND Flash Memory SpecificationSmail ZouariNo ratings yet

- Fujitsu Siemens Amilo Si 1848 - UNIWILL S50IA0x - REV BDocument48 pagesFujitsu Siemens Amilo Si 1848 - UNIWILL S50IA0x - REV BSava TrujaNo ratings yet

- Sony-M751 - PVT - MB - 0627vgn-Sr55e m754h Mbx-190.textmark SCHEMATICDocument54 pagesSony-M751 - PVT - MB - 0627vgn-Sr55e m754h Mbx-190.textmark SCHEMATICvideosonNo ratings yet

- Ig41b M7S V6.0 SDocument36 pagesIg41b M7S V6.0 SiskenderbeyNo ratings yet

- Ms 6380eDocument48 pagesMs 6380ekkjumaNo ratings yet

- Intel - Kabylake Plamform B250/H270: System Chipset: CpuDocument64 pagesIntel - Kabylake Plamform B250/H270: System Chipset: CpuAngel Guerrero OlivoNo ratings yet

- MSI MS-7B17 Rev 1.0 SchematicDocument70 pagesMSI MS-7B17 Rev 1.0 SchematicIonut Lapuste100% (1)

- HP Compaq 6531s Inventec Zzi MV Rev A03 (6820s)Document54 pagesHP Compaq 6531s Inventec Zzi MV Rev A03 (6820s)y2k_yah7758No ratings yet

- Parts Reference List MODEL: MFC8870DW / MFC8860DN MFC8460N DCP8065DN / DCP8060Document41 pagesParts Reference List MODEL: MFC8870DW / MFC8860DN MFC8460N DCP8065DN / DCP8060Andrey KhodanitskiNo ratings yet

- MC56F8006Document100 pagesMC56F8006andreferreira_eletricaNo ratings yet

- 5820 Edition 2Document114 pages5820 Edition 2Erasmo FrancoNo ratings yet

- NES Architecture: Architecture of Consoles: A Practical Analysis, #1From EverandNES Architecture: Architecture of Consoles: A Practical Analysis, #1Rating: 5 out of 5 stars5/5 (1)

- Master System Architecture: Architecture of Consoles: A Practical Analysis, #15From EverandMaster System Architecture: Architecture of Consoles: A Practical Analysis, #15No ratings yet

- Dreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9From EverandDreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9No ratings yet

- Game Boy Advance Architecture: Architecture of Consoles: A Practical Analysis, #7From EverandGame Boy Advance Architecture: Architecture of Consoles: A Practical Analysis, #7No ratings yet

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3From EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3No ratings yet

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6From EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6No ratings yet

- Sega Saturn Architecture: Architecture of Consoles: A Practical Analysis, #5From EverandSega Saturn Architecture: Architecture of Consoles: A Practical Analysis, #5No ratings yet

- GameCube Architecture: Architecture of Consoles: A Practical Analysis, #10From EverandGameCube Architecture: Architecture of Consoles: A Practical Analysis, #10No ratings yet

- MTHP4 Installation Manual v1.9Document15 pagesMTHP4 Installation Manual v1.9Jesus LozanoNo ratings yet

- B-Series Gige - eDocument28 pagesB-Series Gige - eJesus LozanoNo ratings yet

- CCS-R Opaque PrinterDocument1 pageCCS-R Opaque PrinterJesus LozanoNo ratings yet

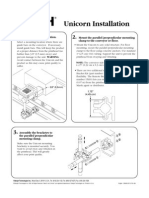

- MARSH Unicorn InstallationDocument20 pagesMARSH Unicorn InstallationJesus LozanoNo ratings yet

- CCS Series Ink LineupDocument2 pagesCCS Series Ink LineupJesus LozanoNo ratings yet

- A Brief History of Linx Printing TechnologiesDocument5 pagesA Brief History of Linx Printing TechnologiesJesus LozanoNo ratings yet

- Autopilot Rev ADocument60 pagesAutopilot Rev AJesus LozanoNo ratings yet

- Marsh Unicorn, Manual Del PropietarioDocument90 pagesMarsh Unicorn, Manual Del PropietarioJesus LozanoNo ratings yet

- Design Fundamentals For PhoDocument2 pagesDesign Fundamentals For PhoJesus LozanoNo ratings yet

- D Mia0401 en CgraficDocument33 pagesD Mia0401 en CgraficJesus LozanoNo ratings yet

- Design Fundamentals For PhoDocument2 pagesDesign Fundamentals For PhoJesus LozanoNo ratings yet

- 4800 Maintenance Instruction: Draining The Ink SystemDocument3 pages4800 Maintenance Instruction: Draining The Ink SystemJesus LozanoNo ratings yet

- Linx Continuous Ink Jet Printers Models 6200S & 6200R: PerformanceDocument2 pagesLinx Continuous Ink Jet Printers Models 6200S & 6200R: PerformanceJesus Lozano0% (1)

- Design Fundamentals For PhoDocument2 pagesDesign Fundamentals For PhoJesus LozanoNo ratings yet

- Emi/Rfi Solutions: Vishay Intertechnology, IncDocument16 pagesEmi/Rfi Solutions: Vishay Intertechnology, IncJesus LozanoNo ratings yet

- 4800 Maintenance Instruction: System Flush ProcedureDocument11 pages4800 Maintenance Instruction: System Flush ProcedureJesus LozanoNo ratings yet