Professional Documents

Culture Documents

5 VHDL Coading

Uploaded by

puppyr0 ratings0% found this document useful (0 votes)

12 views14 pagesgvdvg

Original Title

5 vhdl coading

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentgvdvg

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

12 views14 pages5 VHDL Coading

Uploaded by

puppyrgvdvg

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 14

EXP NO: 5 MODELLING OF SEQUENTIAL DIGITAL SYSTEM

DATE: USING VHDL

AIM:

To synthesis and simulate the VHDL code for the Flip flops logic circuits.

APPRATUS REQUIRED:

ISE 9.1 Simulator.

THEORY:

FLIP FLOPS:

A flip-flop is a circuit that has two stable states and can be used to store state

information. Flip flop is a bistable multivibrator. The circuit can be made to change state by

signals applied to one or more control inputs and will have one or two outputs. It is the basic

storage element in sequential logic. Flip-flops is a fundamental building block of digital

electronics systems used in computers, communications, and many other types of systems.

Flip-flops and latches are used as data storage elements. Such data storage can be

used for storage of state, and such a circuit is described as sequential logic. When used in

a finite-state machine, the output and next state depend not only on its current input, but also

on its current state (and hence, previous inputs). It can also be used for counting of pulses,

and for synchronizing variably-timed input signals to some reference timing signal.

PROCEDURE:

1. Design the given flip-flops logic circuit.

2. Write the vhdl code for the design circuit.

3. Create a new project in ISE simulator and select synthesis/Implementation is source

window to synthesis the program.

4. In the source window, right click on project name and click create new source

(a) In the new source wizard select verilog module and type file name and click

next.

(b) Enter the input, output ports and set their directions according in the define

module window.

(c) Enter finish.

5. File name .v window appears, type the program and save it.

6. Go to process window and double click synthesis XST and view RTL model.

CREATING TEST BENCH WAVEFORM:

7. In the source window select behavior simulation.

8. Right click on the project and select new source.

9. Select source type as test bench waveform and give a filename. (filename should not

be the same as the project name).

10. Enter next and click finish.

11. Timing and clock wizard window appears. Set the clock information as combinational

and click finish.

12. Set the input wave form and save.

13. In the process window, choose Xilinx ISE simulator and in that select, .tbw file,

simulate behavioral model.

14. Verify the simulator output with truth table.

RESULT:

(i) D-FLIPFLOP

PROGRAM:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dff is

Port(d:in STD_LOGIC;

clk:in STD_LOGIC;

rst:in STD_LOGIC;

q:out STD_LOGIC;

qbar:out STD_LOGIC);

end dff;

architecture Behavioral of dff is

begin

process(clk,rst)

begin

if(rst==1)then

q<=0;

else if(clkevent and clk=1)then

q<=d;

end if;

end if;

qbar<=not d;

end process;

end Behavioral;

RTL SCHEMATIC:

clk q

d

reset

OUTPUT:

D FLIPFLOP

DIAGRAM:

CHARACTRISTIC TABLE:

Q D Q(t+1)

0 0 0

0 1 1

1 0 0

1 1 1

(ii) T-FLIPFLOP

PROGRAM:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tff is

Port(t:in STD_LOGIC;

clk:in STD_LOGIC;

rst:in STD_LOGIC;

q:out STD_LOGIC;

qbar:out STD_LOGIC);

end tff;

architecture Behavioral of tff is

signal qt,qbart:STD_LOGIC;

begin

process(clk)

begin

if(rst==0)then

qt<=0;

else if(clkevent and clk=1)then

qt<=(t xor qt);

end if;

end if;

end process;

q<=qt;

qbar<=not qt;

end Behavioral;

RTL SCHEMATIC:

clk q

t

reset qbar

OUTPUT:

T FLIPFLOP

DIAGRAM:

CHARACTRISTIC TABLE:

Q T Q(t+1)

0 0 0

0 1 1

1 0 1

1 1 0

(iii)JK FLIPFLOP

PROGRAM:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity jkff is

Port(j:in STD_LOGIC;

k:in STD_LOGIC;

clk:in STD_LOGIC;

rst:in STD_LOGIC;

q:out STD_LOGIC;

qbar:out STD_LOGIC);

end jkff;

architecture Behavioral of jkff is

signal qt,qbart:STD_LOGIC;

begin

process(clk,rst)

begin

if(rst==0)then

qt<=0;

else if(clkevent and clk=1)then

qt<=((not qt) and j)or(qt and (not k));

else

end if;

end if;

end process;

q<=qt;

qbar<=not qt;

end Behavioral;

RTL SCHEMATIC:

clk q

j

k qb

reset

OUTPUT:

JK FLIPFLOP

DIAGRAM:

CHARACTRISTIC TABLE:

J K Q(t+1)

0 0 Q

0 1 1

1 0 0

1 1 Q

(iv)SR FLIPFLOP

PROGRAM:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity srff is

Port(s:in STD_LOGIC;

r:in STD_LOGIC;

clk:in STD_LOGIC;

rst:in STD_LOGIC;

q:out STD_LOGIC;

qbar:out STD_LOGIC);

end srff;

architecture Behavioral of srff is

signal qt,qbart:STD_LOGIC;

begin

process(clk,rst)

begin

if(rst==0)then

qt<=0;

else if(clkevent and clk=1)then

qt<= s or ((not r) and qt);

else

end if;

end if;

end process;

q<=qt;

qbar<=not qt;

end Behavioral;

RTL SCHEMATIC:

clk q

r

s qbar

reset

OUTPUT:

SR FLIPFLOP

DIAGRAM:

CHARACTRISTIC TABLE:

S R Q(t+1)

0 0 Q

0 1 0

1 0 1

1 1 *

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- 16 Bit Alu in VHDLDocument7 pages16 Bit Alu in VHDLpuppyrNo ratings yet

- 16 Bit Alu in VHDLDocument7 pages16 Bit Alu in VHDLpuppyrNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Full Custom Design With Cadence and Ams Hit-KitDocument29 pagesFull Custom Design With Cadence and Ams Hit-KitAbuHarithHamzahNo ratings yet

- GateDocument1 pageGatepuppyrNo ratings yet

- Aodv CCDocument33 pagesAodv CCpuppyrNo ratings yet

- 2014 Ieee Project Ns2 TitlesDocument2 pages2014 Ieee Project Ns2 TitlesRaghu NathNo ratings yet

- Electron Devices and IcsDocument4 pagesElectron Devices and IcspuppyrNo ratings yet

- Accenture Placement Test Syllabus Exam Pattern 201Document1 pageAccenture Placement Test Syllabus Exam Pattern 201puppyrNo ratings yet

- Accenture Questions 1Document5 pagesAccenture Questions 1puppyrNo ratings yet

- CTS - 1 - Answer KeyDocument1 pageCTS - 1 - Answer KeypuppyrNo ratings yet

- ZIGBEEDocument6 pagesZIGBEEpuppyrNo ratings yet

- Android VersionsDocument12 pagesAndroid VersionspuppyrNo ratings yet

- CTS - 1 - Answer KeyDocument1 pageCTS - 1 - Answer KeypuppyrNo ratings yet

- CPLD ProgDocument33 pagesCPLD ProgpuppyrNo ratings yet

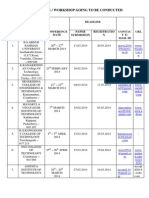

- Conference / Workshop Going To Be Conducted: DeadlineDocument2 pagesConference / Workshop Going To Be Conducted: DeadlinepuppyrNo ratings yet

- Vlsi QnsDocument2 pagesVlsi QnspuppyrNo ratings yet

- Advertisement SERB RecttDocument11 pagesAdvertisement SERB RecttpuppyrNo ratings yet

- 4 RTCDocument9 pages4 RTCpuppyrNo ratings yet

- NC7101Document6 pagesNC7101puppyrNo ratings yet

- Alu VerilogDocument3 pagesAlu VerilogpuppyrNo ratings yet

- 4 RTCDocument9 pages4 RTCpuppyrNo ratings yet

- Alu VerilogDocument3 pagesAlu VerilogpuppyrNo ratings yet

- Clocked Synchronous Sequential Circuits: ExampleDocument4 pagesClocked Synchronous Sequential Circuits: ExamplepuppyrNo ratings yet

- Synchronous Fifo PGMDocument3 pagesSynchronous Fifo PGMpuppyrNo ratings yet

- QMFDocument3 pagesQMFpuppyrNo ratings yet

- AP7111Document71 pagesAP7111puppyrNo ratings yet

- Sub Code & Name:: DOC/LP/01/28.02.02Document6 pagesSub Code & Name:: DOC/LP/01/28.02.02puppyrNo ratings yet

- About The InstitutionDocument3 pagesAbout The InstitutionpuppyrNo ratings yet

- VL9221Document6 pagesVL9221Kunal KhandelwalNo ratings yet

- Universal Shift RegisterDocument1 pageUniversal Shift RegisterpuppyrNo ratings yet

- Sales Flyer 13 BDocument32 pagesSales Flyer 13 BHelloNo ratings yet

- Accuracy PDFDocument2 pagesAccuracy PDFagus kurniawanNo ratings yet

- FX - Programming - Manual - Intermediate and Advance PDFDocument109 pagesFX - Programming - Manual - Intermediate and Advance PDFAnonymous gihiMV3No ratings yet

- VLSI for Wireless Communication Question BankDocument13 pagesVLSI for Wireless Communication Question Bankjebas_ece100% (2)

- 6 - Itu-R M.2010 NavdatDocument21 pages6 - Itu-R M.2010 NavdatTran HoangNo ratings yet

- KNX - CommunicationDocument25 pagesKNX - CommunicationEdouard BurnNo ratings yet

- Haier lt19z6 PDFDocument336 pagesHaier lt19z6 PDFgorlichNo ratings yet

- CCTV8 PDFDocument2 pagesCCTV8 PDFFelix John NuevaNo ratings yet

- OpenVox G410E On Elastix Guide ManualDocument18 pagesOpenVox G410E On Elastix Guide ManualMarco CarvalhoNo ratings yet

- Integrated Circuits of 6,000 Counts Auto-ranging Digital Multimeter with Bar GraphDocument37 pagesIntegrated Circuits of 6,000 Counts Auto-ranging Digital Multimeter with Bar GraphMárcio FerreiraNo ratings yet

- FleetMon S1-C Satellite TransponderDocument2 pagesFleetMon S1-C Satellite TransponderTaufikNo ratings yet

- Design of A Quadrature Decodercounter Interface Ic For Motor ConDocument6 pagesDesign of A Quadrature Decodercounter Interface Ic For Motor ConAmol ElectronicaNo ratings yet

- Bio StationDocument2 pagesBio StationErick Dahomey Arévalo PuenteNo ratings yet

- AIT 501 Instruction Catalogue PDFDocument2 pagesAIT 501 Instruction Catalogue PDFMahammad Husain VijapuraNo ratings yet

- EasyDspic4 ManualDocument30 pagesEasyDspic4 ManualPaul Vintimilla TapiaNo ratings yet

- Kuman 3.5 Inch Touch Screen DatasheetDocument15 pagesKuman 3.5 Inch Touch Screen DatasheetMarcGarciaNo ratings yet

- IMX6SDLAECDocument167 pagesIMX6SDLAECvishalNo ratings yet

- Amateur Radio Magazin 01 - January - 1975 PDFDocument164 pagesAmateur Radio Magazin 01 - January - 1975 PDFJoão Pedro AlmeidaNo ratings yet

- 1871 FeDocument36 pages1871 Ferute silvaNo ratings yet

- NCP1251 DatasheetDocument24 pagesNCP1251 DatasheetJose BenavidesNo ratings yet

- Allama Iqbal Open University, Islamabad (Department of Computer Science) WarningDocument4 pagesAllama Iqbal Open University, Islamabad (Department of Computer Science) WarningRauf KhanNo ratings yet

- TC 917 SystemDocument4 pagesTC 917 SystemcafeeesmoNo ratings yet

- LAB FAT QUESTIONS ANALYSISDocument15 pagesLAB FAT QUESTIONS ANALYSISSrinivasan UmaNo ratings yet

- Msi B75ma-E33 (MS-7808 1.0)Document203 pagesMsi B75ma-E33 (MS-7808 1.0)majkool100% (1)

- Controlling A Robotic Car Through MATLAB GUI - Electronics ProjectDocument4 pagesControlling A Robotic Car Through MATLAB GUI - Electronics ProjectNanxxxNo ratings yet

- Slva666 - Flyback TL494Document25 pagesSlva666 - Flyback TL494betodias30No ratings yet

- Omni Redundant ConfigurationDocument8 pagesOmni Redundant Configurationtriminhdang_phar6701No ratings yet

- AM, FM, and Digital Modulated SystemsDocument26 pagesAM, FM, and Digital Modulated SystemsMe OneNo ratings yet