Professional Documents

Culture Documents

Orthogonal Code Generator For 3G Wireless Transceivers: Boris D. Andreev, Edward L. Titlebaum, and Eby G. Friedman

Uploaded by

Srikanth ChintaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Orthogonal Code Generator For 3G Wireless Transceivers: Boris D. Andreev, Edward L. Titlebaum, and Eby G. Friedman

Uploaded by

Srikanth ChintaCopyright:

Available Formats

Orthogonal Code Generator for 3G Wireless Transceivers

Boris D. Andreev, Edward L. Titlebaum, and Eby G. Friedman

Department of Electrical and Computer Engineering

University of Rochester

Rochester, New York 14627

{bandreev, tbaum, friedman} @ece.rochester.edu

ABSTRACT

Orthogonal variable spreading factor (OVSF) codes are standard

in third generation UMTS cellular systems. The efficient generation

of these codes is essential for reducing the area and power of

wireless transceivers. In this paper, the basic properties of this

family of codes are analyzed from an RTL perspective and two

efficient hardware code generators are proposed. Tradeoffs and

design solutions as well as low power considerations are discussed.

These results represent the first reported implementation of an

OVSF code generator.

1

*

Categories and Subject Descriptors

B.5.1 [RTL Implementation] Design: Arithmetic and Logic Units

B.6.0 [Logic Design] General

B.7.m [Integrated circuits] Miscellaneous

General Terms: Design

Keywords: OVSF codes, CDMA, VLSI, 3GPP, UMTS, WCDMA

1. INTRODUCTION

Modern CDMA cellular systems employ spread spectrum

technology to provide multiuser access. In particular, direct

sequence spread spectrum has been adopted for improved spectral

efficiency, ease of digital implementation, and soft capacity limit.

Each user employs a noiselike wideband signal occupying the

entire allocated frequency band for as long as necessary. In this

way, each user contributes to the background noise affecting all

other users. This additional interference limits the overall system

capacity but because time and bandwidth resources are virtually

unlimited, the resulting capacity is significantly greater than in

conventional cellular systems. In the UMTS (Universal Mobile

Telecommunication System) wireless standard, part of the Third

Generation Partnership Project (3GPP), the spectrum spreading

applied to the symbols in the physical channels consists of two

operations [1]. The first is the channelization operation, which

transforms every data symbol into a number of chips, thereby

increasing the signal bandwidth. The number of chips per data

symbol is called the spreading factor (SF). The channelization

*

This research is supported in part by the Semiconductor Research

Corporation under Contract No. 99-TJ-687, the DARPA/ITO under AFRL

Contract F29601-00-K-0182, grants from the New York State Office of

Science, Technology & Academic Research to the Center for Advanced

Technology Electronic Imaging Systems and to the Microelectronics

Design Center, and by grants from Xerox Corporation, IBM Corporation,

Intel Corporation, Lucent Technologies Corporation, Eastman Kodak

Company, and Photon Vision Systems, Inc.

Permission to make digital or hard copies of all or part of this work for

personal or classroom use is granted without fee provided that copies are

not made or distributed for profit or commercial advantage and that copies

bear this notice and the full citation on the first page. To copy otherwise, or

republish, to post on servers or to redistribute to lists, requires prior specific

permission and/or a fee.

GLSVLSI03, April 28-29, Washington, DC, USA.

Copyright 2003 ACM 1-58113-677-3/03/0004$5.00.

OVSF codes achieve orthogonality between a users different

physical channels. The second operation is the scrambling

operation, where a scrambling code is applied to the spread signal

in order to distinguish signals from asynchronous users. With

channelization, data symbols on the in-phase (I) and quadrature-

phase (Q) branches are independently multiplied with an

orthogonal variable spreading factor (OVSF) code. One control

channel and up to six data channels can be simultaneously

transmitted. The real-valued chip streams on the I- and Q-branches

are combined and treated as a complex-valued stream of chips.

With the scrambling operation, the resultant complex signal is

multiplied by a complex-valued scrambling code.

An overview of the 3GPP standard defining the OVSF codes is

presented in section 2. The generation of OVSF codes for 3GPP

systems is considered from an RTL perspective in section 3. Two

alternative techniques for designing a hardware OVSF code

generator are proposed in sections 4 and 5. The first technique,

described in section 4, refers to a standalone logic circuit achieving

the target function. A more efficient approach is discussed in

section 5, which requires, however, a change in the system software

to support a logic circuit of reduced complexity. Power dissipation

issues are discussed in section 6. Results from the synthesis of the

proposed code generator are reported in section 7 and some related

system level issues are discussed in section 8. Final remarks are

offered in section 9 to conclude the paper.

2. OVSF CODES IN THE 3GPP STANDARD

OVSF codes are defined in the 3GPP standard [1] by the code

tree shown in Fig. 1. A channelization code C

ch,SF,N

is uniquely

described by two numbers: the spreading factor SF in the range

[4 - 512] = [2

2

- 2

9

], and the identification (ID) number N [0,

SF 1]. Each level in the code tree defines channelization codes of

length SF as shown in Fig. 1.

The control channel is spread by code C

256,0

, which consists of

256 logic zeros. When only one data channel is transmitted, data

channel

1

is spread by code C

SF,k

where SF is the spreading factor

and k = SF / 4. When more than one data channel is transmitted, all

of the data channels have a spreading factor equal to 4. Data

channel

n

is spread by the code C

4,k

, where k = 1 if n {1, 2}, k = 3

if n {3, 4}, and k = 2 if n {5, 6}.

SF = 1 SF = 2 SF = 4

C

ch,1,0

= (1)

Cch,2,0 = (1,1)

C

ch,2,1

= (1,-1)

C

ch,4,0

=(1,1,1,1)

C

ch,4,1

= (1,1,-1,-1)

C

ch,4,2

= (1,-1,1,-1)

C

ch,4,3

= (1,-1,-1,1)

Fig. 1: Code tree of Orthogonal Variable Spreading Factor

(OVSF) codes [1]

229

3. RTL PERSPECTIVE ON OVSF CODES

The generation of the OVSF channelization codes is defined in

the 3GPP standard [1] by three matrix expressions. The direct

implementation of these matrix operations requires a significant

amount of resources which is convenient only for a software

realization based on a microcontroller or a digital signal processor.

In order to design an efficient hardware generator for this family of

codes, specific properties of OVSF codes are discussed in this

section.

The chip sequence is specified in the binary set {+1, 1}, while

digital CMOS logic operates on the set {0, 1}. The mapping {+1

logic 0} and {1 logic 1} is therefore adopted as a

convention. The spreading codes serve as control signals for a

complex 1 multiplier [2]. In the remainder of the paper, circuits

issues are discussed with logic levels of 0 and 1.

The binary representation of the ID number describes the

trajectory of the code generation along the OVSF code tree shown

in Fig. 1: a logic 0 for the upper branch or a logic 1 for the lower

branch. This property is illustrated by the following example:

Example: Suppose the channelization code C

8,5

is required.

SF = 8

10

= 1000

2

N = 5

10

= 0101

2

= n

3

n

2

n

1

n

0

The trajectory of code C

8,5

is defined as follows:

Stage 1 a single root, always 0

Stage 2 lower branch, controlled by n

2

Stage 3 upper branch, controlled by n

1

Stage 4 lower branch, controlled by n

0

The individual code chips are controlled by corresponding bits

in the ID number, as listed in Table 1. The OVSF chips can

therefore be produced by a XOR operation over certain bits of the

code ID number. The participation of a specific bit in the XOR

operation is periodic in time and can be controlled by a binary

counter as listed in Table 2.

Based on observations of the data listed in Tables 1 and 2, a

logic level architecture of an OVSF code generator is shown in Fig.

2. The least significant bit (LSB) of the counter enables the MSB of

N, bit n

2

, to be included in the XOR operation. The MSB of the

counter controls n

0

, which is the LSB of N.

The 3GPP standard, however, specifies that the code generator

should be capable of producing codes with a variable spreading

factor over the range SF = 4 to 512. The issue is how best to match

the number N and the binary counter in reverse order for different

spreading factors. Two techniques are suggested to accomplish this

objective:

1. Design a special counter, counting incrementally from 0 to

SF 1. b

8

is always the MSB, while the LSB is specified by

the variable spreading factor SF and is b

x

, where x =

log

2

SF

max

log

2

SF. In the aforementioned example, the

counter has six dummy bits (always at 0) and three active

bits. The MSB b

8

controls bit n

0

of the ID register, and bit b

6

is the LSB of the counter, which controls bit n

2

.

2. Shift the code ID number such that the MSB of N is always

enabled by the LSB of the counter. In this case, a regular

binary counter is required to count between 0 and SF

max

1.

In the following sections, the advantages and drawbacks of both

techniques are described and corresponding logic circuits are

proposed.

4. TECHNIQUE 1: DESIGN OF A SPECIAL COUNTER

The design of a special counter requires less additional

hardware than a circuit that directly implements the proposed

second scheme. An SF register, holding the required spreading

factor, controls the counter cycle, while the ID register controls the

specific OVSF code. This separation of the high level parameters

SF and N provides modularity of the circuit blocks when multiple

OVSF codes are generated. A circuit solution for the counter is

proposed in Fig. 3. The LSB of the counter is specified by the only

bit of the SF register, which is logic 1. The count is from left to

right, where b

8

is always the MSB.

Table1: Generation of channelization code C

8,5

First generated chip Last generated chip

C

8,5

= 0 1 0 1 1 0 1 0

n

3

= 0

always

n

3

n

2

=

n

2

n

3

n

1

=

n

1

n

3

n

2

n

1

=

n

2

n

1

n

3

n

0

=

n

0

n

3

n

2

n

0

= n

2

n

0

n

3

n

1

n

0

=

n

1

n

0

n

3

n

2

n

1

n

0

=

n

2

n

1

n

0

Table 2: Time counter and

XOR operations producing the OVSF code chips

Binary counter Operation

000 0

001 n

2

010 n

1

011 n

2

n

1

100 n

0

101 n

2

n

0

110 n

1

n

0

111 n

2

n

1

n

0

Chip rate

counter

n8 n7 n6 n5 n4 n3 n2 n1 n0

b0 b1 b2 b3 b4 b5 b6 b7 b8

OVSF code ID register

fchip

clock

reset

fchip / SF

OVSF

code

chips

MSB

MSB

Fig. 2: OVSF code generator

.

.

230

The gate level schematics shown in Figs. 2 and 3 provide a

general framework, amenable to logic optimization. The logic

function can be preserved if all AND gates are replaced by more

efficient (in CMOS) NAND gates. OR gates are replaced by NOR

gates. The nine-input XOR tree is optimized for area, as the delay

is not a critical factor for this application.

5. TECHNIQUE 2: MANAGING THE ID NUMBER

An alternative technique for realizing the variable spreading

factor codes is to manage the code number loaded in the ID

register. The MSB is always n

8

and controlled by the LSB of a

regular binary counter 0 : (SF

max

1). The code number is shifted

such that the LSB is n

y

, where y = log

2

SF

max

log

2

SF.

A significant amount of additional logic circuitry is required to

produce a variable shift (dependent on the SF) of the code number

before insertion into the ID register. The information characterizing

the spreading factor and ID number of all of the required codes is

determined at the system level. The problem of varying the

spreading factors can be efficiently resolved by system software

when saving the ID numbers in global memory. The logic shift

operations can be conveniently performed in software. Once the ID

numbers are saved in the appropriate format, the numbers are

downloaded into the ID register. The circuit shown in Fig. 2 uses a

regular binary counter. This approach is illustrated by a few

examples shown in Fig. 4, which complements the circuit

illustrated in Fig. 2.

The stored values represent information describing the

spreading factor and code ID number required to generate the code.

As shown in Fig. 4, these values do not define a single code. The

generated chip sequences are identical for codes C

SF,N

, C

2SF,2N

,

C

4SF,4N

, etc. These code sequences differ only by the length (SF,

2SF, 4SF, etc.), but this parameter is only important for the

sampling moment of the despreading matched filter. The code

generator continuously produces chips from the required codes.

6. POWER DISSIPATION

The power consumed by the circuit changes dynamically

according to the OVSF code being generated. The fewer the

nonzero bits in the ID register, the less activity in the entire circuit,

thereby minimizing power. The effect of a variable counter cycle

on the power consumption is described in this section. This analysis

refers to the first technique (described in section 4 and illustrated in

Figs. 2 and 3), where the counter cycle is controlled by a variable

spreading factor.

The switching activity is maximum when the code C

SFmax,Nmax

=

C

512,511

is generated because the counter clock cycle is also

maximum and all of the bits of the ID register are logic one.

Alternatively, to generate C

4,2

, SF = 2

4

and N = 2, the counter

shifts from 0 to 3, and only one of the AND gates shown in Fig. 2

switches, consuming less power. Minimum power is consumed by

the circuit when C

512,1

is generated. In this case, the single nonzero

bit in the ID register is enabled by the most significant counter bit

(with the lowest switching activity). Static leakage power is

negligible in the target CMOS technologies and circuit densities.

The power consumed by the code generator is the sum of the

power consumed by the individual blocks. In order to estimate the

power dissipation, the switching activity of each individual block is

determined. The initial loading of the SF and ID registers is not

considered. The switching activity of the flip flops in a B-bit binary

counter (counting from 0 to 2

B

1) is listed in Table 3.

The combined switching activity of all stages over one counter

cycle is the sum of a geometric progression with the first term

a

1

= 2 and quotient q = 2,

( ) 1 2 2

q 1

q 1

a S

B

B

1 B

=

=

. (1)

The switching activity of the counter over F

chip

clock cycles is

( )

chip

B

B

B

N

chip

counter

F 2

2

1 2

1 2 2

2

F

A

= =

. (2)

The switching activity in a binary counter varies between F

chip

and 2F

chip

, approaching the maximum as B increases. Based on this

observation and a probabilistic analysis, the switching activity

bounds are derived for all blocks. Based on the gate level power

dissipation per MHz for the target 0.18 m CMOS technology [3],

minimum and maximum power dissipation bounds are estimated.

Power estimates for the first technique, realized by the circuits

shown in Figs. 2 and 3, are listed in Table 4. All of the data are

reported per MHz. The target technology library is discussed in the

following section.

This analysis refers to the general case of any variable cycle

counter and is particularly applicable to the circuits shown in Figs.

Table 3: Switching activity in an N-bit counter

Bit position B 1 B 2 2 1 0

Switching

activity over one cycle

2

1

2

2

2

B 2

2

B 1

2

B

n

8

n

7

n

6

n

5

n

4

n

3

n

2

n

1

n

0

System memory Generated OVSF codes

100000000 C4,2 or C8,4 or C16,8 or

110000000 C4,3 or C8,6 or C16,12 or

111000000 C8,7 or C16,14 or C32,28 or

101000000 C8,5 or C16,10 or C32,20 or

111100000 C16,15 or C32,30 or C64,60 or

Code ID register (from Fig. 2)

Fig. 4: Realization of variable spreading factor

by shifting the ID code number at the system level

SF

register

fchip

fchip / SF

s9 s8 ... s3 s2 0 0

MSB

FF8

D

rs

Q

Q

b8

Fig. 3: Chip rate counter from 0 to SF 1

with variable location of the LSB

FF7

D

rs

Q

Q

b7

FF6

D

rs

Q

Q

b6

FF0

D

rs

Q

Q

b0

231

2 and 3. As discussed in section 5, the hardware required for the

implementation of the second technique is limited to the circuit

shown in Fig. 2. The switching activity of the counter is maximum

since the maximum cycle of SF

max

= 512 is used. Significant power

and area savings, however, are realized since the SF register and

the control circuit for the counting cycle are not required. The

power dissipation is dependent on the OVSF code and, particularly,

on the number and location of the nonzero bits in the ID register.

7. LOGIC SYNTHESIS

The chip duration for UMTS systems is defined in [1] as

ns 260

10 84 . 3

1

F

1

T

6

chip

chip

= = . (3)

Since the critical path delay of the proposed circuit is significantly

smaller than T

chip

, the primary optimization criteria for the logic

synthesis process are area and power, which are well correlated. A

sample code generator is synthesized in Cadence Ambit Buildgates

using an Artisan Components standard cell library in 0.18 m

CMOS technology with a supply voltage of 1.8 volts [3]. For the

first technique, the total area occupied by the circuits shown in

Figs. 2 and 3 is 2100 m

2

with about 85% of the area occupied by

the three registers. Eliminating the cycle control circuit shown in

Fig. 3, the code generator based on the second technique occupies

approximately 1400 m

2

.

The critical path delay in both cases is

about 1 ns, such that a large number of OVSF codes can be

produced by a single generator.

The power dissipation of the circuit varies with the required

code as discussed in the previous section. For a 0.18 m

technology, the power dissipation is approximately 1 mW for the

first technique, assuming a standard chip rate clock of 3.84

Mchips/sec. Accounting for the reduced number of logic gates, the

second technique shown in Fig. 2 consumes about 0.9 mW.

8. SYSTEM LEVEL CONSIDERATIONS

The OVSF code generator proposed in this paper can be

applied to a number of different systems. Such systems include a

UMTS mobile terminal supporting up to six data channels or a base

station receiver processing the incoming signals from K mobile

users. System level tradeoffs are considered together with the

overall transmitter/receiver architecture. Different channelization

codes can be generated by sharing hardware. The proposed solution

produces significant savings in area and power since all

channelization codes for a single user (up to six) or multiple users

can be generated by a single circuit.

One code generator can serve both the receiver and transmitter

of a mobile terminal. As defined in the 3GPP standard [1], there is

either one code with a spreading factor in the range 4 to 512, or

there are several orthogonal codes but with SF fixed at 4. Both

techniques described in sections 4 and 5 can be applied. However,

considering the relatively small size of the transceiver circuit and

the importance of power dissipation and silicon area in portable

applications, the second technique is preferable. In certain cases,

however, a standalone solution such as the first technique can be

applicable when there is no control over the requirements of the

system software.

System specifications are different for a base station receiver,

where many codes of different spreading factors are required. The

software flexibility of the second solution is preferable due to the

reduced hardware complexity. The power efficiency of the

switching codes is enhanced as only the ID register is loaded. The

required change in system software significantly reduces the area

and power of all of the code generators in the base station.

Generally, the second technique described in section 5 offers a

better solution with increased power and area efficiency. This

method also provides more flexibility for dynamically changing the

generated code with minimum overhead in switching activity. A

change in the higher level system software is required, however, for

a shift operation before the code ID number is saved. Alternatively,

if such a requirement cannot be realized, the first solution,

discussed in section 4, can be used to design the OVSF code

generator. The additional hardware is the primary disadvantage of

the first technique.

9. CONCLUSIONS

The generation of orthogonal variable spreading factor codes

for third generation wireless systems is discussed in this paper and

two efficient solutions are proposed. The simplicity and flexibility

of the proposed circuits allow for significant area and power

savings since all of the channelization codes for a single user (up to

six) or multiple users can be produced by a single code generator.

This flexibility is essential for UMTS transceivers, since signals of

variable content and data rate requirements can be transmitted or

received by changing the number and spreading factors of the

channelization codes as specified by the 3GPP standard.

10. REFERENCES

[1] Third Generation Partnership Project; Technical Specification

Group Radio Access Network; 25.213, Spreading and

Modulation, Release 5, www.3gpp.org, September 2002.

[2] B. D. Andreev, E. G. Friedman, and E. Titlebaum, "Efficient

Implementation of a Complex 1 Multiplier," Proceedings of

the ACM Great Lakes Symposium on VLSI, pp. 83-88, April

2002.

[3] TSMC 0.18 m Process 1.8-Volt SAGE-X

TM

Standard Cell

Library Databook, Release 3.1, Artisan Components, October

2001.

Table 4: Power dissipation in OVSF generator blocks

per MHz of the chip clock rate

Artisan Components standard cell library in 0.18 m CMOS technology [3]

Switching

activity

Power / MHz

[nW / MHz]

Block

Min Max

Gate Power

[nW / MHz]

0.18 m Min Max

Counter 1.5 2 50 75 100

SF NAND2 1 15 15 15

SF NOR2 1.5 2 15 22 30

ID NAND2 1.5 2 15 22 30

XOR block 2.5 3 40 100 120

Entire code generator 234 295

232

You might also like

- Electrical Overstress (EOS): Devices, Circuits and SystemsFrom EverandElectrical Overstress (EOS): Devices, Circuits and SystemsNo ratings yet

- 0502 Cutler 36Document5 pages0502 Cutler 36DevRishi C. VijanNo ratings yet

- TTLDocument93 pagesTTLvitaly113No ratings yet

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- L02 MSP430Document34 pagesL02 MSP430Srinivas VN100% (1)

- Study On Equalizers: Anik Sengupta Sohom DasDocument11 pagesStudy On Equalizers: Anik Sengupta Sohom DasAnikSenguptaNo ratings yet

- ArmpptDocument168 pagesArmpptamit_k25No ratings yet

- Performance Analysis of Spreading and Modulation in WCDMA UplinkDocument5 pagesPerformance Analysis of Spreading and Modulation in WCDMA UplinkseventhsensegroupNo ratings yet

- Analysis and Design of Transmission-Line Structures by Means of The Geometric Mean DistanceDocument4 pagesAnalysis and Design of Transmission-Line Structures by Means of The Geometric Mean DistanceAnonymous BBX2E87aHNo ratings yet

- Implementation of Digital Clock On FPGA: Industrial Training Report ONDocument26 pagesImplementation of Digital Clock On FPGA: Industrial Training Report ONAdeel HashmiNo ratings yet

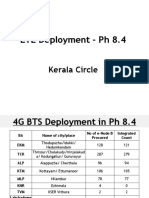

- 4G Deployment-Kerala CircleDocument31 pages4G Deployment-Kerala CircleVinothNo ratings yet

- 16 Micro-Programmed ControlDocument36 pages16 Micro-Programmed ControlJohn Paul Cordova100% (1)

- High Voltage Direct Current Transmission: Converters, Systems and DC GridsFrom EverandHigh Voltage Direct Current Transmission: Converters, Systems and DC GridsNo ratings yet

- Introduction to Mobile Network Engineering: GSM, 3G-WCDMA, LTE and the Road to 5GFrom EverandIntroduction to Mobile Network Engineering: GSM, 3G-WCDMA, LTE and the Road to 5GNo ratings yet

- MicrosequencerDocument38 pagesMicrosequencerJonathan MejiaNo ratings yet

- Unit 5a - CPU DesignDocument64 pagesUnit 5a - CPU DesignMʌŋı ßʌķŞhı100% (1)

- FIR FiltersDocument48 pagesFIR FiltersLjubodrag AvramovićNo ratings yet

- 64 Ia 32 Architectures Optimization ManualDocument842 pages64 Ia 32 Architectures Optimization ManualRaphael de Vasconcelos NascimentoNo ratings yet

- Ripple Carry and Carry Lookahead Adders: 1 ObjectivesDocument8 pagesRipple Carry and Carry Lookahead Adders: 1 ObjectivesYasser RaoufNo ratings yet

- DSP Processor FundamentalsDocument58 pagesDSP Processor FundamentalsSayee KrishnaNo ratings yet

- Convolutional Codes I Algebraic StructureDocument19 pagesConvolutional Codes I Algebraic StructureMarwan HammoudaNo ratings yet

- Messenger Development Without Internet Using Zigbee TechnologyDocument89 pagesMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyNo ratings yet

- FM RadioBoosterDocument2 pagesFM RadioBoosterVijay MirjeNo ratings yet

- Microcontroller ManualDocument91 pagesMicrocontroller ManualjayanthNo ratings yet

- Design of Synchronous FifoDocument18 pagesDesign of Synchronous Fifoprasu440No ratings yet

- ADPLL Design and Implementation On FPGADocument6 pagesADPLL Design and Implementation On FPGANavathej BangariNo ratings yet

- Interfacing Programs For 8085Document37 pagesInterfacing Programs For 8085archankumarturagaNo ratings yet

- (Model No:VBMB - 002) : 8-Bit Digital To Analog Converter Interface BoardDocument56 pages(Model No:VBMB - 002) : 8-Bit Digital To Analog Converter Interface BoardSanthanu Surendran100% (1)

- Fundamentals in Digital IC DesignDocument16 pagesFundamentals in Digital IC DesignSiddharth PanditNo ratings yet

- A CMOS Bandgap Reference Circuit With Sub-1V OperationDocument5 pagesA CMOS Bandgap Reference Circuit With Sub-1V Operationbooky_mookyNo ratings yet

- Circuit TodayDocument30 pagesCircuit TodayBrian GiriNo ratings yet

- HFIC Chapter 9 HF Mixer Switch Modulator DesignDocument48 pagesHFIC Chapter 9 HF Mixer Switch Modulator DesignAnonymous 39lpTJiNo ratings yet

- Microprosser 8085Document15 pagesMicroprosser 8085saigdv1978No ratings yet

- DSPDocument57 pagesDSPhamidr_karamiNo ratings yet

- VLSI Design: 2 To 4 DecoderDocument1 pageVLSI Design: 2 To 4 DecoderohgiggitygooNo ratings yet

- Implementation of A Complete GPS Receiver Using SimulinkDocument9 pagesImplementation of A Complete GPS Receiver Using SimulinkvwnunlaiNo ratings yet

- Ngspice 30 Manual PDFDocument631 pagesNgspice 30 Manual PDFHazelle MamugayNo ratings yet

- Sigma Delta Modulator NutshellDocument5 pagesSigma Delta Modulator NutshellZubair MohammedNo ratings yet

- 8051 Microcontroller FAQDocument160 pages8051 Microcontroller FAQkranthi633No ratings yet

- Important Instructions To Examiners:: (Autonomous)Document29 pagesImportant Instructions To Examiners:: (Autonomous)Rohit Shinde RSNo ratings yet

- Low Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsDocument11 pagesLow Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsIJAR JOURNALNo ratings yet

- NEA Assignment FinalDocument22 pagesNEA Assignment FinalSomnath Khamaru100% (1)

- Eric Thesis SlidesDocument43 pagesEric Thesis SlidesHumberto JuniorNo ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument5 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- Note On HFSS Field Calculator PDFDocument34 pagesNote On HFSS Field Calculator PDFpasquale_dottorato0% (1)

- IEEE Paper Problem StatementsDocument12 pagesIEEE Paper Problem StatementsKeerthiPratheek ReddyNo ratings yet

- Design of VLSI Architecture For A Flexible Testbed of Artificial Neural Network For Training and Testing On FPGADocument7 pagesDesign of VLSI Architecture For A Flexible Testbed of Artificial Neural Network For Training and Testing On FPGAInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Introduction To MicroprocessorDocument31 pagesIntroduction To MicroprocessorMuhammad DawoodNo ratings yet

- Ngspice ManualDocument564 pagesNgspice ManualLalan JoshiNo ratings yet

- Verilog Hardware Description LanguageDocument61 pagesVerilog Hardware Description LanguagesaravisaNo ratings yet

- Laboratory Exercise 3: Discrete-Time Signals: Frequency-Domain RepresentationsDocument18 pagesLaboratory Exercise 3: Discrete-Time Signals: Frequency-Domain RepresentationsNguyễn HưngNo ratings yet

- Real Time DSPDocument4 pagesReal Time DSPMuhammadNo ratings yet

- Binary MultiplierDocument14 pagesBinary MultiplierTaruna AggarwalNo ratings yet

- Worklog 5761 SyncDocument14 pagesWorklog 5761 Synctuanhai1989No ratings yet

- HSPICE Toolbox For Matlab and Octave (Also For Use With Ngspice)Document5 pagesHSPICE Toolbox For Matlab and Octave (Also For Use With Ngspice)Wala SaadehNo ratings yet

- Vlsi Mtech Jntu Kakinada II Sem SyllabusDocument16 pagesVlsi Mtech Jntu Kakinada II Sem Syllabusrv prasad50% (2)

- Very Important 1Document17 pagesVery Important 1Srikanth ChintaNo ratings yet

- Clothes ShopDocument1 pageClothes ShopSrikanth ChintaNo ratings yet

- IoetuhjteokwjgDocument1 pageIoetuhjteokwjgSrikanth ChintaNo ratings yet

- Book 4Document6 pagesBook 4Srikanth ChintaNo ratings yet

- Table View Data VersovaDocument192 pagesTable View Data VersovaSrikanth ChintaNo ratings yet

- PiojgoetjgDocument3 pagesPiojgoetjgSrikanth ChintaNo ratings yet

- HjgkijhkjkDocument2 pagesHjgkijhkjkSrikanth ChintaNo ratings yet

- R T0t9ig53ittjhoit3hjDocument2 pagesR T0t9ig53ittjhoit3hjSrikanth ChintaNo ratings yet

- 9 P 84 y 5 ItogjfklDocument5 pages9 P 84 y 5 ItogjfklSrikanth ChintaNo ratings yet

- Network Survey FeedbackDocument3 pagesNetwork Survey FeedbackSrikanth ChintaNo ratings yet

- O 7 W 6 KRLWJLKDocument4 pagesO 7 W 6 KRLWJLKSrikanth ChintaNo ratings yet

- (Oi 5 Utglit 5 EjkgDocument6 pages(Oi 5 Utglit 5 EjkgSrikanth ChintaNo ratings yet

- RhthyjDocument3 pagesRhthyjSrikanth ChintaNo ratings yet

- Oietuhy 9 P 468 WPDocument1 pageOietuhy 9 P 468 WPSrikanth ChintaNo ratings yet

- 0587 YuoitejgDocument3 pages0587 YuoitejgSrikanth ChintaNo ratings yet

- 35W546TGHUHKJDocument3 pages35W546TGHUHKJSrikanth ChintaNo ratings yet

- U 5 Gfior 3 J 2 Fno 3 RDocument2 pagesU 5 Gfior 3 J 2 Fno 3 RSrikanth ChintaNo ratings yet

- 987R9PUWJFMRLKFDocument2 pages987R9PUWJFMRLKFSrikanth ChintaNo ratings yet

- CS-2 CS-2 CS-2 CS-2 MCS-6 MCS-9 MCS-9 MCS-8 MCS-6 MCS-9 MCS-9 MCS-9 MCS-9 MCS-9 MCS-8 CS-2 MCS-8 CS-2 CS-2 CS-2 CS-2 CS-2Document4 pagesCS-2 CS-2 CS-2 CS-2 MCS-6 MCS-9 MCS-9 MCS-8 MCS-6 MCS-9 MCS-9 MCS-9 MCS-9 MCS-9 MCS-8 CS-2 MCS-8 CS-2 CS-2 CS-2 CS-2 CS-2Srikanth ChintaNo ratings yet

- TYF87T6IHDocument2 pagesTYF87T6IHSrikanth ChintaNo ratings yet

- 785 TyueoipehjflnvDocument1 page785 TyueoipehjflnvSrikanth ChintaNo ratings yet

- 98 EyhgteojrDocument1 page98 EyhgteojrSrikanth ChintaNo ratings yet

- RMAC UL MCS Ordered Range ReportDocument1 pageRMAC UL MCS Ordered Range ReportSrikanth ChintaNo ratings yet

- 15 MCS-1 47 1 5346 80 MCS-2 219 2 243 22 MCS-3 2470 3 50 995 MCS-4 13578 4 125 MCS-5 1187 MCS-6 6670 MCS-7 3367 MCS-8 7147 MCS-9 51904Document2 pages15 MCS-1 47 1 5346 80 MCS-2 219 2 243 22 MCS-3 2470 3 50 995 MCS-4 13578 4 125 MCS-5 1187 MCS-6 6670 MCS-7 3367 MCS-8 7147 MCS-9 51904Srikanth ChintaNo ratings yet

- BFDUIMNFDocument1 pageBFDUIMNFSrikanth ChintaNo ratings yet

- MoettijgDocument2 pagesMoettijgSrikanth ChintaNo ratings yet

- Oitjg 085 UyjDocument2 pagesOitjg 085 UyjSrikanth ChintaNo ratings yet

- J KK CFR WLRDocument1 pageJ KK CFR WLRSrikanth ChintaNo ratings yet

- New Microsoft Office Excel WorksheetDocument1,194 pagesNew Microsoft Office Excel WorksheetSrikanth ChintaNo ratings yet

- MoettijgDocument2 pagesMoettijgSrikanth ChintaNo ratings yet

- History of WiMAX Auto Saved)Document15 pagesHistory of WiMAX Auto Saved)Francis AmaningNo ratings yet

- Report Shangri Lai TG AruDocument23 pagesReport Shangri Lai TG AruDeden DarulNo ratings yet

- Principles of Electronic Communication Systems: Third EditionDocument57 pagesPrinciples of Electronic Communication Systems: Third EditionErwin Roquid IsagaNo ratings yet

- 2016 - SA-G+ 3G Novatel WirelessDocument2 pages2016 - SA-G+ 3G Novatel WirelessDario Gabriel Coz RojasNo ratings yet

- Online Submission of Forms by Private Candidates Comptt. Class X-Xii July 2019Document17 pagesOnline Submission of Forms by Private Candidates Comptt. Class X-Xii July 2019Aditya RajNo ratings yet

- Company Overview: Business SegmentsDocument5 pagesCompany Overview: Business SegmentsSai Shanmuk Dinakar GortiNo ratings yet

- Vodafone Taxation Case StudyDocument20 pagesVodafone Taxation Case Studygauravtu06No ratings yet

- AP BSNL Prepaid Special Tariff VouchersDocument3 pagesAP BSNL Prepaid Special Tariff Vouchersdox4printNo ratings yet

- COAI Annual Report 2009-10Document101 pagesCOAI Annual Report 2009-10cp91110No ratings yet

- Malitel Research DossierDocument2 pagesMalitel Research DossierTaley TabadiNo ratings yet

- IP Overview: Understanding IP Addresses, Classes, and Their ImportanceDocument70 pagesIP Overview: Understanding IP Addresses, Classes, and Their ImportanceElaine Tan-DiazNo ratings yet

- Presentation On HSDPA by Santosh Chapagain (065BEX434)Document9 pagesPresentation On HSDPA by Santosh Chapagain (065BEX434)Santosh ChapagainNo ratings yet

- MDS Orbit Platform: Grid SolutionsDocument4 pagesMDS Orbit Platform: Grid Solutionsoscar2102No ratings yet

- Naveen AirtelDocument68 pagesNaveen AirtellavishNo ratings yet

- 3G Neighbor List Planning GuideDocument3 pages3G Neighbor List Planning GuideOlumide Omoworare100% (1)

- Aloiamoa Anesi - Bluesky - Fixed Wireless 2021Document18 pagesAloiamoa Anesi - Bluesky - Fixed Wireless 2021ANo ratings yet

- Marketing Strategies of (SMART TELECOM) by JVC & LKI 2Document22 pagesMarketing Strategies of (SMART TELECOM) by JVC & LKI 2Lorgie Khim IslaNo ratings yet

- ShekharDocument4 pagesShekharHarish KumarNo ratings yet

- Netimizer Brouchure ENGDocument26 pagesNetimizer Brouchure ENGtrxopti9No ratings yet

- Matrix Navan Cnx200Document37 pagesMatrix Navan Cnx200Anu SuccenaNo ratings yet

- Sales and Distribution Strategy OF Micromax Mobile PhonesDocument4 pagesSales and Distribution Strategy OF Micromax Mobile PhonesAmit BohraNo ratings yet

- Boolean Search StringsDocument58 pagesBoolean Search Stringsselvalakshmi RNo ratings yet

- 3D INTERNET DocumentationDocument19 pages3D INTERNET DocumentationGowthami kurnuthalaNo ratings yet

- 3G Umts - FDD Code Planning: Scrambling, Channelisation and Synchronisation CodesDocument23 pages3G Umts - FDD Code Planning: Scrambling, Channelisation and Synchronisation CodeshshaiNo ratings yet

- Jazz 3-Days Internet Packages: Package Price Details Validity Activation CodeDocument12 pagesJazz 3-Days Internet Packages: Package Price Details Validity Activation CodeMansoor Alishah100% (1)

- Lavenia Nair - 2Document8 pagesLavenia Nair - 2johanis79No ratings yet

- Pemetel: Priit RoosipuuDocument18 pagesPemetel: Priit RoosipuuGourav BhardwajNo ratings yet

- Crown Castle Presentation NAREIT 2014 ReportDocument33 pagesCrown Castle Presentation NAREIT 2014 ReportSafe Tech For SchoolsNo ratings yet

- Research MethodsDocument13 pagesResearch MethodstessemaNo ratings yet