Professional Documents

Culture Documents

Schmitt Trigger

Uploaded by

Haja FarookOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Schmitt Trigger

Uploaded by

Haja FarookCopyright:

Available Formats

Figure 1: Schmitt Trigger

Figure 1 shows the circuit of a Schmitt trigger, the circuit of Schmitt trigger contains

of two identical transistors Q

1

and Q

2

coupled through an emitter R

E

. The resistor

R

1

and R

2

form a voltage divider across the V

CC

supply and ground. These resistors

provide a small forward bias on the base of transistor Q

2

.

Let us suppose that initially there is no signal at the input. Then as soon as the power

supply V

CC

is switched on, the transistor Q

2

starts conducting. The flow of its current

through resistor R

E

produces a voltage drop across it. This voltage drop acts as a

reverse bias across the emitter junction of transistor Q

1

due to which it cuts-off. As a

result of this, the voltage at its collector rises to V

CC

. This rising voltage is coupled to

the base of transistor Q

2

through the resistor R

1

.

It increases the forward bias at the

base of transistor Q

2

and therefore drives it into saturation and holds it there. At this

instant, the collector voltage, level are V

C1

= V

CC

and V

C2

= V

CE(sat)

as shown in Figure 2.

Now suppose an A.C. signal is applied at the input of the Schmitt trigger (i.e. at the

base of the transistor Q

1

). As the input voltage increases above zero, nothing will

happen till it crosses the upper trigger level (U.L.T). As the input voltage increases,

above the upper trigger level, the transistor Q

1

conducts. The point, at which it starts

conducting, is known as upper trigger point (U.T.P). As the transistor Q

1

conducts, its

collector voltage falls below V

CC

. This fall is coupled through resistor R

1

to the base of

transistor Q

2

which reduces its forward bias. This in turn reduces the current of

transistor Q

2

and hence the voltage drop across the resistor R

E

. As a result of this, the

reverse bias of transistor Q

1

is reduced and it conducts more. As the transistor

Q

1

conducts more heavily, its collector further reduces due to which the transistor

Q

1

conducts near cut-off. This process continues till the transistor Q

1

is driven into

saturation and Q

2

into cut-off. At this instant, the collector voltage levels are V

C1

=

V

CE(sat)

and V

C2

= V

CC

as shown in the figure.

The transistor Q

1

will continue to conduct till the input voltage falls below the lower

trigger level (L.T.L). It will be interesting to know that when the input voltage

becomes equal to the lower trigger level, the emitter base junction of transistor

Q

1

becomes reverse biased. As a result of this, its collector voltage starts rising

toward V

CC

. This rising voltage increases the forward bias across transistor Q

2

due to

which it conducts. The point, at which transistor Q

2

starts conducting, is called lower

trigger point (L.T.P). Soon the transistor Q

2

is driven into saturation and Q

1

to cur-off.

This completes one cycle. The collector voltage levels at this instant are V

C1

= V

CC

and

V

C2

= V

CE(sat)

. No change in state will occur during the negative half cycle of the input

voltage.

It is proved from the above discussion that the output of a Schmitt trigger is a positive

going pulse, whose width depends upon the time during which transistor Q

1

is

conducting. The conduction time is set by the upper and lower trigger levels.

You might also like

- DAF CF65/75/85 Series 0E621376Document712 pagesDAF CF65/75/85 Series 0E621376Dan Birkenhead95% (21)

- Multi VibratorDocument4 pagesMulti VibratorHaja FarookNo ratings yet

- Astable MultivibratorDocument5 pagesAstable Multivibratorbhanuka2009No ratings yet

- Astable MultivibratorDocument4 pagesAstable MultivibratorWaldo PulancoNo ratings yet

- Abert AinoDocument12 pagesAbert AinoAINOMUGISHA ABERTNo ratings yet

- Monostable MultivibratorDocument2 pagesMonostable MultivibratorsNo ratings yet

- 555 Tutorial 2Document13 pages555 Tutorial 2Mehar GuptaNo ratings yet

- Multi VibratorDocument4 pagesMulti VibratorAna Josefina BeltranNo ratings yet

- MultivibratorDocument4 pagesMultivibratorsakibNo ratings yet

- Multi VibratorDocument10 pagesMulti VibratorKeith BoltonNo ratings yet

- Schmmitt Trigger: Schmitt Trigger Is Binary Circuit and Closely Resembles A Mulativibroter. It Is ConsistofDocument4 pagesSchmmitt Trigger: Schmitt Trigger Is Binary Circuit and Closely Resembles A Mulativibroter. It Is ConsistofvarachillNo ratings yet

- Multi VibratorsDocument3 pagesMulti VibratorsShameer Sr S RNo ratings yet

- Dual Transistor Multivariate Circuit.Document3 pagesDual Transistor Multivariate Circuit.sbpatel123No ratings yet

- The Push Pull ConverterDocument2 pagesThe Push Pull ConverterNader Asgar Pangarungan MamarobaNo ratings yet

- Multi Vibrators WikipediaDocument13 pagesMulti Vibrators Wikipediasreedhar_vk280No ratings yet

- Unit Iv - Multivibrator CircuitsDocument29 pagesUnit Iv - Multivibrator CircuitsAshwini SaravannavarNo ratings yet

- Multivibrators OverviewDocument15 pagesMultivibrators OverviewAchuilNo ratings yet

- Module-3 Power AmplifierDocument16 pagesModule-3 Power Amplifierlikithapoojar888No ratings yet

- 1.b Circuit Diagram of A Monostable Multivibrator.Document2 pages1.b Circuit Diagram of A Monostable Multivibrator.Rajeshwari SNo ratings yet

- 3 Ece - PDC Unit - I PDFDocument64 pages3 Ece - PDC Unit - I PDFSree VamsiNo ratings yet

- Current Commutated Chopper Through SimulinkDocument54 pagesCurrent Commutated Chopper Through SimulinkAbhijeetSinha100% (1)

- New Class A p2Document1 pageNew Class A p2GGGGGPPPPPPNo ratings yet

- Monostable MutlivibratorDocument4 pagesMonostable MutlivibratorHarshal Paymode100% (1)

- Astable Multivibrator Using TransistorsDocument10 pagesAstable Multivibrator Using TransistorsGangireddy SanjeevNo ratings yet

- UNIT I - SCR Triggering and CommutationDocument14 pagesUNIT I - SCR Triggering and CommutationmalathynarayaniNo ratings yet

- Advance ElectronicsDocument8 pagesAdvance ElectronicswazidulNo ratings yet

- Phase Controlled RectifiersDocument51 pagesPhase Controlled RectifiersAkshay100% (1)

- Single Phase Series InverterDocument9 pagesSingle Phase Series InverterDhivya NNo ratings yet

- Module 2Document22 pagesModule 2canusha820No ratings yet

- RL & RCDocument43 pagesRL & RCThilaga MohanNo ratings yet

- Schmitt TriggerDocument9 pagesSchmitt TriggerMalliKarjunNo ratings yet

- 2095784617.power Electronics Unit IiDocument59 pages2095784617.power Electronics Unit IiSaranya. M SNSNo ratings yet

- Lec. 17Document22 pagesLec. 17Hira MunirNo ratings yet

- UNIT 3 - Part 2 - NotesDocument17 pagesUNIT 3 - Part 2 - NotesmourjyasanyNo ratings yet

- High Voltage Engineering (EEE-491) : Course Teacher: Fahim Mahmud Lecturer Department of Eee, CuetDocument13 pagesHigh Voltage Engineering (EEE-491) : Course Teacher: Fahim Mahmud Lecturer Department of Eee, CuetMD. MAHADI HASAN SAJIB 1602124No ratings yet

- TCVR (Thyristor Control Voltage Regulator)Document10 pagesTCVR (Thyristor Control Voltage Regulator)17TUEE247 VISHNUPRIYA.JNo ratings yet

- A Voltage Divider. 2. Two Comparators 3. An R-S Flip-Flop 4. An N-P-N TransistorDocument5 pagesA Voltage Divider. 2. Two Comparators 3. An R-S Flip-Flop 4. An N-P-N TransistorAzharAjjuNo ratings yet

- Basic Characteristics of Digital IcsDocument17 pagesBasic Characteristics of Digital IcsfgkloNo ratings yet

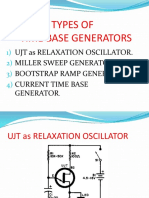

- Types of Time Base GeneratorsDocument14 pagesTypes of Time Base Generatorsraman yarramilliNo ratings yet

- Self Oscillating Flyback ConverterDocument7 pagesSelf Oscillating Flyback ConverterNaren DranNo ratings yet

- Push-Pull Class A Power AmplifierDocument4 pagesPush-Pull Class A Power Amplifierezhilarasi ezhilarsiNo ratings yet

- Unit 2 OscillatorDocument29 pagesUnit 2 Oscillatoripa76No ratings yet

- bài dịch trang 60Document4 pagesbài dịch trang 60Tran CuongNo ratings yet

- Diode TransistorDocument13 pagesDiode TransistorMG CuevasNo ratings yet

- Bistable Mono StableDocument30 pagesBistable Mono StableTurkish GatxyNo ratings yet

- RA100 RepairDocument1 pageRA100 RepairZoeloe_2No ratings yet

- Unit-I Linear WaveshapingDocument42 pagesUnit-I Linear Waveshapingsurya tejaNo ratings yet

- Unit-I Linear WaveshapingDocument46 pagesUnit-I Linear Waveshapingramaiah2369No ratings yet

- Unit-I Linear WaveshapingDocument42 pagesUnit-I Linear WaveshapingsuryaNo ratings yet

- 4 OscillatorsDocument12 pages4 OscillatorsTeshale AlemieNo ratings yet

- Bab 2 Inductors Capacitors and Alternating Current CircuitsDocument42 pagesBab 2 Inductors Capacitors and Alternating Current CircuitsVimal SaravananNo ratings yet

- V T) V I T) V R V R: Boost ConverterDocument3 pagesV T) V I T) V R V R: Boost Converterduppal35No ratings yet

- Unijunction Transistor: T.Y.B.Sc - Eletronics Power EletronicsDocument10 pagesUnijunction Transistor: T.Y.B.Sc - Eletronics Power EletronicsAvinash ChauhanNo ratings yet

- Op Amp and Transistor-Based Analog Square Wave Generator DesignDocument10 pagesOp Amp and Transistor-Based Analog Square Wave Generator DesignAto Triyono MetroNo ratings yet

- Switching Desain Power SupplyDocument4 pagesSwitching Desain Power SupplyZainul FananiNo ratings yet

- Silicon Controlled Rectifier-2Document10 pagesSilicon Controlled Rectifier-2Jenny MaristelaNo ratings yet

- Eec 225Document15 pagesEec 225Ezekiel Iyamu100% (1)

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Simeas T Transducers For Power Variables: Power Quality Catalog SR 10.4 1999Document43 pagesSimeas T Transducers For Power Variables: Power Quality Catalog SR 10.4 1999soltaniNo ratings yet

- Electrical Operation Manual: Vertical Machining CenterDocument107 pagesElectrical Operation Manual: Vertical Machining CenterHiều PhạmNo ratings yet

- Calculation of Induced Sheath Voltage For Transposed and Untransposed Cable ConductorsDocument6 pagesCalculation of Induced Sheath Voltage For Transposed and Untransposed Cable ConductorsPradeep PooNoorNo ratings yet

- 2600T Sensor TechnologyDocument23 pages2600T Sensor TechnologycemsavantNo ratings yet

- 11 12 Automatic Tension Control BTS VFDDocument2 pages11 12 Automatic Tension Control BTS VFDGioj MejNo ratings yet

- Simulation For Iot Based Smart Traffic Control System For Emergency VehiclesDocument44 pagesSimulation For Iot Based Smart Traffic Control System For Emergency VehiclesJeba JinilNo ratings yet

- Applications: PTC ThermistorDocument6 pagesApplications: PTC ThermistorJp NairNo ratings yet

- PULTRUSION MC - MANUAL - MODEL - AIHP-HGR-12 - 2GRP - Instruction Manual PDFDocument39 pagesPULTRUSION MC - MANUAL - MODEL - AIHP-HGR-12 - 2GRP - Instruction Manual PDFPartha PaulNo ratings yet

- 8259 PicDocument6 pages8259 PicpreethipattabiramanNo ratings yet

- Profile of HTGD EPCDocument31 pagesProfile of HTGD EPCAgung RahinoNo ratings yet

- Corneta 855-BN-D30-BDocument3 pagesCorneta 855-BN-D30-BnelsonNo ratings yet

- 37D Metal Gearmotors: Performance Summary and Table of ContentsDocument18 pages37D Metal Gearmotors: Performance Summary and Table of ContentsDavid Castillo UribeNo ratings yet

- Compre Est 2016Document11 pagesCompre Est 2016Maria Anndrea MendozaNo ratings yet

- AutosequencesDocument98 pagesAutosequencesJhonatanNo ratings yet

- List of Is StandardsDocument178 pagesList of Is StandardsRajesh Chunduru0% (1)

- Stealth Digital Analyzer: Why Sweep Is The Right SolutionDocument12 pagesStealth Digital Analyzer: Why Sweep Is The Right Solutionjalmeida88No ratings yet

- 9192 HART-Multiplexer AK00 III en PDFDocument4 pages9192 HART-Multiplexer AK00 III en PDFCristian PisitelloNo ratings yet

- Site Test Report Date: Al-Osais Co. KHUDARIYAH S/S 115/13.8 KV S/S CT Supervision Relay - MVTPDocument4 pagesSite Test Report Date: Al-Osais Co. KHUDARIYAH S/S 115/13.8 KV S/S CT Supervision Relay - MVTPsikander843562No ratings yet

- OLRDocument3 pagesOLRMazhar SaqlainNo ratings yet

- 3-Phase Motor Drives W Oscilloscope 48W-73863-0Document31 pages3-Phase Motor Drives W Oscilloscope 48W-73863-0CarloNo ratings yet

- List of 7400 Series Integrated Circuits PDFDocument22 pagesList of 7400 Series Integrated Circuits PDFduriiNo ratings yet

- Hemant NirmalkarDocument4 pagesHemant NirmalkarkrunalNo ratings yet

- Pure DataDocument11 pagesPure Datatcsaxtc0% (1)

- PSS Lab Manual - 18EEL76Document60 pagesPSS Lab Manual - 18EEL76Rohan J EEE-2019-23100% (1)

- BSC, BSC16 SW - DXAlarmsDocument191 pagesBSC, BSC16 SW - DXAlarmselmoustaphaelNo ratings yet

- LM 723Document21 pagesLM 723C.Rama MurthhyNo ratings yet

- Chapter2-1 - Overview of DC MachinesDocument40 pagesChapter2-1 - Overview of DC MachinesTabi4every175% (4)

- FC22 Bundle Transport For RadimatDocument40 pagesFC22 Bundle Transport For Radimatpk cfctkNo ratings yet

- Drive Spares Old PDFDocument3 pagesDrive Spares Old PDFmiguel angel vanegas medinaNo ratings yet