Professional Documents

Culture Documents

List Scheduling Review: The Ideal Scheduling Outcome: Hardware Resources

Uploaded by

KennethDelaCruzOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

List Scheduling Review: The Ideal Scheduling Outcome: Hardware Resources

Uploaded by

KennethDelaCruzCopyright:

Available Formats

1

List Scheduling

Todd C. Mowry

CS745: Optimizing Compilers

Todd C. Mowry CS745: Instruction Scheduling -2-

Review: The Ideal Scheduling Outcome

What prevents us from achieving this ideal?

Time

N cycles

Before

1 cycle

After

Todd C. Mowry CS745: Instruction Scheduling -3-

Review: Scheduling Constraints

Hardware Resources

finite set of FUs with instruction type, bandwidth, and

latency constraints

cache hierarchy also has many constraints

Data Dependences

cant consume a result before it is produced

ambiguous dependences create many challenges

Control Dependences

impractical to schedule for all possible paths

choosing an expected path may be difficult

recovery costs can be non-trivial if you are wrong

Todd C. Mowry CS745: Instruction Scheduling -4-

Scheduling Roadmap

List Scheduling:

within a basic block

y = c + d

x = a + b

Trace Scheduling:

across basic blocks

x = a + b

y = c + d

Software Pipelining:

across loop iterations

y = c + d

x = a + b

2

Todd C. Mowry CS745: Instruction Scheduling -5-

List Scheduling

The most common technique for scheduling instructions

within a basic block

We dont need to worry about:

control flow

We do need to worry about:

data dependences

hardware resources

Even without control flow, the problem is still NP-hard

y = c + d

x = a + b

Todd C. Mowry CS745: Instruction Scheduling -6-

List Scheduling Algorithm:

Inputs and Outputs

Algorithm reproduced from:

An Experimental Evaluation of List Scheduling", Keith D. Cooper, Philip J.

Schielke, and Devika Subramanian. Rice University, Department of Computer

Science Technical Report 98-326, September 1998.

Inputs:

Output:

Data Precedence

Graph (DPG)

Machine

Parameters

Scheduled Code

I0

---

I3

I10

I7

I2

I1

I8

---

I9

---

I4

I6

I11

I5

Cycle

0

1

2

3

4

I0 I2

I6 I4

I3 I8

I1

I5

I9

# of FUs:

2 INT, 1 FP

Latencies:

add = 1 cycle,

Pipelining:

1 add/cycle,

Todd C. Mowry CS745: Instruction Scheduling -7-

List Scheduling: The Basic Idea

Maintain a list of instructions that are ready to execute

data dependence constraints would be preserved

machine resources are available

Moving cycle-by-cycle through the schedule template:

choose instructions from the list & schedule them

update the list for the next cycle

I2 I0

Cycle

0

1

2

---

Todd C. Mowry CS745: Instruction Scheduling -8-

What Makes Life Interesting: Choice

Easy case:

all ready instructions can be scheduled this cycle

Interesting case:

we need to pick a subset of the ready instructions

List scheduling makes choices based upon priorities

assigning priorities correctly is a key challenge

I5 I1 I7

I5 I1 I2 I7 I0

???

3

Todd C. Mowry CS745: Instruction Scheduling -9-

Intuition Behind Priorities

Intuitively, what should the priority correspond to?

What factors are used to compute it?

data dependences?

machine parameters?

I0 I2

I6 I4

I3 I8

I1

I5

I9

# of FUs:

2 INT, 1 FP

Latencies:

add = 1 cycle,

Pipelining:

1 add/cycle,

Todd C. Mowry CS745: Instruction Scheduling -10-

Two different kinds of edges:

Why distinguish them?

do they affect scheduling differently?

What about output dependences?

Representing Data Dependences:

The Data Precedence Graph (DPG)

I0: x = 1;

I1: y = x;

I2: x = 2;

I3: z = x;

I2

I0

I3

I1

DPG

Code

true edges: E

(read-after-write) e = (I0,I1)

e = (I2,I3)

x

x

anti-edges: E

(write-after-read)

e = (I1,I2)

Todd C. Mowry CS745: Instruction Scheduling -11-

Computing Priorities

Lets start with just true dependences (i.e. edges in DPG)

Priority = latency-weighted depth in the DPG

I0 I2

I6 I4

I3 I8

I1

I5

I9

Todd C. Mowry CS745: Instruction Scheduling -12-

Computing Priorities (Cont.)

Now lets also take anti-dependences into account

i.e. anti-edges in the set E

I0 I2

I6 I4

I3 I8

I1

I5

I9

e

e

4

Todd C. Mowry CS745: Instruction Scheduling -13-

List Scheduling Algorithm

cycle = 0;

ready-list = root nodes in DPG; inflight-list = {};

while ((|ready-list|+|inflight-list| > 0) && an issue slot is available) {

for op = (all nodes in ready-list in descending priority order) {

if (an FU exists for op to start at cycle) {

remove op from ready-list and add to inflight-list;

add op to schedule at time cycle;

if (op has an outgoing anti-edge)

add all targets of ops anti-edges that are ready to ready-list;

}

}

cycle = cycle + 1;

for op = (all nodes in inflight-list)

if (op finishes at time cycle) {

remove op from inflight-list;

check nodes waiting for op & add to ready-list if all operands available;

}

}

}

Todd C. Mowry CS745: Instruction Scheduling -14-

Example

2 identical fully-pipelined FUs

adds take 2 cycles; all other insts take 1 cycle

I0: a = 1

I1: f = a + x

I2: b = 7

I3: c = 9

I4: g = f + b

I5: d = 13

I6: e = 19;

I7: h = f + c

I8: j = d + y

I9: z = -1

I10: JMP L1

I1

I8

I5

I6 I4 I7

I3

I10

I9

I2

I0

Cycle

0

1

2

3

4

5

6

Todd C. Mowry CS745: Instruction Scheduling -15-

Example

2 identical fully-pipelined FUs

adds take 2 cycles; all other insts take 1 cycle

I0: a = 1

I1: f = a + x

I2: b = 7

I3: c = 9

I4: g = f + b

I5: d = 13

I6: e = 19;

I7: h = f + c

I8: j = d + y

I9: z = -1

I10: JMP L1

I1

I8

I5

I6 I4 I7

I3

I10

I9

I2

I0

Cycle

0

1

2

3

4

5

6

I0 I2

I1 I3

I5 I9

I4 I7

I8 I6

--- ---

I10

Todd C. Mowry CS745: Instruction Scheduling -16-

What if We Break Ties Differently?

2 identical fully-pipelined FUs

adds take 2 cycles; all other insts take 1 cycle

I0: a = 1

I1: f = a + x

I2: b = 7

I3: c = 9

I4: g = f + b

I5: d = 13

I6: e = 19;

I7: h = f + c

I8: j = d + y

I9: z = -1

I10: JMP L1

I1

I8

I5

I6 I4 I7

I3

I10

I9

I2

I0

Cycle

0

1

2

3

4

5

6

1

2 3 3 2 3

4 4 4 5

6

5

Todd C. Mowry CS745: Instruction Scheduling -17-

What if We Break Ties Differently?

2 identical fully-pipelined FUs

adds take 2 cycles; all other insts take 1 cycle

I0: a = 1

I1: f = a + x

I2: b = 7

I3: c = 9

I4: g = f + b

I5: d = 13

I6: e = 19;

I7: h = f + c

I8: j = d + y

I9: z = -1

I10: JMP L1

I1

I8

I5

I6 I4 I7

I3

I10

I9

I2

I0

Cycle

0

1

2

3

4

5

6

I0 I2

I1 I5

I3 I8

I4 I7

I9 I6

I10

Todd C. Mowry CS745: Instruction Scheduling -18-

Contrasting the Two Schedules

Breaking ties arbitrarily may not be the best approach

I1

I8

I5

I6 I4 I7

I3

I10

I9

I2

I0

Cycle

0

1

2

3

4

5

6

I0 I2

I1 I3

I5 I9

I4 I7

I8 I6

--- ---

I10

Cycle

0

1

2

3

4

5

I0 I2

I1 I5

I3 I8

I4 I7

I9 I6

I10

1

2 3 3 2 3

4 4 4 5

6

Todd C. Mowry CS745: Instruction Scheduling -19-

Backward List Scheduling

Modify the algorithm as follows:

reverse the direction of all edges in the DPG

schedule the finish times of each operation

start times must still be used to ensure FU availability

Impact of scheduling backwards:

clusters operations near the end (vs. the beginning)

may be either better or worse than forward scheduling

Todd C. Mowry CS745: Instruction Scheduling -20-

Backward List Scheduling Example:

Lets Schedule it Forward First

Hardware parameters:

2 INT units: ADDs take 2 cycles; others take 1 cycle

1 MEM unit: stores (ST) take 4 cycles

Cycle

0

1

2

3

4

5

6

7

8

9

10

11

12

INT INT MEM

LDIa LSL LDIb LDIc LDId

ADDa ADDb ADDc ADDd ADDI

STa STb STc STd STe CMP

BR

LDIa LSL ----

LDIb LDIc ----

LDId ADDa ----

ADDb ADDc ----

ADDd ADDI STa

CMP ---- STb

---- ---- STc

---- ---- STd

---- ---- STe

---- ---- ----

---- ---- ----

---- ---- ----

BR ---- ----

6

Todd C. Mowry CS745: Instruction Scheduling -21-

Now Lets Try Scheduling Backward

Hardware parameters:

2 INT units: ADDs take 2 cycles; others take 1 cycle

1 MEM unit: stores (ST) take 4 cycles

Cycle

0

1

2

3

4

5

6

7

8

9

10

11

INT INT MEM

LDIa LSL LDIb LDIc LDId

ADDa ADDb ADDc ADDd ADDI

STa STb STc STd STe CMP

BR

LDIa ---- ----

ADDI LSL ----

ADDd LDIc ----

ADDc LDId STe

ADDb LDIa STd

ADDa ---- STc

---- ---- STb

---- ---- STa

---- ---- ----

---- ---- ----

CMP ---- ----

BR ---- ----

1

8 8 8

7

5 2 5 5 5 5

7 7 7

7

8 8

Todd C. Mowry CS745: Instruction Scheduling -22-

Contrasting Forward vs. Backward

List Scheduling

Cycle

0

1

2

3

4

5

6

7

8

9

10

11

INT INT MEM

LDIa ---- ----

ADDI LSL ----

ADDd LDIc ----

ADDc LDId STe

ADDb LDIa STd

ADDa ---- STc

---- ---- STb

---- ---- STa

---- ---- ----

---- ---- ----

CMP ---- ----

BR ---- ----

Cycle

0

1

2

3

4

5

6

7

8

9

10

11

12

INT INT MEM

LDIa LSL ----

LDIb LDIc ----

LDId ADDa ----

ADDb ADDc ----

ADDd ADDI STa

CMP ---- STb

---- ---- STc

---- ---- STd

---- ---- STe

---- ---- ----

---- ---- ----

---- ---- ----

BR ---- ----

backward scheduling clusters work near the end

backward is better in this case, but this is not always true

Forward Backward

Todd C. Mowry CS745: Instruction Scheduling -23-

Evaluation of List Scheduling

Cooper et al. propose RBF scheduling:

schedule each block M times forward & backward

break any priority ties randomly

For real programs:

regular list scheduling works very well

For synthetic blocks:

RBF wins when available parallelism (AP) is ~2.5

for smaller AP, scheduling is too constrained

for larger AP, any decision tends to work well

Todd C. Mowry CS745: Instruction Scheduling -24-

List Scheduling Wrap-Up

The priority function can be arbitrarily sophisticated

e.g., filling branch delay slots in early RISC processors

List scheduling is widely used, and it works fairly well

It is limited, however, by basic block boundaries

7

Todd C. Mowry CS745: Instruction Scheduling -25-

Scheduling Roadmap

List Scheduling:

within a basic block

y = c + d

x = a + b

Trace Scheduling:

across basic blocks

x = a + b

y = c + d

Software Pipelining:

across loop iterations

y = c + d

x = a + b

You might also like

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Lec18-Static BRANCH PREDICTION VLIWDocument40 pagesLec18-Static BRANCH PREDICTION VLIWi_2loveu3235No ratings yet

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Computer Science 146 Computer ArchitectureDocument13 pagesComputer Science 146 Computer ArchitectureharshvNo ratings yet

- PLC Programming & Implementation: An Introduction to PLC Programming Methods and ApplicationsFrom EverandPLC Programming & Implementation: An Introduction to PLC Programming Methods and ApplicationsNo ratings yet

- 2.advanced Compiler Support For ILPDocument16 pages2.advanced Compiler Support For ILPThyaga Rajan100% (1)

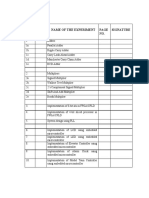

- S.No Date Name of The Experiment NO. SignatureDocument124 pagesS.No Date Name of The Experiment NO. Signaturekarthik2055No ratings yet

- U. Wisconsin CS/ECE 752 Advanced Computer Architecture IDocument74 pagesU. Wisconsin CS/ECE 752 Advanced Computer Architecture Igautamd07No ratings yet

- ECE 552 Chapter 2 - The Basics: Natalie Enright JergerDocument33 pagesECE 552 Chapter 2 - The Basics: Natalie Enright Jergersch123321No ratings yet

- Compiler Techniques For Exposing ILPDocument18 pagesCompiler Techniques For Exposing ILPDivya RadhakrishnanNo ratings yet

- 4.1 Basic Compiler Techniques For Exposing ILP Instruction-Level ParallelismDocument11 pages4.1 Basic Compiler Techniques For Exposing ILP Instruction-Level ParallelismRicher Zara MoranoNo ratings yet

- Unit Ii Program Design and Analysis: - Software Components. - Representations of Programs. - Assembly and LinkingDocument60 pagesUnit Ii Program Design and Analysis: - Software Components. - Representations of Programs. - Assembly and LinkingRahul SharmaNo ratings yet

- ArchitectureDocument5 pagesArchitectureLove SharmaNo ratings yet

- The Big Picture: Requirements Algorithms Prog. Lang./Os Isa Uarch Circuit DeviceDocument60 pagesThe Big Picture: Requirements Algorithms Prog. Lang./Os Isa Uarch Circuit DevicevshlvvkNo ratings yet

- Internal Structure of CPUDocument5 pagesInternal Structure of CPUSaad KhanNo ratings yet

- Reducing Pipeline Branch PenaltiesDocument4 pagesReducing Pipeline Branch PenaltiesSwagato MondalNo ratings yet

- Instruction Pipelining (Ii) : Reducing Pipeline Branch PenaltiesDocument4 pagesInstruction Pipelining (Ii) : Reducing Pipeline Branch Penaltiesdsvidhya123No ratings yet

- Krajewski Ism Ch16Document32 pagesKrajewski Ism Ch16Diego Andres Vasquez50% (2)

- Pipeline Processor DesignDocument89 pagesPipeline Processor Designkumarguptav91No ratings yet

- Lec-10 Software PipeliningDocument24 pagesLec-10 Software Pipelininghimanshu_agraNo ratings yet

- Techniques D'optimisation ArchitecturaleDocument109 pagesTechniques D'optimisation Architecturalesameer_m_daniNo ratings yet

- Traffic LightDocument19 pagesTraffic LightDianne ParNo ratings yet

- EXP 6 Serial AdderDocument2 pagesEXP 6 Serial Adderubuntu 13.0450% (2)

- ACA Unit 8 Hardware and Software For VLIW and EPIC Notes - Unit 8Document35 pagesACA Unit 8 Hardware and Software For VLIW and EPIC Notes - Unit 8Kedar KulkarniNo ratings yet

- CS 294-73 Software Engineering For Scientific Computing Lecture 14: Development For PerformanceDocument40 pagesCS 294-73 Software Engineering For Scientific Computing Lecture 14: Development For PerformanceEdmund ZinNo ratings yet

- Clock DrivenDocument10 pagesClock Drivenbevan678No ratings yet

- Practical 7 Time DelayDocument3 pagesPractical 7 Time DelayHet PatelNo ratings yet

- Lab 3Document5 pagesLab 3Wang WeiXinNo ratings yet

- Ca Final Fa19 BCS 087Document6 pagesCa Final Fa19 BCS 087ahmad razaNo ratings yet

- Unit IIDocument84 pagesUnit IISenthil RajNo ratings yet

- Hpu Improvement in DV Block Line: Ganesh C, Giridharan D., and Guided by A.Venkatesan (Hod/Ap-Mech)Document11 pagesHpu Improvement in DV Block Line: Ganesh C, Giridharan D., and Guided by A.Venkatesan (Hod/Ap-Mech)theijesNo ratings yet

- Pipeline Data Hazards: Example #1 - Write-Back Data HazardDocument6 pagesPipeline Data Hazards: Example #1 - Write-Back Data HazardVardhan RoyNo ratings yet

- AG1280Q48 Smallest System Board V1-Litron EDA Open Source Hardware PlatformDocument12 pagesAG1280Q48 Smallest System Board V1-Litron EDA Open Source Hardware PlatformgabonatorNo ratings yet

- Superscalar Vs VliwDocument8 pagesSuperscalar Vs Vliwpinaki_m771837No ratings yet

- Unit 5-Microcontroller ALPDocument44 pagesUnit 5-Microcontroller ALPsenthilNo ratings yet

- Chapter6 - PipeliningDocument61 pagesChapter6 - PipeliningNimmy MariamNo ratings yet

- Chapter6 - PipeliningDocument61 pagesChapter6 - PipeliningPrakash SubramanianNo ratings yet

- Tyler Wasilenko Assignment 4 BBUS3331 t00609747Document15 pagesTyler Wasilenko Assignment 4 BBUS3331 t00609747Martin Alejandro Rodriguez MartinezNo ratings yet

- Exercise 4Document4 pagesExercise 4Mashavia AhmadNo ratings yet

- CAunitiiiDocument36 pagesCAunitiiiKishore Arun KumarNo ratings yet

- Lecture 9: Case Study - MIPS R4000 and Introduction To Advanced PipeliningDocument23 pagesLecture 9: Case Study - MIPS R4000 and Introduction To Advanced PipeliningNithin KumarNo ratings yet

- Pai Ch05 QueueDocument34 pagesPai Ch05 QueueanonNo ratings yet

- PID ControlerDocument30 pagesPID ControlerRachmah RizkyNo ratings yet

- Slides-Session 7,8 and 9Document40 pagesSlides-Session 7,8 and 9Gabbar SinghNo ratings yet

- ASIC LabDocument75 pagesASIC LabMayur AgarwalNo ratings yet

- EEF011 Computer Architecture 計算機結構: Exploiting Instruction-Level Parallelism with Software ApproachesDocument40 pagesEEF011 Computer Architecture 計算機結構: Exploiting Instruction-Level Parallelism with Software Approachesi_2loveu32350% (1)

- 4 Bit Aritchmatic Logic UnitDocument18 pages4 Bit Aritchmatic Logic UnitMochamad Yusuf Abdul AzizNo ratings yet

- ENSA 312-38 QuestionDocument90 pagesENSA 312-38 QuestionPhoneit PoloNo ratings yet

- UartDocument19 pagesUartapi-26691029No ratings yet

- Rrlature Concept Called Cycle: TL Rvugh AsDocument20 pagesRrlature Concept Called Cycle: TL Rvugh AsKamal JaiswalNo ratings yet

- Operating System Solved Tutoral TwoDocument8 pagesOperating System Solved Tutoral TwovalentinemaryaNo ratings yet

- Mod - 6 Counter ADocument2 pagesMod - 6 Counter AAtit PatelNo ratings yet

- 4G Estimated Tput NokiaDocument17 pages4G Estimated Tput NokiasikasepkalemNo ratings yet

- Tutorial Sheet2014Document6 pagesTutorial Sheet2014Julia DanielNo ratings yet

- Concurrent Programming: Concurrency ConceptsDocument12 pagesConcurrent Programming: Concurrency ConceptsElaine LaLaNo ratings yet

- S-Curve Profile Without Motion ControllerDocument7 pagesS-Curve Profile Without Motion ControllerJordi Castro ÁlvarezNo ratings yet

- Stopwatch Using Logic GatesDocument7 pagesStopwatch Using Logic Gatesakarairi83% (6)

- Topic2c Ss DynamicschedulingDocument94 pagesTopic2c Ss DynamicschedulingCalam1tousNo ratings yet

- DWMC - Lecture2 8051 Programming (ESD 606)Document33 pagesDWMC - Lecture2 8051 Programming (ESD 606)sreenathpnNo ratings yet

- r13 Cse Os Lab ManualDocument53 pagesr13 Cse Os Lab ManualRsvv Prasad Rao100% (1)

- MS-7816 r10 PDFDocument40 pagesMS-7816 r10 PDFpedro arthur AlvesNo ratings yet

- System ArchitectureDocument122 pagesSystem ArchitectureAndres MarneNo ratings yet

- Prova Discursiva Ingles 01Document1 pageProva Discursiva Ingles 01Adriano PereiraNo ratings yet

- Sap AuditDocument2 pagesSap AuditsatyavaninaiduNo ratings yet

- Java Lab 2-1 Manual It & Cse2009-10Document79 pagesJava Lab 2-1 Manual It & Cse2009-10Vijay VallamdasNo ratings yet

- Designers Perspective SI PIDocument149 pagesDesigners Perspective SI PIsmtplvikasNo ratings yet

- Why Have Robots Caught On in ManufacturingDocument2 pagesWhy Have Robots Caught On in ManufacturingJayson Tasarra100% (1)

- Soundbanks and Falcon Expansions Installation Read MeDocument4 pagesSoundbanks and Falcon Expansions Installation Read MeAlexanderNo ratings yet

- An Improved Intrusion Detection System Using Machine Learning With Singular Value Decomposition and Principal Component AnalysisDocument14 pagesAn Improved Intrusion Detection System Using Machine Learning With Singular Value Decomposition and Principal Component AnalysisAli Asghar Pourhaji KazemNo ratings yet

- How To Add Arduino Gas Sensor Library in To Proteus ISIS 7 & 8 - Electronics Lovers Technology We LoveDocument10 pagesHow To Add Arduino Gas Sensor Library in To Proteus ISIS 7 & 8 - Electronics Lovers Technology We LoveindoramaNo ratings yet

- Ios Interview Worksheet: Objective-CDocument5 pagesIos Interview Worksheet: Objective-CathulsaiNo ratings yet

- Represent Real Life Situations Using Functions, Including Piecewise FunctionsDocument16 pagesRepresent Real Life Situations Using Functions, Including Piecewise FunctionsKC Campilan67% (3)

- 5 OlapDocument61 pages5 OlapMH PolashNo ratings yet

- Censoring & TruncationDocument14 pagesCensoring & TruncationkinshuksNo ratings yet

- Hello, Dolly!: Arr. For Guitar Yu - BoykoDocument4 pagesHello, Dolly!: Arr. For Guitar Yu - Boykohuong trinhNo ratings yet

- Price 14.10.2020Document120 pagesPrice 14.10.2020MurcaNo ratings yet

- Softwarisation of Wireless EquipmentDocument61 pagesSoftwarisation of Wireless EquipmentprateekiitkNo ratings yet

- MID1116ra Davao e PDFDocument27 pagesMID1116ra Davao e PDFPhilBoardResultsNo ratings yet

- Cyber BullyingDocument1 pageCyber Bullyingkororo mapaladNo ratings yet

- Add To Cart 15,00 EUR: Other Author's PublicationsDocument1 pageAdd To Cart 15,00 EUR: Other Author's PublicationsReo28No ratings yet

- Coverity AnalysisDocument6 pagesCoverity Analysisabhi9544444444No ratings yet

- Computer Aided Drug Design (Cadd) : Naresh.T M.Pharmacy 1 YR/1 SEMDocument40 pagesComputer Aided Drug Design (Cadd) : Naresh.T M.Pharmacy 1 YR/1 SEMJainendra JainNo ratings yet

- May Nhuom Hoa Mo Mien Dich Xmatrx - ELITEDocument4 pagesMay Nhuom Hoa Mo Mien Dich Xmatrx - ELITEnam7124119No ratings yet

- Three - BduDocument76 pagesThree - BduDharshini AnbazhaganNo ratings yet

- GIS Data Models: Faculty of Applied Engineering and Urban Planning Civil Engineering DepartmentDocument22 pagesGIS Data Models: Faculty of Applied Engineering and Urban Planning Civil Engineering DepartmentMohammed Al MaqadmaNo ratings yet

- Reliance JIO Project (Subhadarshi)Document62 pagesReliance JIO Project (Subhadarshi)Girish Kumar100% (1)

- HB Intro 20220302Document13 pagesHB Intro 20220302PradeepNo ratings yet

- What Is The Internet?: Prepared by Musbri Mohamed Pengurus Besar Yayasan PEKIDA MalaysiaDocument21 pagesWhat Is The Internet?: Prepared by Musbri Mohamed Pengurus Besar Yayasan PEKIDA Malaysiamusbri mohamed100% (12)

- Me2402 - CimDocument1 pageMe2402 - CimhariccetNo ratings yet

- Chapter 7: User-Defined MethodsDocument49 pagesChapter 7: User-Defined MethodsLasalle BoscoNo ratings yet