Professional Documents

Culture Documents

Rtes Lab3

Uploaded by

Muhammad Awais SattarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Rtes Lab3

Uploaded by

Muhammad Awais SattarCopyright:

Available Formats

Real Time Embedded Systems

EE Department

COMSATS Institute of Information

Technology, Lahore.

Real Time Embedded Systems

(Lab 3)

Qsys Introduction Using

Nios II System

Name ___________________________

Regd. Number_____________________

Instructor Signature_________________

Date______________ Marks_____________

CIIT, Lahore

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Qsys Introduction Using Nios II System

Objectives:

In this Lab you will be able to:

CIIT, Lahore

Learn about Nios II system

Learn about the Qsys

Creating a System with Qsys

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Introduction

Nios II System

The Nios II processor can be used with a variety of other components to form a complete

system. These components include a number of standard peripherals, but it is also

possible to define custom peripherals. Alteras DE2-70 Development and Education

board contains several components that can be integrated into a Nios II system. An

example of such a system is shown in Figure 1.

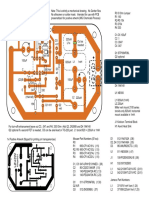

Figure 1. An example Nios II system

CIIT, Lahore

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

The Nios II processor and the interfaces needed to connect to other chips on the DE2-70

board are implemented in the Cyclone II FPGA chip. These components are

interconnected by means of the interconnection network called the Avalon Switch Fabric.

Memory blocks in the Cyclone II device can be used to provide an on-chip memory for

the Nios II processor. They can be connected to the processor either directly or through

the Avalon network. The SRAM and SDRAM memory chips on the DE2-70 board are

accessed through the appropriate interfaces. Input/output interfaces are instantiated to

provide connection to the I/O devices used in the system. A special JTAG UART

interface is used to connect to the circuitry that provides a Universal Serial Bus (USB)

link to the host computer to which the DE2-70 board is connected. This circuitry and the

associated software is called the USB-Blaster. Another module, called the JTAG Debug

module, is provided to allow the host computer to control the Nios II processor. It makes

it possible to perform operations such as downloading programs into memory, starting

and stopping execution, setting program breakpoints, and collecting real-time execution

trace data.

Since all parts of the Nios II system implemented on the FPGA chip are defined by using

a hardware description language, a knowledgeable user could write such code to

implement any part of the system. This would be an onerous and time consuming task.

Instead, one can use the Qsys tool in the Quartus II software to implement a desired

system simply by choosing the required components and specifying the parameters

needed to make each component fit the overall requirements of the system.

CIIT, Lahore

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Qsys Tool

Qsys is a powerful system integration tool which is included as part of the Quartus II

software. Qsys captures system level hardware designs at a relatively high level of

abstraction and also automates the task of defining and integrating customized HDL

components, which may include IP cores, verification IP, and other design modules. Qsys

facilitates design reuse by packaging and making available your custom components and

systems. Qsys integrates your custom components with Altera and third-party developer

components. In some cases, you can implement an entire design using components from

the Altera component library. During system generation, Qsys automatically creates highperformance interconnect logic from the connectivity options you specify, eliminating the

error-prone and time-consuming task of writing HDL to specify the system-level

connections.

Qsys provides the following advantages for hardware system design:

CIIT, Lahore

Automates the process of customizing and integrating components

Supports modular system design

Supports visualization of large systems

Supports optimization of interconnect fabric and pipelining within the system

Fully integrated with the Quartus II software

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Defining and Generating the System in Qsys

The design you build in this lab is a small NIOS II system consist of the following

components.

Nios II/s processor core

On-chip memory

JTAG UART

ALTPLL

System ID peripheral

Start the Quartus II Software

First open the Quatus II software and create the new project in your desired directory as

you have done in your first lab.

Create a New Qsys System

You use Qsys to generate the Nios II processor system, adding the desired components,

and configuring how they connect together. To create a new Qsys system, click Qsys on

the Tools menu in the Quartus II software. Qsys starts and displays the System Contents

tab as shown in figure 2.

CIIT, Lahore

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Figure 2: Qsys GUI in its initial state

Define the System in Qsys

You use Qsys to define the hardware characteristics of the Nios II system, such as which

Nios II core to use, and what components to include in the system. Qsys does not define

software behavior, such as where in memory to store instructions or where to send the

stderr character stream.

In this section, you perform the following steps:

1. Add the Nios II core, on-chip memory, and other components.

2. Specify base addresses and interrupt request (IRQ) priorities.

3. Generate the Qsys system.

CIIT, Lahore

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Clock Settings

On the Clock Settings tab shown in figure 2, double-click the clock frequency in the MHz

column for clk_0 is the default clock input name for the Qsys system. The frequency you

specify for clk_0 must match the oscillator that drives the FPGA. Type the clock

frequency and press Enter.

Next, you begin to add hardware components to the Qsys system. As you add each

component, you configure it appropriately to match the design specifications.

Add the On-Chip Memory

Processor systems require at least one memory for data and instructions. This design

example uses one 20 KB on-chip memory for both data and instructions. To add the

memory, perform the following steps:

1. On the Component Library tab (to the left of the System Contents tab), expand

Memories and Memory Controllers, expand On-Chip, and then click On-Chip

Memory (RAM or ROM).

2. Click Add. The On-Chip Memory (RAM or ROM) parameter editor appears. Figure 3

shows the GUI.

3. In the Block type list, select Auto.

4. In the Total memory size box, type 20480 to specify a memory size of 20 KB.

5. Click Finish. You return to Qsys.

6. Click the System Contents tab. An instance of the on-chip memory appears in the

system contents table.

CIIT, Lahore

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Figure 3: Onchip memory GUI parameter editor

7. In the Name column of the system contents table, right-click the on-chip memory and

click Rename.

8. Type onchip_mem and press Enter.

CIIT, Lahore

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Add the ALTPLL

A PLL is a control system that generates an output signal whose phase is related to the

phase of an input signal. The oscillator generates a periodic signal. The phase detector

compares the phase of that signal with the phase of the input periodic signal and adjusts

the oscillator to keep the phases matched. Bringing the output signal back toward the

input signal for comparison is called a feedback loop since the output is 'fed back' toward

the input forming a loop.

Perform the following steps to add the ALTPLL:

1. On the Component Library tab, expand PLL, and then click Avalon ALTPLL.

2. Click Add. The ALTPLL parameter editor appears as shown in figure 4.

Figure 4: ALTPLL parameter editor

CIIT, Lahore

10

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

3. Enter your desired frequency in the frequency tab in the editor window.

4. Select the output clocks tab, and select the output clock frequency by check the box

shown in figure 5.

Figure 5: ALTPLL parameter editor

5. Click Finish. You return to the Qsys System Contents tab, and an instance of the

ALTPLL appears in the system contents table.

6. In the Name column, right-click the altpll_0 and click Rename.

7. Type pll_0 and press Enter.

CIIT, Lahore

11

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Add the Nios II Processor Core

In this section you add the Nios II/s core and configure it to use 2 KB of on-chip

instruction cache memory. For educational purposes, design example uses the Nios II/s

(standard) core, which provides a balanced trade-off between performance and resource

utilization. In reality, the Nios II/s core is more powerful than necessary for most simple

control applications. Perform the following steps to add a Nios II/s core to the system:

1. On the Component Library tab, expand Processors, and then click Nios II Processor.

2. Click Add. The Nios II Processor parameter editor appears, displaying the Core Nios II

tab. Figure 6 shows the GUI.

3. Under Select a Nios II core, select Nios II/s.

4. In the Hardware multiplication type list, select None.

5. Turn off Hardware divide.

6. Click Finish. You return to the Qsys System Contents tab, and an instance of the Nios

II core appears in the system contents table. Ignore the exception and reset vector error

messages. You resolve these errors in steps 13and 14.

7. In the Name column, right-click the Nios II processor and click Rename.

8. Type cpu and press Enter.

9. In the Connections column, connect the c0 port of the pll to both the clk1port of the

on-chip memory and the clk port of the Nios II processor by clicking the hollow dots on

the connection line. The dots become solid indicating the ports are connected.

10. Connect the s1 port of the on-chip memory to both the data_master port and

instruction_master port of the Nios II processor.

11. Connect the clk port of the clk_0 clock source to the inclk_interface port of the pll_0.

9. Connect the data_master port of the Nios II to the pll_slave port of the ALTPLL.

CIIT, Lahore

12

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Figure 6: Core Nios II tab of the Nios II Processor parameter editor

10. Double-click the Nios II processor row of the system contents table to reopen the

Nios II Processor parameter editor.

11. Under Reset Vector, select onchip_mem.s1in the Reset vector memory list and type

0x0 in the Reset vector offset box.

CIIT, Lahore

13

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Figure 7: Caches and Memory Interfaces tab of the Nios II Processor parameter editor

12. Under Exception Vector, select onchip_mem.s1in the Exception vector memory list

and type 0x20in the Exception vector offset box.

13. Click the Caches and Memory Interfaces tab. Figure 7 shows the GUI.

14. In the Instruction cache list, select 2Kbytes.

15. In the Burst transfers list, select Disable.

16. In the Number of tightly coupled instruction master port(s) list, select None.

17. Click Finish. You return to the Qsys System Contents tab.

CIIT, Lahore

14

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Add the JTAG UART

The JTAG UART provides a convenient way to communicate character data with the

Nios II processor through the USB-Blaster download cable. Perform the following steps

to add the JTAG UART:

1. On the Component Library tab, expand Interface Protocols, expand Serial, and then

click JTAG UART.

2. Click Add. The JTAG UART parameter editor appears sown in figure 8.

Figure 8: JTAG UART parameter editor

CIIT, Lahore

15

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

3. Click Finish. You return to the Qsys System Contents tab, and an instance of the

JTAG UART appears in the system contents table.

4. In the Name column, right-click the JTAG UART and click Rename.

5. Type jtag_uart and press Enter.

6. Connect the c0 port of the pll to the clk port of the JTAG UART

7. Connect the data_master port of the Nios II processor to the avalan_jtag_slave port of

the JTAG UART.

8. Connect the interrupt port of the Nios II processor to the interrupt port of the JTAG

UART.

Add the System ID Peripheral

The system ID peripheral safeguards against accidentally downloading software

compiled for a different Nios II system. If the system includes the system ID peripheral,

the Nios II SBT for Eclipse can prevent you from downloading programs compiled for a

different system.

Perform the following steps to add the system ID peripheral:

1. On the Component Library tab, expand Peripherals, expand Debug and Performance,

and then click System ID Peripheral.

2. Click Add. The System ID Peripheral parameter editor appears shown in figure 9.

3. Click Finish. You return to the Qsys System Contents tab, and an instance of the

system ID peripheral appears in the system contents table.

4. In the Name column, right-click the system ID peripheral and click Rename.

5. Type sysid and press Enter.

CIIT, Lahore

16

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Figure 9: System ID Peripheral parameter editor

6. Connect the c0 of the pll to the clk port of the system ID peripheral.

.

7. Connect the data_master port of the Nios II processor to the control_slave port of the

system ID peripheral.

CIIT, Lahore

17

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Specify Base Addresses and Interrupt Request Priorities

At this point, you have added all the necessary hardware components to the system. Now

you must specify how the components interact to form a system. In this section, you

assign base addresses for each slave component, and assign interrupt request (IRQ)

priorities for the JTAG UART.

Qsys provides the Assign Base Addresses command which makes assigning component

base addresses easy. For many systems, including this design example, Assign Base

Addresses is adequate.

Qsys also provides an Assign Interrupt Numbers command which connects IRQ signals

to produce valid hardware results. However, assigning IRQs effectively requires an

understanding of how software responds to them. Because Qsys does not know the

software behavior, Qsys cannot make educated guesses about the best IRQ assignment.

To assign appropriate base addresses and IRQs, perform the following steps:

1. On the System menu, click Assign Base Addresses to make Qsys assign functional

base addresses to each component in the system.

2. In the IRQ column, connect the Nios II processor to the JTAG UART.

3. Click the IRQ value for the jtag_uart component to select it.

4. Type 0 and press Enter to assign a new IRQ value.

Figure 10 shows the Qsys System Contents tab with the complete system.

Generate the Qsys System

You are now ready to generate the Qsys system. Perform the following steps:

1. Click the Generation tab.

2. Select None in both the Create simulation model and Create test bench Qsys system

lists. Because this lab does not cover the hardware simulation flow, you can select these

settings to shorten generation time.

CIIT, Lahore

18

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Figure 10. System Contents Tab with Complete System

3. Click Generate. The Save changes? dialog box appears, prompting you to save your

design.

4. Type first_nios2_system in the File name box and click Save. The Generate dialog

box appears and system generation process begins.

The generation process can take several minutes. Output messages appear as

generation progresses. When generation completes, the final "Info: Finished: Create

HDL design files for synthesis" message appears. Figure 11 shows the successful

system generation.

CIIT, Lahore

19

Lab Instructor

M Ali Raza

Real Time Embedded Systems

EE Department

Figure 11: Successful system generation

5. Click Close to close the dialog box.

6. On the File menu, click Exit to close Qsys and return to the Quartus II software.

You have finished creating the Nios II processor system. You are ready to integrate the

system into the Quartus II hardware project and use the Nios II SBT for Eclipse to

develop software.

CIIT, Lahore

20

Lab Instructor

M Ali Raza

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Lab Report#4 Serial Communication With Atmega328p/Arduino Uno and Testing With HyperterminalDocument4 pagesLab Report#4 Serial Communication With Atmega328p/Arduino Uno and Testing With Hyperterminalhamza shahbazNo ratings yet

- Reference Copy: Federal Communications CommissionDocument5 pagesReference Copy: Federal Communications CommissionA. D.No ratings yet

- Sleek Performance.: SLIM 7 (14")Document4 pagesSleek Performance.: SLIM 7 (14")RaditNo ratings yet

- Desulfator PCB PDFDocument1 pageDesulfator PCB PDFMarco Antonio NardyNo ratings yet

- POWERTRONIX 3 Phase Auto TransformersDocument1 pagePOWERTRONIX 3 Phase Auto TransformersJhon J TristanchoNo ratings yet

- Next Generation ExchangeDocument15 pagesNext Generation ExchangeVinay TannaNo ratings yet

- 1.1 Hardware and SoftwareDocument13 pages1.1 Hardware and SoftwareAqilah HasmawiNo ratings yet

- Wiring Operation of Washing Machine FDDocument18 pagesWiring Operation of Washing Machine FDRamil Tuason100% (2)

- BSNL 5-EssDocument28 pagesBSNL 5-EssGaurav100% (1)

- 03 RA4133 RL20 LTE KPI Architecture E01Document46 pages03 RA4133 RL20 LTE KPI Architecture E01Teguh YuliantoNo ratings yet

- Blackcore Raptor Lake Spec SheetDocument3 pagesBlackcore Raptor Lake Spec SheetNadendla mastan raoNo ratings yet

- PDFDocument2 pagesPDFInsyafa NalaprajaNo ratings yet

- ParameterDocument175 pagesParameterDilip GamiNo ratings yet

- Hardware QuestionnaireDocument2 pagesHardware QuestionnaireShakila ShakiNo ratings yet

- Parameter: Sub-System Number: SSN Value SSN SCCP User DescriptionDocument4 pagesParameter: Sub-System Number: SSN Value SSN SCCP User DescriptionSrinath Vasam100% (1)

- What Is A Wireless RouterDocument3 pagesWhat Is A Wireless RouterJose C. Lita JrNo ratings yet

- ECZ Computer Studies P1 Past Paper 2015 2016 2017Document27 pagesECZ Computer Studies P1 Past Paper 2015 2016 2017Bricious Mulimbi100% (2)

- Luxomat: PD9-M-1C/S-SDB-IP65 (-GH)Document2 pagesLuxomat: PD9-M-1C/S-SDB-IP65 (-GH)gabby corpuzNo ratings yet

- LAB 7: IIR Filter Design ObjectivesDocument13 pagesLAB 7: IIR Filter Design Objectivesmjrahimi.eee2020No ratings yet

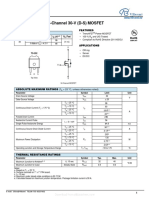

- PHD78NQ03LT: N-Channel 30-V (D-S) MOSFETDocument8 pagesPHD78NQ03LT: N-Channel 30-V (D-S) MOSFETNikolay ShkolkinNo ratings yet

- Variable DC Power SupplyDocument8 pagesVariable DC Power SupplyAizaz Hussain ShahNo ratings yet

- Siklu DS EtherHaul 8010FX PDFDocument2 pagesSiklu DS EtherHaul 8010FX PDFJosé MoralesNo ratings yet

- List Alat TrimbleDocument4 pagesList Alat TrimbleAldi SuyanaNo ratings yet

- LTE - Alarm MappingDocument4 pagesLTE - Alarm MappingEhtesham KhanNo ratings yet

- Grundig E100 Shortwave Radio ManualDocument102 pagesGrundig E100 Shortwave Radio Manualnaupas007No ratings yet

- Digital Predistortion For RF Power AmplifiersDocument4 pagesDigital Predistortion For RF Power AmplifiersxinlivuNo ratings yet

- Fractional-N Frequency SynthesizerDocument5 pagesFractional-N Frequency SynthesizerbaymanNo ratings yet

- Sandeep Singh Ward No-3, V.P.O-Hathin, Dis-Palwal: Working in IPTX Team As DWDM IP OPERATION Engg..Japan NetworkDocument4 pagesSandeep Singh Ward No-3, V.P.O-Hathin, Dis-Palwal: Working in IPTX Team As DWDM IP OPERATION Engg..Japan NetworkGaurav GaudNo ratings yet

- CBSE UGC NET Electronic Science Paper 2 June 2007Document14 pagesCBSE UGC NET Electronic Science Paper 2 June 2007Bhargav. GNo ratings yet

- Sfs Det Chart-Eid-RfsebdiDocument1 pageSfs Det Chart-Eid-Rfsebdiherbster28No ratings yet