0% found this document useful (0 votes)

143 views1 pageComputer Architecture Lesson Plan

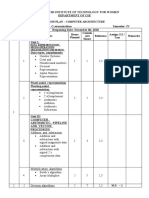

This document contains a lesson plan for a class on computer architecture. It includes objectives like understanding the basic structure and operation of a digital computer. It covers topics like functional units, memory systems, arithmetic operations, control systems, pipelining, and I/O devices over five units. The topics will be discussed across 30 periods, referencing pages from textbooks. The lesson plan defines key terms and lists learning objectives to provide students with a thorough overview of computer architecture concepts.

Uploaded by

stintuCopyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOC, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

143 views1 pageComputer Architecture Lesson Plan

This document contains a lesson plan for a class on computer architecture. It includes objectives like understanding the basic structure and operation of a digital computer. It covers topics like functional units, memory systems, arithmetic operations, control systems, pipelining, and I/O devices over five units. The topics will be discussed across 30 periods, referencing pages from textbooks. The lesson plan defines key terms and lists learning objectives to provide students with a thorough overview of computer architecture concepts.

Uploaded by

stintuCopyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOC, PDF, TXT or read online on Scribd