Professional Documents

Culture Documents

VHDL Laboratory Exercises Full

VHDL Laboratory Exercises Full

Uploaded by

Patrick RamosCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VHDL Laboratory Exercises Full

VHDL Laboratory Exercises Full

Uploaded by

Patrick RamosCopyright:

Available Formats

Practical VHDL samples

The following is a list of files used as examples in the ESD3 lectures.

The files are included overleaf with simulations and also post-synthesis schematics.

The target synthesis library is the Xilinx 4000 series of FPGAs- details of all the components are given at the end.

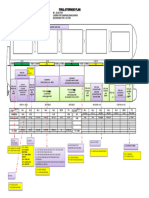

Source Name

Entity Name

Description

andgate.vhd

andgate

Simple AND Gate

pencoder.vhd

mux.vhd

simpreg.vhd

par2ser.vhd

pencoder

mux

simpreg

par2ser

Synthesisable?

4

Implements a simple AND gate. Illustrates a very simple VHDL

source code file- with entity and architecture.

Implements a simple 2 input priority encoder. Illustrates the use of

IF-THEN-ELSE as a prioritised selector.

Implements a simple 2->1 multiplexer with selection input.

Demonstrates the use of the CASE statement as an equal priority

selector.

Implements a simple 8-bit register. Illustrates the inference of

loadable registers etc.

Implements a simple parallel-serial converter- with load and shift left

modes. Illustrates the use of the FOR loop to facilitate multiple access

operations. Also illustrates the use of internal signals.

2 Input Priority Encoder

2->1 Multiplexer

Simple 8 Bit Register

Parallel to Serial

Converter

Comments

Feb 22 1999 09:59

andgate.vhd

Page 1

-------------------------------------------------------------------------------- Title

: Simple AND Gate Instantiation in VHDL

-- Project

: Digital Design IV

-------------------------------------------------------------------------------- File

: andgate.vhd

-- Author

:

<Craig Slorach@HANDEL>

-- Created

: 1999/02/05

-- Last modified : 1999/02/05

-------------------------------------------------------------------------------- Description :

-- Implements a simple AND gate in VHDL- used to highlight both entity

-- and internal architecture.

-------------------------------------------------------------------------------- Modification history :

-- 1999/02/05 : created

------------------------------------------------------------------------------library ieee;

use ieee.std_logic_1164.all;

entity ANDGATE is

port (A,B : in std_logic;

Z : out std_logic);

-- data inputs

-- data output

end ANDGATE;

-- purpose: Implement architecture

architecture MYARCH of ANDGATE is

begin

-- MYARCH

Z <= A and B;

end MYARCH;

Feb 22 1999 09:53

pencoder.vhd

Page 1

-------------------------------------------------------------------------------- Title

: Priority encoder (illustrate IF-THEN-ELSE)

-- Project

: Digital Design IV

-------------------------------------------------------------------------------- File

: pencoder.vhd

-- Author

:

<craigs@HANDEL>

-- Created

: 1999/02/19

-- Last modified : 1999/02/19

-------------------------------------------------------------------------------- Description :

-- Implements a simple priority encoder in VHDL. This code demonstrates

-- a simple examples of the IF-THEN-ELSE statement as a prioritised

-- selector.

-------------------------------------------------------------------------------- Modification history :

-- 1999/02/19 : created

------------------------------------------------------------------------------library ieee;

use ieee.std_logic_1164.all;

entity PENCODER is

port (DATAIN : in std_logic_vector(1 downto 0); -- data input

DATAOUT : out std_logic;

-- data out

CLK,RESET : in std_logic);

-- clock and reset

end PENCODER;

-- purpose: Implement main architecture of PENCODER

architecture BEHAVIOR of PENCODER is

begin

-- BEHAVIOR

-- purpose: Main process

process (CLK, RESET)

begin -- process

-- activities triggered by asynchronous reset (active high)

if RESET = 1 then

DATAOUT <= 0;

-- default output

-- activities triggered by rising edge of clock

elsif CLKevent and CLK = 1 then

if DATAIN(0)=1 then

DATAOUT <= 0;

elsif DATAIN(1)=1 then

DATAOUT <= 1;

end if;

end if;

end process;

end BEHAVIOR;

Feb 22 1999 09:53

mux.vhd

Page 1

-------------------------------------------------------------------------------- Title

: Multiplexer in VHDL

-- Project

: Digital Design IV

-------------------------------------------------------------------------------- File

: mux.vhd

-- Author

:

<craigs@HANDEL>

-- Created

: 1999/02/19

-- Last modified : 1999/02/19

-------------------------------------------------------------------------------- Description :

-- Implement a simple 2->1 multiplexer in VHDL.

-------------------------------------------------------------------------------- Modification history :

-- 1999/02/19 : created

------------------------------------------------------------------------------library ieee;

use ieee.std_logic_1164.all;

entity MUX is

port (SEL : in std_logic;

-- select input

DATAIN : in std_logic_vector(1 downto 0); -- Input data

DATAOUT : out std_logic);

-- Output data

end MUX;

-- purpose: Implement main architecture of MUX

architecture BEHAVIOR of MUX is

begin

-- BEHAVIOR

-- purpose: Main process

-- type:

memoryless

-- inputs:

-- outputs:

process (SEL,DATAIN)

begin

-- process

case SEL is

when 0 =>

DATAOUT <= DATAIN(0);

when others =>

DATAOUT <= DATAIN(1);

end case;

end process;

end BEHAVIOR;

Feb 22 1999 10:08

simpreg.vhd

Page 1

-------------------------------------------------------------------------------- Title

: Simple Register Example

-- Project

: Digital Design IV

-------------------------------------------------------------------------------- File

: simpreg.vhd

-- Author

:

<Craig Slorach@HANDEL>

-- Created

: 1999/02/02

-- Last modified : 1999/02/02

-------------------------------------------------------------------------------- Description :

-- Implements a simple loadable register in VHDL

-------------------------------------------------------------------------------- Modification history :

-- 1999/02/02 : created

------------------------------------------------------------------------------library ieee;

use ieee.std_logic_1164.all;

entity SIMPREG is

port (DIN : in std_logic_vector(7 downto 0); -- system inputs

DOUT : out std_logic_vector(7 downto 0); -- system outputs

ENABLE : in std_logic;

-- enable

CLK,RESET : in std_logic);

-- clock and reset

end SIMPREG;

-- purpose: Main architecture details for SIMPREG

architecture SIMPLE of SIMPREG is

begin

-- SIMPLE

process(CLK,RESET)

begin -- process

-- activities triggered by asynchronous reset (active high)

if RESET = 1 then

DOUT <= "00000000";

-- activities triggered by rising edge of clock

elsif CLKevent and CLK = 1 then

if ENABLE=1 then

DOUT <= DIN;

else

null;

end if;

end if;

end process;

end SIMPLE;

par2ser.vhd

Feb 22 1999 09:53

Page 1

-------------------------------------------------------------------------------- Title

: Parallel to Serial Converter (PAR2SER)

-- Project

: Digital Design IV

-------------------------------------------------------------------------------- File

: par2ser.vhd

-- Author

:

<craigs@HANDEL>

-- Created

: 1999/02/19

-- Last modified : 1999/02/19

-------------------------------------------------------------------------------- Description :

-- Implements a simple 8-bit parallel to serial converter in VHDL.

-------------------------------------------------------------------------------- Modification history :

-- 1999/02/19 : created

------------------------------------------------------------------------------library ieee;

use ieee.std_logic_1164.all;

entity PAR2SER is

port (DIN : in std_logic_vector (7 downto 0);

MODE : in std_logic_vector (1 downto 0);

CLK, RESET : in std_logic;

SDOUT : out std_logic);

-----

input register

mode selection

clock and reset

output data

end PAR2SER;

-- purpose: Implement main architecture of PAR2SER

architecture BEHAVIOR of PAR2SER is

signal IDATA : std_logic_vector(7 downto 0);

begin

-- internal data

-- BEHAVIOR

-- purpose: Main process

process (CLK, RESET)

begin

-- process

-- activities triggered by asynchronous reset (active high)

if RESET = 1 then

SDOUT <= 0;

IDATA <= "00000000";

-- activities triggered by rising edge of clock

elsif CLKevent and CLK = 1 then

case MODE is

when "00" =>

null;

-- no operation

when "01" =>

IDATA <= DIN;

-- load operation

when "10" =>

SDOUT <= IDATA(7);

-- shift left

for mloop in 6 downto 0 loop

IDATA(mloop+1) <= IDATA(mloop);

end loop; -- mloop

when others =>

null;

-- no operation otherwise

end case;

end if;

end process;

end BEHAVIOR;

Plot of Parallel to Serial Example (PAR2SER.VHD)

Tickmarks @ 50n

Properties

Labels @ 100n 0.0m

100n

200n

300n

400n

500n

600n

700n

800n

900n

1u

1.1u

/CLK

/RESET

/DIN

/MODE

UUUUUUUU

00

01100101

01

11

10

/SDOUT

Page 1 of 1, Row 1, Column 1

1.2u

1.3u

1.4u

1.5u

Libraries Guide

IBUF, 4, 8, 16

Single- and Multiple-Input Buffers

Elemen

t

XC3000

XC4000

E

XC4000

X

XC5200

XC9000

IBUF

Primitive

Primitive

Primitive

Primitive

Primitive

IBUF4,

IBUF8,

IBUF16

Macro

Macro

Macro

Macro

Macro

IBUF, IBUF4, IBUF8, and IBUF16 are single and multiple input buffers. An IBUF isolates the internal circuit from the

signals coming into a chip. IBUFs are contained in input/output blocks (IOB). IBUF inputs (I) are connected to an IPAD

or an IOPAD. IBUF outputs (O) are connected to the internal circuit.

Figure 6-3IBUF8 Implementation XC3000, XC4000, XC5200, XC9000

1 - libguide

Libraries Guide

2 - libguide

Libraries Guide

BUF

General-Purpose Buffer

XC3000

XC4000E

XC4000X

XC5200

XC9000

Primitive

Primitive

Primitive

Primitive

Primitive

BUF is a general purpose, non-inverting buffer.

In FPGA architecture, BUF is usually not necessary and is removed by the partitioning software (MAP for XC3000 and

PAR for XC4000). The BUF element can be preserved for reducing the delay on a high fan-out net, for example, by

splitting the net and reducing capacitive loading. In this case, the buffer is preserved by attaching an X (explicit) attribute

to both the input and output nets of the BUF.

In CPLD architecture, BUF is usually removed, unless you inhibit optimization by applying the OPT=OFF attribute to the

BUF symbol or by using the LOGIC_OPT=OFF global attribute.

1 - libguide

Libraries Guide

OBUF, 4, 8, 16

Single- and Multiple-Output Buffers

Elemen

t

XC3000

XC4000

E

XC4000

X

XC5200

XC9000

OBUF

Primitive

Primitive

Primitive

Primitive

Primitive

OBUF4,

OBUF8,

OBUF16

Macro

Macro

Macro

Macro

Macro

OBUF, OBUF4, OBUF8, and OBUF16 are single and multiple output buffers. An OBUF isolates the internal circuit and

provides drive current for signals leaving a chip. OBUFs exist in input/output blocks (IOB). The output (O) of an OBUF

is connected to an OPAD or an IOPAD. For XC9000 CPLDs, if a high impedance (Z) signal from an on-chip 3-state

buffer (like BUFE) is applied to the input of an OBUF, it is propagated to the CPLD device output pin.

Figure 8-1OBUF8 Implementation XC3000, XC4000, XC5200, XC9000

1 - libguide

Libraries Guide

2 - libguide

Libraries Guide

OFDX, 4, 8, 16

Single- and Multiple-Output D Flip-Flops with Clock Enable

Elemen

t

XC3000

XC4000

E

XC4000

X

XC5200

XC9000

OFDX

N/A

Primitive

Primitive

N/A

N/A

OFDX4,

OFDX8,

OFDX1

6

N/A

Macro

Macro

N/A

N/A

1 - libguide

Libraries Guide

OFDX, OFDX4, OFDX8, and OFDX16 are single and multiple output D flip-flops. The flip-flops are located in an

input/output block (IOB) for XC4000E. The Q outputs are connected to OPADs or IOPADs. The data on the D inputs is

loaded into the flip-flops during the Low-to-High clock (C) transition and appears on the Q outputs. When CE is Low,

flip-flop outputs do not change.

The flip-flops are asynchronously cleared with Low outputs, when power is applied or when global set/reset (GSR) is

active. The GSR active level defaults to active-High but can be inverted by adding an inverter in front of the GSR input of

the STARTUP symbol.

Inputs

Outputs

CE

dn

No Chg

dn = state of referenced input one setup time prior to active clock transition

Figure 8-35OFDX8 Implementation XC4000

2 - libguide

Libraries Guide

STARTUP

User Interface to Global Clock, Reset, and 3-State Controls

XC3000

XC4000E

XC4000X

XC5200

XC9000

N/A

Primitive

Primitive

Primitive

N/A

The STARTUP primitive is used for Global Set/Reset, global 3-state control, and the user configuration clock. The

Global Set/Reset (GSR) input, when High, sets or resets every flip-flop in the device, depending on the initialization state

(S or R) of the flip-flop. Following configuration, the global 3-state control (GTS), when High, forces all the IOB outputs

into high impedance mode, which isolates the device outputs from the circuit but leaves the inputs active.

Including the STARTUP symbol in a design is optional. You must include the symbol under the following conditions.

If you intend to exert external control over global set/reset, you must connect the GSR pin to an IPAD and an IBUF,

as shown here.

1 - libguide

Libraries Guide

IFDX, 4, 8, 16

Single- and Multiple-Input D Flip-Flops with Clock Enable

Elemen

t

XC3000

XC4000

E

XC4000

X

XC5200

XC9000

IFDX

N/A

Primitive

Primitive

N/A

N/A

IFDX4,

IFDX8,

IFDX16

N/A

Macro

Macro

N/A

N/A

1 - libguide

Libraries Guide

The IFDX D-type flip-flop is contained in an input/output block (IOB). The input (D) of the flip-flop is connected to an

IPAD or an IOPAD (without using an IBUF). The D input provides data input for the flip-flop, which synchronizes data

entering the chip. The data on input D is loaded into the flip-flop during the Low-to-High clock (C) transition and appears

at the output (Q). The clock input can be driven by internal logic or through another external pin. When CE is Low,

flip-flop outputs do not change.

The flip-flops are asynchronously cleared with Low outputs when power is applied or when global set/reset (GSR) is

active. The GSR active level defaults to active-High but can be inverted by adding an inverter in front of the GSR input of

the STARTUP symbol.

For information on legal IFDX, IFDX_1, ILDX, and ILDX_1 combinations, refer to the "ILDX, 4, 8, 16" section.

Inputs

Outputs

CE

Dn

Qn

Dn

dn

No Chg

dn = state of referenced input (Dn) one setup time prior to active clock

transition

Figure 6-12IFDX8 Implementation XC4000

2 - libguide

Libraries Guide

FDCE

D Flip-Flop with Clock Enable and Asynchronous Clear

XC3000

XC4000E

XC4000X

XC5200

XC9000

Primitive

Primitive

Primitive

Primitive

Macro

FDCE is a single D-type flip-flop with clock enable and asynchronous clear. When clock enable (CE) is High and

asynchronous clear (CLR) is Low, the data on the data input (D) of FDCE is transferred to the corresponding data output

(Q) during the Low-to-High clock (C) transition. When CLR is High, it overrides all other inputs and resets the data

output (Q) Low. When CE is Low, clock transitions are ignored.

The flip-flop is asynchronously cleared, output Low, when power is applied or when global reset (GR for XC3000,

XC5200), global set/reset (GSR for XC4000), or global set/reset preload (PRLD for XC9000) is active. GR for XC3000

is active-Low. PRLD is active-High. The active level of the GSR and of the GR for XC5200 defaults to active-High but

can be inverted by adding an inverter in front of the GSR/GR input of the STARTUP symbol.

Inputs

Outputs

CLR

CE

No Chg

Figure 5-13FDCE Implementation XC9000

1 - libguide

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5811)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- 769D 771D 773D 775D PDFDocument116 pages769D 771D 773D 775D PDFDarmawan Putranto100% (2)

- Journal of Loss PreventionDocument17 pagesJournal of Loss Preventionlokeshkumar_m100% (1)

- Non Destructive Methods For Testing of ConcreteDocument21 pagesNon Destructive Methods For Testing of ConcreteDeepak SinghNo ratings yet

- User Manual: Downloaded From Manuals Search EngineDocument43 pagesUser Manual: Downloaded From Manuals Search EngineM RefaiNo ratings yet

- Chaptert 1 PPT KeznerDocument34 pagesChaptert 1 PPT KeznerLiggie FarmingNo ratings yet

- Din 912Document1 pageDin 912CottagePoolNo ratings yet

- Directivity in Loudspeaker SystemsDocument14 pagesDirectivity in Loudspeaker SystemsDan HauerNo ratings yet

- Google Neural Machine Translation SystemDocument23 pagesGoogle Neural Machine Translation SystemCarlangaslangasNo ratings yet

- Katalog PDFDocument64 pagesKatalog PDFAymeeenNo ratings yet

- As 4758.1-2008 Personal Flotation Devices General RequirementsDocument9 pagesAs 4758.1-2008 Personal Flotation Devices General RequirementsSAI Global - APAC100% (1)

- Zesco TSDocument58 pagesZesco TSSourav SatapathyNo ratings yet

- Norland Bottled Water Equipment Products BrochureDocument5 pagesNorland Bottled Water Equipment Products BrochureDilip Thakare100% (1)

- Philips 80 W Essential Smartbright Led Flood LightDocument8 pagesPhilips 80 W Essential Smartbright Led Flood Lightvasanth kumarNo ratings yet

- Debug 1214Document17 pagesDebug 1214Arief LuthfiyantoNo ratings yet

- Andrew® MultiBand - DGVV65A-FL-4XR, 790-862, 880-960 and 2 X 1710-2690 MHZ - 65° HBW - 1.4mDocument7 pagesAndrew® MultiBand - DGVV65A-FL-4XR, 790-862, 880-960 and 2 X 1710-2690 MHZ - 65° HBW - 1.4mborisNo ratings yet

- Acropolis Institute of Technology and Research, Indore Department of Computer Science and EngineeringDocument6 pagesAcropolis Institute of Technology and Research, Indore Department of Computer Science and EngineeringParv khatriNo ratings yet

- A1 - Parts of The Building Code - W23Document2 pagesA1 - Parts of The Building Code - W23Justin LeNo ratings yet

- Manufacturing Processes (Machining Processes & Machine Tools) (Beng) (Handout)Document82 pagesManufacturing Processes (Machining Processes & Machine Tools) (Beng) (Handout)bananaNo ratings yet

- Automated Irrigation System Using. X-Bee and LabviewDocument6 pagesAutomated Irrigation System Using. X-Bee and Labviewsuhaskakade0075745No ratings yet

- Earthquake and Tsunami PDFDocument12 pagesEarthquake and Tsunami PDFMayank Gautam100% (2)

- p180 Avanti I SopDocument92 pagesp180 Avanti I Sopcougarfly100% (1)

- 13491RDO101 Iligan CityDocument26 pages13491RDO101 Iligan CityAnonymous 8hx6hKN3No ratings yet

- Chapter 3: Factories and Machinery Act 1967Document10 pagesChapter 3: Factories and Machinery Act 1967Aldric Tinker Toyad100% (4)

- DIY IIT Dharwad Mid Eval ReportDocument4 pagesDIY IIT Dharwad Mid Eval ReportSonu SouravNo ratings yet

- Manual Tool Arm PDFDocument12 pagesManual Tool Arm PDFmolsonexportmanNo ratings yet

- Steganography: Khan, Mohammed MinhajuddinDocument13 pagesSteganography: Khan, Mohammed MinhajuddinShivaEshwariNo ratings yet

- RLM Full CatalogDocument47 pagesRLM Full CatalogJoe JoeNo ratings yet

- Smart Warehouse Brochure Digital Version PDFDocument4 pagesSmart Warehouse Brochure Digital Version PDFartomaniacNo ratings yet

- MV Blue Star Final Stowage PlanDocument1 pageMV Blue Star Final Stowage PlanDaniel SilitongaNo ratings yet

- Lexus Body Electrical Diagnosis - Post TestDocument9 pagesLexus Body Electrical Diagnosis - Post TestLong HàNo ratings yet