Professional Documents

Culture Documents

DS PDF

DS PDF

Uploaded by

Andrew HekinnenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DS PDF

DS PDF

Uploaded by

Andrew HekinnenCopyright:

Available Formats

Revised April 2000

DM74LS181

4-Bit Arithmetic Logic Unit

General Description

Features

The DM74LS181 is a 4-bit Arithmetic Logic Unit (ALU)

which can perform all the possible 16 logic operations on

two variables and a variety of arithmetic operations.

Provides 16 arithmetic operations: add, subtract, compare, double, plus twelve other arithmetic operations

Provides all 16 logic operations of two variables:

exclusive-OR, compare, AND, NAND, OR, NOR, plus

ten other logic operations

Full lookahead for high speed arithmetic operation on

long words

Ordering Code:

Order Number

Package Number

DM74LS181N

N24A

Package Description

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600 Wide

Connection Diagram

Logic Symbols

Active High Operands

Active Low Operands

Pin Descriptions

Pin Names

A0A3

VCC = Pin 24

GND = Pin 12

2000 Fairchild Semiconductor Corporation

DS009821

Description

Operand Inputs (Active LOW)

B0B3

Operand Inputs (Active LOW)

S0S3

Function Select Inputs

Mode Control Input

Cn

Carry Input

F0F3

Function Outputs (Active LOW)

A=B

Comparator Output

Carry Generate Output (Active LOW)

Carry Propagate Output (Active LOW)

Cn+4

Carry Output

www.fairchildsemi.com

DM74LS181 4-Bit Arithmetic Logic Unit

October 1988

DM74LS181

Functional Description

DM74LS181 devices. Carry lookahead can be provided at

various levels and offers high speed capability over

extremely long word lengths.

The DM74LS181 is a 4-bit high speed parallel Arithmetic

Logic Unit (ALU). Controlled by the four Function Select

inputs (S0S3) and the Mode Control input (M), it can perform all the 16 possible logic operations or 16 different

arithmetic operations on active HIGH or active LOW operands. The Function Table lists these operations

The A = B output from the device goes HIGH when all four

F outputs are HIGH and can be used to indicate logic

equivalence over four bits when the unit is in the subtract

mode. The A = B output is open-collector and can be wiredAND with other A = B outputs to give a comparison for

more than four bits. The A = B signal can also be used with

the Cn+4 signal to indicate A > B and A < B.

When the Mode Control input (M) is HIGH, all internal carries are inhibited and the device performs logic operations

on the individual bits as listed. When the Mode Control

input is LOW, the carries are enabled and the device performs arithmetic operations on the two 4-bit words. The

device incorporates full internal carry lookahead and provides for either ripple carry between devices using the Cn+4

output, or for carry lookahead between packages using the

signals P (Carry Propagate) and G (Carry Generate). In the

ADD mode, P indicates that F is 15 or more, while G indicates that F is 16 or more. In the SUBTRACT mode, P indicates that F is zero or less, while G indicates that F is less

than zero. P and G are not affected by carry in. When

speed requirements are not stringent, it can be used in a

simple ripple carry mode by connecting the Carry output

(Cn+4) signal to the Carry input (Cn) of the next unit. For

high speed operation the device is used in conjunction with

the 9342 or 93S42 carry lookahead circuit. One carry lookahead package is required for each group of four

The Function Table lists the arithmetic operations that are

performed without a carry in. An incoming carry adds a one

to each operation. Thus, select code LHHL generates A

minus B minus 1 (2s complement notation) without a carry

in and generates A minus B when a carry is applied.

Because subtraction is actually performed by complementary addition (1s complement), a carry out means borrow;

thus a carry is generated when there is no underflow and

no carry is generated when there is underflow. As indicated, this device can be used with either active LOW

inputs producing active LOW outputs or with active HIGH

inputs producing active HIGH outputs. For either case the

table lists the operations that are performed to the operands labeled inside the logic symbol.

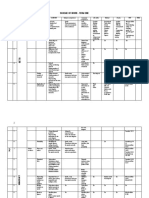

Function Table

Mode Select

Active LOW Operands

Inputs

& Fn Outputs

Logic

Active HIGH Operands

& Fn Outputs

Arithmetic

(Note 2)

Logic

(M = L) (Cn = L)

(M = H)

Arithmetic

(Note 2)

(M = H)

(M = L) (Cn = H)

S3

S2

S1

S0

A minus 1

AB

AB minus 1

A+B

A+B

A+B

AB minus 1

AB

A+B

Logic 1

minus 1

Logic 0

minus 1

A+B

A plus (A + B)

AB

A plus AB

AB plus (A + B)

(A + B) plus AB

AB

A minus B minus 1

AB

A minus B minus 1

A+B

A+B

AB

AB minus 1

AB

A plus (A + B)

A+B

A plus AB

AB

A plus B

AB

A plus B

AB plus (A + B)

(A + B) plus AB

A+B

A+B

AB

AB minus 1

Logic 0

A plus A (Note 1)

Logic 1

A plus A (Note 1)

AB

AB plus A

A+B

(A + B) plus A

AB

AB minus A

A+B

(A + B) plus A

A minus 1

Note 1: Each bit is shifted to the next most significant position.

Note 2: Arithmetic operations expressed in 2s complement notation.

www.fairchildsemi.com

DM74LS181

Logic Diagram

www.fairchildsemi.com

DM74LS181

Absolute Maximum Ratings(Note 3)

Supply Voltage

Note 3: The Absolute Maximum Ratings are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The Recommended Operating Conditions table will define the conditions

for actual device operation.

7V

Input Voltage

7V

0C to +70C

Operating Free Air Temperature Range

65C to +150C

Storage Temperature Range

Recommended Operating Conditions

Symbol

Parameter

Min

Nom

Max

4.75

5.25

Units

VCC

Supply Voltage

VIH

HIGH Level Input Voltage

VIL

LOW Level Input Voltage

0.8

IOH

HIGH Level Output Current

0.4

mA

IOL

LOW Level Output Current

mA

TA

Free Air Operating Temperature

70

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Symbol

Parameter

Conditions

VI

Input Clamp Voltage

VCC = Min, II = 18 mA

VOH

HIGH Level

VCC = Min, IOH = Max,

Output Voltage

VIL = Max

VOL

LOW Level

VCC = Min, IOL = Max,

Output Voltage

VIH = Min

Min

Input Current @ Max

VCC = Max, VI = 7V

Input Voltage

IIH

HIGH Level

VCC = Max, VI = 2.7V

Input Current

IIL

LOW Level

VCC = Max, VI = 0.4V

Input Current

IOS

ICC

Short Circuit

VCC = Max

Output Current

(Note 5)

Supply Current

VCC = Max, Bn, Cn = GND

1.5

0.5

0.25

0.4

0.1

0.3

Sn

0.4

Cn

0.5

M input

20

An, Bn

60

Sn

80

Cn

100

M input

0.4

An, Bn

1.2

Sn

1.6

Cn

2.0

Note 4: All typicals are at VCC = 5V, TA = 25C.

Note 5: Not more than one output should be shorted at a time, and the duration should not exceed one second.

0.35

M input

20

Units

V

V

An, Bn

Sn, M, An = 4.5V

www.fairchildsemi.com

Max

2.7

IOL = 4 mA, VCC = Min

II

Typ

(Note 4)

mA

mA

100

mA

37

mA

VCC = 5V, TA = 25C

Symbol

Parameter

tPLH

Propagation Delay

tPHL

Cn to Cn+4

CL = 15 pF

Conditions

Min

Max

M = GND

Units

27

ns

20

M = GND

tPLH

Propagation Delay

tPHL

Cn to F

26

tPLH

Propagation Delay

M, S1, S2 = GND;

29

tPHL

A or B to G (Sum)

S1, S3 = 4.5V

23

tPLH

Propagation Delay

M, S0, S3 = GND;

32

tPHL

A or B to G (Diff)

S1, S2 = 4.5V

26

tPLH

Propagation Delay

M, S1, S2 = GND;

30

tPHL

A or B to P (Sum)

S0, S3 = 4.5V

30

tPLH

Propagation Delay

M, S0, S3 = GND;

30

tPHL

A or B to P (Diff)

S1, S2 = 4.5V

33

tPLH

Propagation Delay

M, S1, S2 = GND;

32

tPHL

Ai or Bi to Fi(Sum)

S0, S3 = 4.5V

25

tPLH

Propagation Delay

M, S0, S3 = GND;

32

tPHL

Ai or Bi to Fi(Diff)

S1, S2 = 4.5V

33

M = 4.5V

ns

20

tPLH

Propagation Delay

tPHL

A or B to F (Logic)

ns

ns

ns

ns

ns

ns

33

ns

29

tPLH

Propagation Delay

M, S1, S2 = GND;

38

tPHL

A or B to Cn+4 (Sum)

S0, S3 = 4.5V

38

tPLH

Propagation Delay

M, S0, S3 = GND;

41

tPHL

A or B to Cn+4 (Diff)

S1, S2 = 4.5V

41

tPLH

Propagation Delay

M, S0, S3 = GND;

50

tPHL

A or B to A = B

S1, S2 = 4.5V;

62

ns

ns

ns

RL = 2 k to 5.0V

Sum Mode Test Table 1

Function Inputs

S0 = S3 = 4.5V, S1 = S2 = M = 0V

Input

Symbol

Test

tPLH

Other Input

Under

Ai

Other Data Inputs

Under

Apply

Apply

Apply

Apply

4.5V

GND

4.5V

GND

Bi

None

Remaining

Cn

Fi

Cn

Fi

Remaining

tPHL

tPLH

Bi

Ai

None

Remaining

A and B

None

None

tPHL

tPLH

A and B, Cn

B

None

None

tPHL

tPLH

None

None

tPHL

tPLH

None

tPHL

tPLH

None

tPHL

tPLH

Remaining

A and B, Cn

tPHL

tPLH

Test

A and B

tPHL

tPLH

Output

Same Bit

Cn

None

None

tPHL

Remaining

Remaining

A, Cn

Remaining

Remaining

A, Cn

Remaining

Remaining

A, Cn

Remaining

Remaining

A, Cn

All

All

Any F

or Cn+4

Cn+4

Cn+4

www.fairchildsemi.com

DM74LS181

Switching Characteristics

DM74LS181

Diff Mode Test Table 2

Function Inputs

S1 = S2 = 4.5V, S0 = S3 = M = 0V

Input

Symbol

Test

tPLH

Other Input

Under

Other Data Inputs

Same Bit

Under

Apply

Apply

Apply

Apply

4.5V

GND

4.5V

GND

None

Remaining

Remaining

B, Cn

Remaining

Remaining

B, Cn

tPHL

tPLH

None

tPHL

tPLH

None

Output

None

tPHL

Remaining

Test

Fi

Fi

P

A and B, Cn

tPLH

None

None

tPHL

Remaining

A and B, Cn

tPLH

None

None

tPHL

Remaining

A and B, Cn

tPLH

None

None

tPHL

Remaining

A and B, Cn

tPLH

None

tPHL

tPLH

None

tPHL

tPLH

None

Remaining

Remaining

B, Cn

Remaining

Remaining

B, Cn

None

tPHL

Remaining

A=B

A=B

Cn+4

A and B, Cn

tPLH

None

None

tPHL

Remaining

Cn+4

A and B, Cn

tPLH

Cn

None

None

tPHL

All

None

Cn+4

A and B

Logic Mode Test Table 3

Function Inputs

S1 = S2 = M = 4.5V, S0 = S3 = 0V

Input

Other Input

Symbol

Under

Test

tPLH

Other Data Inputs

Same Bit

Under

Apply

Apply

Apply

Apply

4.5V

GND

4.5V

GND

None

None

tPHL

tPLH

Remaining

Test

Any F

A and B, Cn

B

None

tPHL

www.fairchildsemi.com

Output

None

Remaining

A and B, Cn

Any F

DM74LS181 4-Bit Arithmetic Logic Unit

Physical Dimensions inches (millimeters) unless otherwise noted

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600 Wide

Package Number N24A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

2. A critical component in any component of a life support

device or system whose failure to perform can be reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the

user.

www.fairchildsemi.com

www.fairchildsemi.com

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Envision Math Common Core WorkbookDocument270 pagesEnvision Math Common Core WorkbookJenny67% (3)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Lufthansa EASA - Module-01Document73 pagesLufthansa EASA - Module-01Senthil FlyhighNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 16 Bit AdderDocument4 pages16 Bit AdderNilesh Maurya100% (1)

- 1.0 Computer System 2021 - 2022 StudentsDocument145 pages1.0 Computer System 2021 - 2022 Studentsnurain syuhadaNo ratings yet

- FractionsDocument56 pagesFractionsSarose ThapaNo ratings yet

- Chapter 4 Combinational LogicDocument67 pagesChapter 4 Combinational LogicAbaid UllahNo ratings yet

- PolynomialsDocument53 pagesPolynomialsmerezemenike272No ratings yet

- Chapter 1 Real Numbers (JNV)Document18 pagesChapter 1 Real Numbers (JNV)swatiNo ratings yet

- Worksheet # 1.3-ADocument2 pagesWorksheet # 1.3-ASadia SherazNo ratings yet

- TernaryDocument2 pagesTernarypshtarkov8503No ratings yet

- p.6 Primary Six MTC Scheme of Work Teacher - AcDocument18 pagesp.6 Primary Six MTC Scheme of Work Teacher - Acokwir daniel chrispusNo ratings yet

- Daily Lesson Log Business MathDocument99 pagesDaily Lesson Log Business MathbelleNo ratings yet

- 2Q-Budget of Work-Math IVDocument2 pages2Q-Budget of Work-Math IVmaylinda l. bacoyNo ratings yet

- Lecturer 01 - Number SystemDocument51 pagesLecturer 01 - Number Systemshihab285No ratings yet

- Binary Arithmetic Binary Addition: MODULE 3 - Number System ArithmeticDocument5 pagesBinary Arithmetic Binary Addition: MODULE 3 - Number System ArithmeticJim SumayaNo ratings yet

- CGS 3269 Computer Architecture Concepts: Positional Number SystemsDocument12 pagesCGS 3269 Computer Architecture Concepts: Positional Number SystemssharikNo ratings yet

- Binomial Theorem - Assignment For JEEDocument39 pagesBinomial Theorem - Assignment For JEEPankaj MeenNo ratings yet

- Mathematics Analysis and Approaches Paper 3 TZ2 HL MarkschemeDocument32 pagesMathematics Analysis and Approaches Paper 3 TZ2 HL Markschemegreensyrup123No ratings yet

- Rational ExpressionsDocument2 pagesRational ExpressionsRazzler DazzlerNo ratings yet

- Perhitungan Asidi AlkalimetriDocument4 pagesPerhitungan Asidi AlkalimetriChristoperQ HutaurukNo ratings yet

- Lab Session 4: ObjectiveDocument10 pagesLab Session 4: ObjectiveDarwin VargasNo ratings yet

- The g9 Joint Examination Pp1 MsDocument12 pagesThe g9 Joint Examination Pp1 Mswinrosenyaboke56No ratings yet

- Percentages AnswersDocument1 pagePercentages AnswersWho YouNo ratings yet

- Square Till 125Document2 pagesSquare Till 125Mayur SomvanshiNo ratings yet

- Center Activity Answer KeyDocument4 pagesCenter Activity Answer KeyAnna K. RiveraNo ratings yet

- Self Exercises 2Document27 pagesSelf Exercises 2budi_putraNo ratings yet

- Operations in FractionsDocument5 pagesOperations in FractionsJennifer LegaspiNo ratings yet

- RS Aggarwal Solutions Class 10 Chapter 2 - Exercise 2.1Document44 pagesRS Aggarwal Solutions Class 10 Chapter 2 - Exercise 2.1tarun rockyNo ratings yet

- 1.5 Arithmetic Means Students WK 2Document2 pages1.5 Arithmetic Means Students WK 2Goerge Sapnap DreamNo ratings yet

- Activity 3 - Patterns, Mathe Translations - Answer KeyDocument2 pagesActivity 3 - Patterns, Mathe Translations - Answer KeyJustin Paul HibionadaNo ratings yet