Professional Documents

Culture Documents

Slowclock

Uploaded by

Chaitanya Bharath0 ratings0% found this document useful (0 votes)

5 views1 pageOriginal Title

slowclock.txt

Copyright

© © All Rights Reserved

Available Formats

TXT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

5 views1 pageSlowclock

Uploaded by

Chaitanya BharathCopyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

You are on page 1of 1

module slowclock(clk, reset, clk_1Hz);

input clk, reset;

output clk_1Hz;

reg clk_1Hz = 1'b0;

reg [27:0] counter;

always@(posedge reset or posedge clk)

begin

if (reset == 1'b1)

begin

clk_1Hz <= 0;

counter <= 0;

end

else

begin

counter <= counter + 1;

if ( counter == 25000000)

begin

counter <= 0;

clk_1Hz <= ~clk_1Hz;

end

end

end

endmodule

You might also like

- BSC Magazine October 2019 PDFDocument50 pagesBSC Magazine October 2019 PDFChaitanya BharathNo ratings yet

- Test For Official Language of State PDFDocument1 pageTest For Official Language of State PDFChaitanya BharathNo ratings yet

- Procedure For Doing Project Work in IIT BombayDocument1 pageProcedure For Doing Project Work in IIT BombayChaitanya BharathNo ratings yet

- Crack High Level - Puzzle Question 2019 - Edition 3 PDFDocument179 pagesCrack High Level - Puzzle Question 2019 - Edition 3 PDFHemant Sarva80% (5)

- ECE Course Corrected 14 Nov. 2016Document12 pagesECE Course Corrected 14 Nov. 2016Chaitanya BharathNo ratings yet

- CGPA To Percentage ConversionDocument1 pageCGPA To Percentage ConversionChaitanya BharathNo ratings yet

- IAS Recommendation Letter FormatDocument2 pagesIAS Recommendation Letter FormatAshwin RamanujamNo ratings yet

- IAS Recommendation Letter FormatDocument2 pagesIAS Recommendation Letter FormatAshwin RamanujamNo ratings yet

- Copy A String To A StringDocument32 pagesCopy A String To A StringChaitanya BharathNo ratings yet

- Cmos 180nm Bulk FileDocument2 pagesCmos 180nm Bulk FileChaitanya Bharath0% (1)

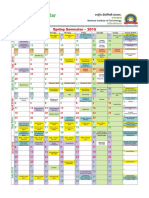

- Academics Calendar 2016Document2 pagesAcademics Calendar 2016Chaitanya BharathNo ratings yet

- SlowclockDocument1 pageSlowclockChaitanya BharathNo ratings yet

- Name: K Chaitanya Bharath ROLL: BT14ECE056 Exp - 3: AIM: Find The Delays in CMOS Inverter CircuitDocument3 pagesName: K Chaitanya Bharath ROLL: BT14ECE056 Exp - 3: AIM: Find The Delays in CMOS Inverter CircuitChaitanya BharathNo ratings yet

- SubjectsDocument1 pageSubjectsChaitanya BharathNo ratings yet

- KabaddiDocument8 pagesKabaddiChaitanya BharathNo ratings yet

- ReadmeDocument1 pageReadmeChaitanya BharathNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- 40002148B Pic18f27q84Document20 pages40002148B Pic18f27q84Au GroupsNo ratings yet

- Mod. AAC-1/EV: Modular Educational Systems For Drives of Ac MotorsDocument2 pagesMod. AAC-1/EV: Modular Educational Systems For Drives of Ac Motorslusoegyi 1919No ratings yet

- ManualDocument82 pagesManualRicardo RojasNo ratings yet

- A10 EVB ManualDocument52 pagesA10 EVB ManualAnime TubeNo ratings yet

- Experiment 2 - Measurements On Coaxial Lines: Z C Z R Z R U Z C CDocument5 pagesExperiment 2 - Measurements On Coaxial Lines: Z C Z R Z R U Z C Csadke213No ratings yet

- SAED Digital Standard Cell Library - Rev1!4!20Document100 pagesSAED Digital Standard Cell Library - Rev1!4!20Jordan JohnsonNo ratings yet

- Micro Controller Based Code LookDocument9 pagesMicro Controller Based Code LookHimanshu MehtaNo ratings yet

- Physics Exp 8 GRP 10Document6 pagesPhysics Exp 8 GRP 10Elizabeth Jade ViceraNo ratings yet

- CCN Lab 2.Document3 pagesCCN Lab 2.buntuNo ratings yet

- Huawei GprsDocument30 pagesHuawei GprsMoses Gitonga KathuriNo ratings yet

- Kenwood TS-830: Survival GuideDocument37 pagesKenwood TS-830: Survival GuideSanyel SaitoNo ratings yet

- Electricity Worksheet Physics GcseDocument5 pagesElectricity Worksheet Physics Gcsetun1123tNo ratings yet

- PROFIBUS-FMS Communications Processor (505-CP5434-FMS) ManualDocument187 pagesPROFIBUS-FMS Communications Processor (505-CP5434-FMS) ManualĐỗ Thiện Phúc VinhNo ratings yet

- Data0305 MX485netDocument3 pagesData0305 MX485netAbdelhamid SammoudiNo ratings yet

- Rabiner & Juang - Fundamentals of Speech RecognitionDocument277 pagesRabiner & Juang - Fundamentals of Speech RecognitionHarish Padaki100% (2)

- LB 1923Document17 pagesLB 1923Phạm Tuấn AnhNo ratings yet

- 3.3G Cellular, WMAN (WIMAX), WLAN (WIFI), WPAN (Bluetooth and UWB), Mobile Ad Hoc Networks (MANET), and Wireless Sensor NetworksDocument36 pages3.3G Cellular, WMAN (WIMAX), WLAN (WIFI), WPAN (Bluetooth and UWB), Mobile Ad Hoc Networks (MANET), and Wireless Sensor Networksekhy29No ratings yet

- Max77960 Max77961Document83 pagesMax77960 Max77961bubai karNo ratings yet

- Classified ICTDocument117 pagesClassified ICTAnshu Netani87% (15)

- Design and Construction of The CircuitsDocument10 pagesDesign and Construction of The Circuitsepi guzmanNo ratings yet

- Dell OptiPlex 7020 Technical Spec Sheet FINALDocument2 pagesDell OptiPlex 7020 Technical Spec Sheet FINALnothing2lose219No ratings yet

- Engine Knock Sensors - Part TwoDocument4 pagesEngine Knock Sensors - Part TwoFabricio LimaNo ratings yet

- Moving Coil Instruments: L I B N FDocument31 pagesMoving Coil Instruments: L I B N Faurellia moNo ratings yet

- HI-300 Thru HI-307: Datasheet - LiveDocument10 pagesHI-300 Thru HI-307: Datasheet - LiveDeybbiNo ratings yet

- Polk - Command Bar - Quick - Start - GuideDocument86 pagesPolk - Command Bar - Quick - Start - GuideVictor AguilarNo ratings yet

- Computer Networks HandbookDocument189 pagesComputer Networks HandbookDhirenkumar RathodNo ratings yet

- Unit 1 - ARM7Document67 pagesUnit 1 - ARM7Makrand KakatkarNo ratings yet

- Philips 27pt81s Pss AenDocument2 pagesPhilips 27pt81s Pss Aenpollito2doNo ratings yet

- LBC2403-1206 Series Battery Charger InstructionsDocument6 pagesLBC2403-1206 Series Battery Charger InstructionsLuis GonzalezNo ratings yet

- Catalog MATIX - BticinoDocument72 pagesCatalog MATIX - BticinoAna RuxandraNo ratings yet