Professional Documents

Culture Documents

Study and Analysis of Low Voltage Differential Voltage Current Conveyor: A Novel Design

Uploaded by

Technos_IncOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Study and Analysis of Low Voltage Differential Voltage Current Conveyor: A Novel Design

Uploaded by

Technos_IncCopyright:

Available Formats

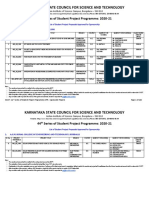

International Journal of Advances in Engineering Sciences Vol.

1, Issue 2, April, 2011

STUDY AND ANALYSIS OF LOW VOLTAGE

DIFFERENTIAL VOLTAGE CURRENT

CONVEYOR: A NOVEL DESIGN

Kamlesh Kumar Singh1

Ph.D.(Pursuing), Dept. of Electronics,

Dr. R. M. L. Avadh University, Faizabad

Email: kam2k_singh@yahoo.com

Prof.(Dr.) Kalyan. Singh2

HOD, Dept. of Electronics,

Dr. R. M. L. Avadh University, Faizabad

ABSTRACT- This paper presents a novel CMOS

differential voltage current conveyor. The differential

voltage current conveyor exhibits low voltage and a wide

dynamic input range. It is very suitable to use in a voltagemode signal processing, which is continually more popular

than any other technique. The proposed element is realized

in a CMos technology and is examined the performances

through PSPICE simulations. Experimental results show

good agreement with the simulation results and prove the

feasibility of the novel design.

of the output current follows the input current direction with

both currents flowing either into or out of the device. Since the

DVCC exhibits two high input impedance terminals, it shows

itself suitable for handling differential input signals. In

addition, it has the advantage of minimizing the number of

floating elements inherent in many CCII applications.

Keywords: Current-conveyor, differential voltage, current

conveyor, PSPICE.

1. INTRODUCTION

Since its first introduction, by A. Sedra and K. Smith in 1970 ,

the second-generation current conveyor (CCII) has proved to

be a versatile analog building block that can be used to

implement numerous high frequency analog signal

applications. However, when it comes to applications

demanding differential or floating inputs like impedance

converters and current mode instrumentation amplifiers, which

also require two high input impedance terminals, a single CCII

block is no more sufficient. In addition, most of these

applications employ floating elements in order to minimize the

number of used CCII blocks. For this reason and in order to

provide two high input impedance terminals, the differential

voltage current conveyor (DVCC) was proposed in 1997 as a

four terminal device with the following properties [Fig.1]:

0

IY1

I 0

Y 2 1

V X

0

I Z

0

1

0

0

Figure 1: Block representation of the DVCC

In this paper a new CMOS DVCC is proposed. This paper is

organized as follows: In section 2 the proposed Novel low

voltage DVCC circuit is presented. Thereafter, DVCC study

and analysis are discussed in section 3. PSPICE simulations

for proposed circuits are provided.

2. NOVEL DESIGN OF LOW VOLTAGE DVCC

Proposed DVCC is similar as DVCC. But it has multiple

outputs (two Z+ stages and one Z- stage) as shown in Fig.

2.1.The gain of second Z+ stage and Z- stage is three times of

first Z+ stage as defined in equations (2.1, and 2.2).

0

VY 1

0

VY 2

0

I X

0

VZ

While the X terminal voltage follows the voltage difference of

terminals Y1 and Y2, a current injected at the X terminal is

being replicated to the Z terminal. An ideal DVCC exhibits

zero input resistance at terminal X, and infinite resistance at

both Y terminals as well as the Z terminal. The flow direction

Figure 2.1 Schematic Diagram of Modified DVCC

12

International Journal of Advances in Engineering Sciences Vol.1, Issue 2, April, 2011

Current and voltage relation for Modified DVCC are as

follows

VX=VY1-VY2

(2.1)

IY1=IY2=0

IZi+=k1IX

IZj-=k2IX

Where: i=1, 2 and j=1

VY1= voltage at node Y1

VY2= voltage at node Y2

VX= voltage at node X

(2.2)

(2.3)

(2.4)

IX = current at node X

IZi+=currents at output node Z+

IZj-= current at output node ZA proposed DVCC incorporates two Z+ stages, one with k1=1

and the other with k1=3. Moreover, it also has a Z- stage with

k2=3 (equation 2.4). As far as modified DVCC

implementation is concerned the required gain (as given in

equation (2.3, 2.4) from X to Z terminal is realized by

maintaining the aspect ratios of different transistors as defined

in equation (2.5 2.6).

(W/L)7, 8 = a;

(W/L)12, 13 = b

(2.5)

(W/L) 9, 15, 16, 17 = 3a;

(W/L)14, 18, 19, 20 = 3b

Figure 2.2 CMOS Realization of Novel DVCC

Figure 3.1 and 3.2 shows the DC characteristic obtained by

simulation. Figure 3.1 proves that equation (2.1) is correct. It

is obtained by fixed VY1 and varies VY2. By making Vin1 fixed

at 0 mV and vary the Vin2, the variation in Vx is obtained

which is shown in figure 3.1. This figure also verifies equation

2.1.

(2.6)

Figure (3.3) shows the current relationship of DVCC. It can be

obtained just putting VY1 as constant and varying VY2. It shows

that device get saturated when -1V > VY2 > +1V

The proposed DVCC uses only 20 transistors as shown in Fig.

2.2.The proposed DVCC is also a versatile building block for

application demanding floating inputs. CMOS realization of

this block is given in figure 2.2.

Figure 3.3 shows output Current relation at terminal Z1+, Z2+

and Z1-. In this case making Vin1 constant and varying Vin2

the current responses can be observed. This clearly shows that

currents variations are linear between -1V to +1V. The gain

of output current at terminal Z2+ and Z1- is three times of

current at X terminal, and the gain of output current at Z1+

terminal is same as the gain of current at X terminal.

All transistors operate in saturation region and the sources are

connected to bulk/substrate. Transistor M5 and M6, work as a

current mirror which are set to drive two differential amplifier

consist of transistors M1, M2, M3 and M4. This forces to give

relation in equation (2.1). Transistor M7 and M12 provide the

necessary feedback action to make the voltage Vx independent

of current drawn from the terminal X. The current through

terminal X is conveyed to the Z1+ terminal with the help of

transistor M7, M8, M12 and M13. And the current through

terminal X is conveyed to the Z2+ terminal with the help of

transistor M7, M8, M9, M12, M13 and M14. By using extra

current mirror the current is conveyed in an inverted manner

to the Z1- terminal.

AC Analysis of Novel DVCC

AC analysis of proposed DVCC has also been done and

simulation result is given in figure 3.4 and 3.5. Figure 3.4

verifies the voltage relation between input nodes. It also shows

the range of frequency suitable for operation, it shows that

frequency up to 200MHz the voltage relationship is fine.

3. Simulation Results of NOVEL DVCC

Figure 3.5 shows that current relationship is also satisfied up

to the frequency of 200 MHz. The gain of output current at

terminal Z2+ and Z1- is three times of current at X terminal, and

the gain of output current at Z1+ terminal is same as the gain of

current at X terminal as given in equations (2.3, 2.4).

DC Analysis of Novel DVCC

PSPICE simulation on the CMOS implemented circuit of

modified DVCC, using level 3 model parameter give the good

agreement with the theoretical results. Figure 3 .1 shows the

DC characteristic of proposed DVCC; it shows that when DC

voltage of 100mV applies at input node Y1 (V1) and 60mV at

node Y2 (V2), it gives the 40mV at node X (V3). In this way it

verifies the voltage relationship of equation (2.1).

Transient Analysis of Novel DVCC

PSPICE simulation is also carried out for sinusoidal inputs.

These results also give a good agreement between theoretical

and experimental results. These results also verify the basic

13

International Journal of Advances in Engineering Sciences Vol.1, Issue 2, April, 2011

equation (2.1, 2.3 and 2.4) for DVCC in time domain in Figure

3.6 and 3.7

Author:

Kamlesh Kumar Singh is presently Asstt.Prof. in the

department of Electronics and Communication Engg., Amity

University Uttar Pradesh, Lucknow,India, He is also a

research scholar in Dept. of Electronics, Dr. R. M. L. Avadh

University, Faizabad . He received his M.Tech. Degree in

Electronic Design and Technology from U.P. Technical

University, Lucknow, India, in 2003.Before joining Amity

University, he also worked in Integral University as an Asstt.

Prof.in department of Electronics Engg. In 2000, he also

worked at Central Scientific Instruments Organization (CSIO),

Chandigarh, as an project scholar. He has been actively

involved in the field of Technical Education as Academician,

Researcher, Teacher, Planner and Administrator. He has

guided several M.Tech. and B.Tech. students in Electronics

Engg. discipline. He has also co-ordinated Front End VLSI

design Program

4. CONCLUSION

A new technique is proposed in this paper. A new low voltage

CMOS realization of proposed DVCC has been described. The

circuit is based on voltage and current mirror circuits.

Simulation results using PSPICE program exhibit that the

presented circuit design offers practical alternative solution to

use the CMOS DVCC in application circuits instead of the

DVCC elements. where experimental results show improved

performance in terms of dynamic range and power

consumptions compared with previous solutions .The circuit

provides high performance in terms of Low voltage and

current transferring, frequency response and linearity.

5.FIGURES

100mV

Vy2

Vy1

V

O

L

T

A

G

E

50mV

Vx

0V

0s

V(1)

V(2)

5us

V(3)

10us

15us

20us

Time

Figure 3.1 Various Voltages Responses

1.0V

V

x

0V

-1.0V

-1.0V

V(3)

-0.5V

0V

VIN2

Figure 3.2 Input Voltage Relations with Vx

14

0.5V

1.0V

International Journal of Advances in Engineering Sciences Vol.1, Issue 2, April, 2011

400uA

Iz2+

C

U

R

R

E

N

T

Iz1+

0A

Ix

Iz1-400uA

-1.0V

I(R1)

-0.5V

I(R2)

I(R3)

0V

0.5V

1.0V

I(R4)

VIN2

Figure 3.3 Output Current Responses

3.0V

Vy2

Vy1

V 2.0V

O

L

T

A

G

1.0V

E

Vx

0V

1.0Hz

V(1)

V(2)

1.0KHz

V(3)

1.0MHz

500MHz

Frequency

Figure 3.4 Frequency Responses of Voltages

300uA

Iz1-

C 200uA

U

R

R

E

N

T 100uA

Iz2+

Iz1+

Ix

0A

1.0Hz

I(R1)

I(R2)

1.0KHz

I(R3)

I(R4)

Frequency

1.0MHz

Figure 3.5 Frequency Responses of Various Currents

15

500MHz

International Journal of Advances in Engineering Sciences Vol.1, Issue 2, April, 2011

100mV

V

O

L

T

A

G

E

Vy1

Vy2

Vx

0V

-100mV

0s

V(1)

5us

V(3)

V(2)

10us

15us

20us

Time

Figure 3.6 Various Voltages Responses

20uA

C

U

R

R

E

N

T

Iz2+

Iz1-

Ix

Iz1+

0A

-20uA

0s

I(R1)

5us

I(R2)

I(R3)

10us

I(R4)

Time

15us

20us

Figure 3.7 Input/Output Current Responses

[6] S. A. Mahmoud, M. A. Hashiesh, A. M. Soliman, Lowvoltage digitally

controlled fully differential current conveyor, IEEE Trans. on Circuits and

Syst.-I, vol. 52, No. 10, pp. 2055-64, Oct. 2005.

[7] R. Senani, Novel circuit implementation of Current Conveyor using

operational amplifier and OTA, Electronics Letters, vol. 16(1), pp. 2-3,

1980.

[8] . Sedra, and K. C. Smith, A second generation current conveyor and its

applications, IEEE Trans., vol. CT-17, pp. 132-134, 1970.

[9] S. Maheshwari., High CMRR wide bandwidth instrumentation

amplifier using current controlled conveyors, International Journal of

Electronics, vol. 89 (12), pp. 889-896, 2002.

[10] S. S. Gupta and R. Senani, CMOS Differential Difference Current

Conveyors and Their Applications, IEE Proc Circuits Devices Systems,

vol. 148, pp. 335-336, 2001.

6. REFERNCES

[1] K. Smith and A. Sedra, The Current Conveyor-a new circuit building

block, IEEE Proc., vol. 56, pp. 1368-1369, 1968.

[2] S. S. Rajput and S. S. Jamuar. "Low voltage. Low power high

performance current mirror for portable analogue and mixed mode

applications". accepted in IEE Proceedings. Circuits. Devices and Systems.

[3] B. Wilson, Trend in current conveyor and current-mode amplifier

design, Int. J. Electron., vol. 23, pp. 573-583, 1992.

[4] H. 0. Elwan. and A. M. Soliman. "Low voltage. low power CMOS

current conveyors". IEEE Trans. Circuits and Systems-I, vol. 44. 110. 9.

pp. 828-835. Sept. 19973, pp. 573-583, 1992.

[5] D. R. Bhaskar, V. K. Sharma, M. Monis and S. M. I. Rizvi, New

current-mode universal biquad filter, Microelectronics Journal, vol. 30,

pp. 837-839, 1999

16

You might also like

- High Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastaDocument12 pagesHigh Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastanengsintanovitaNo ratings yet

- A Low-Voltage Current Conveyor Using Inverter-Based Error Amplifier and Its Oscillator ApplicationDocument7 pagesA Low-Voltage Current Conveyor Using Inverter-Based Error Amplifier and Its Oscillator ApplicationAshin AntonyNo ratings yet

- CMOS Translinear CellsDocument4 pagesCMOS Translinear CellsSumitChoudharyNo ratings yet

- Performance Analysis of Multi-Level Inverter For Dynamic Voltage RestorerDocument6 pagesPerformance Analysis of Multi-Level Inverter For Dynamic Voltage Restorersup9No ratings yet

- Improved Voltage and Power Quality of Cascaded Inverters Using Sine Quantization Progression MethodDocument8 pagesImproved Voltage and Power Quality of Cascaded Inverters Using Sine Quantization Progression MethodSabdo WibowoNo ratings yet

- 1.2 V BiCMOS Sinh-Domain FiltersDocument21 pages1.2 V BiCMOS Sinh-Domain Filterschr kasimNo ratings yet

- Analog Multiplier PDFDocument7 pagesAnalog Multiplier PDFpratimasingh15696No ratings yet

- Implementation of KHN Biquad Filter Using Differential Voltage Current Controlled ConveyorDocument4 pagesImplementation of KHN Biquad Filter Using Differential Voltage Current Controlled ConveyorijsretNo ratings yet

- High Performance CMOS Four Quadrant Analog Multiplier in 45 NM TechnologyDocument6 pagesHigh Performance CMOS Four Quadrant Analog Multiplier in 45 NM TechnologyInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Chen 2016Document5 pagesChen 2016srilakshmisiriNo ratings yet

- Realization of Voltage Mode Universal Filter by Using Single Differential Voltage Current Conveyor Transconductance AmplifierDocument4 pagesRealization of Voltage Mode Universal Filter by Using Single Differential Voltage Current Conveyor Transconductance AmplifierijsretNo ratings yet

- Second Generation Current ConveyorDocument4 pagesSecond Generation Current Conveyormuhammad_andinovaNo ratings yet

- 06125602Document6 pages06125602Ahmad Sadam SyaeroziNo ratings yet

- Cad Lab ManualDocument15 pagesCad Lab ManualSougata Ghosh100% (2)

- Digitally Programmable Second Generation Current Conveyor-Based FPAADocument11 pagesDigitally Programmable Second Generation Current Conveyor-Based FPAAShailaja ManthaNo ratings yet

- Single-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDocument14 pagesSingle-Phase Seven-Level Grid-Connected Inverter For Photovoltaic Systemqais652002No ratings yet

- Briquetting, Binder, Solid Waste From Flour Mill (SWFM), Biomass, Cotton Waste.Document4 pagesBriquetting, Binder, Solid Waste From Flour Mill (SWFM), Biomass, Cotton Waste.International Jpurnal Of Technical Research And ApplicationsNo ratings yet

- Analog Electronics Lab ManualDocument49 pagesAnalog Electronics Lab ManualReddyvari VenugopalNo ratings yet

- Single-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDocument9 pagesSingle-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDeepak Kumar NayakNo ratings yet

- 11 Imposed Sinusoidal SourceDocument10 pages11 Imposed Sinusoidal SourcesathyasonyNo ratings yet

- Novel, Switch, Z-Source Three-Phase InverterDocument6 pagesNovel, Switch, Z-Source Three-Phase InverterJanjanam PraveenNo ratings yet

- Low Noise AmplifierDocument7 pagesLow Noise AmplifierGautam DhanabalanNo ratings yet

- Analysis and characterization of current mirror topologies in 90nm technologyDocument6 pagesAnalysis and characterization of current mirror topologies in 90nm technologyGurinder Pal SinghNo ratings yet

- A New Voltage-Mode Khn-Biquad Using Differential Difference Current ConveyorsDocument4 pagesA New Voltage-Mode Khn-Biquad Using Differential Difference Current ConveyorsAkanksha MathurNo ratings yet

- High-Frequency Response Modelling of Continuous-Time Current MirrorsDocument7 pagesHigh-Frequency Response Modelling of Continuous-Time Current Mirrorsaiace00No ratings yet

- Fine Tuning of Cascaded D-Q Axis Controller For AC-DC-AC Converter Without DC Link Capacitor Using Artificial Neural NetworkDocument8 pagesFine Tuning of Cascaded D-Q Axis Controller For AC-DC-AC Converter Without DC Link Capacitor Using Artificial Neural NetworkHedra GirgisNo ratings yet

- Permanent Magnet Synchronous Motor Drive Based On Maximum Boost Control Z-Source SVPWMDocument8 pagesPermanent Magnet Synchronous Motor Drive Based On Maximum Boost Control Z-Source SVPWMQamilNo ratings yet

- Analog Integrated Circuits Exercise 4: Common-Source and Differential AmplifiersDocument9 pagesAnalog Integrated Circuits Exercise 4: Common-Source and Differential Amplifiersubuntu 13.04No ratings yet

- A Simplified Forward and Backward Sweep ApproachDocument5 pagesA Simplified Forward and Backward Sweep ApproachImranAhmadQuadriNo ratings yet

- Harmonic and Loss Analysis of Space-Vector Modulated ConvertersDocument6 pagesHarmonic and Loss Analysis of Space-Vector Modulated Convertersahmet ozturkNo ratings yet

- Model Predictive Current Control Method With ImproDocument20 pagesModel Predictive Current Control Method With ImprogiovanniNo ratings yet

- A New Approach Ultra Low Voltage CMOS Logic Circuits AnalysisDocument5 pagesA New Approach Ultra Low Voltage CMOS Logic Circuits AnalysisijsretNo ratings yet

- Modified Valley-Fill For Harmonics ReductionDocument4 pagesModified Valley-Fill For Harmonics ReductionAyong HiendroNo ratings yet

- Control of Indirect Matrix Converter Under Unbalanced Source Voltage and Load Current ConditionsDocument7 pagesControl of Indirect Matrix Converter Under Unbalanced Source Voltage and Load Current Conditionssweetu_adit_eeNo ratings yet

- Comparison of CMOS Current Mirror SourcesDocument5 pagesComparison of CMOS Current Mirror SourcesidescitationNo ratings yet

- 4 Quadrant Mos MultiplierDocument4 pages4 Quadrant Mos Multiplierapi-3758194No ratings yet

- International Journal of Computational Engineering Research (IJCER)Document7 pagesInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)No ratings yet

- Operational Transconductance Amplifier For Highly Linear ApplicationDocument5 pagesOperational Transconductance Amplifier For Highly Linear ApplicationIJERDNo ratings yet

- WTHD and Power Quality Analysis of Space Vector Modulated Voltage Source Inverters For WecsDocument7 pagesWTHD and Power Quality Analysis of Space Vector Modulated Voltage Source Inverters For Wecsdaiduongxanh14113No ratings yet

- Iceict2015i020315001 PDFDocument6 pagesIceict2015i020315001 PDFmadihaNo ratings yet

- Modified Multilevel Inverter Topology For Grid Connected PV SystemsDocument7 pagesModified Multilevel Inverter Topology For Grid Connected PV SystemsAJER JOURNALNo ratings yet

- Control Strategy for Three-Phase PWM Boost RectifierDocument18 pagesControl Strategy for Three-Phase PWM Boost RectifierHoàngMạnhTuấnNo ratings yet

- Implementation of A High Voltage Power SupplyDocument4 pagesImplementation of A High Voltage Power SupplyJiakeat LiauNo ratings yet

- International Journal of Electronics and Communications (AEÜ)Document12 pagesInternational Journal of Electronics and Communications (AEÜ)RajeeNo ratings yet

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDocument12 pagesDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaNo ratings yet

- 2006 Crte IV Curve Measurement PV SecDocument5 pages2006 Crte IV Curve Measurement PV Secmoussa1986No ratings yet

- Modified Z-Source Single-Phase Inverter for PM Motor DrivesDocument6 pagesModified Z-Source Single-Phase Inverter for PM Motor DrivesPRACHI KATARENo ratings yet

- Multistring Five-Level Inverter With Novel PWMDocument13 pagesMultistring Five-Level Inverter With Novel PWMsandeepbabu28No ratings yet

- A Nonlinearity-Compensated All-MOS Voltage-to-Current ConverterDocument5 pagesA Nonlinearity-Compensated All-MOS Voltage-to-Current ConverterAram ShishmanyanNo ratings yet

- Solutions of Ac - DC Power Flow.-2Document7 pagesSolutions of Ac - DC Power Flow.-2Krishna ReddyNo ratings yet

- Elmeco4 325-331Document7 pagesElmeco4 325-331luis900000No ratings yet

- Low Noise GaAs FET/BJT VCODocument8 pagesLow Noise GaAs FET/BJT VCOsanjeevsoni64No ratings yet

- Single Phase Full Bridge Inverter With Coupled Filter Inductors and Voltage Doubler For PV Module Integrated Converter SystemDocument7 pagesSingle Phase Full Bridge Inverter With Coupled Filter Inductors and Voltage Doubler For PV Module Integrated Converter Systemd_wiNo ratings yet

- All MOS - Voltage To Current - ConverterDocument5 pagesAll MOS - Voltage To Current - ConverterAram ShishmanyanNo ratings yet

- Paper 2 - PEL20120014 - 2ndDocument5 pagesPaper 2 - PEL20120014 - 2ndSherif M. DabourNo ratings yet

- Energies: Analysis of Dc-Link Voltage Switching Ripple in Three-Phase PWM InvertersDocument14 pagesEnergies: Analysis of Dc-Link Voltage Switching Ripple in Three-Phase PWM InvertersluanleNo ratings yet

- Current Operational AmplifierDocument12 pagesCurrent Operational AmplifierJosé CamachoNo ratings yet

- ECE 8223 Analog IC Project ReportDocument15 pagesECE 8223 Analog IC Project Reportdiwakar4621No ratings yet

- EE3408E Project Design A Two-Stage Operational AmplifierDocument4 pagesEE3408E Project Design A Two-Stage Operational AmplifierLaSo ASNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Wind Turbine ArchitectureDocument1 pageWind Turbine ArchitectureTechnos_IncNo ratings yet

- Android IntroDocument7 pagesAndroid IntroTechnos_IncNo ratings yet

- WSN and RoutingDocument20 pagesWSN and RoutingTechnos_IncNo ratings yet

- Bigdata Medical1 PDFDocument5 pagesBigdata Medical1 PDFTechnos_IncNo ratings yet

- An Efficient E2E Verifiable E-Voting System Without Setup AssumptionsDocument9 pagesAn Efficient E2E Verifiable E-Voting System Without Setup AssumptionsTechnos_IncNo ratings yet

- Android Best Titles 2018Document2 pagesAndroid Best Titles 2018Technos_IncNo ratings yet

- Smartphone-Based Door Locking SystemDocument4 pagesSmartphone-Based Door Locking SystemTechnos_IncNo ratings yet

- Robot LiteratureDocument58 pagesRobot LiteratureTechnos_IncNo ratings yet

- Economical Study and TestingDocument16 pagesEconomical Study and TestingTechnos_IncNo ratings yet

- Driver Drowsiness ProjectDocument67 pagesDriver Drowsiness ProjectTechnos_IncNo ratings yet

- Install Guide Ja JPDocument124 pagesInstall Guide Ja JPAtlantislandNo ratings yet

- Banking Robot MissingDocument18 pagesBanking Robot MissingTechnos_IncNo ratings yet

- Form 1Document5 pagesForm 1rammohanNo ratings yet

- IEEE ConferenceDocument9 pagesIEEE ConferenceTechnos_IncNo ratings yet

- Thermal and Structural Analysis of Vented and Normal Disc Brake RotorsDocument9 pagesThermal and Structural Analysis of Vented and Normal Disc Brake RotorsTechnos_IncNo ratings yet

- Energy Efficient Scheduling of Real-Time Tasks in Cloud EnvironmentDocument8 pagesEnergy Efficient Scheduling of Real-Time Tasks in Cloud EnvironmentTechnos_IncNo ratings yet

- A Human Hand Gesture Based TV Fan Control System Using Open CVDocument99 pagesA Human Hand Gesture Based TV Fan Control System Using Open CVTechnos_IncNo ratings yet

- Skin Cancer ReportDocument85 pagesSkin Cancer ReportTechnos_IncNo ratings yet

- Android Theft Tracking ReportDocument56 pagesAndroid Theft Tracking ReportTechnos_IncNo ratings yet

- Buffer ReportDocument58 pagesBuffer ReportTechnos_IncNo ratings yet

- ESP8266 WiFi Module Quick Start GuideDocument15 pagesESP8266 WiFi Module Quick Start GuideMitesh Khadgi100% (1)

- Image Fusion ReportDocument79 pagesImage Fusion ReportTechnos_IncNo ratings yet

- Object DetectionDocument20 pagesObject DetectionTechnos_Inc100% (1)

- Embedded C LanguageDocument34 pagesEmbedded C LanguageTechnos_Inc100% (1)

- Hand GestureDocument18 pagesHand GestureTechnos_IncNo ratings yet

- MEMS and Microsystems OverviewDocument11 pagesMEMS and Microsystems OverviewSenthilkumaar JSNo ratings yet

- AddersDocument11 pagesAddersFikris RamadhaniNo ratings yet

- Target TrackinDocument39 pagesTarget TrackinTechnos_IncNo ratings yet

- Io DesignDocument14 pagesIo DesignTechnos_IncNo ratings yet

- Online Review ModulesDocument2 pagesOnline Review ModulesTechnos_IncNo ratings yet

- Theory of Personality Chapter-1Document13 pagesTheory of Personality Chapter-1chat gaza0% (1)

- Dualtech Training Center Presentation RVSADocument17 pagesDualtech Training Center Presentation RVSADennis SalongaNo ratings yet

- Md Alauddin resume for finance rolesDocument2 pagesMd Alauddin resume for finance rolesShanto ShikdarNo ratings yet

- Questionnaire FinalDocument7 pagesQuestionnaire Finalapi-676636026No ratings yet

- 1 Shared Vision & RationaleDocument5 pages1 Shared Vision & Rationaleapi-664491465No ratings yet

- Effective Training: Systems, Strategies and Practices,: 4 EditionDocument14 pagesEffective Training: Systems, Strategies and Practices,: 4 EditionMaleeha WaheedNo ratings yet

- 1982-1983 Southern Illinois University Bulletin Carbondale Campus PDFDocument221 pages1982-1983 Southern Illinois University Bulletin Carbondale Campus PDFJoe HollandNo ratings yet

- Ethical Issues of StudentsDocument11 pagesEthical Issues of StudentsAyeshaNo ratings yet

- Report Assessment 1 CSC264 - Muhammad Hafiz Imran Bin AhmadDocument9 pagesReport Assessment 1 CSC264 - Muhammad Hafiz Imran Bin AhmadMUHD HAFIZ IMRAN BIN AHMADNo ratings yet

- 4th Periodical in MAPEH 5Document5 pages4th Periodical in MAPEH 5Airma Ross Hernandez100% (1)

- Jorge Hernandez Finished Zine For Senior Project-CompressedDocument16 pagesJorge Hernandez Finished Zine For Senior Project-Compressedapi-550322126No ratings yet

- Reflective Writing - PoetryDocument20 pagesReflective Writing - PoetryPhion MulcareNo ratings yet

- House and Home HandbookDocument100 pagesHouse and Home HandbookANA ELENA TILLERO VALDIVIEZONo ratings yet

- AgileDocument4 pagesAgilebilal786khan74% (38)

- Nutrition for Oral and Dental HealthDocument27 pagesNutrition for Oral and Dental HealthMarco TNo ratings yet

- Topic 2 - The Application LetterDocument19 pagesTopic 2 - The Application LetterMad KennyNo ratings yet

- Clinical Case Reviews 2016Document34 pagesClinical Case Reviews 2016johnNo ratings yet

- Nearpod: Creation of AccountsDocument4 pagesNearpod: Creation of AccountsKlarisi VidalNo ratings yet

- Leadership and Philosophy EssayDocument6 pagesLeadership and Philosophy Essayapi-570983722100% (1)

- TACO Design Suite PDFDocument4 pagesTACO Design Suite PDFjupocNo ratings yet

- Down Syndrome and AutismDocument8 pagesDown Syndrome and AutismChristine Joy GonzalesNo ratings yet

- Ethics and Accountability in PhilippineDocument32 pagesEthics and Accountability in PhilippineMelchor Padilla DiosoNo ratings yet

- 44S SPP Sanctioned Projects ListDocument240 pages44S SPP Sanctioned Projects ListM. Sadiq. A. PachapuriNo ratings yet

- Bns Accomplishment ReportDocument4 pagesBns Accomplishment ReportRaquel ParcareyNo ratings yet

- Curriculum Vitae: Career ObjectiveDocument3 pagesCurriculum Vitae: Career ObjectiveZakir AhmadNo ratings yet

- Meningkatkan Motivasi Dan Hasil Belajar Siswa Menggunakan Media Animasi Pada Materi Pertumbuhan Dan Perkembangan Tumbuhan Di SMA Negeri 1 JalaksanaDocument6 pagesMeningkatkan Motivasi Dan Hasil Belajar Siswa Menggunakan Media Animasi Pada Materi Pertumbuhan Dan Perkembangan Tumbuhan Di SMA Negeri 1 JalaksanaAbiy NusaibahNo ratings yet

- 4-Organization Behavior - Introduction-24!09!2021 (24-Sep-2021) Material I 24-09-2021 MGT1065 Module-IIIDocument50 pages4-Organization Behavior - Introduction-24!09!2021 (24-Sep-2021) Material I 24-09-2021 MGT1065 Module-IIIDivyansh SrivastavaNo ratings yet

- Reviewer in Industrial and Organizational PsychologyDocument4 pagesReviewer in Industrial and Organizational PsychologyAirra May MedranoNo ratings yet

- Lesson Plan WorksheetDocument4 pagesLesson Plan WorksheetMichael UrrutiaNo ratings yet

- Critical Thinking in Midwifery PracticeDocument19 pagesCritical Thinking in Midwifery PracticeDyna Amani FadillahNo ratings yet