Professional Documents

Culture Documents

Eec452-De Lab II

Uploaded by

mailme4121Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Eec452-De Lab II

Uploaded by

mailme4121Copyright:

Available Formats

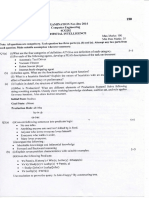

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT.

OF ELECTRONICS & COMMUNICATION

ENGG.

BUDDHA INSTITUTE OF TECHNOLOGY

DEPARTMENT OF ELECTRONICS & COMMUNICATION

ENGG.

LAB MANUAL

Semester : FOURTH

Sub Code : EEC 452

Subject : Digital Electronics Lab-II

Digital Electronics Lab-II Manual

4th sem

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

INDEX

Sl. #

Experiment / Program

Page #

1.

TTL TRANSFER CHARACTERISTICS AND TTL

IC GATES.

2.

3.

CMOS GATE TRANSFER CHARACTERISTICS.

IMPLEMENTATION OF A 3-BIT SIPO AND SISO

SHIFT REGISTER USING FLIP-FLOPS.

4

6

4.

09

6.

7.

IMPLEMENTATION OF A 3-BIT PIPO AND PISO

SHIFT REGISTER USING FLIP-FLOPS.

DESIGN OF SEVEN SEGMENT DISPLAY DRIVER

FOR BCD CODES.

BCD ADDER & SUBTRACTOR.

Study of ALU

8.

8085 ASSAMBLY LANGUAGE PROGRAMMING.

20

5.

Digital Electronics Lab-II Manual

4th sem

11

14

17

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Experiment No- 1

AIM: To study TTL transfer characteristics.

APPARATUS REQUIRED: Digital Trainer Kit, Dual Power supply, Multimeter.

IC 74LS00 (TTL Based Quad 2-Input NAND Gate) and

Connecting wires.

THEORY:

TTL CHARACTERISTICS:

Fan-in is the maximum number of inputs to a gate. Although physical considerations limit fan-in,

more pragmatic factors, such as limitations on the number of pins possible on IC packages and their

standardization predominate. TTL NAND gates typically provide 1, 2, 4, or 8 inputs.

If more than eight inputs are required, then a network of NAND gates must be employed.

Fan-out specifies the number of standard loads that the output of a gate can drive without

impairing its normal operation. A standard load is defined to be the amount of current required to

drive an input of another gate in the same logic family. Due to the nature of TTL gates, two different

fan-out values are given, one for HIGH outputs and one for LOW outputs.

Negative; hence, IILmax = -1.6mA. A typical TTL gate can source 400 A (I0H(max)) of

Current and can sink 16 mA (I0L(max)). Hence TTL gates typically have a HIGH (logic level) fanout of |I0H(max)/IIH(max)| = |-400 A / 40 A| = 10, and a LOW fan-out of

|I0L(max)/IIL(max)| = |16 mA / -1.6 mA| = 10. Exceeding these fan-out limits may result in incorrect

voltage levels at the output, as a gate cannot provide or sink enough current. A

CIRCUIT DIAGRAM:

voltage transfer curve is a graph of the input voltage to a gate versus its output voltage Figure 3.2

shows the transfer curve for TTL inverter without any fan out. When the input voltage is 0 V, the

output is HIGH at 3.3 V. As the input voltage is increased from 0 to 0.7 V, the output

Current & Voltage parameters:

High level i/p voltage VIH : This is the min. i/p voltage at the o/p corresponding to logic1.

Digital Electronics Lab-II Manual

4th sem

Page1

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Low level i/p voltage VIL : This is the max. i/p voltage which is recognized by the gate as logic0.

High level output voltage VOH : This is the min. voltage available at the o/p corresponding to

logic1.

Low level o/p voltage VOL : This is the max. voltage available at the o/p corresponding to logic0.

PROCEDURE:

1) Connect the circuit as per circuit diagram for TTL IC.

2) Vary the i/p voltage in steps & note down corresponding o/p voltage.

3) Plot graph of Vi Vs Vo.

OBSERVATIONS:

Sr.

1

2

3

4

5

6

7

Digital Electronics Lab-II Manual

Vi

4th sem

Vo

Page2

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

RESULT: Thus transfer characteristics of TTL IC is studied.

PRECAUTIONS:

(i)

Connections were given as per circuit diagram.

(ii)

Switch on the power supply after connecting circuit.

(iii)

Logical inputs were given as per truth table.

(iv)

Observe the logical output and verify with the truth tables.

Digital Electronics Lab-II Manual

4th sem

Page3

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Digital Electronics Lab-II Manual

4th sem

Page4

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Experiment No- 2

AIM: To study CMOS transfer characteristics.

APPARATUS REQUIRED: Digital Trainer Kit, Dual Power supply, Multimeter.

IC 74H00 ((CMOS Based Quad 2-Input NAND Gate)) and

Connecting wires.

THEORY:

CMOS FAMILY

CMOS logic is exemplified by its extremely low power consumption and high noise immunity.

Hence, it is prevalently used in devices demanding low power dissipation, such as digital

wristwatches and other battery powered devices, or in devices operated in noisy environments, such

as industrial plants. A wide variety of CMOS logic devices in the 4000 series are available. Unlike

TTL logic, CMOS logic requires two supply voltages, VDD and VSS. In typical logical designs,

VDD ranges from +3 V to +16 V. The other supply, VSS, is normally grounded. Also, the physical

representation of the binary states in CMOS logic is not entirely compatible with TTL logic. As a

consequence of CMOS's extremely high input impedance, the logic levels in CMOS systems are

essentially VDD and ground. If, for example, a 5 volt power supply is used, LOW typically ranges

from 0 to 0.01 V and HIGH from 4.99 to 5.0 V for CMOS outputs. Input voltages ranging from 3.5 to

5 V are recognized as HIGH and voltages from 0 to 1.5 V as LOW. It may appear that CMOS output

logic levels, using a 5 V power supply, completely conform to the TTL logic level ranges of 0 to 0.8

V for LOW and 2.0 to 5.5 V for HIGH. However, the Typical CMOS gates can sink about 0.4 mA in

the LOW state while maintaining an output voltage of 0.4 V or less. (A pull-up resistor to +5 can be

connected to the gate output to assure that the output is above 3.5V.) Whether this is sufficient for

reliable operation depends upon the exact specifications for both the TTL outputs and the CMOS

inputs.

CIRCUIT DIAGRAM:

CMOS CHARACTERISTICS:

The voltage transfer curve for a typical CMOS logic gate is shown in Figure 3.6. Note that the curves

in the transition region are almost vertical. This narrow transition region is the reason for CMOS

logic's high noise immunity. Not much voltage range is covered in the transition from voltage and is

approximately half the supply voltage.

Digital Electronics Lab-II Manual

4th sem

Page5

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

As with TTL logic, current spiking occurs during switching. Hence, bypass capacitors are used in

CMOS logic design as well. However, they are not as critical as in TTL logic design because of

CMOS's high noise immunity. Whereas the typical quiescent (static) power dissipation (power

dissipation of a device that is not changing logic states) of TTL IC's was about 40 mW, the power

dissipation of CMOS IC's are typically 25 nW.

PROCEDURE:

1) Connect the circuit as per circuit diagram for CMOS IC.

2) Vary the i/p voltage in steps & note down corresponding o/p voltage.

3) Plot graph of Vi Vs Vo.

OBSERVATIONS:

Sr.

1

2

3

4

5

6

7

Digital Electronics Lab-II Manual

Vi

4th sem

Vo

Page6

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

RESULT: Thus transfer characteristics of CMOS IC is studied.

PRECAUTIONS:

(i)

Connections were given as per circuit diagram.

(ii)

Switch on the power supply after connecting circuit.

(iii)

Logical inputs were given as per truth table.

(iv)

Observe the logical output and verify with the truth tables.

Digital Electronics Lab-II Manual

4th sem

Page7

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Experiment No- 3

AIM: Bread board implementation of a 3-bit SIPO & SISO shift resisters using flip-flops.

APPARATUS REQUIRED:

Sl.No.

COMPONENT

SPECIFICATION

QTY.

1.

2.

3.

4.

D FLIP FLOP

OR GATE

IC TRAINER KIT

CONNECTING WIRE

IC 7474

IC 7432

-

2

1

1

AS PER RQUIREMENT

THEORY:

In digital circuits, a shift register is a cascade of flip flops, sharing the same clock, which has the

output of any one but the last flip-flop connected to the "data" input of the next one in the chain,

resulting in a circuit that shifts by one position the one-dimensional "bit array" stored in it, shifting in

the data present at its input and shifting out the last bit in the array, when enabled to do so by a

transition of the clock input. More generally, a shift register may be multidimensional; such that its

"data in" input and stage outputs are themselves bit arrays: this is implemented simply by running

several shift registers of the same bit-length in parallel.

Shift registers can have both parallel and serial inputs and outputs. These are often configured as

serial-in, parallel-out (SIPO) or as parallel-in, serial-out (PISO). There are also types that have

both serial and parallel input and types with serial and parallel output. There are also bi-directional

shift registers which allow shifting in both directions: LR or RL. The serial input and last output

of a shift register can also be connected together to create a circular shift register.

Serial-in, serial-out (SISO)

Destructive readout

These are the simplest kind of shift registers. The data string is presented at 'Data In', and is shifted

right one stage each time 'Data Advance' is brought high. At each advance, the bit on the far left (i.e.

'Data In') is shifted into the first flip-flop's output. The bit on the far right (i.e. 'Data Out') is shifted

out and lost.

The data are stored after each flip-flop on the 'Q' output, so there are four storage 'slots' available in

this arrangement; hence it is a 4-Bit Register. To give an idea of the shifting pattern, imagine that the

register holds 0000 (so all storage slots are empty). As 'Data In' presents 1, 0,1,1,0,0,0,0 (in that order,

with a pulse at 'Data Advance' each time this is called clocking or strobing) to the register, this is

the result. The left hand column corresponds to the left-most flip-flop's output pin, and so on.

Digital Electronics Lab-II Manual

4th sem

Page8

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

So the serial output of the entire register is 10110000. As you can see if we were to continue to input

data, we would get exactly what was put in, but offset by four 'Data Advance' cycles. This

arrangement is the hardware equivalent of a queue. Also, at any time, the whole register can be set to

zero by bringing the reset (R) pins high.

Serial-in, parallel-out (SIPO)

This configuration allows conversion from serial to parallel format. Data is input serially, as

described in the SISO section above. Once the data has been input, it may be either read off at each

output simultaneously, or it can be shifted out and replaced.

LOGIC DIAGRAM:

SERIAL IN SERIAL OUT:

TRUTH TABLE:

CLK

Serial In

Serial Out

SERIAL IN PARALLEL OUT

Digital Electronics Lab-II Manual

4th sem

Page9

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

TRUTH TABLE:

CLK

DATA

OUTPUT

QA

QB

QC

QD

RESULT: The entire shift right & shift left operations are verified operations.

PRECAUTIONS:

(i)

(ii)

(iii)

(iv)

Connections were given as per circuit diagram.

Switch on the power supply after connecting circuit.

Logical inputs were given as per truth table.

Observe the logical output and verify with the truth tables.

Digital Electronics Lab-II Manual

4th sem

Page10

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Experiment No- 4

AIM: Bread board implementation of a 3-bit PIPO & PISO shift resisters using flip-flops.

APPARATUS REQUIRED:

Sl.No.

COMPONENT

SPECIFICATION

QTY.

1.

2.

3.

4.

D FLIP FLOP

OR GATE

IC TRAINER KIT

CONNECTING WIRE

IC 7474

IC 7432

-

2

1

1

AS PER RQUIREMENT

THEORY:

Parallel-in, serial-out (PISO)

This configuration has the data input on lines D1 through D4 in parallel format. To write the data to

the register, the Write/Shift control line must be held LOW. To shift the data, the W/S control line is

brought HIGH and the registers are clocked. The arrangement now acts as a PISO shift register, with

D1 as the Data Input. However, as long as the number of clock cycles is not more than the length of

the data-string, the Data Output, Q, will be the parallel data read off in order.

4-Bit PISO Shift Register

The animation below shows the write/shift sequence, including the internal state of the shift register.

A register is capable of shifting its binary information in one or both directions is known as shift

register. The logical configuration of shift register consist of a D-Flip flop cascaded with output of

one flip flop connected to input of next flip flop. All flip flops receive common clock pulses which

causes the shift in the output of the flip flop.

PARALLEL IN SERIAL OUT

Digital Electronics Lab-II Manual

4th sem

Page11

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

TRUTH TABLE:

CLK

Q3

Q2

Q1

Q0

OUTPUT

PARALLEL IN PARALLEL OUT

RESULT: The entire shift right & shift left operations are verified operations.

PRECAUTIONS:

(i)

Connections were given as per circuit diagram.

(ii)

Switch on the power supply after connecting circuit.

(iii)

Logical inputs were given as per truth table.

(iv)

Observe the logical output and verify with the truth tables.

Digital Electronics Lab-II Manual

4th sem

Page12

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Experiment No- 5

AIM: Design of seven segment display driver for BCD code.

APPARATUS REQUIRED: Digital Trainer Kit, IC mc14511

Seven segment display (common anode),

Power Supply and Connecting wires.

THEORY:

In order to produce the required numbers or HEX characters from 0 to 9 and A to F respectively, on

the display the correct combination of LED segments need to be illuminated and BCD to 7-segment

Display Decoders such as the 74LS47 do just that. A standard 7-segment LED display generally has

8 input connections, one for each LED segment and one that acts as a common terminal or

connection for all the internal segments.

There are two important types of 7-segment LED digital display.

The Common Cathode Display (CCD) - In the common cathode display, all the cathode

connections of the LED's are joined together to logic "0" and the individual segments are

illuminated by application of a "HIGH", logic "1" signal to the individual Anode terminals.

The Common Anode Display (CAD) - In the common anode display, all the anode

connections of the LED's are joined together to logic "1" and the individual segments are

illuminated by connecting the individual Cathode terminals to a "LOW", logic "0" signal.

7-Segment Display Format

Truth Table for a 7-segment display

Individual Segments

Display

c d e F g

Digital Electronics Lab-II Manual

0

1

2

3

4

5

4th sem

Individual Segments

b c d e f

Display

Page13

8

9

A

b

C

d

E

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

6

7

7-Segment Display Elements for all Numbers.

Binary Coded Decimal

Binary Coded Decimal (BCD or "8421" BCD) numbers are made up using just 4 data bits (a nibble

or half a byte) similar to the Hexadecimal numbers we saw in the binary tutorial, but unlike

hexadecimal numbers that range in full from 0 through to F, BCD numbers only range from 0 to 9,

with the binary number patterns of 1010 through to 1111 (A to F) being invalid inputs for this type of

display and so are not used as shown below.

Decimal

0

1

2

3

4

5

6

7

Binary Pattern

8

4

2

1

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

BCD

Decimal

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Binary Pattern

8

4

2

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

BCD

8

9

Invalid

Invalid

Invalid

Invalid

Invalid

Invalid

BCD to 7-Segment Display Decoders

A binary coded decimal (BCD) to 7-segment display decoder such as the TTL 74LS47 or 74LS48,

have 4 BCD inputs and 7 output lines, one for each LED segment. This allows a smaller 4-bit binary

number (half a byte) to be used to display all the denary numbers from 0 to 9 and by adding two

displays together; a full range of numbers from 00 to 99 can be displayed with just a single byte of 8

data bits.

BCD to 7-Segment Decoder

Digital Electronics Lab-II Manual

4th sem

Page14

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

The use of packed BCD allows two BCD digits to be stored within a single byte (8-bits) of data,

allowing a single data byte to hold a BCD number in the range of 00 to 99.

An example of the 4-bit BCD input (0100) representing the number 4 is given below.

In practice current limiting resistors of about 150 to 220 would be connected in series between the

decoder/driver chip and each LED display segment to limit the maximum current flow. Different

display decoders or drivers are available for the different types of display available, e.g. 74LS48 for

common-cathode LED types, 74LS47 for common-anode LED types, or the CMOS CD4543 for

liquid crystal display (LCD) types.

RESULT:

Digital Electronics Lab-II Manual

4th sem

Page15

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

PRECAUTIONS:

1) Connect the circuit as shown fig.

2) Switch on the power supply & observe the output on 7-segment display for

different BCD input.

Digital Electronics Lab-II Manual

4th sem

Page16

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Experiment No- 6

AIM: To study of BCD Adder.

APPARATUS REQUIRED: Digital Trainer Kit

IC -7483 , 7408 , 7432

Connecting wires and Power supply ( 5v, Vcc )

Theory:

A BCD adder is a circuit that adds two BCD digits in parallel and produces a sum digit which is also

in BCD adder must include the correction logic in its internal construction. This adder has two 4 bit

BCD inputs X3 X2 X1 X0 , Y3 Y2 Y1 Y0 and a carry input (Cin). It also has a 4 bit sum output (S3

S2 S1 S0) and a carry output (Cout). Here the sum output is also in BCD form.

A BCD adder circuit must be able to do the following:

1. Add two 4-bit BCD numbers using straight binary addition.

2. If the 4-bit sum is equal to or less than 9, the sum is in proper BCD form and no Correction is

needed.

3. If the 4-bit sum is greater than 9, or if a carry is generated from the sum, the sum is not in the

BCD form. Then the digit 6 (0110) should be added to the sum to produce the BCD results.

The carry may be produced due to this addition and it is added to the next decimal position.

Digital Electronics Lab-II Manual

4th sem

Page17

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

LOGIC DIAGRAM OF BCD ADDER

K MAP

Y = S4 (S3 + S2)

TRUTH TABLE:

BCD SUM

S4

Digital Electronics Lab-II Manual

S3

S2

4th sem

S1

CARRY

C

Page18

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

RESULT: Operation of BCD adder is verified.

PRECAUTIONS: 1) Connections were given as per circuit diagram.

2) Logical inputs were given as per truth table

3) Observe the logical output and verify with the truth tables.

Digital Electronics Lab-II Manual

4th sem

Page19

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Experiment No-7

AIM: Implementation of Arithmetic Algorithm and perform ALU operations.

APPARATUS REQUIRED:

Digital Trainer Kit

IC 74181 and connecting wires

PROCEDURE:

1. Connections are made as shown in the Circuit diagram.

2. Change the values of the inputs and verify at least 5 functions given in the

Function table.

Pin detail & Function table:

Digital Electronics Lab-II Manual

4th sem

Page20

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Pin Diagram of IC 74181

Digital Electronics Lab-II Manual

4th sem

Page21

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

RESULT:

Digital Electronics Lab-II Manual

4th sem

Page22

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

Experiment No-8

AIM: 8085 assembly Language programming.

APPARATUS REQUIRED: 8085 Microprocessor Kit.

PROCEDURE:

1. Enter the program from location 2000 onward using EXMEM Command. Also enter the data at

locations 2009 and 200A.

2. Execute the program from 2000 using GO key and examine the result at location 200B.

PROGARM: (FOR ADDITION)

ADDRESS

OPCODE

2000

2003

2004

2005

2006

2007

2008

2009

200A

200B

21 09 20

LABEL

MNEMONIC

LXI

MOV

INX

ADD

INX

MOV

RST

7E

23

86

23

77

EF

OPRAND

H 2009

A,M

H

M

H

M,A

5

COMMENTS

Point to 1st no.

Load it in to accumulator

Point to 2nd number

Add the two numbers

Point to storage

Store it

DATA

DATA

Two HEX nos. to be added.

RESULT

Result

EXAMPLE:

Address

2009

200A

200B

Data

23 Data in decimal

32 Data in decimal

55 Answer in decimal

RESULT:

PROGARM: (FOR SUBTRACTION)

ADDRESS

OPCODE

2000

2003

2004

2005

2006

2007

21 09 20

LABEL

7E

23

96

23

77

Digital Electronics Lab-II Manual

MNEMONIC

LXI

MOV

INX

SUB

INX

MOV

OPRAND

H 2009

A,M

H

M

H

M,A

4th sem

COMMENTS

Point to 1st no.

Load it in to accumulator

Point to 2nd number

Subtract the two numbers

Point to storage

Store it

Page23

BUDDHA INSTITUTE OF TECHNOLOGY, GORAKHPUR - DEPTT. OF ELECTRONICS & COMMUNICATION

ENGG.

2008

2009

200A

200B

EF

RST

DATA

DATA

Two HEX nos. to be subtracted.

RESULT

Result

EXAMPLE:

Address

2009

200A

200B

Data

32 Data in decimal

12 Data in decimal

20 Answer in decimal

RESULT:

Digital Electronics Lab-II Manual

4th sem

Page24

You might also like

- State Space StabilityDocument4 pagesState Space Stabilitymailme4121No ratings yet

- CH 6Document53 pagesCH 6mailme4121No ratings yet

- FIR and IIR Filter Design Using Matlab: Prof. C.M KyungDocument12 pagesFIR and IIR Filter Design Using Matlab: Prof. C.M Kyungmailme4121No ratings yet

- Vlsi Unit1 NotesDocument34 pagesVlsi Unit1 Notesmailme4121No ratings yet

- CBSE Class 11 Physics Notes - Laws of MotionDocument18 pagesCBSE Class 11 Physics Notes - Laws of Motionmailme41210% (1)

- ENSC380 Objectives: Summary of Different Fourier Transform Methods Learn The Relationship Between Different DT MethodsDocument11 pagesENSC380 Objectives: Summary of Different Fourier Transform Methods Learn The Relationship Between Different DT Methodsmailme4121No ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Reference BookDocument313 pagesReference BooknirdeshNo ratings yet

- Prosthetic Arm For AmputeesDocument6 pagesProsthetic Arm For AmputeesPratik ParsewarNo ratings yet

- Motion 2000 Hydraulic v8 42-02-1P20 B7Document248 pagesMotion 2000 Hydraulic v8 42-02-1P20 B7ElputoAmo XD100% (1)

- Exambank HigherDocument62 pagesExambank HigherJust WadeNo ratings yet

- WO2015026689A1 - OBS IngevityDocument55 pagesWO2015026689A1 - OBS IngevityelenitabastosNo ratings yet

- SMPS Teune Mee PDFDocument71 pagesSMPS Teune Mee PDFbacuoc.nguyen356No ratings yet

- Research On The Formation of M1-Type Alite Doped With MgO and SO3-a Route To Improve The Quality of Cement Clinker With A High Content of MgODocument11 pagesResearch On The Formation of M1-Type Alite Doped With MgO and SO3-a Route To Improve The Quality of Cement Clinker With A High Content of MgODerekNo ratings yet

- Gas SolubilityDocument59 pagesGas Solubilitysomsubhra100% (1)

- Importance of ForecastingDocument37 pagesImportance of ForecastingFaizan TafzilNo ratings yet

- 24/10/2017. ",, IssnDocument2 pages24/10/2017. ",, IssnMikhailNo ratings yet

- Second Periodical ExamDocument19 pagesSecond Periodical ExamMaynard Lee Estrada GomintongNo ratings yet

- IET DAVV 2014 Com2Document12 pagesIET DAVV 2014 Com2jainam dudeNo ratings yet

- Chapter 8 RevaDocument20 pagesChapter 8 RevaanildhakeNo ratings yet

- Manual Xtable EXCEL LinkDocument7 pagesManual Xtable EXCEL LinkElena Alexandra BeladanNo ratings yet

- Length Standards EngDocument1 pageLength Standards EngAsif Hameed100% (2)

- Codd's 12 Rules For Relational DatabasesDocument5 pagesCodd's 12 Rules For Relational DatabasesArul VermanNo ratings yet

- Reasoning Calendar Questions Finding Day or Date, Concepts, Shortcuts ExplainedDocument8 pagesReasoning Calendar Questions Finding Day or Date, Concepts, Shortcuts ExplainedManish KumarNo ratings yet

- The Nature of Mathematics: "Nature's Great Books Is Written in Mathematics" Galileo GalileiDocument9 pagesThe Nature of Mathematics: "Nature's Great Books Is Written in Mathematics" Galileo GalileiLei-Angelika TungpalanNo ratings yet

- Wyatt, ASTRA V Software User's Guide PDFDocument372 pagesWyatt, ASTRA V Software User's Guide PDFR YNo ratings yet

- The Impact of Credit Risk On The Financial Performance of Chinese BanksDocument5 pagesThe Impact of Credit Risk On The Financial Performance of Chinese Banksvandv printsNo ratings yet

- Ch23 Review ProblemsDocument25 pagesCh23 Review ProblemsحمدةالنهديةNo ratings yet

- RC2 22873Document2 pagesRC2 22873Henok AlemayehuNo ratings yet

- DE SHORT METHODS - RevisedDocument4 pagesDE SHORT METHODS - RevisedWilma NaderaNo ratings yet

- Blockchain Spec PDFDocument18 pagesBlockchain Spec PDFblueNo ratings yet

- Code Reason Effect: Step 1. Step 1ADocument2 pagesCode Reason Effect: Step 1. Step 1AAhmedmahNo ratings yet

- Pretvorbe Merskih EnotDocument4 pagesPretvorbe Merskih Enotpetrusa505No ratings yet

- AN78M20FDocument10 pagesAN78M20FFrantsiskoNo ratings yet

- Geehy 32 Bit ARM Cortex MCU - 2023 07 13 090801Document4 pagesGeehy 32 Bit ARM Cortex MCU - 2023 07 13 090801palurdo2No ratings yet

- Fy CS Labbook 2019 20Document46 pagesFy CS Labbook 2019 20rajeshkanade121No ratings yet

- CAPPC Presentation 12-5-05Document46 pagesCAPPC Presentation 12-5-05rahulNo ratings yet