Professional Documents

Culture Documents

AD Converters

Uploaded by

sayan0 ratings0% found this document useful (0 votes)

12 views28 pagesApplied electrical and electronics

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentApplied electrical and electronics

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

12 views28 pagesAD Converters

Uploaded by

sayanApplied electrical and electronics

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 28

NALOG-TO-DIGITAL

DIGITAL-TO-ANALOG —

CONVERTERS

17.1 INTRODUCTION

Ananalog quantity is one that can take on any value over a continuous range of v t represents

exact value, Most physical variables are analog in nature. Temperature, pressure, light and

‘ound intensity, position, rotation, speed, etc. are some examples of analog quantities,

A digital quantity takes on only discrete values. The value is expressed in a digital code such

‘Sabinary or BCD number.

When a physical process is monitored or controlled by a digital system such as a digital

seats the physical Variables are first converted into electrical signals using transducers, and

these electrical analog signals are converted into digital signals using analog-to-digital

Suverers(ADCS). These digital signals are processed by a digital computer andthe output ofthe

is converted into analog signals using digital-to-analog converters (DACs). The

is modified by an actuator and the output of the actuator is applied as the control

“shows how ADCs and DACs function as interfaces between a completely digital

ligital computer and the analog world. This function has become increasingly

.sive microcomputers are being widely used for process control,

77

:

NALOG (D/A) CONVERSION

iy. D/A is the process of converting a value Tepresented in digital code si,

Ql 0: BED. into voltage or eurrent which i proportional to the digital vale hoa

shows the symbol for a typical 4-bit D/A converter. Each of the digital inputs A, B, C,axiD,

assume a. pga therefore, there are 24 = 16 possible combinations of inputs. Foreachin

cee M,....1111, the D/A converter Outputs a unique value of voltage. The x

output voltage .,, is proportional othe input binary number, that is,

Analog output = K x digital input

‘where K is the proportionality factor and is constant value for a given DAC. The analogs)

can, of course, be current or voltage.

Resolution = step size= 1

Figure 17.2 Output wavetorm ofa DAC fed by a binary counter,

{7.2.1 Parameters of DAC

Resolution (step size). The resolution of aD.

the smallest change

inan analog output as a result of a change in the digital input. The resolution oF seen

Gefined as the reciprocal of the number of discrete steps in the full-scale output of the DAC. The

resolution is always equal to the Weight of the LSB and is also referred to as the step size. The

resolution or step size is the size of the jumps in the staircase waveform, The step size is the

out Will change as the digital input value is changed from one value to the next.

Forthe waveform shown in Fig

‘ure 17.3, the resolution or step size = 1 V. The step size of the DAC

Ithe same as the proportionality factor in the DAC input-output relationship,

Although resolution can be expressed as the amount of

Mill express it as a percentage of the full-scale output as

ALB

AC is defined as

‘oltage or current Per step, it is also

step size

% resolution = “PSVE 1999,

full scale

Since, full-scale = number of steps x step size,

x

total number of steps

resolution can be expressed as

% resolution =

100%

In Beneral, for an N-bit DAC, the number of different levels will be 2" and the number of

willbe 2"_ 1. The greater the number of bits, the greater will be the number of steps and the

atullet Will be the Step size, and therefore, the finer will be the resolution. Of course, the cost of

DAC increases with the number of input bits. cased,

The accuracy of a DACis usually specified in terms of its full-scale erora

anchare normally ed asa percentage ofthe converter’s full-scale output, The

ae

or,

ome

maximum deviation of the DAC’s output from its expected (ideal) value, expre

Of the full-scale, The linearity error is the maximum deviation of

©utput. The accuracy and resolution of a DAC must be co

700 ena OF DIGITAL CIRCUITS

Settling speed of a DACis usually specified by giving jy

fime, The oPetmtween the instant when the digital inpot changes ana g

pani ae error band for the last time, usually + 1/2 LSB around the

output enter

of 2054

: ed as the time for the DAC output to sete ‘olution

the change in digital input. It a rpics th a current output will have shorter seq we step

size of its final value, Generally, r et

those with voltage outputs. f fs ‘Thus d

Offset voltage. Ideally the output of a DAC should be zero when the binary inp a

mice, however there ia very small output voltage under this, situation called thea

This offet error, if not corrected, willbe added tothe expected DAC output foraliigg 472.2 DP

‘A DAC is said to be monotonic if its output increases as the bj ‘the DAC W

incremented from one value to the next. This means that the staircase output will haveng gg where 4-bit

steps as the binary inti ineremented fom Oto fll-scale value. The DAC issaiggat Pats co

monotonic, if its output decreases when the binary input is incremented, BCD inputs

AC it bits

EXAMPLE17.1. Determine the resolution of (a) 6-bit DAC and that of aI ee a

in terms of percentage. Or athe

Solution weight that i

(a) For the 6-bit DAC,

4 resolution 100 = s<100 = 1.589%

2-1 6

(b) For the 12-bit DAC,

4% resolution «100 = 100 = 0.0084

is | 4095

EXAMPLE 17.2 A 6-bit DAC has a step size of 50 mV. Determine the AMAIA

voltage and the percentage resolution

Solution

With 6 bits, there will be 2 — 1 = 63 ste,

= 05 steps of size 50 mV each.

The full-scale output will, therefore, be

63x 50mV=3.15 y

S0mv

% resolution = Sis yX100= 4 100 = 1.587% j oa

EXAMPLE 17.3 Ang i 008! and Dic.

Find the full-scale output, ce Fi patees Vag = 0.05 V fora digital input of i iy ee Peo

a ~ Nhat is the resolution? What is Vu: for an input of OOO lution

Fall-scale output =

Step size x Number of steps

" = 0.05(28 _ 1) =0.05 x 255 = 12,75 V

resolution = 1 1

Way GPs S100. = 0.392%

Vou. for an input F 00101010 249 x 0.95 Meso

[EIT Acertain6-bitDAChasg

full-scale out

ime. What is the range of possible out net mA and a fu

i st PU for an j Scale error

that the ft 04 F Mut of 1000097

‘Tue af 2 mA/63 = 31.7 LA, Sing,

; t size is 2 HA. Since 100000 = \

U2 step te ae TO14 HA. The error can be as much ase glog anny Acti sould be

NES than Ppysibe actual Output can deviate by this amency from the ideal value of 10

gfe atl UtPu can be anywhere fom 1004 nae el ‘a

Zero, fy th

Voltage 92 DAC Using BCD Input Code

cases, ft

s AC we considered earlier used a binay input code, Many DACs

input js the DI

use a BCD input code,

code groups are used for each decimal digit, Figure 174showet :

code group eit, Figure 17.4 shows the diagram of an 8-b

waward sere bit code & gram of an 8-bit

saieit) converter of this type. Each 4-bit code sroup can range from 0000 to 1001, and so the

be non es present decimal numbers from 00 to 99, Within each code group, the Weight ofthe

Dinputs represe soup, the weig

Be escein the normal binary proportions (1/204 8), but the relative weights ofeach code

DAC ee rrerent by a factor of 10. Figure 17.4 shows the relative weights ofthe various bis

ed " bits that make up the BCD code for the most significant digit (MSD) have a relative

séahtthat is 10 times th

Ht hac Step size = weight of As

BOD | c,

usp

ut code.

ae sing BOD inpu iy

Figure 17.4 DAC us 1714 find the following 4

Ay is 0.2 V in Figure Tay forD,C\BiAy

PAMPLE 17.5 If the we . perce tage resolution, @

5001 Sep size, (b) full-scale output, (

‘dD, is

0? 4CaB yA, = 0100. bo spscale ovat

‘on the LSD, it 0s, ie fl

{Step size is the weight of the LSB of the LS gi

are two

[There are 99 steps since there ate

Sx02V = 198 V,

Be = 1%

Theresotution is og TO

step size__ 100% = 9.8

full-scale output

|

y

’ 8 FUNDAMENTALS OF DIGITAL CIRCUITS

jehts ofthe various bits in the number in volts ares

fea) MSD: D, = 16, C, =8.B, =4,A, =2

Lsb Dy= 1.6, C,= 0.8, By = 0. vee

{@) One way to find V,,, fora given input is o add the weights of all the bits that gy

for an input of 01100100, we have

Cc, By Cy

Vig =8V+4V +08 V

As the BCD input code represents 64, and the step size is 0.2 V, V,,, can alsobeq

as

2.8. V

(0.2.V) x64 = 12.8V

EXAMPLE 17.6 A certain 12-bit BCD DAC has a full-scale output of 19,98

er iz Case

(a) the percentage resolution and (b) the converter’s step size Spee 17

ie er, 2R

Solution 1 Tadder, 2

(a) 12 BCD bits correspond to three decimal digits, i.e. decimal numbers from 000) ‘oter'h

Therefore, the output of the DAC has 999 possible steps from 0 V to 19.98 VeThaas foarmier,

have

1 cout

% resolution = z 100% 100% = 0.1%

number of steps

full-scale outpu 9.98 V

(b) Step size = full-scale output _ shoo

number of steps 999

17.2.3 Bipolar DACs

So far we have assumed that the binary input toa DAC is an unsigned number and the DAC

erro ace tetirent Such types of DACS are called unipoler DAG

Bipolar DACs are designed to produce both Positive and negative values. This is gee

done by using the binary input as a signed number with the MSB as the sign bit (ofeet

for ~), Negative input values are often Presented in 2's complement form, althout Pe

thabnitude form is also used by some DACs, For example, suppose we have a 6-bit

anaes the 2's complement system and hag a esc SP input vals

from 100000 (-32) worn as @ resolution of 0.2 V. The binary inpt

1111431) to produce analog from-6.4 V1

THAMES Gua el LLC 8 Outputs in the range from=6: ial

He ate 63 eps (21) 6602 V between ne negative and positive limits. st

, cs

y i,

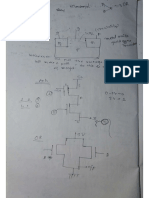

y 179 THE R2ALADDER TYPE Dag 7

The R22 ladder type p, ‘ ‘

\i patel combinatioee or, ances Popular DAC. It uses a ladder network cont rane

: configured a votuge foe alles R and 2R. Hence the name, The oper :

configured is

@R-2R ladder type DAC havine ea

the input terminals of the

‘peration of the DAC is

ing a

DAC, an equi;

a8 follows:

MsB

—_____ Mss

Digital input |

Figure 17.5 -2R ladder ype DAG.

When the input is 1000 i

Uillustrates the procedure to calculate V., when the inputs 100

ie; 2s in parallel with 2R, so tha the combinations equivalent to Mi

aoherR giving 2R. This 2R in parallel with another 2R is equivalent wo RG

fume we ultimately find that R., = 2R. The output voltage, V_. = ED.

== =

, 2 (0 Vyand,

(@) When the input is 1000; Dg, D, and D, are grounded (0 V)

q= 2h,

1 i ll

‘circuit equivalent to (a) when oa

' citcuit to the left of A is replaced .

‘784. FUNDAMENTALS OF DIGITAL CIRCUITS.

amp configs

op" The principal

i; _ a stan

a erefore, standard

(@) When te inpitis 0100 Dy, D, and D, are grounded (0V) and D; = +E 1h

R

2n

a2nS oR

Pa 3

a (aw

(0) Th cet aqutvaento (2) when the crcut

isreplabed by fs equvaent resistance Ai.

ang a

iM 8

pa oD oa ixenat

4% ((2A\\2A) + Fl=2R oa

) Theo

ay pee

(©) Thovenns equivalent the let of A a

Aig 2h

ee

ay +e

2A Vy e

(@) Calculation of Va, using the votage dvier rule

Figure 177. Calculation of V,., when the input is 0100,

ri

Case 4: When the input is 001

Figure 17.9 illustrates the

Vay =EN6, Provedure to calculate V,. when the input is 0001. The 0

pts @ 1 and all other inputs are a 0, the output

) The circuit equivalent to (a) wh

en the circultto he

be

nh

4 28=E (obtained by loop cent method or ny he MER

5 &

I Fo= M((2AII2A) + Fl2A) + AOR + A= 2A

Im

(c) Thevenin’s equivalent to th

@ left of A.

aR

— i

Im

(6) Calculation of Vi, using the voltage divider rule,

Figure 17.9 Calculation of V,., when the input i 0001

Solution

‘The output voltage level caused by the D, bit =

The output voltage level caused by the D, bit (MSB)

‘The output voltage level caused by the D, bi

E178 What is the resolu

ipihis resolution expressed ae ,

eis +5 V, what is the resoty

ion of a

jatin S12. The resolution

fealation is obtained by multiplyi

fhus.the resolution in volt

a4 THE WEIGHTED-RESISTOR Type DAC

Sellagram of the weight ,

silo produce a weight ‘perational amplifir is

sitisof the bit positio: i “enghts are proportional 1 the

m@iisamplified by a f 1s an inverting amplifier, ach

ance divided by the input

Ritu to which itis « amplified by R/2R. By

amplified by R,/4R

(SB) D,

oa 4

c + son

D, +

pan (LSB) D, A +

Figure 17.10 Since the

Tei 1. 10 acts 25.2 Virtual groan ¢

MVerting terminal of the op-amp 1 Figure

ad,

and inverts,

D, Di, De) x{

\ |. +> +9 7 rene

\ jerent-valoed Po

, dif

Pein disadvantage of this type of DAC is: that

“Ach bit position of the digital input

Solution i

jth a gain of 1, so, its weight = 5) ee

(a) The MSB passes with again >. following bit passes with a g

i 52.= he

ee the LSB passes with a gain of 1/8, So, its weight

weight = 5/4 = 1.25

(b) Therefore, the full scale output

R

1 ee

a ee) +

=1kQ) (34 ix

9.375 V

The full-scale output, when R, is changed to 500 2 is

(when Ry

EXAMPLE 17.10 Determine the output of the DAC in Figure 17-11, ifthe seq

the 4-bit numbers in Figure 17.11b is applied to the inputs. Dy is the LSB.

Solution ’

First, let us determine the output current / for each of the weighted inputs, Since

input (~) of the op-amp is at 0 V (virtual ground) and a binary 1 corresponds 19

current through any of the input resistors is 5 V divided by the resistance valle,

S3V_ 90125 mA; SV __ 9.025 mA

400 kQ

sv

= 0.05 mA;

1

2 100 kQ

The input impedance of the op-amp is extremely large; therefore, the

op-amp is zero. Thus, the current, J, + I, +1, + 1,, has to go through the feedb

R,, Since one end of R, is at 0 V (virtual ground), the drop across Ry edu

voltage

e 17.11b, the first input code is

‘code is 0010, for which the otge i

‘output voltage is — 0.75, and so on, Bach succes

age by - 0.25 V. So, for this particular st '

staircase waveform going from 0 V to ~ 3.75 V in—

im is shown in Figure 17,12.

E17. Design at Ph

levels are 1=+5)

790. FUNDAMENTALS OF DIGITAL GIRCUTS

‘Therefore

‘When the input is 1101, the output voltage

47.5 THE SWITCHED CURRENT-SOURCE TYPE D:

The R2Ra DAC and the weighted ded sich

into the cireuit, wher summed up with otf M ted circuit DAG

ela tn tage cep, the bina np ea

onl ‘

Figure 17.13 shows he circuit diagram ofa current switching type DAC, Nota

deri connected toa vole source Ey. The current inthe fist 2R resistor Om

given by /,= Eqg/2R, because Ey is directly applied across 2R. The current in the sO

given by Egrp/4R because the equivalent resistance to the right of the second 2R is 2Rand. 3

rent Eyey(R + R) coming into the fst Ris equally divided between the second ai

toits right

In genera, the current that lows in each 28 resistors given by, = (Eyl) Oa

12 =0, Syn N~ 1s the subseript forthe current created by input D,, and Ns the total

inputs, Thus, each current is weighted by the bit :

position it represents

‘The switches that connect the curens cither to ground or tothe input of te ont

amplifier are controlled by the digital input. The op~ 11 those cures

E ¢ op-amp sums up all thos ot

corresponding digital inputs are HIGH. The amplifier also serves as a voltage-t0-CUmTem Cok gg

is connected in an inverting configuration and ts outputis V... =~ [where fy iS

currents that have been switched wits input cn es ae nal ott

she

ie, the output of the DAC is proportional 1

of the variable Eye and the variable digital input. In that case, the circuit is called ®

IF Eygp ian externally variable volta

DAC andthe output represents the product of an analog input Ey, and a digital in

‘use) Ds

F

EXAMPLE 17.12

Egey = 10 V. Find th

digital input is 101

Solution

Since the digital ing

‘Therefore, the outp

EXAMPLE 17.13

is produced, What

Solution

Therefore,

Hence the output

witched

DACs,

S can be

re used

uurrents

ational

n ROR

pply is

1 2Ris

so, the

he 2R

where

per of

fional

yhose

enter.

sf the

yduct

lyin

Digital input

Figure 17.13 The

BAMPLE 17.12 The switched cur

Fe 10V. Find the total current de

digital input is 1101

Solution

Site the digital input is 1101, the total

-bit switch

>t switched currentsource Dag,

7.13 has R= $k and

the output voltage when the

current into the amplifier

ie fs given by

+h +l, TA

Free) (Eras

4k)” 16R

1010 10)_130_13

20°80) 80 8

Teefore, the outpu

PUMPLE 17.13 In 04-bit DAC, fora igital input of 010 an oupatcumeatot 10m

Poduced. What will be the output current for a digital input of 10

Suton

of 0100, ie. 4

Output current = 10 mA fora digital inpat of 0100, ie. 4

Analog output = K x digital input

Teefore, e

=2.5mA

4

a

Mie Output current for a digital input of 1011 1: 10

| ‘ THE Swit cHED-CAPACITOR TYPE DAC

tors ins

bcapacitor type DAC employs welled Sider

larged capacitors form a capacitive

binary inputs.

technology has been devel

ticularly MOS circuits. It is

784 FUNDAMENTALS OF DIGITAL ciRcUITS

b Divide by-256 counter

% % % % a a 2, 9,

Dy Ds; _D, dD, 0,

2D, Dy]

DIA converter

Figure 17.18 Logic diagram of the Counter-type ADC,

into reference analog voltage (which is in the form of a step) by the DAC. The counter eo

to advance from one state to the next, Producing successively larger steps in the refere a

ut Voltage reaches the value ofthe analog signal, the comparator ou

reach the counter and the.

UITs

requires ‘comparators. A reference voltage Egg is connected to a

divides cece qual increment levels. Bach level is compared to

a log input, one comparator and all those

ven anal

voltage comparator, For any 8 its are connected to a priority encoder, which,

HIGH output. All comparator output ; priority encoder, wh

a corresponding to the input having the highest priority, which in this case

represents the largest input. ‘Thus, the digital output represents the voltage that is closest

the analog input.

‘The voltage applied to

(by voltage divider action),

the inverting terminal of the uppermost comparator in

TR+R

Similarly, the voltage applied to the inverting terminal of the second comparator is

6R_)

(apeg) tae = 5% Eee

iS

( ae ar Ea

ee

and so forth, The increment between voltages is Fer

The flash converter uses no clock signal, because there is no timing or sequencing pei

‘The conversion takes place continuously. The only delays in the conversion are in the comp

and the priority encoders.

Figure 17.20 shows the block diagram of a modified flash A/D converter. To performantit

conversion, it requires two 4-bit flash converters. So, an 8-bit conversion can be done by tsi

30[= 2 x (24 — 1)] comparators instead of 25! — 1) comparators, One 4-bit flash converters

used to produce the four most significant bits (MSBs). Those four bits are converted back iit

analog voltage by a D/A converter and this voltage is subtracted from the analog input. ‘The different

between the analog input and the analog voltage corresponding to the four most significant bits

an analog voltage corresponding to the four least significant bits (LSBs). Therefore, that vollages

converted to the four least significant bits by another 4-bit flash converter.

4MSBs

4-bit flash

ADC.

diss )-Kke Latches [eva

4-bit flash

ADC.

Figure 17.20 Modified flash ADC.

EXAMPLE 17.16 Determine the digital output of a 3-bit si

i -bit simultaneous A/D

Mia nos seal onto eeting pales (encoder enable) shown in

rE “gules 27 Thg ners a

Figure 17.21 Example 17.16: Waveforms

u coal,

put sequence is listed as follows and shown in F

110, 110, 100, 010, 000, 000

- IF the D/A ony

siete 8 /A 0

causing the bit in the coy

put, the comparator output is HIGH, and

inpu He H, and:

Ys

tem enables the MSB first, then the next

ive been tried, the conversion cycle is con

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Btech MeDocument8 pagesBtech MesayanNo ratings yet

- Electrical Part 2Document46 pagesElectrical Part 2sayanNo ratings yet

- Analog To Digital Converter PDFDocument27 pagesAnalog To Digital Converter PDFsayanNo ratings yet

- Electric DrivesDocument31 pagesElectric DrivessayanNo ratings yet

- Encoder DecoderDocument14 pagesEncoder DecodersayanNo ratings yet

- Multiplexers & .Document14 pagesMultiplexers & .sayanNo ratings yet