Professional Documents

Culture Documents

Programmable Logic Devices: PDF Created With Pdffactory Pro Trial Version

Uploaded by

निमँलसिंह राउलजीOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Programmable Logic Devices: PDF Created With Pdffactory Pro Trial Version

Uploaded by

निमँलसिंह राउलजीCopyright:

Available Formats

Programmable Logic Devices

PDF created with pdfFactory Pro trial version www.pdffactory.com

n PLDs

¡ Programmable Logic Devices (PLD)

n General purpose chip for implementing circuits

n Can be customized using programmable switches

¡ Main types of PLDs

n PLA

n PAL

n ROM

n CPLD

n FPGA

¡ Custom chips: standard cells, sea of gates

PDF created with pdfFactory Pro trial version www.pdffactory.com

n PLD as a Black Box

Logic gates

Inputs and Outputs

(logic variables) programmable (logic functions)

switches

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Programmable Logic Array (PLA)

x1 x2 xn

¡ Use to implement

circuits in SOP form

Input buffers

¡ The connections in and

inverters

the AND plane are

programmable x1 x1 xn xn

P1

¡ The connections in

the OR plane are AND plane OR plane

programmable Pk

f1 fm

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Gate Level Version of PLA

x1 x2 x3

Programmable

connections

f1 = x1x2+x1x3'+x1'x2'x3 OR plane

P1

f2 = x1x2+x1'x2'x3+x1x3

P2

P3

P4

AND plane

f1 f2

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Customary Schematic of a PLA

x1 x2 x3

OR plane

f1 = x1x2+x1x3'+x1'x2'x3

P1

f2 = x1x2+x1'x2'x3+x1x3

P2

P3

P4

x marks the connections left in AND plane

place after programming

f1 f2

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Limitations of PLAs

¡ PLAs come in various sizes

n Typical size is 16 inputs, 32 product terms, 8 outputs

¡ Each AND gate has large fan-in à this limits the number of

inputs that can be provided in a PLA

¡ 16 inputs à 216 = possible input combinations; only 32

permitted (since 32 AND gates) in a typical PLA

¡ 32 AND terms permitted à large fan-in for OR gates as well

n This makes PLAs slower and slightly more expensive than

some alternatives to be discussed shortly

¡ 8 outputs à could have shared minterms, but not required

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Programmable Array Logic (PAL)

x1 x2 xn

¡ Also used to implement

circuits in SOP form

Input buffers

¡ The connections in and fixed connections

inverters

the AND plane are

programmable x1 x1 xn xn

P1

¡ The connections in

the OR plane are AND plane OR plane

NOT programmable Pk

f1 fm

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Example Schematic of a PAL

x1 x2 x3

f1 = x1x2x3'+x1'x2x3

f2 = x1'x2'+x1x2x3 P1

f1

P2

P3

f2

P4

AND plane

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Comparing PALs and PLAs

¡ PALs have the same limitations as PLAs (small

number of allowed AND terms) plus they have a

fixed OR plane à less flexibility than PLAs

¡ PALs are simpler to manufacture, cheaper, and

faster (better performance)

¡ PALs also often have extra circuitry connected to the

output of each OR gate

n The OR gate plus this circuitry is called a macrocell

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Macrocell

Select

Enable

OR gate from PAL 0

f1

1

D Q

Flip-flop

Clock

back to AND plane

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Macrocell Functions

¡ Enable = 0 can be used to allow the output pin for f1

to be used as an additional input pin to the PAL

¡ Enable = 1, Select = 0 is normal

for typical PAL operation Select

Enable

0

f1

1

¡ Enable = Select = 1 allows D Q

the PAL to synchronize the Clock

output changes with a clock

pulse back to AND plane

¡ The feedback to the AND plane provides for multi-

level design

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Multi-Level Design with PALs

¡ f = A'BC + A'B'C' + ABC' + AB'C = A'g + Ag'

n where g = BC + B'C' and C = h below

A B

Sel = 0

En = 0

0

1

h

D Q

Sel = 0

Clock En = 1

0

g

1

D Q

Select

Clock

0

f

1

D Q

Clock

PDF created with pdfFactory Pro trial version www.pdffactory.com

n ROM

¡ A ROM (Read Only Memory) has a fixed AND plane

and a programmable OR plane

¡ Size of AND plane is 2n where n = number of input

pins

n Has an AND gate for every possible minterm so that all

input combinations access a different AND gate

¡ OR plane dictates function mapped by the ROM

PDF created with pdfFactory Pro trial version www.pdffactory.com

n 4x4 ROM

¡ 22x4 bit ROM has 4 addresses that are decoded

2-to-4 decoder

a0

a1

d3 d2 d1 d0

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Programming SPLDs

¡ PLAs, PALs, and ROMs are also called SPLDs –

Simple Programmable Logic Devices

¡ SPLDs must be programmed so that the switches

are in the correct places

n CAD tools are usually used to do this

¡ A fuse map is created by the CAD tool and then that map is

downloaded to the device via a special programming unit

n There are two basic types of programming techniques

¡ Removable sockets on a PCB

¡ In system programming (ISP) on a PCB

n This approach is not very common for PLAs and PALs but

it is quite common for more complex PLDs

PDF created with pdfFactory Pro trial version www.pdffactory.com

n An SPLD Programming Unit

¡ The SPLD is removed from the PCB, placed into the

unit and programmed there

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Removable SPLD Socket Package

¡ PLCC (plastic-leaded chip carrier)

PLCC socket soldered to

the PCB

d

boar

it

circu

d

r i nte

P

PDF created with pdfFactory Pro trial version www.pdffactory.com

n In System Programming (ISP)

¡ Used when the SPLD cannot be removed from the

PCB

¡ A special cable and PCB connection are required to

program the SPLD from an attached computer

¡ Very common approach to programming more

complex PLDs like CPLDs, FPGAs, etc.

PDF created with pdfFactory Pro trial version www.pdffactory.com

n CPLD

¡ Complex Programmable Logic Devices (CPLD)

¡ SPLDs (PLA, PAL) are limited in size due to the

small number of input and output pins and the limited

number of product terms

n Combined number of inputs + outputs < 32 or so

¡ CPLDs contain multiple circuit blocks on a single

chip

n Each block is like a PAL: PAL-like block

n Connections are provided between PAL-like blocks via an

interconnection network that is programmable

n Each block is connected to an I/O block as well

PDF created with pdfFactory Pro trial version www.pdffactory.com

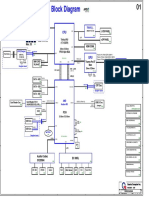

n Structure of a CPLD

I/O block

I/O block

PAL-like PAL-like

block block

Interconnection wires

I/O block

I/O block

PAL-like PAL-like

block block

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Internal Structure of a PAL-like Block

¡ Includes macrocells

n Usually about 16 each

PAL-like block

¡ Fixed OR planes

n OR gates have fan-in

between 5-20 PAL-like block

DQ

¡ XOR gates provide

negation ability DQ

n XOR has a control

DQ

input

PDF created with pdfFactory Pro trial version www.pdffactory.com

n More on PAL-like Blocks

¡ CPLD pins are provided to control XOR, MUX, and

tri-state gates

¡ When tri-state gate is disabled, the corresponding

output pin can be used as an input pin

n The associated PAL-like block is then useless

¡ The AND plane and interconnection network are

programmable

¡ Commercial CPLDs have between 2-100 PAL-like

blocks

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Programming a CPLD

¡ CPLDs have many pins – large ones have > 200

n Removal of CPLD from a PCB is difficult without breaking

the pins

n Use ISP (in system programming) to program the CPLD

n JTAG (Joint Test Action Group) port used to connect the

CPLD to a computer

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Example CPLD

¡ Use a CPLD to implement the function

n f = x1x3x6' + x1x4x5x6' + x2x3x7 + x2x4x5x7

(from interconnection wires)

x1 x2 x3 x4 x5 x6 x7 unused

PAL-like block

0 1

0

f

D Q

PDF created with pdfFactory Pro trial version www.pdffactory.com

n FPGA

¡ SPLDs and CPLDs are relatively small and useful for

simple logic devices

n Up to about 20000 gates

¡ Field Programmable Gate Arrays (FPGA) can handle

larger circuits

n No AND/OR planes

n Provide logic blocks, I/O blocks, and interconnection wires

and switches

n Logic blocks provide functionality

n Interconnection switches allow logic blocks to be connected

to each other and to the I/O pins

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Structure of an FPGA

I/O block

interconnection

switch

I/O block

I/O block

logic block

I/O block

PDF created with pdfFactory Pro trial version www.pdffactory.com

n LUTs

¡ Logic blocks are implemented using a lookup table

(LUT)

n Small number of inputs, one output

n Contains storage cells that can be loaded with the desired

values

n A 2 input LUT uses 3 MUXes

to implement any desired function x1

of 2 variables 0/1

¡ Shannon's expansion at work!

0/1

f

0/1

0/1

x2

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Example 2 Input LUT

x1 x2 f

0 0 1 f = x1'x2' + x1x2, or using Shannon's expansion:

0 1 0

1 0 0

1 1 1

x1

1

0

f

0

1

x2

PDF created with pdfFactory Pro trial version www.pdffactory.com

n 3 Input LUT

¡ 7 2x1 MUXes and x1

8 storage cells are x2

required 0/1

0/1

¡ Commercial LUTs have 0/1

4-5 inputs, and 16-32

0/1

storage cells f

0/1

0/1

0/1

0/1

x3

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Programming an FPGA

¡ ISP method is used

¡ LUTs contain volatile storage cells

n None of the other PLD technologies are volatile

n FPGA storage cells are loaded via a PROM when power is

first applied

¡ The UP2 Education Board by Altera contains a

JTAG port, a MAX 7000 CPLD, and a FLEX 10K

FPGA

n The MAX 7000 CPLD chip is EPM7128SLC84-7

n EPM7 à MAX 7000 family; 128 macrocells; LC84 à 84 pin

PLCC package; 7 à speed grade

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Example FPGA

¡ Use an FPGA with 2 input LUTS to implement the

function f = x1x2 + x2'x3

x3 f

n f1 = x1x2

n f2 = x2'x3 x1

n f = f1 + f2 x1 0 x2 0

0 f1 1 f2

0 0

x2 x2 x3

1 0

f1 0

1 f

1

f2

1

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Another Example FPGA

¡ Use an FPGA with 2 input LUTS to implement the

function f = x1x3x6' + x1x4x5x6' + x2x3x7 + x2x4x5x7

n Fan-in of expression is too large for FPGA (this was simple

to do in a CPLD)

n Factor f to get sub-expressions with max fan-in = 2

¡ f = x1x6'(x3 + x4x5) + x2x7(x3 + x4x5)

= (x1x6' + x2x7)(x3 + x4x5)

n Could use Shannon's expansion instead

¡ Goal is to build expressions out of 2-input LUTs

PDF created with pdfFactory Pro trial version www.pdffactory.com

n FPGA Implementation

¡ f = (x1x6' + x2x7)(x3 + x4x5)

x4 x5 x3 f

x1

x1 0 x4 0 x3 0

0 A 0 C 1 E

x6 x6 1 x5 0 C 1

1

0 1

x2

x2 0 A 0 D 0

0 B 1 D 0 f

x7 x7 0 1

B 1

0

E 1

1

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Custom Chips

¡ PLDs are limited by number of programmable

switches

n Consume space

n Reduce speed

¡ Custom chips are created from scratch

n Expensive à used when high speed is required, volume

sales are expected, and chip size is small but with high

density of gates

n ASICs (Application Specific Integrated Circuits) are custom

chips that use a standard cell layout to reduce design costs

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Standard Cells

¡ Rows of logic gates can be connected by wires in

the routing channels

n Designers (via CAD tools) select prefab gates from a library

and place them in rows

n Interconnections are made by wires in routing channels

¡ Multiple layers may be used to avoid short circuiting

¡ A hard-wired connection between layers is called a via

x1 f2

x2

x3

f1

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Example: Standard Cells

¡ f1 = x1x2 + x1'x2'x3 + x1x3'

¡ f2 = x1x2 + x1'x2'x3 + x1x3

x1 f2

x2

x3

f1

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Sea of Gates Gate Array

¡ A Sea of Gates gate array is just like a standard cell

except all gates are of the same type

n Interconnections are run in channels and use multiple

layers

n Cheaper to manufacture due to regularity

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Example: Sea of Gates

¡ f1 = x2x3' + x1x3

black à bottom

layer channels

red à top layer channels

PDF created with pdfFactory Pro trial version www.pdffactory.com

n Digital Logic Technology Tradeoffs

Full custom

VLSI design

ASICs

Speed / Density /

Complexity / Likely

Market Volume CPLDs

FPGAs

PLDs

Engineering cost / Time to develop

PDF created with pdfFactory Pro trial version www.pdffactory.com

You might also like

- Data Envelopment Analysis: Models and Extensions: Production/Operations ManagementDocument4 pagesData Envelopment Analysis: Models and Extensions: Production/Operations Managementmithunrecdgp100% (2)

- Motor TestingDocument26 pagesMotor TestingGas Gas DucatiNo ratings yet

- FpgaDocument99 pagesFpgaBABU MNo ratings yet

- MQ-4C TritonDocument2 pagesMQ-4C TritonLeakSourceInfoNo ratings yet

- Cswip QuestionDocument3 pagesCswip Questionfasith9534No ratings yet

- Architecture of FPGAs and CPLDS: A TutorialDocument41 pagesArchitecture of FPGAs and CPLDS: A Tutorialgongster100% (5)

- Difference Between Forging and CastingDocument2 pagesDifference Between Forging and CastingMOHAMMAD ALINo ratings yet

- Bridge Inspection ManualDocument539 pagesBridge Inspection ManualماقوريNo ratings yet

- Parking BrakeDocument16 pagesParking BrakeDat100% (1)

- Progrmmable LOGIC DevicesDocument42 pagesProgrmmable LOGIC DevicessujalNo ratings yet

- IE1204 Digital Design F11: Programmable Logic, VHDL For Sequential CircuitsDocument68 pagesIE1204 Digital Design F11: Programmable Logic, VHDL For Sequential CircuitsAhmad AliNo ratings yet

- CPLD BestDocument40 pagesCPLD BestSujoy paulNo ratings yet

- L12 SlidesDocument93 pagesL12 SlidesSujoy paulNo ratings yet

- 3 FPGA DevicesDocument18 pages3 FPGA DevicesSamuel ChimborazoNo ratings yet

- Programmable Logic Devices (PLD) : Dr. Fatma ElfoulyDocument26 pagesProgrammable Logic Devices (PLD) : Dr. Fatma Elfoulybeshoymaherr1No ratings yet

- Fpga 1Document38 pagesFpga 1my mailNo ratings yet

- ECEG-4221-VLSI - Lec - 07 - PLD PAL PLA CPLD FPGA ROMDocument39 pagesECEG-4221-VLSI - Lec - 07 - PLD PAL PLA CPLD FPGA ROMNuhamin BirhanuNo ratings yet

- Fpga Lec 3-4 Logic ImplementationDocument64 pagesFpga Lec 3-4 Logic Implementationvikas310No ratings yet

- ECEN 248 - Introduction To Digital Systems Design (Spring 2008) (Sections: 501, 502, 503, 507)Document21 pagesECEN 248 - Introduction To Digital Systems Design (Spring 2008) (Sections: 501, 502, 503, 507)Vipula RawteNo ratings yet

- Routing ProtocolsDocument189 pagesRouting ProtocolsAnonymous 5ayh2NfJpsNo ratings yet

- Introduction To Programmable Logic DevicesDocument30 pagesIntroduction To Programmable Logic Devicesmanish100% (1)

- Rom PDFDocument32 pagesRom PDFdiptiNo ratings yet

- GF10x/11x Design Ove Erview: Nvidia Conf FidentialDocument56 pagesGF10x/11x Design Ove Erview: Nvidia Conf FidentialnumusNo ratings yet

- Programmable Logic DevicesDocument40 pagesProgrammable Logic DevicesjaigodaraNo ratings yet

- Programmable Logic Devices: Edit By: Zulhelman, ST. MTDocument47 pagesProgrammable Logic Devices: Edit By: Zulhelman, ST. MTShafira LuthfiyahNo ratings yet

- Pla Pal RomDocument33 pagesPla Pal Romvpj_jamesNo ratings yet

- Islamic University of Technology: EEE 4483 Digital Electronics & Pulse TechniquesDocument8 pagesIslamic University of Technology: EEE 4483 Digital Electronics & Pulse TechniquesMUHAMMAD JAWAD CHOWDHURY, 180041228No ratings yet

- Lec 13Document2 pagesLec 13jkmaroNo ratings yet

- Acer Aspire V5-551G 1 Quanta ZRP - RevA1ADocument44 pagesAcer Aspire V5-551G 1 Quanta ZRP - RevA1ATom ArcillaNo ratings yet

- FPGADocument28 pagesFPGAmain2510No ratings yet

- Programmable Logic DevicesDocument40 pagesProgrammable Logic DevicesNishanth NissanNo ratings yet

- BRKACI-2642-Layer 3 OutsDocument100 pagesBRKACI-2642-Layer 3 OutsSandroNo ratings yet

- 3 Intermediate Code GenerationDocument20 pages3 Intermediate Code GenerationAKASH PALNo ratings yet

- ONOS+P4 tutorial (master) - Google 幻灯片 PDFDocument38 pagesONOS+P4 tutorial (master) - Google 幻灯片 PDFcopslockNo ratings yet

- The DSP Primer11: Transposed FIR With Multiplier BlockDocument40 pagesThe DSP Primer11: Transposed FIR With Multiplier Blockksreddy2002No ratings yet

- Manejo Apuntadores en RPGDocument41 pagesManejo Apuntadores en RPGLuis CardenasNo ratings yet

- Programmable Logic Devices 2, TutorialDocument10 pagesProgrammable Logic Devices 2, Tutorialindresh.verma100% (1)

- EG - VHDL - AlteraDocument144 pagesEG - VHDL - AlteraChouabna AbderraoufNo ratings yet

- MMS 2017 - Content Distribution TroubleshootingDocument42 pagesMMS 2017 - Content Distribution TroubleshootingVenkatesh KonadaNo ratings yet

- P522 - AFDX/ARINC-664 Interface PMC: WWW - Men.de/products/p522Document4 pagesP522 - AFDX/ARINC-664 Interface PMC: WWW - Men.de/products/p522vijaykumar ponugotiNo ratings yet

- Programmable Logic ArrayDocument22 pagesProgrammable Logic ArrayxcNo ratings yet

- 15.6" ZRP Block Diagram: Memory DownDocument47 pages15.6" ZRP Block Diagram: Memory DownMihohohoNo ratings yet

- Lec 05Document13 pagesLec 05jyothibellary4233No ratings yet

- Alternate I-O SourcesDocument13 pagesAlternate I-O SourcesBsvNo ratings yet

- Introduction To Cmos Vlsi Design: Logical EffortDocument47 pagesIntroduction To Cmos Vlsi Design: Logical EffortRakhi BherwaniNo ratings yet

- Context: Reliable Communication Over Packet Erasure NetworksDocument34 pagesContext: Reliable Communication Over Packet Erasure Networksnick_csdNo ratings yet

- F 22 Depron PDFDocument2 pagesF 22 Depron PDFWalterNo ratings yet

- TCP-IP Cheat SheetDocument2 pagesTCP-IP Cheat Sheettwo.face.dave.1235No ratings yet

- Field Programmable Logic Array PDFDocument2 pagesField Programmable Logic Array PDFRachelNo ratings yet

- Chapter 3 - Combinational Logic DesignDocument17 pagesChapter 3 - Combinational Logic DesignMuhammad AzeemNo ratings yet

- Kartikmohta Com Tech ParallelportDocument9 pagesKartikmohta Com Tech ParallelportMike ThomsonNo ratings yet

- RSLinx Classic Comparison PDFDocument1 pageRSLinx Classic Comparison PDFIvan LpzNo ratings yet

- Assembler 1 PDFDocument169 pagesAssembler 1 PDFsanjuzebraNo ratings yet

- LEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingFrom EverandLEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingNo ratings yet

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- Python for Signal Processing: Featuring IPython NotebooksFrom EverandPython for Signal Processing: Featuring IPython NotebooksRating: 5 out of 5 stars5/5 (1)

- Fedora 9 and Red Hat Enterprise Linux BibleFrom EverandFedora 9 and Red Hat Enterprise Linux BibleRating: 2.5 out of 5 stars2.5/5 (1)

- LPC 2148 UserDocument348 pagesLPC 2148 UserpavankrishnatNo ratings yet

- 1 Introducing Embedded Systems and The MicrocontrollersDocument23 pages1 Introducing Embedded Systems and The Microcontrollersनिमँलसिंह राउलजीNo ratings yet

- 0 ArchitectureDocument22 pages0 Architectureनिमँलसिंह राउलजीNo ratings yet

- By Anita BhattDocument51 pagesBy Anita Bhattनिमँलसिंह राउलजीNo ratings yet

- El402: Embedded System Design CREDITS 5 (L 3, T 0, P 2)Document2 pagesEl402: Embedded System Design CREDITS 5 (L 3, T 0, P 2)निमँलसिंह राउलजीNo ratings yet

- 2 - Notice For Mid Sem Exam (Online)Document1 page2 - Notice For Mid Sem Exam (Online)निमँलसिंह राउलजीNo ratings yet

- 02 ARM ArchitectureDocument43 pages02 ARM Architectureapi-3726520100% (1)

- Laplace Formula PDFDocument2 pagesLaplace Formula PDFनिमँलसिंह राउलजीNo ratings yet

- Dcom VivaDocument1 pageDcom Vivaनिमँलसिंह राउलजीNo ratings yet

- Simulation of Horn Antenna Using HFSS: January 2005Document10 pagesSimulation of Horn Antenna Using HFSS: January 2005निमँलसिंह राउलजीNo ratings yet

- ENGINEERINGDocument2 pagesENGINEERINGनिमँलसिंह राउलजीNo ratings yet

- Syallabus AA SSRDocument1 pageSyallabus AA SSRaditya bhandakkarNo ratings yet

- Department of Electronics Engineering: Sub Name: Guided Research and ReadingDocument13 pagesDepartment of Electronics Engineering: Sub Name: Guided Research and Readingनिमँलसिंह राउलजीNo ratings yet

- Vachnamrut Yuvano MateDocument68 pagesVachnamrut Yuvano Mateनिमँलसिंह राउलजीNo ratings yet

- Night TechnologyDocument7 pagesNight Technologyनिमँलसिंह राउलजीNo ratings yet

- CPP ReportDocument5 pagesCPP ReportSujay Hazra100% (1)

- General Sir John Kotelawala Defence University: Application For A Detailed Degree Certificate/TranscriptDocument3 pagesGeneral Sir John Kotelawala Defence University: Application For A Detailed Degree Certificate/TranscriptNatasha de SilvaNo ratings yet

- Octagonal Blender PDFDocument4 pagesOctagonal Blender PDFMohsinShaikhNo ratings yet

- Automatic Room Light Controller With Visitor Counter-1Document2 pagesAutomatic Room Light Controller With Visitor Counter-1Amitosh MishraNo ratings yet

- DocumentationDocument131 pagesDocumentationm_adnane_dz3184No ratings yet

- Performance-Based Seismic Design of Rocking Shallow Foundations in Cohesive SoilDocument14 pagesPerformance-Based Seismic Design of Rocking Shallow Foundations in Cohesive SoilSong FendaNo ratings yet

- WoodwardDocument5 pagesWoodwardMuhammad UsmanNo ratings yet

- Harsh SukhramaniDocument6 pagesHarsh SukhramaniHarsh SukhramaniNo ratings yet

- 5950 Part 1-1990Document120 pages5950 Part 1-1990José Miguel100% (1)

- Operation Manual Transas M-2Document62 pagesOperation Manual Transas M-2Дмитрий ПеснякNo ratings yet

- WG1AR5 Chapter08 FINAL PDFDocument82 pagesWG1AR5 Chapter08 FINAL PDFMariel YarrodNo ratings yet

- C SB453H8A Sanyo 5.5TR CompressorDocument14 pagesC SB453H8A Sanyo 5.5TR CompressorHarsh Vani AroraNo ratings yet

- Qus Mod 4.2 PCBDocument14 pagesQus Mod 4.2 PCBJagbir SinghNo ratings yet

- Boeing Fire AERO - 2011 - Q2 - Article3Document10 pagesBoeing Fire AERO - 2011 - Q2 - Article3Braulio GomesNo ratings yet

- Weidmuller HazLoc Catalog 2014 LIT1315EDocument12 pagesWeidmuller HazLoc Catalog 2014 LIT1315Evaseem shaikNo ratings yet

- Is 2571-1970Document27 pagesIs 2571-1970Deboline MitraNo ratings yet

- 2016 GME Steel ProductsDocument16 pages2016 GME Steel ProductsMarco Dos Santos NevesNo ratings yet

- Quick Reference Guide OptiPoint 500 FamilyDocument92 pagesQuick Reference Guide OptiPoint 500 FamilyAlvaro ManjarresNo ratings yet

- Ferroelectric RAM FRAM Seminar Report1Document20 pagesFerroelectric RAM FRAM Seminar Report1Gaurav ReddyNo ratings yet

- Recovery of Spent CatalystDocument4 pagesRecovery of Spent CatalystUtsav PatelNo ratings yet

- Saskatchewan Drivers HandbookDocument175 pagesSaskatchewan Drivers HandbookdrivershandbooksNo ratings yet

- Z4 Multi-Function Button Retrofit KitDocument12 pagesZ4 Multi-Function Button Retrofit KitgioioioiNo ratings yet