Professional Documents

Culture Documents

Chapter 7 Registers and Register Transfer

Uploaded by

Farid ChaparroOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter 7 Registers and Register Transfer

Uploaded by

Farid ChaparroCopyright:

Available Formats

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R.

Kime Page 1/21

Chapter 7 Registers and Register Transfer

Outline: - More structure, with multiple stages or cells that are identical or

close to identical circuits are considered.

- Registers are particular useful for storing information during the

processing of data.

- Counters assist us in sequencing the processing.

- Register transfer notation (microoperations)

7-1) Registers and Load Enable

4-Bit Register

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 2/21

- Register with Parallel Load

4-Bit Register with Parallel Load

7-2) Registers Transfers

Digital systems are designed using a modular, hierarchical

approach. In most digital system designs, we partition the system into two

types of modules:

- a datapath: A datapath consists of processing logic and a collection

of registers that performs data processing

- a control unit: A control unit is made up of logic that determines the

sequence of data-processing operations performed by the datapath

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 3/21

The movement of the data stored in registers and the processing

performed on the data are referred to as register transfer operations.

The register transfer operations of digital systems are specified by the

following three basic components:

1. the set of registers in the system

2. the operations that are performed on the data stored in the

registers, and

3. The control that supervised the sequence of operations in the

system.

The elementary operations performed on the data stored in registers

are called microoperations. (Ex: load, count, add, subtract, shift, etc.) A

counter with parallel load is able to perform two microoperations: increment

and load.

Interaction between Datapath and Control Unit

7-3) Registers Transfers Operations

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 4/21

K1 : R 2 ← R1

Transfer from R1 to R2 when K1 = 1

K 2 : R 2 ← R1, R1 ← R 2 ; Exchange

7-4) A Note for VHDL and Verilog Users

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 5/21

7-5) Microoperations

Microoperation is an elementary operation performed on data stored in

registers or memory.

- Transfer Microoperations

- Arithmetic Microoperations

X K1 : R1 ← R1 + R 2

XK1 : R1 ← R1 + R 2 + 1

Note: (

X K1 + XK1 = X + X K1 = K1 )

Implementation of Add and Subtract Microoperations

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 6/21

- Logic Microoperations

- The AND microoperations can be used for clearing one or more bits

in a register to 0

10101101 10101011 R1 (data)

00000000 10101011 R2 (mask)

00000000 10101011 R1 ← R1 ∧ R 2

- The OR microoperations is used to set one or more bits in a

register.

10101101 10101011 R1 (data)

11111111 10101011 R2 (mask)

11111111 10101011 R1 ← R1 ∨ R 2

- The XOR microoperations can be used to complement one or more

bits in a register.

10101101 10101011 R1 (data)

11111111 00000000 R2 (mask)

01010010 10101011 R1 ← R1 ⊕ R 2

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 7/21

- Shift Microoperations

7-6) Microoperations on a Single Register

- Multiplexer-Based Transfers

If (K = 1) then (R0 ← R1) else if (K

1 2 = 1) then (R0 ← R 2)

K1 : R 0 ← R1

K1 K 2 : R 0 ← R 2

Use of Multiplexers to Select between Two Registers

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 8/21

Generalization of Multiplexer Selection for n Sources

- Shift Registers

4-Bit Shift Register

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 9/21

Shift Register with Parallel Load

Shift : Q ← slQ

Shift ⋅ Load : Q ← D

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 10/21

- Bidirectional Shift Register

Bidirectional Shift Register with Parallel Load

S1 ⋅ S 0 : Q ← slQ

S1 ⋅ S 0 : Q ← srQ

S1 ⋅ S 0 : Q ← D

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 11/21

- Ripple Counter

4-Bit Ripple Counter

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 12/21

- Synchronous Binary Counter

4-Bit Synchronous Binary Counter

- Serial and Parallel Counters

- Up-Down Binary Counters

A 4-bit up-down binary counter

D A0 = Q0 ⊕ EN

D A1 = Q1 ⊕ ((Q0 ⋅ S + Q0 ⋅ S ) ⋅ EN )

D A 2 = Q2 ⊕ ((Q0 ⋅ Q1 ⋅ S + Q0 ⋅ Q1 ⋅ S ) ⋅ EN )

D A3 = Q3 ⊕ ((Q0 ⋅ Q1 ⋅ Q2 ⋅ S + Q0 ⋅ Q1 ⋅ Q2 ⋅ S ) ⋅ EN )

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 13/21

- Binary Counters with Parallel Load

4-Bit Binary Counters with Parallel Load

- Other Counters

- BCD Counter

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 14/21

- Arbitrary Count sequence

Counter with Arbitrary Count

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 15/21

7-7) Register Cell Design

Example: [7-1] Register Cell Design

Register A is to implement the following register transfer

AND: A ← A ∧ B

EXOR: A ← A ⊕ B

OR: A ← A ∨ B

( )

Di = A(t + 1) = AND ⋅ Ai ⋅ Bi + EXOR ⋅ Ai Bi + Ai Bi + OR ⋅ ( Ai + Bi ) + AND ⋅ EXOR ⋅ OR ⋅ Ai

Logic Diagram – Register Cell Design

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 16/21

Example: [7-2] Register Cell Design

Register A is to implement the following register transfer

SHL: A ← slA

EXOR: A ← A ⊕ B

ADD: A ← A + B

Logic Diagram – Register Cell Design

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 17/21

7-8) Multiplexer and Bus-Based Transfers for Multiple Registers

- Three Stage Bus: In a multiplexer, a large number of sources means a

high fan-in OR, which requires multiple levels of OR gates, introducing

more logic and increasing delay. In contrast, three-state buffers provide

a practical way to construct fast buses with many sources.

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 18/21

- Memory Transfer

Read: DR ← M [ AR]

Write: M [ AR] ← DR

7-9) Serial Transfer and Microoperations

Serial Transfer

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 19/21

- Serial Addition

7-10) HDL Representation for Shift Registers and Counters – VHDL

Example: [7-3] VHDL for a 4-Bit Shift Register

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 20/21

Example: [7-4] VHDL for a 4-Bit Counter

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

Ch.07 Ref: Logic and Computer Design Fundamental By M. Morris Mano, Charles R. Kime Page 21/21

7-11) HDL Representation for Shift Registers and Counters - Verilog

Example: [7-5] Verilog for a 4-Bit Shift Register

Example: [7-6] Verilog for a 4-Bit Counter

June 04 Lecture note for ENE 431 By Dejwoot KHAWPARISUTH

You might also like

- Register Transfer and Micro OperationsDocument49 pagesRegister Transfer and Micro OperationsabhishekNo ratings yet

- Computer System Architecture: (Third Edition)Document25 pagesComputer System Architecture: (Third Edition)Ram SethuNo ratings yet

- Decoders Explained: Types, Applications and Designing Logic CircuitsDocument25 pagesDecoders Explained: Types, Applications and Designing Logic CircuitsmohitNo ratings yet

- Chapter01 Digital Systems and Binary NumbersDocument33 pagesChapter01 Digital Systems and Binary Numbersökkeş kurtNo ratings yet

- Unit 2Document44 pagesUnit 2nagpal3No ratings yet

- Morris Mano ch01Document25 pagesMorris Mano ch01Praveen DhawanNo ratings yet

- Chapter5-The Memory SystemDocument78 pagesChapter5-The Memory SystemAvirup RayNo ratings yet

- Chapter 8 - PipeliningDocument38 pagesChapter 8 - Pipeliningnagpal3No ratings yet

- Pipeline and Vector ProcessingDocument37 pagesPipeline and Vector ProcessingGiri Saranu83% (12)

- Application of S-R Latch - Digital Logic & DesignDocument13 pagesApplication of S-R Latch - Digital Logic & DesignskyviperNo ratings yet

- Computer Organization and ArchitectureDocument21 pagesComputer Organization and ArchitectureHebziba Jeba Rani S100% (1)

- CH - 1 Digital SystemsDocument44 pagesCH - 1 Digital SystemsRaquel BarretoNo ratings yet

- Register Transfer Language Register Transfer Bus and Memory Transfers Logic Micro-Operations Shift Micro-Operations Arithmetic Logic Shift UnitDocument11 pagesRegister Transfer Language Register Transfer Bus and Memory Transfers Logic Micro-Operations Shift Micro-Operations Arithmetic Logic Shift UnitYash Gupta MauryaNo ratings yet

- COA Course Overview & Technology TrendsDocument55 pagesCOA Course Overview & Technology TrendsSanam KhanNo ratings yet

- MultiplexersDocument20 pagesMultiplexersسید یاور امام کاظمیNo ratings yet

- Ripple Carry and Carry Lookahead Adders: 1 ObjectivesDocument8 pagesRipple Carry and Carry Lookahead Adders: 1 ObjectivesYasser RaoufNo ratings yet

- Single Source Shortest Path Unit-3Document43 pagesSingle Source Shortest Path Unit-3Phani Kumar100% (1)

- Multilevel view of a machine's architectureDocument3 pagesMultilevel view of a machine's architectureVarsha Rani0% (1)

- Exercise 7 - Register Transfer Level (RTL) LogicDocument4 pagesExercise 7 - Register Transfer Level (RTL) LogicdureNo ratings yet

- Verilog - ManoDocument43 pagesVerilog - ManoMohammod Ahad ArianNo ratings yet

- Interfacing ADC With 8051Document15 pagesInterfacing ADC With 8051Pavan Kumar N100% (1)

- Module 4 - Number Systems and Boolean AlgebraDocument8 pagesModule 4 - Number Systems and Boolean AlgebraSuyog ChavanNo ratings yet

- Asynchronous Data Transfer Modes of Transfer Priority Interrupt Direct Memory Access Input-Output Processor Serial CommunicationDocument49 pagesAsynchronous Data Transfer Modes of Transfer Priority Interrupt Direct Memory Access Input-Output Processor Serial CommunicationGeorgian ChailNo ratings yet

- 8086 Microprocessor Lab 1Document7 pages8086 Microprocessor Lab 1Tyler BarneyNo ratings yet

- S.No Topics Lec: Advanced Computer Network ETCS-401Document4 pagesS.No Topics Lec: Advanced Computer Network ETCS-401Anshul MittalNo ratings yet

- Digital System Design Using Verilog December 2011Document1 pageDigital System Design Using Verilog December 2011Vinayaka HmNo ratings yet

- Module 1 PDFDocument33 pagesModule 1 PDFKetan Janai100% (1)

- Chapter 3 Boolean Anlgebra and Logi GatesDocument59 pagesChapter 3 Boolean Anlgebra and Logi Gatesworld channelNo ratings yet

- DAC InterfacingDocument6 pagesDAC InterfacingSumeet SainiNo ratings yet

- Stack and SUBROUTINES Bindu AgarwallaDocument15 pagesStack and SUBROUTINES Bindu AgarwallaNobodyNo ratings yet

- Unit 5 - A CASE STUDY - Using Pic MicrocontrollerDocument33 pagesUnit 5 - A CASE STUDY - Using Pic MicrocontrollerPoonthalirNo ratings yet

- Sample Exam QuestionsDocument9 pagesSample Exam Questionssomeguyinoz100% (1)

- Instruction PipelineDocument27 pagesInstruction PipelineEswin AngelNo ratings yet

- Digital System Objective QuestionsDocument17 pagesDigital System Objective QuestionsRanjeet pratap singh bhadoriyaNo ratings yet

- Csa Mod 2Document28 pagesCsa Mod 2anusarat100% (1)

- Chapter-4A (Transforming Data Into Information)Document38 pagesChapter-4A (Transforming Data Into Information)api-3774277No ratings yet

- Basic Computer OrganizationDocument20 pagesBasic Computer OrganizationMag Creation100% (1)

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationDocument13 pagesUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaNo ratings yet

- Bitwise OperatorsDocument4 pagesBitwise OperatorsslspaNo ratings yet

- CC442 Chapter 8 Asynchronous CounterDocument19 pagesCC442 Chapter 8 Asynchronous CounterMuhamdA.BadawyNo ratings yet

- MSI Logic Circuits GuideDocument17 pagesMSI Logic Circuits GuideAnonymous AyCl4LNo ratings yet

- Part III 8051 General PgmsDocument7 pagesPart III 8051 General PgmsHEMANo ratings yet

- Final Digital Logic Design PPTDocument140 pagesFinal Digital Logic Design PPTGHULAM MOHIUDDINNo ratings yet

- Cs8351 Digital Principles and System DesignDocument161 pagesCs8351 Digital Principles and System DesignGanesamoorthy BNo ratings yet

- Computer Architecture Midterm1 CmuDocument30 pagesComputer Architecture Midterm1 CmuÖzgürCemBirlerNo ratings yet

- Parallel Computing Architectures & ProgrammingDocument1 pageParallel Computing Architectures & ProgrammingRohith RajNo ratings yet

- Combinational Circuit Adder, Subtractor and MultiplexerDocument24 pagesCombinational Circuit Adder, Subtractor and Multiplexerram5nath-3100% (1)

- Computer Organization NotesDocument115 pagesComputer Organization NotesEbbaqhbqNo ratings yet

- DSP Processor FundamentalsDocument58 pagesDSP Processor FundamentalsSayee KrishnaNo ratings yet

- 8,16,32 Floating Point Processing in ARMDocument25 pages8,16,32 Floating Point Processing in ARMOMKAR BHILARE100% (1)

- Computer Network SyllabusDocument4 pagesComputer Network SyllabusSanjay ShresthaNo ratings yet

- Digital Logic Design TutorialDocument10 pagesDigital Logic Design TutorialShadab IrfanNo ratings yet

- COA Unit 1Document33 pagesCOA Unit 1Keshav NaganathanNo ratings yet

- Lecture2 ThirdmicroprocessorcDocument22 pagesLecture2 Thirdmicroprocessorcxkurt358792100% (2)

- Unisa Digital Logic NotesDocument8 pagesUnisa Digital Logic NotesmmasalekNo ratings yet

- Vlsi TechnologyDocument64 pagesVlsi TechnologySougata GhoshNo ratings yet

- Stucor CS3351-GKDocument269 pagesStucor CS3351-GKNightdive StudiosNo ratings yet

- Register Transfers and DatapathsDocument40 pagesRegister Transfers and DatapathsaravinNo ratings yet

- COA Unit-1 FinalDocument34 pagesCOA Unit-1 Finalpriyanka60% (5)

- Diagrama de Flujo No-PipelinedDocument1 pageDiagrama de Flujo No-PipelinedFarid ChaparroNo ratings yet

- Foreign Language III - SyllabusDocument5 pagesForeign Language III - SyllabusFarid ChaparroNo ratings yet

- PIC16F84A DataSheetDocument88 pagesPIC16F84A DataSheetEmanueleNo ratings yet

- CV For ExamDocument1 pageCV For ExamFarid ChaparroNo ratings yet

- Washington State Cloud Readiness ReportDocument27 pagesWashington State Cloud Readiness Reportrajutamang2021.btNo ratings yet

- SubqueryDocument4 pagesSubqueryDGreatWannieNo ratings yet

- 1z0-982 Exam Questions: Oracle Enterprise Planning and Budgeting Cloud Service 2017 Implementation EssentialsDocument51 pages1z0-982 Exam Questions: Oracle Enterprise Planning and Budgeting Cloud Service 2017 Implementation Essentialssuman dNo ratings yet

- Raster Data Model: A Seminor OnDocument42 pagesRaster Data Model: A Seminor OnAmber Joy TingeyNo ratings yet

- Selenium WebDriver NotesDocument12 pagesSelenium WebDriver Notesvvenkat123No ratings yet

- On Passivity, Reinforcement Learning and Higher-Order Learning in Multi-Agent Finite GamesDocument14 pagesOn Passivity, Reinforcement Learning and Higher-Order Learning in Multi-Agent Finite Gameshareem7bilalNo ratings yet

- NBCPDocument17 pagesNBCPArch. Jan EchiverriNo ratings yet

- Identity and Access Management SuiteDocument2 pagesIdentity and Access Management SuiteVladan DabovicNo ratings yet

- MODBUS Parameter Specifications V5.00Document84 pagesMODBUS Parameter Specifications V5.00g6653568No ratings yet

- Evaluating Gearbox Concepts Efficiently: 1. AbstractDocument9 pagesEvaluating Gearbox Concepts Efficiently: 1. AbstractSajad FilabiNo ratings yet

- Instant Download Chez Nous Branche Sur Le Monde Francophone Canadian 3rd Edition Valdman Test Bank PDF Full ChapterDocument33 pagesInstant Download Chez Nous Branche Sur Le Monde Francophone Canadian 3rd Edition Valdman Test Bank PDF Full ChapterAlexanderSanchezpnyx100% (7)

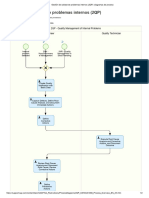

- Gestión de Calidad de Problemas Internos (2QP) - Diagramas de ProcesoDocument2 pagesGestión de Calidad de Problemas Internos (2QP) - Diagramas de ProcesoDiego CincottaNo ratings yet

- Best Buy China Case RevisedDocument19 pagesBest Buy China Case RevisedKuldeep BarwalNo ratings yet

- Document-SAP EWM For Fashion 1.0: 1.general IntroductionDocument3 pagesDocument-SAP EWM For Fashion 1.0: 1.general IntroductionAnonymous u3PhTjWZRNo ratings yet

- File Check LogDocument4,062 pagesFile Check LogNguyễnThạchNo ratings yet

- IV Cse-D Seminar FormatDocument8 pagesIV Cse-D Seminar FormatPenchalaiah NarasapuramNo ratings yet

- Assignment On Business AnalyticsDocument6 pagesAssignment On Business AnalyticsPreet BhatiaNo ratings yet

- Azure COst ManagementDocument946 pagesAzure COst ManagementHasan ShahriarNo ratings yet

- Data TemplateDocument30 pagesData TemplateAnonymous 8jfdgHiNo ratings yet

- Journey Optimizer Architecture DiagramDocument25 pagesJourney Optimizer Architecture DiagramDavid CastilloNo ratings yet

- Curriculume Vitae - DinalDocument1 pageCurriculume Vitae - DinaldainelNo ratings yet

- Microstrip LineDocument2 pagesMicrostrip LineMedo KassabNo ratings yet

- ABB-Welcome: User ManualDocument58 pagesABB-Welcome: User ManualjackNo ratings yet

- Anti-Theft System Using I2C MEMS Sensor and ZigBeeDocument1 pageAnti-Theft System Using I2C MEMS Sensor and ZigBeeSomu VenkatNo ratings yet

- Satchwell Product CatalogDocument36 pagesSatchwell Product CatalogSergio HitcarNo ratings yet

- Linuxintro LEFE 4.31Document304 pagesLinuxintro LEFE 4.31wcastro8182No ratings yet

- TAFJ-AS JBossInstall v7 EAPDocument34 pagesTAFJ-AS JBossInstall v7 EAPEmmanuel Uchenna ChukwuNo ratings yet

- Serta MotionPerfect Owner Manual V001 10.16.18 V2Document36 pagesSerta MotionPerfect Owner Manual V001 10.16.18 V2i800621No ratings yet

- MIP S4 Section BDocument3 pagesMIP S4 Section Bkabli ilyassNo ratings yet

- Exadata Patching Recipe V1.0 - NetsoftmateDocument48 pagesExadata Patching Recipe V1.0 - Netsoftmateraghu12421No ratings yet