Professional Documents

Culture Documents

Lesson Plan

Uploaded by

gokulCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lesson Plan

Uploaded by

gokulCopyright:

Available Formats

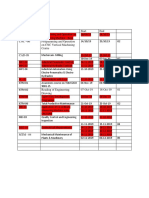

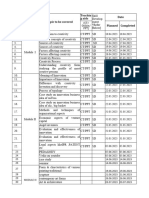

ECE2003 – DIGITAL LOGIC DESIGN

FALL 2019-20

Lesson Plan

S. No. Lecture Date Lecture Topic

1 11/07/2019 Brief review of Number Systems

2 16/07/2019 Digital Logic Gates and its electrical characteristics

3 18/07/2019 Review of RTL, DTL, TTL, ECL

4 23/07/2019 CMOS families

5 25/07/2019 Basic Definitions, Axiomatic Definition of Boolean Algebra

6 27/07/2019 Basic Theorems and Properties of Boolean Algebra

7 30/07/2019 Boolean Functions, Canonical and Standard Forms

8 01/08/2019 The Map Method - K-map

9 06/08/2019 Product of Sums simplifications

10 08/08/2019 Sum of Products Simplification

11 13/08/2019 NAND and NOR Implementation

CAT-1

12 27/08/2019 Design Procedure, Binary Adder-Subtractor

13 29/08/2019 Parallel Adder, Binary Multiplier

14 3/09/2019 MagnitudeComparator-4 bit, Parity generator and checker.

15 10/09/2019 Decoders, Encoders, Multiplexers, De-multiplexer,

16 12/09/2019 Application of Mux and Demux

17 17/09/2019 Lexical Conventions, Ports and Modules, Operators

18 19/09/2019 Gate Level Modeling & Data Flow Modeling

19 24/09/2019 Behavioral level Modeling, Testbench

20 26/09/2019 Latches, Flip-Flops-SR, D, JK & T

CAT-2

21 8/10/2019 Shift Registers-SISO, SIPO, PISO,PIPO

22 10/10/2019 Design of synchronous sequential circuits- State table and state

diagrams

23 15/10/2019 Design of counters-Modulo-n

24 17/10/2019 Johnson, Ring, Up/Down

25 22/10/2019 Design of Mealy and Moore FSM

26 24/10/2019 Sequence detection

27 29/10/2019 Modeling of Combinational Circuits using Verilog HDL

28 31/10/2019 Modeling of Combinational Circuits using Verilog HDL

29 5/11/2019 Modeling of Sequential Logic Circuits using Verilog HDL

30 7/11/2019 Modeling of Sequential Logic Circuits using Verilog HDL

You might also like

- VLSI Design Lesson Plan for ECE DepartmentDocument8 pagesVLSI Design Lesson Plan for ECE DepartmentBasava RajuNo ratings yet

- Electronics & Communication Engineering Department: (Even Semester 2018-19) Lecture PlanDocument5 pagesElectronics & Communication Engineering Department: (Even Semester 2018-19) Lecture PlanVimal ChaudharyNo ratings yet

- MSP430 Lecture Plan Details Microcontroller ArchitectureDocument4 pagesMSP430 Lecture Plan Details Microcontroller ArchitectureVimal ChaudharyNo ratings yet

- Name of The Value Added Courses Date of Introduction CivilDocument8 pagesName of The Value Added Courses Date of Introduction CivilRajesh Kumar PNo ratings yet

- JNTUH Placement ReportDocument2 pagesJNTUH Placement ReportRajendra KrishnaNo ratings yet

- B SCDocument96 pagesB SCMohamedibrahim SNo ratings yet

- NNFL LPDocument4 pagesNNFL LPKrushnasamy SuramaniyanNo ratings yet

- IT6801 NAAC - SOA Lesson Plan - R2013Document4 pagesIT6801 NAAC - SOA Lesson Plan - R2013addssdfaNo ratings yet

- Lesson - CepdeDocument1 pageLesson - Cepdearun aryaNo ratings yet

- CS6703 Regulation-Lesson plan-CS6703-GRID AND CLOUD COMPUTING - 7th SemesterDocument5 pagesCS6703 Regulation-Lesson plan-CS6703-GRID AND CLOUD COMPUTING - 7th SemesteraddssdfaNo ratings yet

- Public Examination Schedule (BPUT)Document2 pagesPublic Examination Schedule (BPUT)ManishNo ratings yet

- JIPMER GIS Substation and Cable Drawing ReleaseDocument8 pagesJIPMER GIS Substation and Cable Drawing ReleasemanishNo ratings yet

- Course Plan (Proposed) : Simulation Mechanism and Simulation Tools Simulation Mechanism and Simulation ToolsDocument2 pagesCourse Plan (Proposed) : Simulation Mechanism and Simulation Tools Simulation Mechanism and Simulation Toolssharma29neeleshNo ratings yet

- Mini Project Presentation1 Final Presentation Parking SensorDocument12 pagesMini Project Presentation1 Final Presentation Parking SensorChethan ReddyNo ratings yet

- Technical Specifications 7+5 ( ('2&.6,' ( (/ (&75,&&217$,1 (5 CRANES) 25:+$5) 12Document365 pagesTechnical Specifications 7+5 ( ('2&.6,' ( (/ (&75,&&217$,1 (5 CRANES) 25:+$5) 12Al-Razzaq Al-WahhabNo ratings yet

- Internal Presentation On ": Department of Computer Science & EngineeringDocument37 pagesInternal Presentation On ": Department of Computer Science & Engineeringanushka bhati80% (5)

- Siemens Aunz Training Timetable 2019 PDFDocument1 pageSiemens Aunz Training Timetable 2019 PDFMubashar AliNo ratings yet

- S.No: LAB Title Date Score Sign 1Document2 pagesS.No: LAB Title Date Score Sign 1Anum MemonNo ratings yet

- QS - Lesson - Plan PDFDocument2 pagesQS - Lesson - Plan PDFrajaanwarNo ratings yet

- October 2019: Short Term Programmes (Contact Mode)Document10 pagesOctober 2019: Short Term Programmes (Contact Mode)Bharati ThakurNo ratings yet

- Estimation Training Schedule: Introduction To Oil & Gas ProductionDocument2 pagesEstimation Training Schedule: Introduction To Oil & Gas ProductionMohammed Azaas SyedNo ratings yet

- B.SC 19 PDFDocument94 pagesB.SC 19 PDFDinesh GdkNo ratings yet

- Service MenuDocument21 pagesService MenuAlexis FloresNo ratings yet

- Computer Graphics: Practical FileDocument2 pagesComputer Graphics: Practical FileLalit KaulNo ratings yet

- Crane tinning line installation reportDocument4 pagesCrane tinning line installation reportirhamciptanarialNo ratings yet

- CS8591 CN Lecture Plan FormatDocument5 pagesCS8591 CN Lecture Plan FormataddssdfaNo ratings yet

- M.E. Applied Electronics Branch:: Controller of ExaminationsDocument54 pagesM.E. Applied Electronics Branch:: Controller of ExaminationsBlessyNo ratings yet

- WSN Edited Unit-2 CHapter-2Document34 pagesWSN Edited Unit-2 CHapter-2himanshu kumarNo ratings yet

- 3.2.2 Consolidated Workshops, Seminars IndexDocument8 pages3.2.2 Consolidated Workshops, Seminars Indexsatya durga prasad kalagantiNo ratings yet

- Vignana Bharathi Institute of Technology: Hyderabad: Department of Electronics and Communication EngineeringDocument2 pagesVignana Bharathi Institute of Technology: Hyderabad: Department of Electronics and Communication Engineeringravikumar rayalaNo ratings yet

- Deliverables February 2019Document2 pagesDeliverables February 2019Anonymous SjKX2mNo ratings yet

- Time Table For Practical Examination of Design Engineering 2B (2160001) Regular Zone 1 - Summer 2019Document17 pagesTime Table For Practical Examination of Design Engineering 2B (2160001) Regular Zone 1 - Summer 2019Akash ThankiNo ratings yet

- Engineering Master Drawing/Document List (MDL)Document23 pagesEngineering Master Drawing/Document List (MDL)Boishal Bikash BaruahNo ratings yet

- (Partial) : Name Roll No. Branch DegreeDocument1 page(Partial) : Name Roll No. Branch DegreeAzim CoolNo ratings yet

- Lab Report: SEMESTER (2020-21)Document2 pagesLab Report: SEMESTER (2020-21)VmosaNo ratings yet

- Deliverables May 2019Document2 pagesDeliverables May 2019Anonymous SjKX2mNo ratings yet

- Actual EngagementSheet-EMD-I - Dr. J Jamnani-AY 2020-21Document2 pagesActual EngagementSheet-EMD-I - Dr. J Jamnani-AY 2020-21Poonam JamnaniNo ratings yet

- H2020 Work ProgrammesDocument3 pagesH2020 Work ProgrammesMiguel TitoNo ratings yet

- StudentGradeHistory 19BCY10038Document4 pagesStudentGradeHistory 19BCY10038Help UsNo ratings yet

- 2019-08 Komtrax UNIMINEX JOIFULLDocument11 pages2019-08 Komtrax UNIMINEX JOIFULLEduin Edgardo Corregidor CastroNo ratings yet

- Broadband Over Power Lines (BPL) Developments and Policy IssuesDocument35 pagesBroadband Over Power Lines (BPL) Developments and Policy IssuesJohn EganNo ratings yet

- Start Date: June 24, 2019 Target End: July 29, 2019Document1 pageStart Date: June 24, 2019 Target End: July 29, 2019DANILO D. ESCOTO JR.No ratings yet

- RUA Seguridad Corp Check Disbursement Report Sep-19Document15 pagesRUA Seguridad Corp Check Disbursement Report Sep-19Nicah CuajaoNo ratings yet

- Mumbai Metro Rail Line 3 UGC-03 BIM Progress ReviewDocument10 pagesMumbai Metro Rail Line 3 UGC-03 BIM Progress ReviewVimal YadavNo ratings yet

- Reference ListDocument7 pagesReference ListsparkCENo ratings yet

- Ugi Syst 330 Naa Rep 226 - C - Door Schedule MKNDocument12 pagesUgi Syst 330 Naa Rep 226 - C - Door Schedule MKNAr Arka Prava BarikNo ratings yet

- Advance Microprocessor Course ScheduleDocument2 pagesAdvance Microprocessor Course ScheduleHaider AlrudainyNo ratings yet

- Vignana Bharathi Institute of Technology: Hyderabad: Department of Electronics and Communication EngineeringDocument2 pagesVignana Bharathi Institute of Technology: Hyderabad: Department of Electronics and Communication Engineeringravikumar rayalaNo ratings yet

- CNC, CAD, Automation Training ScheduleDocument2 pagesCNC, CAD, Automation Training ScheduleMeer Mustafa AliNo ratings yet

- 2-Abstract Template - Main Project - S7 - EEE July - Dec 2019Document4 pages2-Abstract Template - Main Project - S7 - EEE July - Dec 2019Ananthakrishnan SyamkumarNo ratings yet

- VVATSCS012Document2 pagesVVATSCS012shanNo ratings yet

- 8.3 F-02 Master List of Document1Document11 pages8.3 F-02 Master List of Document1Ashish DubeyNo ratings yet

- Lecture 2 - Modelling RequirementsDocument47 pagesLecture 2 - Modelling RequirementsJermyn G EvangelistaNo ratings yet

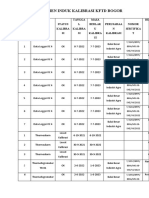

- Dokumen Induk KalibrasiDocument3 pagesDokumen Induk KalibrasiditaNo ratings yet

- Lesson PlanDocument8 pagesLesson PlansreevidyanidhirriasNo ratings yet

- Session Plan: Course Title:TS SDP-3 (JFSD) Course Code:20TS3101AHDocument4 pagesSession Plan: Course Title:TS SDP-3 (JFSD) Course Code:20TS3101AHChaithanya MotupallyNo ratings yet

- Activity Report For July 2020 - Pravin AwalkondeDocument6 pagesActivity Report For July 2020 - Pravin AwalkondePravin AwalkondeNo ratings yet

- KL University: Department of Electronics and Communication Engineering III/IV B. Tech, 6 Semester, 2017-18Document4 pagesKL University: Department of Electronics and Communication Engineering III/IV B. Tech, 6 Semester, 2017-18Naveen Kishore GattimNo ratings yet

- Integration of Demand Response into the Electricity Chain: Challenges, Opportunities, and Smart Grid SolutionsFrom EverandIntegration of Demand Response into the Electricity Chain: Challenges, Opportunities, and Smart Grid SolutionsNo ratings yet

- Handbook on Battery Energy Storage SystemFrom EverandHandbook on Battery Energy Storage SystemRating: 4.5 out of 5 stars4.5/5 (2)

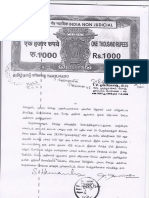

- Scanned by TapscannerDocument3 pagesScanned by TapscannergokulNo ratings yet

- 0 OmnipotenceDocument76 pages0 OmnipotencegokulNo ratings yet

- Module 2Document46 pagesModule 2gokulNo ratings yet

- Revised - Quiz - DA Schedule - VelloreDocument1 pageRevised - Quiz - DA Schedule - VelloregokulNo ratings yet

- DLD Assignment 1Document11 pagesDLD Assignment 1gokulNo ratings yet

- DLD Mod 1Document99 pagesDLD Mod 1Ajay KumarNo ratings yet

- DLD Module-3Document47 pagesDLD Module-3gokulNo ratings yet

- Number SystemsDocument50 pagesNumber SystemsSolomon TekluNo ratings yet

- DLD Assignment - 1Document2 pagesDLD Assignment - 1gokulNo ratings yet

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- DLD Mod 1Document99 pagesDLD Mod 1Ajay KumarNo ratings yet

- Academic Calendar Fall 2019-20Document2 pagesAcademic Calendar Fall 2019-20gokulNo ratings yet

- 4 Kundur Z-TransfProperties HandoutsDocument5 pages4 Kundur Z-TransfProperties HandoutsBittuNo ratings yet

- GloGerl6irgrLb's Gsngg er,lergd.,6b Gesu$$sgenr-:r-_L_gr.onenDocument1 pageGloGerl6irgrLb's Gsngg er,lergd.,6b Gesu$$sgenr-:r-_L_gr.onengokulNo ratings yet