Professional Documents

Culture Documents

Lecture2 PDF

Lecture2 PDF

Uploaded by

Frankie LiuOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture2 PDF

Lecture2 PDF

Uploaded by

Frankie LiuCopyright:

Available Formats

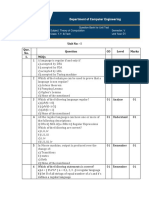

EECS222: Embedded System Modeling Lecture 2

EECS 222:

Embedded System Modeling

Lecture 2

Rainer Dömer

doemer@uci.edu

The Henry Samueli School of Engineering

Electrical Engineering and Computer Science

University of California, Irvine

Lecture 2: Overview

• Introduction to Embedded System Design

– Top-down system design flow

• Models of Computation

• System-Level Description Languages

• Separation of Concerns

– Computation vs. Communication

– Intellectual Property (IP)

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 2

(c) 2019 R. Doemer 1

EECS222: Embedded System Modeling Lecture 2

Top-Down System Design Flow

requirements Product features constraints

Specification

pure functional untimed

model

Architecture

transaction level estimated timing

model

Communication

bus functional timing accurate

model

Implementation

RTL / IS cycle accurate

model

Structure Manufacturing Timing

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 3

Models of Computation

• Computational Model

– Formal, abstract description of a system

– Various degrees of

• supported features

• complexity

• expressive power

• Examples

– Evolution process from FSM to PSM

• Finite State Machine (FSM)

• FSM with Data (FSMD)

• Super-state FSMD

• ...

• Program State Machine (PSM)

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 4

(c) 2019 R. Doemer 2

EECS222: Embedded System Modeling Lecture 2

Models of Computation

• Finite State Machine (FSM)

– Basic model for describing control

– States and state transitions

• FSM = <S, I, O, f, h>

– Two types:

• Mealy-type FSM (input-based)

• Moore-type FSM (state-based)

S1 S2

S3

FSM model

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 5

Models of Computation

• Finite State Machine (FSM)

• Data Flow Graph (DFG)

– Basic model for describing computation

– Directed graph (acyclic)

• Nodes: operations

• Edges: data flow, dependency of operations

Op1 Op2 Op3

Op4

Op5 Op6

DFG model

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 6

(c) 2019 R. Doemer 3

EECS222: Embedded System Modeling Lecture 2

Models of Computation

• Finite State Machine (FSM)

• Data Flow Graph (DFG)

• Finite State Machine with Data (FSMD)

– Combined model for control and computation

• FSMD = FSM + DFG

– Implementation: controller plus data path (RTL processor)

Op1 Op2

Op1 Op2 Op3

S1 S2

Op4

Op1 Op2 S3

Op5 Op6

Op3

FSMD model

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 7

Models of Computation

• Finite State Machine (FSM)

• Data Flow Graph (DFG)

• Finite State Machine with Data (FSMD)

• Super-State FSM with Data (SFSMD)

– FSMD with complex, multi-cycle states

• States described by procedures in a programming language

a = 42;

a = a + b;

b = a * 2;

c = c + d;

for(c=0; c<100; c++)

PS1 PS2 { b = c + a;

if (b < 0)

b = -b;

a = 42; else

while (a<100) b = b + 1;

{ b = b + a; PS3

a = b * 10;

if (b > 50) }

c = c + d;

a = a + c;

} SFSMD model

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 8

(c) 2019 R. Doemer 4

EECS222: Embedded System Modeling Lecture 2

Models of Computation

• Finite State Machine (FSM)

• Data Flow Graph (DFG)

• Finite State Machine with Data (FSMD)

• Super-State FSM with Data (SFSMD)

• Hierarchical Concurrent FSM (HCFSM)

– FSM extended with hierarchy and concurrency

• Multiple FSMs composed hierarchically and in parallel

– Example: Statecharts

S1 S3

HCFSM model S5

S2 S4

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 9

Models of Computation

• Finite State Machine (FSM)

• Data Flow Graph (DFG)

• Finite State Machine with Data (FSMD)

• Super-State FSM with Data (SFSMD)

• Hierarchical Concurrent FSM (HCFSM)

• Program State Machine (PSM)

– HCFSMD plus programming language

...

• States described by procedures a = 42;

in a programming language while (a<100)

{ b = b + a;

– Example: SpecC if (b > 50)

c = c + d;

PS1 PS3 else

PSM model PS5 c = c + e;

PS2 PS4 a = c;

}

...

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 10

(c) 2019 R. Doemer 5

EECS222: Embedded System Modeling Lecture 2

Models of Computation

• State-based Models

– FSM, DFG, FSMD, SFSMD, HCFSM, PSM

– Petri Nets

–…

• Process-based Models

– Processes and threads

– Kahn Process Network (KPN)

– Synchronous Data Flow (SDF)

– …

• Imperative Programming Models

– C/C++, …

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 11

System-Level Description Languages

• Goals and Requirements

– Formality

• Formal syntax and semantics

– Executability

• Validation through simulation

– Synthesizability

• Implementation in HW and/or SW

• Support for IP reuse

– Modularity

• Hierarchical composition

• Separation of concepts

– Completeness

• Support for all concepts found in embedded systems

– Orthogonality

• Orthogonal constructs for orthogonal concepts

– Simplicity

• Minimality

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 12

(c) 2019 R. Doemer 6

EECS222: Embedded System Modeling Lecture 2

System-Level Description Languages

• Requirements supported by existing languages

Behavioral

hierarchy

Structural

hierarchy

Concurrency

Synchronization

Exception

handling

Timing

State

transitions

Composite

data types

not supported partially supported supported

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 13

System-Level Description Languages

• Requirements supported by existing languages

Behavioral

hierarchy

Structural

hierarchy

Concurrency

Synchronization

Exception

handling

Timing

State

transitions

Composite

data types

not supported partially supported supported

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 14

(c) 2019 R. Doemer 7

EECS222: Embedded System Modeling Lecture 2

Evolution of Design Languages

• Timeline of system-level design languages

Past Present Future

Java

1995

6000+ C

?

Computer 1978 SystemC

2002

Languages C++

1986 SpecC

2000

(Boston

SystemVerilog

2005

Computer

VHDL

Museum, 1995)

1987 BlueSpec

2003?

Verilog

1984

Dates indicate year of publication of first reference book

and/or year of invention. Please correct me if I’m wrong!

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 15

System-Level Description Languages

• Examples of Languages in Use Today

– C/C++

• ANSI standard programming languages, software design

• Initially used for system design because of availability, practicality

– SystemC

• IEEE standard 1666-2011 (initially created at UCI, standardized by OSCI)

• C++ library and application programming interface (API)

– SpecC

• SLDL with compiler, based on the ANSI C language standard

• Designed and built at UCI, promoted by SpecC Technology Open Consortium

– Matlab

• Algorithm design, specification and simulation in engineering

– UML

• Unified Modeling Language, graphical software specification and engineering

– SystemVerilog

• Verilog with C extensions

– SDL

• Telecommunication standard by ITU, used in COSMOS

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 16

(c) 2019 R. Doemer 8

EECS222: Embedded System Modeling Lecture 2

System-Level Description Languages

• Examples of Languages in Use Today, Course Coverage

– C/C++

• ANSI standard programming languages, software design

• Initially used for system design because of availability, practicality

SystemC

• IEEE standard 1666-2011 (initially created at UCI, standardized by OSCI)

• C++ library and application programming interface (API)

SpecC

• SLDL with compiler, based on the ANSI C language standard

• Designed and built at UCI, promoted by SpecC Technology Open Consortium

– Matlab

• Algorithm design, specification and simulation in engineering

UML

• Unified Modeling Language, graphical software specification and engineering

– SystemVerilog

• Verilog with C extensions

– SDL

• Telecommunication standard by ITU, used in COSMOS

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 17

Separation of Concerns

• Fundamental Principle in Modeling of Systems

• Clear separation of concerns

– address separate issues independently

• System-Level Description Language (SLDL)

– orthogonal concepts

– orthogonal constructs

• System-level Modeling

– Computation

• encapsulated in modules / behaviors

– Communication

• encapsulated in channels

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 18

(c) 2019 R. Doemer 9

EECS222: Embedded System Modeling Lecture 2

Computation vs. Communication

• Traditional model P1 P2

s1

– Processes and signals s2

s3

– VHDL example: entity P1 […] process […]

s1 <= ’1’;

s2 <= ’1’;

wait until s3’event and s3 = ’1’;

s2 <= ’0’;

xy = x + 2 * y;

s1 <= xy;

s2 <= ’1’;

wait until s3’event and s3 = ’1’;

s1 <= ’0’;

s2 <= ’0’;

[…]

– Mixture of computation and communication

Automatic replacement impossible!

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 19

Computation vs. Communication

C1

• SpecC model B1

v1

B2

– Behaviors and e2

channels e3

– SpecC example: behavior B1 […] channel C1 […]

{ { send (int d)

c.send(1); { v1 = d;

notify e2;

xy = x + 2 * y; wait e3;

}

c.send(xy); […]

}

v1 = 0;

[…]

}

– Separation of computation and communication

Plug-and-play!

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 20

(c) 2019 R. Doemer 10

EECS222: Embedded System Modeling Lecture 2

Computation vs. Communication

• Traditional model P1 P2

s1

s2

s3

– Processes and signals

– Mixture of computation and communication

– Automatic replacement impossible

C1

• SpecC model B1

v1

B2

v2

v3

– Behaviors and channels

– Separation of computation and communication

– Plug-and-play

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 21

Computation vs. Communication

• Protocol Inlining C1

– Specification model B1 B2

v1

– Exploration model v2

v3

• Computation in behaviors

• Communication in channels

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 22

(c) 2019 R. Doemer 11

EECS222: Embedded System Modeling Lecture 2

Computation vs. Communication

• Protocol Inlining C1

– Specification model B1 B2

v1

– Exploration model v2

v3

• Computation in behaviors

• Communication in channels

– Implementation model B1 B2

v1

v2

v3

• Channel disappears

• Communication inlined into behaviors

• Wires exposed

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 23

Computation vs. Communication

• Protocol Inlining

C1

B1 B2 B1 B2

v1 v1

e2 e2

e3 e3

– SpecC example:

behavior B1 […] channel C1 […] behavior B1 […]

{ { send (int d) { v1 = 1;

c.send(1); { v1 = d; notify e2;

notify e2; wait e3;

xy = x + 2 * y; wait e3; xy = x + 2 * y;

} v1 = xy;

c.send(xy); […] notify e2;

} wait e3;

v1 = 0; v1 = 0;

[…] […]

} }

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 24

(c) 2019 R. Doemer 12

EECS222: Embedded System Modeling Lecture 2

Intellectual Property (IP)

• Computation IP: Wrapper model

B

IP

v1

v2

Synthesizable IP in wrapper

behavior

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 25

Intellectual Property (IP)

• Computation IP: Wrapper model

B T

IP

v1

replacable

at any time

v2

Synthesizable Transducer IP in wrapper

behavior

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 26

(c) 2019 R. Doemer 13

EECS222: Embedded System Modeling Lecture 2

Intellectual Property (IP)

• Computation IP: Wrapper model

B T

IP

v1

replacable

at any time

v2

Synthesizable Transducer IP in wrapper

behavior

• Protocol inlining with wrapper

B1 B1

IP IP

v1 v1

v2 v2

before after

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 27

Intellectual Property (IP)

• Computation IP: Adapter model

B T IP

A

v1

replacable

at any time

v2

Synthesizable Transducer Adapter IP

behavior

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 28

(c) 2019 R. Doemer 14

EECS222: Embedded System Modeling Lecture 2

Intellectual Property (IP)

• Computation IP: Adapter model

B T IP

A

v1

replacable

at any time

v2

Synthesizable Transducer Adapter IP

behavior

• Protocol inlining with adapter

B1 IP B1 IP

A

v1 v1

v2 v2

before after

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 29

Intellectual Property (IP)

• Communication IP: Channel with wrapper

C1 C2

v1

replacable

v2

at any time

IP

v3

Virtual channel IP protocol channel in wrapper

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 30

(c) 2019 R. Doemer 15

EECS222: Embedded System Modeling Lecture 2

Intellectual Property (IP)

• Communication IP: Channel with wrapper

C1 C2

v1

replacable

v2

at any time

IP

v3

Virtual channel IP protocol channel in wrapper

• Protocol inlining with hierarchical channel

B1 B2 B1 B2

v1 v1

v2 v2

before after

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 31

Intellectual Property (IP)

• Incompatible busses: Transducer insertion

B1 T IP

v1 A

v4

v2

v5

v3

Synthesizable System bus Transducer Adapter IP bus IP

behavior

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 32

(c) 2019 R. Doemer 16

EECS222: Embedded System Modeling Lecture 2

Intellectual Property (IP)

• Incompatible busses: Transducer insertion

B1 T IP

v1 A

v4

v2

v5

v3

Synthesizable System bus Transducer Adapter IP bus IP

behavior

• Protocol inlining with transducer

B1 T IP

v1

v4

v2

v5

v3

after

EECS222: Embedded System Modeling, Lecture 2 (c) 2019 R. Doemer 33

(c) 2019 R. Doemer 17

You might also like

- Tlm2 Getting Started 2Document6 pagesTlm2 Getting Started 2Frankie LiuNo ratings yet

- Getting Started With TLM-2.0 - Part1Document6 pagesGetting Started With TLM-2.0 - Part1Frankie LiuNo ratings yet

- Getting Started With TLM-2.0Document5 pagesGetting Started With TLM-2.0Frankie LiuNo ratings yet

- Tlm2 Getting Started 1Document8 pagesTlm2 Getting Started 1Frankie LiuNo ratings yet

- The TLM-2.0 Standard: John Aynsley, DoulosDocument43 pagesThe TLM-2.0 Standard: John Aynsley, DoulosFrankie LiuNo ratings yet

- TLM-2 0 1Document8 pagesTLM-2 0 1Frankie LiuNo ratings yet

- TLM-2.0 Review and FAQDocument1 pageTLM-2.0 Review and FAQFrankie LiuNo ratings yet

- Systemc ExamplesDocument8 pagesSystemc ExamplesFrankie LiuNo ratings yet

- C++ - YouCompleteMe, Header Files - Stack OverflowDocument2 pagesC++ - YouCompleteMe, Header Files - Stack OverflowFrankie LiuNo ratings yet

- Complete TLM-2.0 AT Example, Including Initiators, Interconnect and TargetsDocument4 pagesComplete TLM-2.0 AT Example, Including Initiators, Interconnect and TargetsFrankie LiuNo ratings yet

- 2019 DVCon India Modern SystemC.v2 - 4.3Document41 pages2019 DVCon India Modern SystemC.v2 - 4.3Frankie LiuNo ratings yet

- Using Default .Ycm - Extra - Conf - Py, The Standard c++11 Headers Are Not Found. Issue #303 Ycm-Core - YouCompleteMeDocument10 pagesUsing Default .Ycm - Extra - Conf - Py, The Standard c++11 Headers Are Not Found. Issue #303 Ycm-Core - YouCompleteMeFrankie LiuNo ratings yet

- Lecture6 SystemC Intro PDFDocument25 pagesLecture6 SystemC Intro PDFFrankie LiuNo ratings yet

- The Definitive Guide To Systemc: The Systemc LanguageDocument4 pagesThe Definitive Guide To Systemc: The Systemc LanguageFrankie LiuNo ratings yet

- c++11 YoucompletemeDocument3 pagesc++11 YoucompletemeFrankie LiuNo ratings yet

- SpecC and SystemCDocument2 pagesSpecC and SystemCFrankie LiuNo ratings yet

- The Definitive Guide To Systemc: The Systemc LanguageDocument23 pagesThe Definitive Guide To Systemc: The Systemc LanguageFrankie LiuNo ratings yet

- Doulus SystemC TutorialDocument23 pagesDoulus SystemC TutorialFrankie LiuNo ratings yet

- Lecture3 PDFDocument12 pagesLecture3 PDFFrankie LiuNo ratings yet

- Lecture5 PDFDocument14 pagesLecture5 PDFFrankie LiuNo ratings yet

- EECS 222: Embedded System Modeling: Lecture 9: OverviewDocument11 pagesEECS 222: Embedded System Modeling: Lecture 9: OverviewFrankie LiuNo ratings yet

- Lecture4 PDFDocument9 pagesLecture4 PDFFrankie LiuNo ratings yet

- Lecture6 PDFDocument4 pagesLecture6 PDFFrankie LiuNo ratings yet

- Lecture7 PDFDocument2 pagesLecture7 PDFFrankie LiuNo ratings yet

- Cursor Movement - How Do I Navigate To Topics in Vim's Documentation - Vi and Vim Stack ExchangeDocument5 pagesCursor Movement - How Do I Navigate To Topics in Vim's Documentation - Vi and Vim Stack ExchangeFrankie LiuNo ratings yet

- Lecture8 PDFDocument3 pagesLecture8 PDFFrankie LiuNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5810)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- Paper Final RusuDocument9 pagesPaper Final RusuImam MoeslimNo ratings yet

- Rough Set Adaptive in The Model Based of Cellular Automata and Multi-AgentsDocument7 pagesRough Set Adaptive in The Model Based of Cellular Automata and Multi-AgentsManaging Editor Journal of ComputingNo ratings yet

- The Petri Net Method: DR Chris LingDocument41 pagesThe Petri Net Method: DR Chris LingOtto Heinrich WehmannNo ratings yet

- Digital Design Using Verilog HDL: Fall 21Document39 pagesDigital Design Using Verilog HDL: Fall 21ifireNo ratings yet

- UML State Machine Diagrams and ModelingDocument19 pagesUML State Machine Diagrams and ModelingrishikarthickNo ratings yet

- Testing Embedded SoftwareDocument34 pagesTesting Embedded SoftwaresonNo ratings yet

- Lecture#03, FA, Union, Complement, Intersection, Concatenation, Kleene StarDocument59 pagesLecture#03, FA, Union, Complement, Intersection, Concatenation, Kleene StarAzka AzizNo ratings yet

- Scheme and Syllabus of B.Tech. (2018 Batch Onwards)Document14 pagesScheme and Syllabus of B.Tech. (2018 Batch Onwards)Suri SrNo ratings yet

- Finite State MachinesDocument21 pagesFinite State Machinesindah_yantiNo ratings yet

- Chapter Two-Computational ComplexityDocument19 pagesChapter Two-Computational ComplexityErmias MesfinNo ratings yet

- Verilog ExercisesheetDocument6 pagesVerilog ExercisesheetFionna ImmaculateNo ratings yet

- 6 Regular ExpressionsDocument28 pages6 Regular ExpressionsSahir LodhiNo ratings yet

- Learning Game AI Programming With Lua Sample ChapterDocument74 pagesLearning Game AI Programming With Lua Sample ChapterPackt Publishing100% (1)

- Embedded Systems Design 10EC74Document110 pagesEmbedded Systems Design 10EC74VarunNo ratings yet

- Finite Automata and Turing Machines: Frank StephanDocument50 pagesFinite Automata and Turing Machines: Frank StephanAbhishekSharmaNo ratings yet

- Chomsky and Greibach Normal FormDocument6 pagesChomsky and Greibach Normal Formarihan23100% (1)

- Placement Manual ECEDocument44 pagesPlacement Manual ECEArjun ChauhanNo ratings yet

- Introduction To The Theory of Computation: by Solomon Getachew 1Document17 pagesIntroduction To The Theory of Computation: by Solomon Getachew 1Lamesgn YigremNo ratings yet

- Finite State Machine (FSM) : ExampleDocument22 pagesFinite State Machine (FSM) : Examplehaseeb tNo ratings yet

- Chapter 2 (Part A) Finite AutomataDocument43 pagesChapter 2 (Part A) Finite AutomataFilomeno SilvaNo ratings yet

- Sad Assignment ConDocument91 pagesSad Assignment ConTUSHAR CHAURENo ratings yet

- Unit-Ii Regular Expressions and Languages DefinitionDocument34 pagesUnit-Ii Regular Expressions and Languages DefinitionGanesh KumarNo ratings yet

- Regular Expressions: Reading: Chapter 3Document39 pagesRegular Expressions: Reading: Chapter 3Pro HammadNo ratings yet

- Theory of ComputationDocument279 pagesTheory of Computationapi-3864917No ratings yet

- T.E. Information Technology 2019 Course 28.06.2021Document116 pagesT.E. Information Technology 2019 Course 28.06.2021Sonali BirjeNo ratings yet

- Wind TurbineDocument82 pagesWind TurbineJován MéridaNo ratings yet

- QB of TOC For TY B TECH MRSDocument4 pagesQB of TOC For TY B TECH MRSVaibhavi PatilNo ratings yet

- Fa 1 MotivationDocument21 pagesFa 1 Motivationrula mohammadNo ratings yet

- A Domain-Specific Language For The Control of Self-Adaptive Component-Based ArchitectureDocument19 pagesA Domain-Specific Language For The Control of Self-Adaptive Component-Based ArchitectureBruno OliveiraNo ratings yet

- B.Tech. (CSE) - DS Semester-4Document24 pagesB.Tech. (CSE) - DS Semester-4dabagac581No ratings yet