Professional Documents

Culture Documents

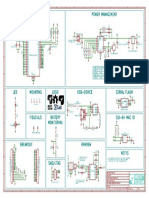

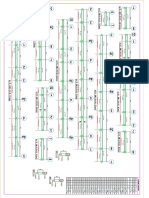

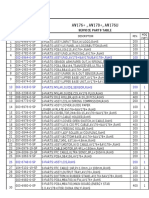

Schematics 3610843

Uploaded by

olger huancara gasparaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Schematics 3610843

Uploaded by

olger huancara gasparaCopyright:

Available Formats

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D D

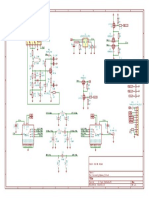

PMU_ANALOG

[2]

[2]

RTC_MODE

OSC32KO

OSC32KI

VBATBK

[2]

[15]

HW_VER_ADC

MIC_BIAS

D6

C7

A6

B6

E6

B8

A8

1uF

OSC32KI

OSC32KO

VBATBK

RTC_MODE

ADCI1

ADCI2

ADCI3

(10mA / ON)

C0203

G10 H5

MICBIAS ADI_SCLK ADI_SCLK [5]

[8] MIC_P C15 H4

MICP ADI_SYNC ADI_SYNC [5]

[8] D15 RTC ADC G2

MIC_N MICN ADI_D ADI_D [5]

G8

HEADMIC_BIAS AUXMICBIAS

C2

AUD_SCLK AUD_SCLK [5]

A13

AUXMICP

A14 F1

AUXMICN AUD_ADSYNC [5]

C AUD_ADD0

D1

AUD_ADSYNC

AUD_ADD0 [5]

C

H9

HEADMICBIAS

E14 G1

1uF

[8] HEADMIC_P AUD_DASYNC [5]

HEADMICP AUD_DASYNC

[8] HEADMIC_N F14 G3 [5]

HEADMICN AUD_DAD0 AUD_DAD0

C0204

1K R0209 H10 G5

[8] HEADMIC_IN_DET HEADMIC_IN AUD_DAD1 AUD_DAD1 [5]

A die To D die INTERFACE

G14 D2

AIL1 XTL_BUF_EN0 XTL_BUF_EN0 [5]

F15 E2 [5]

AIR1 XTL_BUF_EN1 XTL_BUF_EN1

AUDIO

[8] AORP K12

AORP

E3

EXT_RST_B EXT_RST_B [5]

[8] K13

AORN AORN

E4 ANA_INT [5]

ANA_INT

[8] HP_DET J10

BKBT RTC

HEADSET_L_INT

J9 D3 [5]

GND_DET CHIP_SLEEP CHIP_SLEEP VBATBK

4.7K

K14

[2] HP_L HEAD_P_L

J14 F2

[2] HP_R HEAD_P_R CLK32K CLK_32K [5]

VBATBK VBATBK

[8] C14 U0200-A

EAR_P EARP

R0200

10K(n.m)

B14 ASIC-SC2723G-170-0.4 [2] OSC32KO

[8] EAR_N EARN

10K(n.m)

D4 [5]

CLKIN_26MHZ PMU_26M_IN

CLK

F12

[8] PAOUT_P PA_OUTP

[8] E12 C6 PMU_32K_IN

PAOUT_N PA_OUTN CLK32K_DCXO

[15]

R0207

R0211

PIN K8 VREFN First to C0207

R0210 0R

H13

VCOM

22uF

C0207

22uF

1uF

X0200

Then to main GND [2,8] AMPG_VCOM C0210 1uF H12

VCMI DPIN

R2

BB_USB_DP [5]

C0200

C0202

R1 [2] [2] OSC32KI

RTC_MODE

USB

DMIN BB_USB_DM [5]

K8

VREFN

[2] OSC32KI

0R

6.8pF

6.8pF

P3 [12]

DPOUT CON_USB_DP

R0206

P2

DMOUT CON_USB_DM [12]

C0212

C0201

L10

CPNEG

C0209 1uF

C0208 1uF M13 E7

CAP_P EXTRSTN EXTRSTN [13]

CAP-1UF-0603

CLASS G AMP

N13 J2

SYSTEM

CAP_N PBINT PBINT [13]

H3

PBINT2 PBINT2 [12]

[2] HP_L L14

HEAD_AMPG_INL

C0205 2.2uF J3

[2] HP_R PRODT

L15

HEAD_AMPG_INR

C0213 2.2uF B2

(NC) PTEST

M14

[8] HP_GDRO_L HEAD_DRO_L

M15 B5

[8] HP_GDRO_R HEAD_DRO_R WHTLED DCXO_LOW_CUR

[15]

DCXO_LOW_CUR

0R(n.m) R0208

VBATA

L8 H2 WB_CLK_REQ [17]

[2,8] AMPG_VCOM AMPG_VCOM EXT_XTL_EN0

WHTLED_IB0

WHTLED_IB1

WHTLED_IB2

WHTLED_IB3

C11

B13

C12

C13

B WHTLED_IB[2:0] is used for RGB LED if need. B

[10]FLASH_SINK

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

River.Du 2015-10-12 Hardware DEPT.

DATED:

EQA: COMPANY:

Mulder.Han

2015-10-12 Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu CONFIDENTIAL AND PROPRIETARY SHEET: 5 OF 23

2015-10-12

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

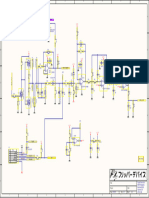

PMU_POWER

D SC2723 LDO ouput D

Power Output Voltage (V) Output Current Default Voltage Default

VDD1V8 1.2~1.8 200mA 1.8V ON

VBAT VBAT

AVDD28 1.8~3.3 100mA 2.8V ON

4.7uF/6.3V

10uF/6.3V

10uF/6.3V

2

2

VDD2V8 1.8~3.3 200mA 2.8V ON

T

RV0301

RV0302

C0326

C0328

C0334

1

VDDSIM0 1.8~3.3 200mA OFF

1

VDDSIM1 1.8~3.3 200mA OFF

VBAT must pass C0326 C0328

Then to PIN K10 H8 E9 E8 E5 J6 F9 E10 VDDSIM2 1.8~3.3 200mA OFF

C0334 must be close to PIN E10 F9

VBAT

VBAT 60-80MIL VDDRF0 1.2~1.8 200mA 1.8V ON

K10

E10

H8

E9

E8

E5

F9

J6

VBATAUD

VBATD

VBATD

VBATCG

VBATA

VBATA

VBATPA

VBATPA

(width>=0.3mm)

(width>=0.3mm)

(width>=0.5mm)

(width>=0.5mm)

(width>=0.5mm)

AVDDVB

VDDCAMA 1.8~3.3 150mA OFF

P9 G15

VBATDRV AVDDVB

1

VDDCAMMOT 1.8~3.3 100mA OFF

RV0303

1uF C0313

(30mA / OFF)

RV0303 NC R6

VBATDRV VDDAO

C0330 10uF/6.3V R8 J15

VBATDRV VBAT VDDAO

T

VBATAUD (150mA / OFF) 2.2uF C0311

VDDEMMCCORE 1.8~3.3 300mA 3.0V ON

2

P7 AVDDPA

(width>=1.5mm)

VBATDRV

VBATDRV

C0331 10uF/6.3V P6 F10

VBATDRV VBATPA AVDDPA

10uF/6.3V C0317

(400mA / OFF)

P8 AVDD2V8

VBATDRV

At least C0331 must close IC

P5

VBATDRV VBATA AVDD_2V8

(100mA / ON)

A4

2.2uF C0309

VDDSDCORE 1.8~3.3 300mA OFF

P10 VDD2V8

VBATDRV

VDDCORE

N5

N10

VBATDRV

VBATDRV

VDD_2V8

(200mA / On)

A10

VDDSDIO VDDSDIO 1.8~3.3 100mA OFF

VBATD

J5

C0346 10uF/6.3VL0300 0.68uH R5

VDD_SDIO

VBATBK 2.6/2.8/3.0/3.2 10mA 2.8V ON

DCDC CORE

LX_CORE (100mA / OFF)

(2000mA / ON)

VDDSIM0

T5

LX_CORE

C3

VDD_SIM0

T4

LX_CORE (200mA / OFF)

C R4 B3

VDDSIM1

VDDVIB 1.8~3.3 200mA OFF C

VDDARM [6] VFBCORE VFB_CORE VBATA VDD_SIM1

(200mA / OFF)

VDDSIM2

T6 A2 KPLED_OUT 1.8~3.3 50mA OFF

DCDC ARM

22uF 0.47UH LX_ARM VDD_SIM2

(3000mA / ON)

C0318 L0301 1uF C0333

(200mA / OFF)

R7 VDDUSB

LX_ARM

T7

LX_ARM

VBATD

VDD_USB

(60mA / OFF)

J1

VDDCAMMOT

VDD_WIFIPA 1.8~3.3 500mA OFF

[6] T2 VDDCAMA

VFBARM VFB_ARM

A11

VDD_CAMMOT

VDDMEM

(100mA / OFF)

VDD_DCXO 1.8~3.3 50mA 1.8V ON

DCDC WRF DCDC MEM

POWER

C0327 10uF/6.3V

L0302 1.0uH N1

(800mA / ON)

LX_MEM

B4

VBATA VDD_CAMA

1uF C0310

(150mA / OFF)

VDDWRF

P1

VFB_MEM

VDD_EMMCCORE

C9

VDDEMMCCORE

VDDCAMD 1.2~1.8 150mA OFF

2.2uF/6.3V C0308

(300mA / ON)

VDDSDCORE

2.2uH L0305 T9

(300mA / ON)

LX_RF

0603 size should be use for C0320

C0320 4.7uF

U0200-B

VDD_SDCORE

(300mA / OFF)

B9

VDDDCXO VDDUSB 1.8~3.3 60mA 3.3V OFF

R3 ASIC-SC2723G-170-0.4

VFB_RF VBATD

VDDWPA B10

VDD_DCXO

(50mA / ON)

VDDWIFIPA

C0319 4.7uF 2.2uH L0304 T11

DCDC WPA

LX_WPA

(700mA / OFF)

C10

VDD_WIFIPA

4.7uF C0325

(500mA / OFF)

R10 PIN Bypass VBAT VFB>0.25mm R10

(700mA)

VFB_WPA VDDEMMCIO VDDAO 2.9/3.1/3.2/3.3 150mA OFF

VDDWCN

[5]RF_APT_DAC T12

APC_WPA VDD_GEN0

R12

AVDD1V8

VDDEMMCIO>12mil The power of U0200.R12 and U0200.T14 pin is swapped,

(200mA / ON)

T14

The change should be modified by SW

2.2uF 2.2uH GAUGE BAT DET DCDC GEN DCDC CON VDD_GEN1

(300mA / OFF)

C0321 L0306 T8 1uF(n.m) C0336

LX_CON (100mA / ON)

VDDRF0

VDDLDO

T3

VFB_CON

VDD_RF0

(200mA / On)

R13

VDD1V8

2.2uF C0305 AVDDVB 2.9/3.1/3.2/3.3 30mA OFF

H6

10uF/6.3V 2.2uH DCDC GEN VDD_1V8

C0329 L0303 P15 2.2uF C0307

(800mA / ON)

LX_GEN (200mA / ON)

VDDCAMCORE

R11

(800mA)

VDCDC_GEN

VDD_CAMD

(150mA / OFF)

R14 R0325 0 AVDDPA 2.9/3.1/3.2/3.3 400mA OFF

VDDCAMIO

BATDET_VREF

R11 PIN VDCDC_GEN>0.5mm R15

VDD_CAMIO

K5

BATDET_VREF (200mA / OFF)

[12] BAT_TEMP_ADC B7

BAT_DET

VDDAMP

VDDCAMIO 1.2~1.8 200mA OFF

1uF

N14

VDDAMP

(200mA / OFF) 2.2uF C0314

K3

FUEL

[12] SENSE_P SENSE_P

C0300

B1

(NC) VPP

[12] SENSE_N K2

SENSE_N

VBATD VDD_VIBR

B11

All capacitors must be close to U0200.

(200mA / OFF)

VIB_CTRL

AVDDAMP 1.2~1.8 200mA OFF

0.1uF(n.m)

CHARGE

K6

CHGR_MODE SINK

L2 B12

[12]

VBAT_SENSE VBATSEN VBATD KPLED_OUT

(50mA / OFF)

K1

[12]ISENSE ISENSE

C0315

NC

L6 T1

[12]VDRV VDRV NC

M1 T15

VDRV2 NC

[12] VCHG_D

R0301 0R L5

VCHG

GND

NC

A15 VDDGEN0 1.2~1.8 200mA 1.8V ON

B VBUS_5V R0300 100R

M3

CC_COMP NC

A1

B

M2

CV_COMP

AGNDVB

VSSDRV

VSSDRV

VSSDRV

VSSDRV

VSSDRV

VSSDRV

VSSDRV

CPGND

1uF

VSSPA

VSSPA

VDDGEN1 1.2~1.8 100mA 1.8V ON

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C0302

L7

F7

F8

G6

G7

H7

J7

K7

N9

N8

N7

N6

M6

M7

M5

D12

D13

M10

K9

DCDCARM 0.6~3.7 3000mA 0.9V ON

DCDCCORE 0.6~3.7 2000mA 0.9V ON

DCDCMEM 0.6~3.7 800mA 1.2V ON

DCDC_GEN 0.6~3.7 800mA 2.2V ON

DCDCRF 0.6~3.7 300mA 1.5V ON

DCDCWPA 0.6~3.7 700mA OFF

DCDCCON 0.6~3.7 300mA OFF

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

River.Du 2015-10-12 Hardware DEPT.

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 6 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

eMMC+LPDDR3

D D

VDD1V8

0

VDDMEM

R0504

BC

10uF/6.3V

0.1uF

0.1uF

4.7uF

0.1uF

0.1uF

1uF

1uF

1uF

C0507

C0504

C0518

C0516

C0514

C0510

C0511

C0512

C0513

W11

M10

M12

AA3

AA5

AB3

AB4

AB9

AA9

AB5

AB8

H12

N11

R11

K10

K12

V10

V12

Y12

P11

T10

T12

J11

W5

M5

G5

G9

H8

U8

U9

N5

R5

U5

Y8

K5

P5

P8

V5

F3

F4

F9

F5

F8

T5

L8

L9

L2

L5

J5

VDDEMMCCORE

VDD1

VDD1

VDD1

VDD1

VDD1

VDD1

VDD1

VDD1

VDD1

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDD2

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

K2

VDDCA

B3

VCC

N2

VDDCA

B12

VCC

U2

4.7uF

0.1uF

0.1uF

VDDCA

B13

VDDEMMCCORE VCC

V2

VDDCA

C4

VCC

C0505

C0502

C0517

D8

VCC

VDDEMMCIO

LPDDR3 Power CK

P3

EMCLK_P [7]

N3 [7]

CK EMCLK_N

A4

VCCQ

B6 T2 [7]

VCCQ CKE0 EMCKE0

B9 R2

4.7uF

0.1uF

0.1uF

VDDEMMCIO VCCQ CKE1

eMMC Power

C7

VCCQ

U3 [7]

CS0 EMCSN0

C11

C0506

C0503

C0508

VCCQ

T3

CS1 EMCSN1 [7]

Y2 [7]

CA0 EMA0

A11

VDDI

Y3

CA1 EMA1 [7]

W2 [7]

CA2 EMA2

1uF

W3 [7]

CA3 EMA3

C CA4

V3

EMA4 [7]

C

C0500

L3 [7]

CA5 EMA5

K3

CA6 EMA6 [7]

J3

CA7 EMA7 [7]

J2 [7]

CA8 EMA8

A7

RCLK

H2

CA9 EMA9 [7]

B8

[7] EMMC_CLK CLKM

W12

DQ0 EMD00 [7]

V11

DQ1 EMD01 [7]

[7] A6

EMMC_CMD CMD

V13

DQ2 EMD02 [7]

U11

DQ3 EMD03 [7]

C2 U13

[7] EMMC_RST RST DQ4 EMD04 [7]

eMMC

T11

DQ5 EMD05 [7]

EMMC_D[0:7] T13

DQ6 EMD06 [7]

EMMC_D0 A9

DAT0

R12

DQ7 EMD07 [7]

EMMC_D1 B10

DAT1

EMMC_D2 C6 R10 [7]

DAT2 DM0 EMDQM0

EMMC_D3 B5

DAT3

T9

DQS0 EMDQS0_P [7]

EMMC_D4 C9

DAT4

R9

DQS0 EMDQS0_N [7]

EMMC_D5 A10

DAT5

EMMC_D6 A5

DAT6

N12

DQ8 EMD08 [7]

EMMC_D7 B4

DAT7

M13

DQ9 EMD09 [7]

M11

DQ10 EMD10 [7]

L13

DQ11 EMD11 [7]

L11

DQ12 EMD12 [7]

U0500

LPDDR3

K11

MEM-LPDDR3+EMMC-KMQN1000SM-B316 DQ13 EMD13 [7]

K13

DQ14 EMD14 [7]

J12

DQ15 EMD15 [7]

N10 [7]

DM1 EMDQM1

M9

DQS1 EMDQS1_P [7]

N9

DQS1 EMDQS1_N [7]

A1

DNU

AB12

DNU & RFU

DQ16 EMD16 [7]

A14

DNU

AB11

DQ17 EMD17 [7]

AA1

DNU

AB10

DQ18 EMD18 [7]

AA14

DNU

AA13

DQ19 EMD19 [7]

AB1

DNU

AA12

DQ20 EMD20 [7]

AB2

DNU

AA10

DQ21 EMD21 [7]

AB13

DNU

Y13

DQ22 EMD22 [7]

B AB14

DNU

DQ23

Y11

EMD23 [7]

B

W10

DM2 EMDQM2 [7]

Y9

DQS2 EMDQS2_P [7]

A2 W9

VSF DQS2 EMDQS2_N [7]

A13

VSF

B1 H11

VSF DQ24 EMD24 [7]

B14 H13

VSF DQ25 EMD25 [7]

D2 G10

VSF DQ26 EMD26 [7]

NC

D3 G12

VSF DQ27 EMD27 [7]

D4 G13

VSF DQ28 EMD28 [7]

D5 F10

VSF DQ29 EMD29 [7]

D6 F11

VSF DQ30 EMD30 [7]

F12

DQ31 EMD31 [7]

J10 [7]

DM3 EMDQM3

A3 H9

VSSM DQS3 EMDQS3_P [7]

add

A8 J9

VSSM DQS3 EMDQS3_N [7]

A12

VSSM

VDDMEM

B2

VSSM

G2 R0500 240 +/-1%

ZQ0

B7

VSSM R0503 240 +/-1%

G3

NC(ZQ1)

10K(n.m)

B11

VSSM

C3

VSSM

C5 P10

GND

VSSM NC(ODT) EMODT [7]

C8 VREFDQ

VSSM

10K(n.m) R0510

C10

VSSM

P13

VREFDQ

10nF/10V

C12

VSSM

C13 VDDMEM

VSSM

D7 M2

VSSM VREFCA

C0519

10K(n.m)

R0511

VSSCA

VSSCA

VSSCA

VSSCA

VSSCA

VSSCA

VSSCA

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA2

AA4

AA8

F2

G4

G8

H3

H5

L4

M3

M4

N4

N8

P4

P12

R3

R4

R8

T4

Y4

Y5

AA11

F13

G11

H10

J8

J13

K8

K9

L10

L12

M8

N13

P9

R13

T8

U10

U12

V8

V9

W8

W13

Y10

H4

J4

K4

P2

U4

V4

W4

VREFCA

10K(n.m) R0512

10nF/10V

A A

C0520

R0513

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

River.Du

2015-10-12 Hardware DEPT.

DATED:

EQA: COMPANY:

Mulder.Han

2015-10-12 Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu CONFIDENTIAL AND PROPRIETARY SHEET: 8 OF 23

2015-10-12

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

DIGITAL

D D

E28

DIGTAL D23

SPI RF0

[15] RFSDA0/GPIO1 KEYOUT[0]/GPIO121

SPI_DATA_RF0 KEYOUT0 [13]

(VIO1)

[15] E27 B22 SHDN

SPI_CLK_RF0 RFSCK0/GPIO2 KEYOUT[1]/GPIO122 [8]

F24 B23

[15] SPI_LE_RF0 RFSEN0/GPIO3 (WPU) KEYOUT[2]/PWMB(G0)/GPIO123

KEYPAD

E25

(WPU)

(VIO1)

KEYIN[0]/EXTINT2/GPIO124 KEYIN0 [13]

F25

SPI RF1

RFSDA1/GPIO4

E24

(WPU)

(VIO1)

KEYIN[1]/EXTINT3/GPIO125 KEYIN1 [13]

H25

RFSCK1/GPIO5

C23

KEYIN[2]/EXTINT4/PLL_LOCK/GPIO126

J25

RFSEN1/GPIO6 (WPU)

B25

SPI0_DO/SDA1/GPIO91

[15] J28

RFCTL_0 RFCTL[0]/GPIO19

B26

SPI 0

(VIO1)

SPI0_DI/GPIO92

[15] RFCTL_1 J27

RFCTL[1]/GPIO20

C26

FOR LTE / WCDMA / TDS / GSM

SPI0_CLK/SCL1/GPIO93

[15] RFCTL_2 K29

RFCTL[2]/GPIO21

B24

(WPU) SPI0_CSN/GPIO90

RF_ANTSWITCH_EN

K28

L29

RFCTL[3]/GPIO22

INTERFACE V26 [15]

RFCTL[4]/GPIO23 MAIN_RXIP RXIP_MADC

MADC IQ

[16] A23 AG19

SPI2_DO/GPIO53 [2] ADI_SCLK ADI_SCLK/SDA5

RFCTL_4 L28 U26 [15]

RFCTL[5]/GPIO24 MAIN_RXIN RXIN_MADC

[16] B21 AG18

SPI 2

(VIO1)

SPI2_DI/GPIO54 [2] ADI_SYNC ADI_SYNC/SCL5

K26 V25

RFCTL[6]/GPIO25 MAIN_RXQP RXQP_MADC [15]

A24 [2] ADI_D AH19

SPI2_CLK/GPIO55 ADI_D

K25 W25 RXQN_MADC [15]

RFCTL[7]/GPIO26 MAIN_RXQN

A21

(WPU) SPI2_CSN/GPIO52

M27 AH23

RFCTL[8]/GPIO27 [2] AUD_SCLK AUD_SCLK/IIS2CLK

MADC.DIV IQ

M28 W28 RXIP_MADC_DIV [15]

RFCTL[9]/GPIO28 MAIN_DIV_RXIP

AH16 R2100 0 [14] [2] AUD_ADSYNC AJ20

SD0_CLK0/GPIO153 TF_SD0_CLK0 AUD_ADSYNC

L25 V28

RFCTL[10]/GPIO29

AF16 AH22

MAIN_DIV_RXIN RXIN_MADC_DIV [15]

SD0_CMD/GPIO150 TF_SD0_CMD [14] AUD_ADD0/IIS2DI

N29 [2] AUD_ADD0 Y29

SDIO 0

RFCTL[11]/GPIO30 MAIN_DIV_RXQP RXQP_MADC_DIV [15]

AF15 [14]

(VSD)

SD0_D[0]/GPIO151 TF_SD0_D0

M26 [2] AH20 W29

A to D Interface

RFCTL[12]/GPIO31 AUD_DASYNC AUD_DASYNC/IIS2LRCK MAIN_DIV_RXQN RXQN_MADC_DIV [15]

AH17 [14]

SD0_D[1]/GPIO152 TF_SD0_D1

N28 AE21

RFCTL[13]/GPIO32 [2] AUD_DAD0 AUD_DAD0/IIS2DO

AF18

RFCTRL

SD0_D[2]/GPIO149 TF_SD0_D2 [14]

N27 AF19 AA28

(VIO1)

(VIO1)

RFCTL[14]/GPIO33 [2] AUD_DAD1 AUD_DAD1 MAIN_TXIP TXIP_MDAC [15]

MDAC IQ

AE18

SD0_D[3]/GPIO148 TF_SD0_D3 [14]

E29 Y28

RFCTL[15]/GPIO7 MAIN_TXIN TXIN_MDAC [15]

[2] AH21

XTL_BUF_EN0 XTL_BUF_EN0

F28 Y26

RFCTL[16]/GPIO8 MAIN_TXQP TXQP_MDAC [15]

AG15 R2112 0 [17] [2] AJ21

SD1_CLK/GPIO64 WF_SD1_CLK XTL_BUF_EN1 XTL_BUF_EN1

H26 Y27

RFCTL[17]/GPIO9 MAIN_TXQN TXQN_MDAC [15]

AF14 WF_SD1_CMD [17]

SD1_CMD/GPIO65

G29 AF22

SDIO 1

RFCTL[18]/GPIO10 [2] EXT_RST_B EXT_RST_B

AE14

(VIO1)

SD1_D[0]/GPIO66 WF_SD1_D0 [17]

T28

SEC_RXIP

SADC IQ

AE13 [2] ANA_INT AE22

SD1_D[1]/GPIO67 WF_SD1_D1 [17] ANA_INT

C G25

RFCTL[19]/GPIO11

SD1_D[2]/GPIO68

AH15

WF_SD1_D2 [17]

SEC_RXIN

T29

C

G28 [2] AG22 U27

RFCTL[20]/GPIO12 CHIP_SLEEP CHIP_SLEEP SEC_RXQP

FOR LTE ONLY

AJ15

SD1_D[3]/GPIO69 WF_SD1_D3 [17]

K24 T27

RFCTL[21]/GPIO13 SEC_RXQN

F26 [2] CLK_32K

AF20

RFCTL[22]/GPIO14 CLK_32K

AB26

SIMCLK0/GPIO157 SIM0_CLK [14]

(VSIM0)

P25

SIM0

SEC_TXIP T2101

SDAC IQ

AC28 [14]

SIMDA0/GPIO158 SIM0_DA

H29 P26

RFCTL[23]/GPIO15 SEC_TXIN

PTEST

AD28

(VIO1)

SIMRST0/GPIO159 SIM0_RST [14]

H27 AJ23 T26

RFCTL[24]/GPIO16 PTEST SEC_TXQP

H28 R25

RFCTL[25]/GPIO17 SEC_TXQN

AD27 [14]

[17] SIMCLK1/GPIO160 SIM1_CLK

(VSIM1)

J26

SIM1

WCN_LTECOEXIST_RX RFCTL[26]/GPIO18

AD26 AH8

SIMDA1/GPIO161 SIM1_DA [14] [9] MDSI_DATA0_P MDSI_DATAP0

AA27 RF_PA_RAMP [16]

APCOUT0

AE27 [9] AH7

[17] SIMRST1/GPIO162 SIM1_RST [14] MDSI_DATA0_N MDSI_DATAN0

WCN_LTECOEXIST_TX M25

RFCTL[27]/GPIO34

AB29

APCOUT1

P28 VDD2V8 [9] AJ8

VDD1V8 MDSI_DATA1_P

APC

RFCTL[28]/RFFE_SCK1/GPIO38 MDSI_DATAP1

4.7K(n.m)

4.7K(n.m)

AB25

MIPI DISPLAY

SIMCLK2/SCL4/GPIO154

(VSIM2)

N24 AJ9 AA26

SIM2

RFCTL[29]/RFFE_SDA1/GPIO39 MDSI_DATA1_N MDSI_DATAN1 APCOUT2 RF_APT_DAC [3]

AC25 [9]

SIMDA2/SDA4/GPIO155

AD25 [9] MDSI_DATA2_P AG9 AB28

SIMRST2/CLK_AUX1/GPIO156 MDSI_DATAP2 APCOUT3

RFFE(MIPI)

4.7K

4.7K

[9] MDSI_DATA2_N AF9 U2100-C

MDSI_DATAN2

N26

R2117

R2116

(VIO1)

[16] RFFE_SCLK0 RFFE_SCK0/GPIO36

(WPU)

D28 I2C2_SCL

I2C2: G Sensor, M Sensor, L+P Sensor, Gyroscope ASIC-SC9832A-492-0.4 U29

(VIO1)

[11]

IIC2

SCL2/GPIO127 AFCOUT0

[16] R28 U2100-A MDSI_DATA3_P AF10

AFC

RFFE_SDA0 RFFE_SDA0/GPIO37 MDSI_DATAP3

C28 [9]

ASIC-SC9832A-492-0.4 (WPU) SDA2/GPIO128 I2C2_SDA [11]

MDSI_DATA3_N AG10 U28

MDSI_DATAN3 AFCOUT1

R2115

R2114

[9]

CLK_OUT

D27 [9] AH10

(WPU)

(VIO2)

IIC3

SCL3/EXT_XTL_EN0/GPIO146 I2C3_SCL [9] MDSI_CLK_P MDSI_CLKP [2]

A9 G17 PMU_26M_IN

CCIRD[0]/GPIO40 CLK26M_SINE_O

D26 [9] AH9

(WPU) SDA3/EXT_XTL_EN1/GPIO147 I2C3_SDA [9] MDSI_CLK_N MDSI_CLKN

C8

CCIRD[1]/GPIO41

D21 AP_26M_IN [15]

(FOR AP) CLK26M_SINE0

I2C3: CTP R2106 4.02K AH11

CLK_IN

MDSI_REXT

EXINT

[10] CAM_MCLK A8 D25 CTP_INT [9]

(VIO2)

VDDCAMIO CMMCLK/CLK_AUX2/GPIO42 EXTINT0/WDRST/GPIO144

G20 CP_26M_IN [15]

33pF(n.m) (FOR CP) CLK26M_SINE1

C2100 E8 E26 [9]

CMPCLK/CLK_CP0_DSP/GPIO43 EXTINT1/GPIO145 CTP_RST B11

[10] CAM0_DATA0_P MCSI0_DATAP0

(VCAM)

CCIR

[10]CAM_RST0 D8 [10] B10 B16

CMRST0/GPIO44 CAM0_DATA0_N MCSI0_DATAN0 LVDS_DATAP0

AH28 [17]

IIS0DI/GPIO56 BT_PCM_OUT

4.7K(n.m)

4.7K(n.m)

[10]CAM_RST1 D9 B17

CMRST1/GPIO45 LVDS_DATAN0

AG27 A11

(VIO1)

[17] [10]

IIS0

IIS0DO/GPIO57 BT_PCM_IN CAM0_DATA1_P MCSI0_DATAP1

[10] CAM_PWDN0 F8 AH27 [17] [10] A12 D18

CMPD0/GPIO46 IIS0CLK/GPIO58 BT_PCM_CLK CAM0_DATA1_N MCSI0_DATAN1 LVDS_DATAP1

MIPI CAMRA 0

[10] E9 AJ27 [17] D19

CAM_PWDN1 CMPD1/GPIO47 IIS0LRCK/GPIO59 BT_PCM_SYNC LVDS_DATAN1

[10] C12

CAM0_DATA2_P MCSI0_DATAP2

R2111

R2110

C10 C13 E18

SCL0/GPIO48 (WPU) [10]

LVDS(NC)

[10]I2C0_SCL CAM0_DATA2_N MCSI0_DATAN2 LVDS_DATAP2

AF29 [17]

IIS1DI/GPIO130 GPS_PDN

B9 E19

[10] I2C0_SDA SDA0/GPIO49 (WPU) LVDS_DATAN2

AF28 E12

(VIO1)

[10]

IIS1

IIS1DO/GPIO131 CAM0_DATA3_P MCSI0_DATAP3

AF27 BT_WAKE_HOST [17] [10] D12 B19

IIS1CLK/GPIO132 CAM0_DATA3_N MCSI0_DATAN3 LVDS_DATAP3

AG28 [17] B18

IIS1LRCK/GPIO133 BT_HOST_WAKE LVDS_DATAN3

AF11 B13

(VIO1)

[9] [10]

LCM

LCM_RSTN LCM_RSTN/GPIO50 CAM0_CLK_P MCSI0_CLKP

[10] B12 A20

[9] CAM0_CLK_N MCSI0_CLKN LVDS_DATAP4

LCM_FMARK AG11 AF26

DSI_TE/GPIO51 (H) U0TXD/GPIO60 BT_U0RXD [17]

B20

LVDS_DATAN4

UART0

AE26 4.02K R2105 B14

(WPU)

(VIO1)

U0RXD/GPIO61 BT_U0TXD [17] MCSI0_REXT

AE25 [17] A17

U0CTS/GPIO62 BT_U0RTS LVDS_CLKP

[15] AG14 AG26 [10] CAM1_DATA0_P D14 A18

BOARD_ID0 TRACECLK/SPI1_CLK/SD2_CLK/GPIO134 U0RTS/GPIO63 BT_U0CTS [17] MCSI1_DATAP0 LVDS_CLKN

[10] CAM1_DATA0_N D15

MCSI1_DATAN0

HSIC(NC)

MIPI CAMRA 1

[15] BOARD_ID1 AJ14

TRACECTRL/SPI1_DI/SD2_CMD/GPIO135

UART1

AH26 BB_U1TXD [13] AC16

(H)

(VIO1)

U1TXD/GPIO70 HSIC_DATA

[10] CAM1_DATA1_P A15

TRACE DATA

[13] MCSI1_DATAP1

AH14 AE24 BB_U1RXD AC15

TRACEDAT[0]/SPI1_DO/SD2_D0/GPIO136 (WPU) U1RXD/GPIO71 HSIC_STROBE

B [17] AH13 [10] CAM1_DATA1_N

B15

MCSI1_DATAN1 B

(VIO1)

WB_RST TRACEDAT[1]/SPI1_CSN/SD2_D1/GPIO137

UART2

AF12 AJ26 CAM1_CLK_P C16 AH18 R2113 200

(VIO1)

[9] LCM_BL_PWM TRACEDAT[2]/PWMC/SD2_D2/GPIO138 U2TXD/GPIO72 [10] MCSI1_CLKP VRES

[17] AE12 AF24 [10] CAM1_CLK_N C15

USB

GPS_GPIO0 TRACEDAT[3]/IIS3DI/SD2_D3/GPIO139 U2RXD/GPIO73 MCSI1_CLKN

AD17

DP BB_USB_DP [2]

[11] PROX_INT AG12

TRACEDAT[4]/IIS3DO/SD2_D4/GPIO140

4.02K R2107 A14 AD16 BB_USB_DM [2]

[17] MCSI1_REXT DM

[9] LCM_ID AH12 AH25 GPS_U0RXD

TRACEDAT[5]/IIS3CLK/SD2_D5/GPIO141 U3TXD/GPIO74

UART3

AJ12 AH24 GPS_U0TXD [17]

(VIO1)

TRACEDAT[6]/IIS3LRCK/SD2_D6/GPIO142 U3RXD/GPIO75

AJ11 AJ24 [17]

TRACEDAT[7]/WF_COEXIST/SD2_D7/GPIO143 U3CTS/GPIO76 GPS_U0RTS

AF23

U3RTS/GPIO77 GPS_U0CTS [17]

UART4

AD23 BB_U4TXD [13]

(VIO1)

ARM JTAG

U4TXD/GPIO78

AG23 [13]

BB_U4RXD

(VIO1)

U4RXD/GPIO79

AE6

MTCK/GPIO82

AF6

MTMS/GPIO83 (WPU)

B27 WF_COEXIST [17]

MEMS MIC

MEMS_MIC_CLK0/WF_COEXIST_G0/GPIO94

A27

(VIO1)

MEMS_MIC_DATA0/BEIDOU_COEXIST/GPIO95 [11]

INT_G

B28

MEMS_MIC_CLK1/EXT_XTL_EN2/GPIO96 GPS_CLK_REQ [17]

AG6

DTDO_LTE/GPIO85

C27

MEMS_MIC_DATA1/EXT_XTL_EN3/GPIO97

DSP JTAG

AH6 WF_WAKE_HOST [17]

DTDI_LTE/GPIO86 (WPU)

(VIO1)

AJ6

DTCK_LTE/GPIO87

D29

CLK_AUX0/PROBE_CLK/GPIO129 CON_32K_IN [17]

AH5

(WPU)

(VIO1)

DTMS_LTE/GPIO88

CLK

AJ5 N25

DRTCK_LTE/GPIO89 (H) XTL_EN/GPIO35

T2100

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

River.Du 2015-10-12 Hardware DEPT.

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 10 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

POWER

D D

VDDARM

U11

POWER V14

VDDARM VFB_ARM VFBARM [3]

10uF/6.3V

A U12

VDDARM VFB_ARM_N

U14

FB

0.1uF

1uF

U13

VDDARM

W17

VFB_CORE VFBCORE [3]

V12

VDDARM

W16

C2207

C2206

C2208

VDDARM INPUT

VFB_CORE_N

V13

VDDARM

VDDMEM

V11

VDDARM

P10

VDDMEM

W12

VDDARM

N10

VDDMEM

W13

VDDARM

M10

VDDMEM INPUT

VDDMEM

10uF/6.3V

W14

VDDARM

L11

VDDMEM

1uF

Y11

VDDARM

L10

VDDMEM

Y12

VDDARM

T10

C2227

C2205

VDDMEM

Y13

4.7uF

0.1uF

VDDARM

GND

1uF

Y10 U17

VDDMEM VSS

Y14

VDDARM

W11 F9 U20

VDDMEM VSS VSS

C2209

C2210

C2226

R10 K11 V15

VDDCORE VDDMEM VSS VSS

V10 K12 V16

VDDMEM VSS VSS

P17 U10 K18 V17

VDDCORE VDDMEM VSS VSS

T11 K19 V20

VDDCORE VSS VSS

T12 U23 AVDD1V8 L12 W15

VDDCORE AVDD_BB VSS VSS

K13 L13 T14

VDDCORE VSS VSS

K14 L14 W20

VDDCORE 2.2uF VSS VSS

C2212

K15 F18 L15 Y15

2.2uF

0.1uF

22uF

VDDCORE AVDD_PLL VSS VSS

K16 M11 Y16

VDDCORE VSS VSS

W10

EMVDD_PLL

K17 M12 AC7

C2204

C2203

C2202

VDDCORE VSS VSS

L16 M13 AC12

VDDCORE VSS VSS

L17 M14 AC13

VDDCORE 0.1uF VSS VSS

G13 C2223

AVDD_LVDS

L18 M15 AC11

VDDCORE VSS VSS

L19 M16 AE19

VDDCORE VSS VSS

10uF/6.3V

C L20 G10 M17 G23

C

0.1uF

VDDCORE MCSI_AVDD VSS VSS

M18 N11 AE17

VDDCORE VSS VSS

M19 N12 B2

C2201

C2200

VDDCORE VSS EMVSSQ

AC10

MDSI_AVDD

VDDCORE INPUT

M20 N13 E1

VDDCORE VSS EMVSSQ

POWER INPUT

N18 N14 H1

VDDCORE VSS EMVSSQ

N19 AJ17 N15 AJ1

GND

GND

VDDCORE HSIC_VDD12 VSS EMVSSQ

U2100-D U2100-E

P13 N16 AC4

VDDCORE ASIC-SC9832A-492-0.4 VSS ASIC-SC9832A-492-0.4 EMVSSQ

P18 N20 H4

VDDCORE VSS EMVSSQ

AJ18

VDDUSB

P19 VDDUSB P11 A1

VDDCORE 1uF VSS EMVSSQ

C2225

R13 P12 AD1

VDDCORE VSS EMVSSQ

R17 F7 C2216 0.1uF P14 K5

VDDCORE VNF0 VSS EMVSSQ

R18 P15 J5

VDDCORE VDD1V8 VSS EMVSSQ

R19 P16 AD4

VDDCORE VSS EMVSSQ

G6

VNF1

T17 VDDEMMCIO P20 M1

VDDCORE 0.1uF VSS EMVSSQ

C2217

T18 R11 M4

VDDCORE VSS EMVSSQ

T19 D10 R12 N6

VDDCORE VCAM VSS EMVSSQ

VDDCAMIO

U18 C2211 1uF R14 T1

VDDCORE VSS EMVSSQ

U19 R15 AC17

VDDCORE VSS HSIC_VSS12

AE15 R2206 0

V18

VSD

R2205 0(n.m) VDDSDIO R2205 Only support SD2.0 R16

VDDCORE VSS

P23

V19 C2222 1uF VDDSDCORE R2206 Support SD3.0 & SD2.0 R20

AGND_AFC

VDDCORE VSS

G11

VDDSIM0 MCSI_AGND

T13 AC29 T15

VDDCORE VSIM0 VSS

AE10

0.1uF MDSI_AGND

W18 C2214 T16

VDDCORE VSS

F14

AVSS_LVDS

AGND

W19 T20

VDDCORE VSS

AE29 C19

VSIM1 AVSS_LVDS

Y17 VDDSIM1 U15

VDDCORE 0.1uF VSS

C2215 F20

AVSS_PLL

Y18 U16

VDDCORE VSS

U24

AVSS_BB

AE28 AD24

VSIM2 VSS

AG7

MDSI_AGND

N17

VSS

D13

MCSI_AGND

AJ29

NC

AH1 F22 VDD1V8

NC VIO1

A28 M24 C2218 0.1uF

NC VIO1

A2 Y19

NC VIO1

NC

A29

NC

AH29

NC VDD2V8

E23

AJ2

VIO2 VIO2=VDD1V8 For 1.8V CTP IO interface

NC 1uF

C2220

AJ28 VIO2=VDD2V8 For 2.8V CTP IO interface

NC

B1 AA25 AVDD2V8

NC AVDD28

B29 C2224 1uF

NC

T24

NC

BP

P29 BP_LDO_CAP

LDO_CAP

T25

NC

1uF

C2219

B B

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

2015-10-12 Hardware DEPT.

River.Du

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 11 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D D

MEMORY

[7] EMD[00:31]

MEMORY

(VMEM)

EMD00 AE2 T4 [4]

EMD[0] EMCLK_P

CLK

CLKDPMEM

EMD01 AE3 T5

EMD[1] LPDDR2/3 CLKDMMEM EMCLK_N [4]

EMMC

EMD02 AD3

EMD[2]

EMD03 AC3 U3 [4]

EMD[3] EMCKE[0] EMCKE0

EMD04 AC2

EMD[4]

U2

LANE-0

EMCS_N[0] EMCSN0 [4]

(VMEM)

EMD05 AC1

EMD[5]

CTRL and CMD

V1 [4]

EMCS_N[1] EMCSN1

EMD06 AB1

EMD[6]

EMD07 AB2 P4

EMD[7] EMODT[0] EMODT [4]

(VMEM)

[4] AA1 W5

EMDQM0 EMDQM[0] EMDTO[0]

Y4

EMDTO[1]

AB3

[4] EMDQS0_P EMDQS[0]

AB4 R3

[4] EMDQS0_N EMDQS_N[0] EMATO

C [7] EMD[00:31] C

EMD08 L3 EMA[0:9]

EMD[8]

EMD09 L1 Y3 EMA0

EMD[9] EMA[0]

EMD10 K1 W4 EMA1

EMD[10] EMA[1]

EMD11 J4 W2 EMA2

EMD[11] EMA[2]

EMD12 J1 V2 EMA3

LANE-1

ADDRESS

EMD[12] EMA[3]

(VMEM)

H2 W1 EMA4

(VMEM)

EMD13 EMD[13] EMA[4]

EMD14 H3 R1 EMA5

EMD[14] EMA[5]

EMD15 G3 P1 EMA6

EMD[15] EMA[6]

R2 EMA7

EMA[7]

[4] L2

EMDQM1 EMDQM[1]

N2 EMA8

EMA[8]

K4 N4 EMA9

[4] EMDQS1_P EMDQS[1] EMA[9]

K3

[4] EMDQS1_N EMDQS_N[1]

[7] EMD[00:31] U2100-B

VREFCA

EMD16 AG4 ASIC-SC9832A-492-0.4

EMD[16]

R5

EMVREFO_CA

EMD17 AJ3

EMD[17] VREFDQ

VREF

(VMEM)

EMD18 AF4

EMD[18]

EMD19 AH3 V5

EMD[19] EMVREFO_DQ

EMD20 AG3

LANE-2

EMD[20]

(VMEM)

(VMEM)

EMD21 AH4

EMD[21]

ZQ

AA2 R2300 240

EMZQ

EMD22 AF1 +/-1%

EMD[22]

EMD23 AG1

EMD[23]

STRAPPIN

[4] AE1 A5

EMDQM2 EMDQM[2] (WPU) NFD[0]/GPIO112

(VNF0)

A6

(WPU) NFD[1]/GPIO113

[4] EMDQS2_P

AF3

EMDQS[2] NC,Don't use as the GPIO

B6

AF2

(WPU) NFD[2]/GPIO114

[4] EMDQS2_N EMDQS_N[2]

B8

(WPU) NFD[3]/GPIO115

[7] EMD[00:31]

E7 [4]

EMMC_D7/GPIO101 EMMC_D7

EMD24 F2

EMD[24]

C7 [4]

EMMC_D6/GPIO100 EMMC_D6

EMD25 F1

EMD[25]

E5 [4]

EMMC_D5/GPIO103 EMMC_D5

EMD26 D2

EMD[26]

B5 [4]

EMMC_D4/GPIO104 EMMC_D4

EMD27 D1

EMD[27]

D4 [4]

EMMC_D3/GPIO106 EMMC_D3

eMMC

EMD28 E4

(VNF1)

LANE-3

EMD[28] [4]

(VMEM)

A3 EMMC_D2

EMMC_D2/GPIO109

EMD29 D3

EMD[29]

B7 [4]

EMMC_D1/GPIO108 EMMC_D1

EMD30 C2

EMD[30]

C4

EMMC_D0/GPIO98 EMMC_D0 [4]

EMD31 C1

EMD[31]

D7 R2301 0

(H) EMMC_CLK/GPIO102 EMMC_CLK [4]

[4] G1

EMDQM3 EMDQM[3]

D5

(WPU) EMMC_CMD/GPIO99 EMMC_CMD [4]

F4 B3

[4] EMDQS3_P EMDQS[3] EMMC_RST/GPIO107 EMMC_RST [4]

F3 B4

[4] EMDQS3_N EMDQS_N[3] GPIO105

B B

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

2015-10-12 Hardware DEPT.

River.Du

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 12 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

MAIN MIC RECEIVER

D D

Close to BB Close to MIC Close to RCV

MIC_BIAS

R0903 510 R0904 1.5K¦¸

R0920 0

[2]EAR_P

J0905 J0910

100pF

PAN00-01120-0107 PAN00-01120-0107

R0943

R0901 1K C0901 0.1uF 1 1

[2] MIC_P

0R J0911

100pF

2.2uF

PAN00-01120-0107

C0909

1

C0905

C0908

J0906

R0944 PAN00-01120-0107 R0921 0

[2]EAR_N

R0902 1K C0902 0.1uF 1

[2] MIC_N

0R

47pF

47pF

1

1

RV0908

47pF

47pF

RV0907

R0905 510 R0906 1.5K¦¸

RV0920

33pF

33pF

RV0921

C0910

C0911

C0906

C0907

T

T

C0903

C0904

2

T

2

GND

C C

HEAD MIC SPEAKER

Close to BB Close to SPK

Close to BB Close to MIC

HEADMIC_BIAS

J0907

PAN00-01120-0107

R0911

1

[2] PAOUT_P

C0942

0R(n.m)

33PF(n.m)

J0908

1K

R0909

PAN00-01120-0107

R912

[2] 1

PAOUT_N

100pF(n.m)

0R(n.m)

C0917 4.7uF

33pF

33pF

T

T

C0918 0.22uF

RV0906

RV0905

R0907 1K C0912 0.1uF

VOP [8]

C0950

[2]

C0922

C0921

HEADMIC_P 100pF

[8]

2K

VON

C0914

GND

R0910

R0908 1K C0913 0.1uF

[2] HEADMIC_N HEADMIC_IN_DET[2,8]

47pF

47pF

C0915

C0916

Cap need used together

Or del together if no EMI issue

Del Cap when change Bead to 0ohm Rs

Note:C0912 C0913 use 1uF Cap

B B

3.5mm Headphone Jack Audio PA

VBAT

B0901 120 OHM

4.7uF

0.1uF

Ear Jack need support:

Close to Jack

C0940

C0941

Earphone Pin 4 & Pin 5

VDD2V8

CLOSE TO PA

Plug in Connect

220K(n.m)

2.2uF

4.7uF

15NF(n.m)

C0936

10K¦¸

C0935 2.2uF

C0923

Pull out Disconnect

C0937

D1

D2

C1

A3

B3

B1

B2

47pF

C0930

R0930

1nF

C2P

VDD

VDD

C1N

C2N

C2N

C1P

R0914

[5] SHDN A4 D3

10K R0913 SHDN PVDD

[2] HP_DET

C0938

R0931

C0931 15nf A2 B4 B0910 120 OHM

220pF

AORN INN VOP

[2]

3K VOP [8]

VON [8]

U0901 AW8736 D4 B0911 120 OHM

C0934

R0932 VON

15NF(n.m)

C0932 15nf A1

J0902 AORP INP

GND

GND

GND

[2]

1nF

PH20-1A30F38A

3K

R0915 33R 1000OHM 1

[2] HP_GDRO_L FB0901

4

C2

C3

C4

5

C0939

[2] HP_GDRO_R R0916 33R FB0902 1000OHM

3

C0933

1000OHM 2

[2,8] HEADMIC_IN_DET FB0903

C0924 1000pF

[17] FM_ANT

600OHM

C0924 closed to earphone connector

10K

10K

T

0.22uF

0.22uF

RV0910

RV0901

RV0902

RV0903

RV0904

FB0904

C0925

C0926

R0935

R0936

fc>=40KHz

R0917 0

[2] AMPG_VCOM

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

River.Du 2015-10-12 Hardware DEPT.

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 13 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D D

VDD2V8

VDD2V8

4.5" HVGA LCM

1UF

T

CTP

RV1024

100K¦¸(n.m)

C1020

R1026

J1002

TP100-W800

1

VDD

2

R1022 100R GND

3

[5] I2C3_SCL 100R SCL

R1023 4

[5] I2C3_SDA 1K SDA

R1024 5

[5] CTP_RST 1K RST

R1025 6

[5] CTP_INT INT

7

GND

8

GND

T

RV1020

RV1021

RV1022

RV1023

TP1001

J

1

0

0

1

VDD2V8

FH26-25S-0.3SHW

CTP_SCL_CON TP1002

1

CAMF_PWDN

2 [5]

MDSI_CLK_P

AGND

3 TP1003

[5]

MDSI_CLK_N SDA CTP_SDA_CON

4

AVDD(2.8V)

5

[5]

MDSI_DATA0_P SCL

6 [5] CTP_RST_CON TP1004

RESET MDSI_DATA0_N

7

VSYNC

8

CAMR_PWDN [5]

MDSI_DATA1_P

[5] 9 TP1005

MDSI_DATA1_N HSYNC CTP_INT_CON

10

DVDD(1.5V)

11

[5]

MDSI_DATA2_P DOVDD(2.8V)

12

Y7 [5]

MDSI_DATA2_N

13

XCLK

14 [5]

Y6 MDSI_DATA3_P

[5]

MDSI_DATA3_N 15

DGND

16

Y5

17

PCLK

18

R1021

1K Y4 LCM_FMARK [5]

[5]LCM_ID 19

Y0

20 LCM_RSTN[5]

Y3

21

VDD1V8 Y1

22

Y2 VDD2V8

23

LCM_LED+ FLASH+

24 LCD_CABC

GND

25 [9]

LCM_LED- FLASH-

26 2

GND 0

27 0

C1014

GND 1

C1015

C

C1003

T

T

C1025

RV1001

100nF

RV1002

2.2uF

100nF

22pF

22pF

1

C

2.2uF

0

0

1

C

C

VBAT

LCD BL

L1001 10uH

U1001

BL8545

D1001 R1016

VIN LX LCM_LED+ [9]

R1050 0OHM 0

[5] LCM_BL_PWM CE OVP

C1012

R1051 0OHM GND FB LCM_LED- [9]

C1007

LCD_CABC

C1006

C1008

5

0

V

[9]

R1030

100K

5.1OHM

R1017

C1010

C1011

22pF

1uF

100nF

4.7uF

10pF(n.m)

C1009

100pF

10pF(n.m)

B B

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

2015-10-12 Hardware DEPT.

River.Du

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 14 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D D

VDDCAMCORE

VDDCAMMOT VDDCAMIO CAM_AVDD

8M Sensor

4.7UF(n.m)

22pF(n.m)

CAM_AVDD

1uF(n.m)

0.1uF

4.7uF

1UF

1uF

C1101

C1102

C1104

C1103

C1106

C1105

C1110

R1125 0

VDDCAMA

4700NF

C1137

J1101

DF37NC-24DS-0.4V

[5,10]I2C0_SCL 1 13

SCL GND

[5,10]I2C0_SDA 2 14

SDA DP3 CAM0_DATA3_P[5]

[5,10] 3 15 [5]

CAM_PWDN1 PDN DN3 CAM0_DATA3_N

[5,10]CAM_RST1 4 16 [5]

5 RST CLKP 17

CAM0_CLK_P

GND CLKN [5]

CAM0_CLK_N

6 18 [5]

VDDCAMCORE 7 DVDD DP0 19 CAM0_DATA0_P

VDDCAMMOT VDDVCM DN0 CAM0_DATA0_N [5]

8 20 [5]

VDDCAMIO 0R R1110 VDDIO DP1 CAM0_DATA1_P

9 21 CAM0_DATA1_N [5]

VBAT VBAT DN1

10 22

CAM_AVDD AVDD DP2 CAM0_DATA2_P[5]

11 23

[2] FLASH_SINK R1120 0R FLASH_SINK DN2 [5]

CAM0_DATA2_N

[5,10]CAM_MCLK 12 24

MCLK GND

C1116

[5,10]CAM_RST1

[5,10]

CAM_PWDN1

22pF(n.m)

1

RV1105

RV1104

22pF

22pF

C C

T

T

2

2

C1138

C1139

VDDCAMIO CAM_AVDD

5M Sensor

1UF

1uF

1UF

C1111

C1112

C1125

B B

Refer to M8010

J1102

DF37NC-24DS-0.4V [5,10]

CAM_PWDN0

R1126 0 0 CAM_RST0[5,10]

1 13 R1121 [5,10]

CAM_MCLK

VDDCAMCORE DVDD MCLK

2 14

3 GND 15

IOVDD [5,10]

CAM_PWDN0

VDDCAMIO 4 PDN 16

AVDD GND

CAM_AVDD 5 17 CAM1_CLK_P[5]

22pF

GND CLKP

22pF

6 18 CAM1_CLK_N[5]

GND CLKN

7 19

GND GND

8 20 [5]

CAM1_DATA0_P

GND DP0

9 21 [5]

C1108

CAM1_DATA0_N

C1144

NC DN0

CAM_RST0 [5,10] 10 22

RST GND

11 23

22pF(n.m)

I2C0_SDA [5,10] [5]

CAM1_DATA1_P

10pF(n.m)

SDA DP1

I2C0_SCL [5,10] 12 24 [5]

CAM1_DATA1_N

SCL DN1

22pF

1uF

C1114

C1109

C1161

C1117

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

2015-10-12 Hardware DEPT.

River.Du

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 15 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D D

G Sensor

C C

VDD1V8 VDD2V8 VDD1V8

U1201

BMA220

3

VDDIO

1

330¦¸(n.m) SDO

[5,11] I2C2_SDA R1206 2 4

SDI VDD

R1207 330¦¸(n.m) 12

Default 3D BMA223

[5,11] I2C2_SCL SCK

C1207

10 7

CSB VDDA

11

PS

INT_G 5 8

INT GND

C1206

[5] R1210 0R(n.m) 6 9

2.2uF(n.m)

CAP0 GND

n.m

100nF(n.m)

B B

ALS VDD1V8 VDD2V8

2.2uF(n.m) VBAT

100K(n.m)

R1201

C1204

U1203

TMD27723

4.7uF(n.m)

1 4

VDD LEDA

[5,11] R1202 330(n.m) 2 6

I2C2_SCL SCL LDR

T

[5,11] I2C2_SDA R1203 330(n.m) 8 5

SDA LEDK

C1205

RV1201

7 3

[5] PROX_INT INT GND

n.m

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

River.Du Hardware DEPT.

2015-10-12

DATED:

EQA: COMPANY:

Mulder.Han

2015-10-12 Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu CONFIDENTIAL AND PROPRIETARY SHEET: 16 OF 23

2015-10-12

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D D

BATTERY 5pin Micro USB

TB1303

USB BOOT CONTROL

TB1301

TB1306

Battery temperature monitor VDD1V8

NBOOT = Float----->NAND BOOT

If not use,BAT_TEMP_ADC connect to GND

1

NBOOT = 0 ----->USB BOOT

1

TB1302

47K

VBAT

VCHG

PBINT2 is only for auto power on.

R1306

3

2 4

ESDH7V0P1

D1305

If ESD test FAILURE, Put on the MLVs and TVSs

3

R1305 510 1

1uF

[3] BAT_TEMP_ADC

1

GND

D1306

0.1uF

22uF

VDD VOUT

470pF

NC

PAN26-03356-S105

C1305

NC

NC

2

1

2

J1301

1

1

10K(n.m)

GND

R1310

C1304

D1309

C1303

TB1304 TB1308

D1308

C1302

D1307

VDD VOUT [3]

SENSE_P

2

2

2

ESDH7V0P1

0.02

J1302

MICROUSB_KIU90511S1R_HOLEP0.1MMYD

R1307

1

VBUS TB1305

R1308 0 [3] 2 [2] R1309

SENSE_N 6 D- CON_USB_DM 1K

F [2] PBINT2

7

F 3

8 D+ CON_USB_DP [2]

F

9

F 4

ID

2

5

GND

T

RV1308

2

2

T

1

RV1306

RV1307

1

1

C C

CHARGE

OVP

VCHG_D [3]

R1325

0(NF)

R1320

ISENSE [3]

U1302

6 1 VBUS_5V

D D

10K

VBUS_5V R1321 [3,12]

VBAT_SENSE [3] 5 2

D D

U1301

R1303

VCHG 4 3

S G

4 1 [12]

D C

4.7uF

10

D C

7 should afford 1A current PPM6N30V9

PPT3FD503E0-2 Q1301

E

[3] VDRV 6 8

S C

B B

C1321

R1302 R1304 0.068ohm VBAT

3 9 B

B C

1nF

100R

100K

2

E G

5

Pt>1W hREF=100~300 @0.5A Ic>1A

2

C

T

C1320

MI2551

RV1309

R1316

1

1nF

30KOHM

2 T 1

B A

Vgs(th)<1.5V Rds(0n)<10R D1303

C1319

10000OHM

R1315

GND

R1317

GND

GND

1

SC_01 AP_Sheiding Cover T1

MARK-1.0

1

T2

MARK-1.0

1

TB1312

1

SC_02

RF_Sheiding Cover T3

1

T4

1

WCN_Sheiding Cover

1

SC_03

MARK-1.0 MARK-1.0

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

2015-10-12 Hardware DEPT.

River.Du

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 17 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D D

V

o

l

u

m

e

+

K

e

y

:

K

E

Y

I

N

0

+

K

E

Y

O

U

T

0

TM1403TM1404TM1405TM1406

V

I

B

R

A

T

O

R

C C

R1401 1K(n.m) EXTRSTN [2]

J1401

OK_03NF10_04

1 10 R1402 1K [5]

KEYOUT0 J1404

2 9 PAN00-01120-0107

KEYIN1 [5]

K

E

Y

I

N

0

R1403 1K

[

5

]

8 R1410

3 1

7 R1404 1K VIB_CTRL [3]

4

5 6 0R

R1407 1K

PBINT [2]

J1405

PAN00-01120-0107

1

RV1404

RV1403

RV1402

RV1401

1uF

T

T

T

T

C1405

GND

GND

B B

UART POINT Test Points TM1401 TM1402

[5] BB_U1RXD R1405 1K

T1411 T1410

[5] [5] R1406 1K

BB_U4RXD BB_U1TXD

BB_U4TXD [5]

RV1411

RV1410

T

T

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

2015-10-12 Hardware DEPT.

River.Du

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 19 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D D

SIM0 & SIM1&T-Flash 3in1

VDDSDCORE

100K(n.m)

R1501

NC

03-202113H

J1501

20 VDDSIM1

S_VCC

19 [5]

TF_SD0_D2

DAT2

1 18 [5]

S_GND CD/DAT3 TF_SD0_D3

2 17 [5]

S_VPP CMD TF_SD0_CMD

SIM1_DA 3 16

S_IO VDD VDDSDCORE

[5]

4 15 [5]

MS_GND CLK TF_SD0_CLK0

5 14

MS_VPP VSS

SIM0_DA 6 13 [5]

TF_SD0_D0

MS_IO DAT0

[5]

SIM0_RST 7 12 [5]

TF_SD0_D1

MS_RST DAT1

[5]

SIM0_CLK 8 11

MS_CLK S_RST SIM1_RST [5]

[5]

GND

GND

GND

GND

9 10 SIM1_CLK [5]

VDDSIM0 MS_VCC S_CLK

C1510

C1511

C1512

C1514

C1515

C1516

C1503

C1504

C1506

C1505

21

22

23

24

C1501

C1502

T

T

T

T

T

T

RV1506

RV1508

RV1505

RV1504

RV1501

RV1507

RV1503

RV1502

22pF

22pF

22pF

22pF

22pF

22pF

22pF

27PF

1uF

27PF

C C

ENHANCE_ELEMENT2

J1502

B Rear cam enhance_element B

3

1

2

ENHANCE_HOLE2ENHANCE_HOLE2 ENHANCE_HOLE2ENHANCE_HOLE2

1 1 1 1

J1504 J1506 J1508 2 J1510 2

2 2

PCB enhance_hole

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

2015-10-12 Hardware DEPT.

River.Du

DATED:

EQA: COMPANY:

Mulder.Han 2015-10-12

Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu 2015-10-12 CONFIDENTIAL AND PROPRIETARY SHEET: 20 OF 23

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

Diversity LTE Path AVDD2V8

TRANSCEIVER

J0602 J0603

J0601

1 1 1

1

1 1

D D

U0600

100nF

4.7uF

100nF

100nF

J0604

10pF

10pF

10pF

10pF

10pF

100nF

100nF C0640 SKY13418-485LF VDDDCXO

R0612 0¦¸ R0615 0¦¸

2 1

4 3 SW_DRX_FDD/WCDMA_B2 [15]

VDD RF1 VDDRF0

C0628

C0629

C0650

C0647

C0648

C0649

C0657

C0631

C0630

C0658

9 [15] U0610

RF2 SW_DRX_FDD_B7 VDDWRF VDDRF0

0¦¸

0¦¸

6

5

4

3

SR3593G

0¦¸

C0609 47pF 13 2

NC

ANT RF3 SW_DRX_FDD_B28B [15]

C0604

L0605

10

RF4 SW_DRX_FDD/WCDMA_B4 [15] RF

0¦¸

10NH

[5] RFCTL_0 5 1

V3 RF5 SW_DRX_FDD_B28A [15] POWER DECOUPLE

0¦¸

NC

R0630

[5] 6 11 SW_DRX_FDD_B5[15]

RFCTL_1 V2 RF6 100nF C0639

L0602

K5 B1

VDD1V8XO RX_CAP1V5

[5] 7 14

V1 RF7

R0631

RFCTL_2

12 E10

R0632

RF8 RX_CAP1V8

H15 100nF C0638

VDD1V8TX (width>=0.3mm)

15 8

GND N/C

J8

RX_CAP_SYN

100nF C0637

J6

VDD1V8RF (width>=0.3mm)

RX IQ

K3 R8 L0666 47nH

VDD1V5RF (width>=0.3mm) RX_IP RXIP_MADC [5]

0¦¸ R0633

P7 L0667 47nH RXIN_MADC [5]

RX_IN

K7 P9 L0668 47nH

VDD1V1DIG RX_QP RXQP_MADC [5]

N8 L0669 47nH

RX_QN RXQN_MADC [5]

DET

DIV ANT SAME WITH LA [16] RF_POWER_DET

R0619 27¦¸ J14

RF_PDET

DRX IQ

150¦¸

M13 L0670 47nH

DRX_IP RXIP_MADC_DIV [5]

150¦¸

GRX DRX_IN

N14 L0671 47nH

RXIN_MADC_DIV [5]

A14 P15 L0672 47nH

GRX_LB (GSM LB ONLY, 729-960MHz) DRX_QP RXQP_MADC_DIV [5]

47nH

R0620

B15 R14 L0673

GRX_HB (GSM/TDS ONLY, 729-960MHz) DRX_QN RXQN_MADC_DIV [5]

R0621

FDD_B28A_Diversity TRX path NC

Diversity TDDLTE RX Path

PRX TX IQ C0616 4.7pF

U0602

R0626 0¦¸

SAFFB773MAA0F0A [16] B7 P11 [5]

RF_RX_FDD/WCDMA_B5 PRX_L0 TX_IP TXIP_MDAC

R0627 0¦¸

C0615 22PF 1 4 C0614 47pF C0654 2nH R10

RF_DRX_FDD_B28A [15] TX_IN [5]

5.1nH

[15] SW_DRX_FDD_B28A UBLN1 UBLN2 B3 0¦¸ TXIN_MDAC

R0628

2.7pF

PRX_L1

P13

3.9nH

TX_QP TXQP_MDAC [5]

2 R0629 0¦¸

GND1 A2 R12

[16] RF_RX_FDD_B28A PRX_L2 (ALL BAND, 699-960MHz) TX_QN NC TXQN_MDAC [5]

5 3

FDD_B7_Diversity TRX path GND3 GND2 4.7pF

L0651

C0617

L0610

L0611

[16] RF_RX_FDD_B28B B5

U0603

PRX_L3 SPI

SAFFB2G65AA0F0A

[16] A4 L14 SPI_LE_RF0 [5]

RF_RX_GSM900 PRX_L4 SPI_LE

C0612 22PF 1 4 C0613 47pF L0617 2nH

[15]

5.1nH

[15] SW_DRX_FDD_B7 UBLN1 UBLN2 RF_DRX_FDD_B7 M15

SPI_CLK SPI_CLK_RF0 [5]

2.7pF

A6

[16] PRX_M1

3.9nH

RF_RX_DCS

2

GND1

CLOSE TO U0610 SPI_DATA

L16

SPI_DATA_RF0 [5]

A8

5 3 [16] RF_RX_FDD_B4 PRX_M2 (ALL BAND, 1710-2170MHz) R0614

GND3 GND2 0R

C0618

RTC

L0616

L0615

[16]

RF_RX_FDD/W/PCS_B2 B9

PRX_M3

M1

FDD_B28B_Diversity TRX path U0604

A10

PRX_H1

XO_MODE

M3 R0613 0R(n.m)

[2]

DCXO_LOW_CUR

CLK_32K [2]

PMU_32K_IN

C CLOSE TO U0610

SAFFB788MAA0F0A

[16] RF_RX_FDD_B7

B11

PRX_H2

C

22PF 47pF 2nH

C0621 1 4 C0622 L0623

RF_DRX_FDD_B28B [15]

(ALL BAND, 2110-2690MHz) CLK

5.1nH

[15] SW_DRX_FDD_B28B UBLN1 UBLN2

2.7pF

A12

3.9nH

PRX_H3

2 P1

REFOUT1

GND1

B13 NC

5 3 PRX_H4

GND3 GND2 N2 C0632 1NF

C0623

[17]

L0622

REFOUT2 WB_26M_IN

L0621

DRX P3 C0635 1NF

AP_26M_IN [5]

REFOUT3

[15] G2

RF_DRX_FDD/WCDMA_B5 DRX_L0 C0636 1NF

R6 CP_26M_IN [5]

RF_CLK

CLOSE TO U0610 L2

DRX_L1

H3 T1

[15] RF_DRX_FDD_B28B DRX_L2 (ALL BAND, 699-960MHz) XO_P TRANS_26M_IN [15]

J2 R2

[15] RF_DRX_FDD_B28A DRX_L3 XO_N XO_N [15]

K1

DRX_L4 NC

H1 A16

DRX_M1 NC-1

J16

NC-2

[15]RF_DRX_FDD/WCDMA_B4 F3

DRX_M2 (ALL BAND, 1710-2170MHz)

K15

NC-3

E2 N4

[15] RF_DRX_FDD_B2 DRX_M3 NC-4

Diversity FDDLTE/WCDMA RX Path

R4

NC-5

F1

DRX_H1

R16

NC-6

D3 T3

DRX_H2 NC-7

(ALL BAND, 2110-2690MHz)

T5

NC-8

D1

[15] RF_DRX_FDD_B7 DRX_H3

T9

NC-9

C2 T15

DRX_H4 NC-10

FDD/WCDMA_B5_Diversity Rx path TX GND

U0609

D15

SAFFB881MAN0F0A TX_LB1

D7

47pF 18nH VSS-1

C0643 100pF 1 4 C0633 C0644 E14

[15] SW_DRX_FDD_B5 UBLN1 UBLN2 RF_DRX_FDD/WCDMA_B5 [15] [16] RF_TX_LB_T/R_PAM TX_LB2 (ALL BAND, 699-915MHz)

D9

VSS-2

2.2pF

7.5nH

2 C14 D13

GND1 [16] RF_TX_LB_GSM TX_LB3 VSS-3

0¦¸

5 3 E8

GND3 GND2 VSS-4

NC

C16

L0618

[16] RF_TX_HB_GSM TX_HB0

F5

L0620

L0619

VSS-5

[16] F15 F9

RF_TX_MB_T/R_PAM TX_HB1 VSS-6

(ALL BAND, 1710-2690MHz)

G6

VSS-7

E16

TX_HB2

CLOSE TO U0610 22pF

VSS-8

G10

[16] RF_TX_HB_T/R_PAM C0688 G16 M11

TX_HB3 VSS-9

C0689

2.2pF

B B

CLOSE TO U0610 1uF(NF) C0651

3.9nH

R0653 100K NC

GPS_TSEN_VREFP

[17]

FDD/WCDMA_B2_Diversity Rx path[MATCH]

4.7pF

NC

R0652 NC 0¦¸

[17] GPS_TSEN_IN

L0631

L0600

U0608

[15] SW_DRX_FDD/WCDMA_B2

C0646 39pF 1

SAFFB1G84AB0F0A

UBLN1 UBLN2

4 C0641 1nH C0655 3nH

RF_DRX_FDD_B2 [15]

co-pad VDDDCXO

R0640 0¦¸

3.6nH

TRANS_26M_IN' [17]

5.1nH

2

GND1 R0601 0¦¸ NC

5 3 X0600

GND3 GND2

L0639

1XXB26000MAB

NC

C0600 1NF 3 4 C0601 10pFNC

L0614

[15] TRANS_26M_IN OUT VCC

NC

R0650 0¦¸ 2 1 R0600 0¦¸

GND2 GND1

NC

R0651 0¦¸

[17]

GPS_TSEN_VREFN

NC

XO_N[15]

Dual TCXO/VCTCXO+TCXO/Share TCXO

26M Configuration X0600 Y1801 C0600 C0636 C0635 C0632 C1808 C1817 C1809 C1834 R0640 R0600 R0602 C0601 R1812 R1813

Dual TCXO TCXO TCXO 1000pF 1000pF 1000pF 0ohm NF 1000pF NF 1000pF NF NF 0 ohm 10pF NF 0 ohm

FDD/WCDMA_B4_Diversity Rx path[MATCH] VCTCXO+TCXO VCTCXO TCXO 1000pF 1000pF 1000pF 0ohm NF 1000pF NF 1000pF NF 0 ohm NF 10pF NF 0 ohm

U0607

SAFFB2G14AA0F0A

C0652 39pF 1 4 C0642 0.6nH C0608 3nH

Defualt Share TCXO NF TCXO NF 1000pF 1000pF NF 1000pF NF 1000pF 1000pF 0 ohm NF 0 ohm NF 0 ohm NF

[15]SW_DRX_FDD/WCDMA_B4 UBLN1 UBLN2 RF_DRX_FDD/WCDMA_B4 [15]

3.6nH

5.1nH

3pF

2

4.7pF

GND1

4.7pF

NC

NC

5 3

L0640

GND3 GND2

L0641

L0633

L0613

L0647

CLOSE TO U0610

A Band info VDD1V8

A

VDD1V8

10K¦¸

10K¦¸

20K(NF)

NC

R0606 NC

R0610

R0605

HW_VER_ADC [2]

[5] BOARD_ID0 ADC/GPIO 00 01 10 11 TITLE & REV:

20K¦¸

[5] BOARD_ID1 SP9832A-2_CS_SCH_V0.1.0

10K¦¸

10K¦¸

0 reserved reserved reserved reserved DOCUMENT NO.:

R0603

R0607

R0604

1 reserved reserved reserved reserved

DESIGNER: DATED: DEPARTMENT:

River.Du Hardware DEPT.

2 reserved reserved reserved reserved 2015-10-12

DATED:

EQA: COMPANY:

Mulder.Han

3 reserved reserved reserved reserved 2015-10-12 Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu CONFIDENTIAL AND PROPRIETARY SHEET: 9 OF 23

2015-10-12

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

Primary Antenna

TD/GSM PA + Switch

J0405 J0403

J0404 J0402

1 1 1 1 0¦¸ R0420 2 1 C0438 47pF

1 1 ANT_CON [16]

12nH

10nH

NC

1.2pF

1.2pF

Primary TRX Path FDD/WCDMA

NC

NC

VBAT

6

5

4

3

0¦¸

L0423

C0460

C0459

L0424

R0412

GND

5.6nH

R0403

C0433 22pF

10uF

RF_POWER_DET[15]

0¦¸

3.3pF

47pF

U0406

1

FDDLTE_B4

RV0403

RV0404

SAYEY1G95GA0F0A

L0478

C0489 47pF

D ANT_CON [16]

D

10nH

C0432

5.6PF 47pF

3.3pF

[16] C0445 6 3 C0447

C0431

SW_TRX_FDD_B4 PAM_TX_FDD_B4[16]

C0430

3.3pF

ANT TX

3.3pF

3.3pF

3.3pF

T

2

2

U0408 47pF 1.5nH 1.5nH

2.7nH

1 C0446 C0479 C0498

RX RF_RX_FDD_B4[15]

5

C0434

MXD8528

C0428

C0436

GND3

2.4nH

10

19

17

22

C0405

C0435

3.3nH

9

L0459

4 8

3.9pF

NC1

CPL

VBATT

VCC

ANT

NC GND2 GND5

1 9 37

RF1 GND TRX1 2 7 NC

C0482

GND1 GND4

L0435

C0484 47pF C0246 2.4nH 3 36

6.8nH [15] RF_TX_HB_GSM HB_IN TRX2

L0496

L0412

L0404

35

L0436

TRX3 SW_TRX_FDD_B28A [16]

CLOSE TO U0610

47pF

8

ANT RF2

7 C0487 39pF

TRX4

34 SW_TRX_FDD_B7 [16] CLOSE TO U0610

C0427 47pF 2 33 SW_RX_GSM900 [16]

[15] RF_TX_LB_GSM LB_IN TRX5

VDD

5 AVDD2V8 [3,6,15]

32 SW_RX_DCS [16]

TRX6

[5] RF_ANTSWITCH_EN 4 2 31 SW_TRX_FDD/WCDMA_B5 [16]

EN GND TRX7

U0401

[5] RFCTL_4 3 6 [5] R0402 1.5K¦¸ 8 30 SW_TRX_FDD_B28B [16]

VC GND RF_PA_RAMP VRAMP SKY77916-11 TRX8

29 [16]

TRX9 SW_TRX_FDD_B4

100nF

470pF

100nF

6.8nH

C0429

100nF

39pF

28

TRX10 SW_TRX_FDDLTE/W/PCS_B2[16]

R0425 1.5K¦¸ 5 27

[5,16] RFFE_SCLK0 SCLK TRX11

C0483

C0481

C0486

C0485

R0426 1.5K¦¸ 6 26

L0495

[5,16] RFFE_SDA0 SDATA TRX12

7 25

VDD1V8 VIO TRX13

100nF

EPGND

GND10

GND11

GND12

GND13

24

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

TRX14 NC

470pF

470pF

3.3nH

L0473

C0437

11

12

13

14

15

16

18

20

21

23

38

39

GND GND GND

GND GND

FDDLTE/WCDMA/PCS_B2 U0412

C0488

C0490

SAYEY1G74BC0B0A

C0448 47pF 6 3 L0479 1.5nH

[16] SW_TRX_FDDLTE/W/PCS_B2 ANT TX PAM_TX_FDD/W_B2[16]

1 C0449 1.2nH C0477 47pF C0499 3.9nH

18nH

RX RF_RX_FDD/W/PCS_B2 [15]

NC 5

GND3

3.3nH 4 8

L0405 GND2 GND5

2 7

GND1 GND4

L0476

L0477 L0420

3.9pF 3.9pF

CLOSE TO U0610

Primary RX Path GSM/TDS

3.3nH

NC

FDDLTE/WCDMA_B5 U0413

L0446

SAYEY836MBA0F0A

C0455 2.7nH 47pF

C [16] SW_TRX_FDD/WCDMA_B5

6

ANT TX

3 C0457 PAM_TX_FDD/WCDMA_B5 [16] C

47pF

8.2nH

1 C0456 R0410 15nH

RX RF_RX_FDD/WCDMA_B5 [15]

18nH

5

3.3nH

GND3

DCS_RX

3.3nH

NC

4 8

GND2 GND5 NC

2 7

GND1 GND4

L0486

U0410

L0406

L0487

F6QA1G960M2AP

L0485

C0450 47pF 1 4 C0452 47pF R0455 3.6nH

[16] SW_RX_DCS UBLN1 UBLN2 RF_RX_DCS [15]

3.9nH

3.3nH

NC

3.3nH

1pF

NC GND1

5

GND3 GND2

3

CLOSE TO U0610

L0458

R0450

R0451

L0456

CLOSE TO U0610

3.3nH

U0402

L0444

NC

FDDLTE/WCDMA_B7 C0442

2.7nH

SAYEY2G53BA0F0A

47pF

[16] 6 3 C0444 PAM_TX_FDD_B7 [16]

SW_TRX_FDD_B7 ANT TX

8.2nH

1 C0411 47pF 12nH L0418

3.3nH

RX RF_RX_FDD_B7 [15]

5

GND3

6.8PF

1pF

1pF

4 8

GND2 GND5

NC

NC

L0443

NC

L0442

NC 2 7

C0418

GND1 GND4

C0419

C0421

GSM_900 U0407

F6QA1G960M2AP

C0491 47pF 1 4 C0492 47pF L0428 3.6nH

[16] SW_RX_GSM900 UBLN1 UBLN2 RF_RX_GSM900 [15]

CLOSE TO U0610

3.9nH

3.3nH

2

1pF

3.3nH

NC

NC GND1

5 3

GND3 GND2

C0493

L0422

L0421

L0427

CLOSE TO U0610

3.3nH

U0403

FDDLTE/WCDMA_B28A

L0445

SAYEY2G53BA0F0A

NC

C0443 2.7nH 47pF

6 3 C0453 PAM_TX_FDD_B28A [16]

[16] SW_TRX_FDD_B28A ANT TX

8.2nH

3.3nH

1 C0454 47pF 12nH L0447

RX RF_RX_FDD_B28A [15]

B 5

GND3 B

6.8PF

1pF

1pF

4 8

LTE/WCDMA PAM

GND2 GND5

NC

NC

NC

L0450

NC 2 7

C0461

GND1 GND4

C0462

L0451

C0463

VDDWPA VDDWPA

VBAT

CLOSE TO U0610

10pF NC

1NF

1uF

1NFNC

10pF

1uF

10pF

1NF

1

1

RV0401

RV0402

C0414

C0415

C0416

C0402

C0401

C0400

C0404

C0403

T

T

2

3.3nH

FDDLTE/WCDMA_B28B

U0404

L0448

SAYEY2G53BA0F0A NC

29

30

28

10

11

8

9

0¦¸

0¦¸

C0464 47pF

NC

2.7nH 6 3 C0467 PAM_TX_FDD_B28B [16]

VCC1

VCC2

VCC2_2

NC1

NC2

NC3

NC4

VBATT

ANT TX

[16] SW_TRX_FDD_B28B

NC

8.2nH

3.3nH

1 C0468 47pF 12nH L0467

RX RF_RX_FDD_B28B [15]

5

3.3nH

GND3

3.3nH

L0414

L0400

1pF

6.8PF

NC

1pF

T/R2 42

NC 4 8

47pF GND2 GND5

[15] C0410 3 RFIN_H

RF_TX_HB_T/R_PAM

L0464

T/R1 41 2 7

C0466

L0425

L0429 GND1 GND4

L0426

3.3nH

L0465

C0469

C0472

NC

NC

NC

B41 39 NC

6 SCLK

[5,16] RFFE_SCLK0

B40 37

5 SDATA

[5,16] RFFE_SDA0 B7 35 47pF

C0425 PAM_TX_FDD_B7 [16]

VDD1V8

7 VIO

B38 33

CLOSE TO U0610

100nF

B34/39 32

MB4 26

C0422

MB3 25

MB2 23 C0412 47pF

PAM_TX_FDD/W_B2[16]

U0400 MB1 21 C0417 47pF [16]

PAM_TX_FDD_B4

RF-PAM-SKY77643-11 LB5 20 C0440 47pF PAM_TX_FDD_B28A [16]

C0406 47pF C0470 47pF 12 RFIN_M LB1 19

[15] RF_TX_MB_T/R_PAM

LB2 18 C0420 47pF

PAM_TX_FDD/WCDMA_B5 [16]

LB3 17

C0480 3.9nH C0407 10nH C0471 47pF 13 RFIN_L

12nH

[15] RF_TX_LB_T/R_PAM

A LB4 16 C0441 47pF

PAM_TX_FDD_B28B [16] A

3.9pF

3.3nH

1.5pF

NC

3.3nH

1pF

EPGND1

EPGND2

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

3.3nH

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

12nH

L0440

12nH

NC

L0417

L0415

L0403

L0416

14

15

22

24

27

31

34

36

38

40

43

44

45

46

47

48

49

50

NC

L0409

NC

L0407

L0419

L0441

NC

NC

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

River.Du 2016-06-06 Hardware DEPT.

DATED:

EQA: COMPANY:

Mulder.Han 2016-06-06 Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu CONFIDENTIAL AND PROPRIETARY SHEET: 7 OF 23

2016-06-07

6 5 4 3 2 1

REVISION RECORD

LTR ECO NO: APPROVED: DATE:

D BT&WIFI&GPS ANT MARLIN D

2

4

6

U7205

GND

GND

GND

1 R1803 0¦¸

HF DPX_WF [17]

R1801 0¦¸

ANT

5 3

1.8pF

LF

VDDWIFIPA

NC

CO-PAD

C11836

J1801 J1802

10uF(nf)

10uF(nf)

1 0¦¸ R1826 R1802 0¦¸

27pF

1 1 1 DPX_ANT [17]

NC

0¦¸

0¦¸

[17]

C1812

C1836

C1830

DPX_GPS

NC

NC

R7213 For External Diplexer VDD1V8

C1822

C1821

R7206 For Internal Diplexer U1801-A

BWFG-SC2342A-175-0.4

If you need better RF performance,please use the external diplexer

BT/WIFI/FM

1uF

POWER INPUT UART

C1811

L12 E18 [5]

AVDD33_PA U0TXD BT_U0TXD

E17 [5]

VDDWCN U0RXD BT_U0RXD

A14 D17

DVDD18_IO U0RTS BT_U0RTS [5]

C17

GPS SAW LNA

U0CTS BT_U0CTS [5]

B18

DVDD16_CORE

D18

U1TXD

G8 SDIO

GND

VDDSIM2 AVDD16_TRX_ISM

A12

SD_CLK WF_SD1_CLK [5]

E9 A13

AVDD16_AFE SD_CMD WF_SD1_CMD [5]

A15 [5]

SD_D0 WF_SD1_D0

M15

AVDD16_FM

B15

C1802 1NF SD_D1 WF_SD1_D1 [5]

27pF C1813 INTERNAL B16 U1801-C

SD_D2 WF_SD1_D2 [5]

1uF

D9

1uF

AVDD13_AFE BWFG-SC2342A-175-0.4

C1814 B17

C1807

C1805

U1803 1uF [5]

1uF

SD_D3

1uF

WF_SD1_D3

AW5015DNR

C1806

IIS GND

C1804

R1804 0¦¸ A17

[17] DPX_GPS DVDD11_CORE

GND

27pF C1815 B10

U7204

2 3 C1803 33pF IISDI BT_PCM_IN [5] GND

CO-PAD SAFFB1G56KB0F0A VDD RFOUT GPS_RF_IN [17] C1816 A10 B13 G16

1uF [5]

1561.1/1575.42/1601.72MHz

RF IISDO BT_PCM_OUT VSS VSS

R1805 0¦¸ 2.0nH L1808 1 4 C1820 33pF L1807 9.1nH 5 B11 B14 H3

[17] DIP_GPS_OUT UBIN UBOUT RFIN 47pF IISCLK BT_PCM_CLK [5] VSS VSS

1 [17] C1630 M6

GND1 DPX_ANT DIP_ANT_IN

C11 C3 J5

2.0nH

8.2nH

NC IISLRCK BT_PCM_SYNC [5] VSS VSS

2 6 4

GND1

1.8pF

GPS_LNA_EN EN GND2

1.8pF

M8 C5 H5

5 3 [17] [17] DIP_RF_IN DIP_WF_IN GPIO VSS VSS

GND3 GND2

NC

L17 C6 H10

NC

GPIO0 WF_WAKE_HOST [5] VSS VSS

M10

C1801

[17] RF_ISM_P RF_ISM_P

C1631

L1810

L1601

K17 [5] C10 H11

GPIO1 BT_WAKE_HOST VSS VSS

H9

RF_ISM_N

C GPIO2

J17

BT_HOST_WAKE [5] C12

VSS VSS

H12

C

H17 C14 H13

C1618 10pF(nf) FM GPIO3 WF_COEXIST [5] VSS VSS

C15 H14

L1602 27nH M14 CLK VSS VSS

[8] FM_ANT FM_LANT

B9 C16 H15

OSC_26M WB_26M_IN1 [17] VSS VSS

L14 D3 H16

FM_SANT VSS VSS

L18 [5,17]

CLK_32K CON_32K_IN

D4 J3

VSS VSS

CTRL JTAG D5 J7

VSS VSS

[5] J18 F17

WB_RST RST_N MTCK WCN_LTECOEXIST_TX [5] D6 J8

VSS VSS

F18

MTDO

WIFI/BT SAW LNA

[2] WB_CLK_REQ A9 D10 J9

XTLEN VSS VSS

H18

MTDI

D11 J10

VSS VSS

M17 G17 WCN_LTECOEXIST_RX [5]

PTEST MTMS

D12 J11

VSS VSS

1 of 3 D13 J12

VSS VSS

D14 J13

VSS VSS

D16 J15

VSS VSS

E3 J16

VSS VSS

E4 K5

VSS VSS

R1807 0¦¸ U1802 E5 K6

[17] DPX_WF RF-SAW-SAFEA2G45MC0F0A VSS VSS

CO-PAD 2441MHz E6 K8

VSS VSS

R1808 NC

0¦¸ 1nH C1826 4 1 2.0nH L1802 E8 K10

[17] DIP_RF_IN UBLAN UBLAN RF_ISM_P [17] VSS VSS

GND

GND

GND

4.3nH

E10 K11

0.5pF

4.7nH

VSS VSS

E12 K12

5

VSS VSS

NC

GE2

E14 K13

C1810

VSS VSS

L1805

L1803

E16 K14

VSS VSS

F3 K16

VSS VSS

F4 L1

VSS VSS

F5 L2

VSS VSS

F6 L4

VSS VSS

F8 L5

VSS VSS

F9 L6

VSS VSS

F10 L7

VSS VSS

F11 L8

VSS VSS

F12 L9

VSS VSS

F13 L10

VDD1V8 VSS VSS

DPX selection F15

VSS VSS

L11

VALUE R7213 R7206 R7224 R7223 R7253 R7252 G4

VSS VSS

L13

G5 L15

VSS VSS

External DPX 0ohm NF 0ohm NF 0ohm NF U1801-B

H2 L16

BWFG-SC2342A-175-0.4 VSS VSS

VDDWCN

Internal DPX NF 0ohm NF 0ohm NF 0ohm G9

VSS VSS

M2

GPS

1uF

1uF

G10 M5

VSS VSS

POWER INPUT UART G11 M7

VSS VSS

C1832

C1833

B4 C4 GPS_U0TXD [5]

GE2_VDDIO GE2_UART_TXD

G12 M9

VSS VSS

H1 B3

GE2_VDDIO GE2_UART_RXD GPS_U0RXD

B JTAG

[5] G13

VSS VSS

M11

B

G14

VSS

3 of 3

A6 B2

GE2_DVDD16_CORE GE2_MTCK

A2 [5]

GE2_MTDO GPS_U0CTS

E7 B1

GE2_AVDD16_AFE GE2_MTDI GPS_U0RTS [5]

C2

GE2_MTMS

H6

GE2_AVDD16_RX_VCO

SPI

1uF

1uF

1uF

1uF C1825 INTERNAL G3

GE2_SPI_CLK

G7

GE2_AVDD13_AFE

C1827 G2

C1819

C1823

C1824

27pF GE2_SPI_DO

A5 F2

GE2_DVDD11_CORE GE2_SPI_DI

27pF C1828

J1

GE2_SPI_CS

1uF C1829

RF

3pF C1831 J4

[17] GPS_RF_IN GE2_RF_IN GPIO

L1811

0¦¸

M4 F1

[17] DIP_GPS_OUT DIP_GPS_OUT GE2_GPIO0 GPS_GPIO0 [5]

VDDDCXO

NC C1

GE2_GPIO1

3.3nH

A1

R1806

A1_NC

A18

A18_NC CLK

M1 D2

M1_NC GE2_CLK_32K CON_32K_IN [5,17]

NC

M18

M18_NC 1NF C1851 [15,17] Y1801

H7 WB_26M_IN

GE2_VCO_MONITOR TG-5006CG-12H

CTRL

B5 D7 1NF C1834 3 4

GE2_T_DIG GE2_XO_IN OUT VCC

A3

[5] GPS_PDN GE2_CHIP_EN TSEN 26MHz

C1835

NC K1 B6 GPS_TSEN_VREFP 2 1

[17] GPS_LNA_EN GE2_LNA_EN GE2_TSEN_VREFP 1NF GND2 GND1

1uF

[15] C1808

E2 C7 [15] TRANS_26M_IN'

0¦¸

GPS_TSEN_IN

R9

[5] GPS_CLK_REQ GE2_XTLEN GE2_TSEN_IN

0¦¸ R1814 [15]

E1 B7

C1818

22pF

GE2_PTEST GE2_TSEN_VREFN GPS_TSEN_VREFN

1uF(NF)

1NF C1809

NC

[15]

[17] WB_26M_IN1

2 of 3

CO-PADNC

R1815

1NF C1817

10k

[15,17]

WB_26M_IN

C7233

C1850

Main GND Point

It's not a component

A A

TITLE & REV:

SP9832A-2_CS_SCH_V0.1.0

DOCUMENT NO.:

DESIGNER: DATED: DEPARTMENT:

River.Du Hardware DEPT.

2015-10-12

DATED:

EQA: COMPANY:

Mulder.Han

2015-10-12 Spreadtrum communications, Inc.

APPROVED: DATED:

Gang.Xu CONFIDENTIAL AND PROPRIETARY

2015-10-12 SHEET: 23 OF 23

You might also like

- TG 2016 - 09Document116 pagesTG 2016 - 09Joe Kozak88% (8)

- Kenworth Medium Duty BBM Dec 2011Document179 pagesKenworth Medium Duty BBM Dec 2011Daemonarch Av100% (2)

- 797 FDocument10 pages797 FRonny Leon NuñezNo ratings yet

- OTR DatabookDocument91 pagesOTR DatabookSamuel Hendra Sinaga100% (2)

- TP - MT5510I.PB801 Schematic Diagram PDFDocument10 pagesTP - MT5510I.PB801 Schematic Diagram PDFJORGE75% (8)

- Rumble 200 V3 Schematics-DiagramsDocument4 pagesRumble 200 V3 Schematics-DiagramsOrlandd Sanchezz100% (1)

- Fender Rumble 100 V3 TDA8950-88534Document7 pagesFender Rumble 100 V3 TDA8950-88534Claudio Ariel Vera trussy100% (1)

- ZTE Blade G V815W SchematicDocument13 pagesZTE Blade G V815W Schematicsluz2000100% (2)

- Instant Assessments for Data Tracking, Grade 2: MathFrom EverandInstant Assessments for Data Tracking, Grade 2: MathNo ratings yet

- Its Raining Idioms A Figurative Language ActivityDocument11 pagesIts Raining Idioms A Figurative Language ActivityTyrone MoogNo ratings yet

- CWNA Chapter5Document41 pagesCWNA Chapter5SerNo ratings yet

- 308 Hyd PDFDocument1 page308 Hyd PDFchanlin100% (2)

- Maximizing Earthmover Tire Performance Through Proper CareDocument127 pagesMaximizing Earthmover Tire Performance Through Proper CareAkshat BhartiyaNo ratings yet

- Nokia XL Dual SIM RM-1030 RM-1042 Service Schematics v1.0Document19 pagesNokia XL Dual SIM RM-1030 RM-1042 Service Schematics v1.0MarcinDryjaNo ratings yet

- LED driver circuit revisionDocument1 pageLED driver circuit revisionies837No ratings yet

- Training Content SM-G7102 (Galaxy Grand2) HWDocument69 pagesTraining Content SM-G7102 (Galaxy Grand2) HWПаха КирьяновNo ratings yet

- InstaPDF - in Indian Grocery Items List 476Document6 pagesInstaPDF - in Indian Grocery Items List 476Anto VasuNo ratings yet

- The Globe's Holiday CrosswordDocument2 pagesThe Globe's Holiday CrosswordThe Globe and MailNo ratings yet

- Manual Tecnico Epson s01 s02 s11 s12Document142 pagesManual Tecnico Epson s01 s02 s11 s12Ricardo Nicolau Werlang78% (9)

- R9 MainPCB SCHDocument13 pagesR9 MainPCB SCHpradipto87No ratings yet

- I45 (TCk4531) - MAIN - SCH - V1.1pdfDocument16 pagesI45 (TCk4531) - MAIN - SCH - V1.1pdfcoliuntung02No ratings yet

- Hongmi NOTE SubDocument1 pageHongmi NOTE SubMarcelo DanielNo ratings yet