Professional Documents

Culture Documents

Defect Oriented PDF

Defect Oriented PDF

Uploaded by

HaroldOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Defect Oriented PDF

Defect Oriented PDF

Uploaded by

HaroldCopyright:

Available Formats

See discussions, stats, and author profiles for this publication at: https://www.researchgate.

net/publication/224091637

Defect-oriented cell-aware ATPG and fault simulation for industrial cell

libraries and designs

Conference Paper · December 2009

DOI: 10.1109/TEST.2009.5355741 · Source: IEEE Xplore

CITATIONS READS

38 570

8 authors, including:

R. Krenz-Baath Andreas Glowatz

Hochschule Hamm-Lippstadt Mentor Graphics

31 PUBLICATIONS 173 CITATIONS 27 PUBLICATIONS 532 CITATIONS

SEE PROFILE SEE PROFILE

Jürgen Schlöffel Hamidreza Hashempour

Mentor Graphics None

55 PUBLICATIONS 679 CITATIONS 36 PUBLICATIONS 350 CITATIONS

SEE PROFILE SEE PROFILE

Some of the authors of this publication are also working on these related projects:

SAT-based ATPG View project

BASTION View project

All content following this page was uploaded by Jürgen Schlöffel on 06 June 2014.

The user has requested enhancement of the downloaded file.

Defect-Oriented Cell-Aware ATPG and Fault Simulation for Industrial Cell

Libraries and Designs

F.Hapke1, R.Krenz-Baath1, A.Glowatz1, J.Schloeffel1, H.Hashempour2, S.Eichenberger3, C.Hora2, D. Adolfsson2

1 2 3

Mentor Graphics NXP Semiconductors NXP Semiconductors

Tempowerkring 1B Prof. Holstlaan, HTC-46 Gerstweg 2, FD3

21079 Hamburg 5656AA Eindhoven, 6534AE Nijmengen,

Germany The Netherlands The Netherlands

Abstract

Industry is facing increasingly tougher quality Methods to specifically target cell-internal defects have

requirements for more complex ICs. To meet these been proposed in numerous publications. Techniques

quality requirements we need to improve the defect such as N-Detect [3], Embedded-Multi-Detect (EMD)

coverage. This paper presents a new methodology to [6], or Gate-Exhaustive testing [7] have shown

significantly increase the defect coverage of the test considerable success to cover those un-modeled

patterns generated by ATPG tools. The fault model defects. However those techniques are either too

used during the ATPG is enhanced to directly target complex for real-world designs or merely improve the

layout-based intra-cell faults. In contrast to previous probability of detecting cell-internal defects.

techniques, such as Gate-Exhaustive, N-Detect, or

Embedded-Multi-Detect, which either are too complex The contribution of this work is the introduction of a

for real-world designs or merely improve the new methodology to directly target library cell-internal

probability of detecting intra-cell defects, the new defects. This new method we call Cell-Aware (CA).

approach targets the actual root causes of intra-cell The paper presents the general flow of the new

defects. The newly proposed Cell-Aware-methodology approach and discusses individual components in detail.

has been evaluated for 90nm and 65nm technologies on The new method has been evaluated on a large number

1671 library cells and on 10 real industrial designs of 90nm and 65nm library cells and on various

with up to 50 million faults. The experimental results industrial designs with up to 50 million faults. The

show an average increase of 1.2% in defect coverage results have been compared to previous state-of-the-art

and a reduction of 420ppm in escape rate for a 50mm2 techniques. The experimental results underline the

design. significant increase of test quality enabled by this new

technology.

1 Introduction The remainder of the paper is organized as follows: The

objective of Section 2 is the discussion of previous

To achieve today’s quality requirements on large work in this area. In Section 3 the new CA

Systems-on-Chips (SoC) we need to obtain high defect methodology is introduced and the individual

coverages with our test patterns. This is achieved by the components are described in detail. Experimental

creation of test patterns based on wide range of results we achieved with the CA methodology are

methods and fault models. Commonly used are for presented and discussed in Section 4. The achieved

example Stuck-At (SA), Bridging [1][2], Inter-Cell- impact on production testing is described in Section 5.

Opens [3] and Transition-Faults [4]. All these state-of- Section 6 gives an outlook on possible future work.

the-art fault models share the assumption, that a fault Section 7 concludes the paper.

only occurs between library cell instances, at the ports

of library cells, or outside of library cells between the

interconnect lines of the library cells. State-of-the-art

ATPG tools apply those standard fault models and do

2 Previous Work

either assume no faults within the library cells, or The problem of defects not covered by standard fault

consider faults inside the library cell based on the gate models, and techniques to target them has been the

model used by the ATPG. These gate models are well objective of numerous publications. Methods such as

suitable for propagating fault effects through the library N-Detect [3], Embedded Multi Detect [6], or Gate-

cells. Furthermore they are useful for injecting faults at Exhaustive [7] test strategies have been successfully

the cell ports or at the ATPG primitives. However these applied to deal with those uncovered defects.

gate models are not suitable for modeling real layout-

based defects inside library cells.

Paper 1.2 INTERNATIONAL TEST CONFERENCE 1

978-1-4244-4867-8/09/$25.00 ©2009 IEEE

In N-Detect testing, the chance of detection is improved Unfortunately the proposed flow including layout

by targeting the same fault multiple times under extraction, netlist manipulation and the subsequent test

different conditions. However, this typically also pattern generation is not applicable for large designs.

increases the pattern set by a factor N and therefore

makes the test costly. The concept of the EMD ATPG 3 A new Cell-Aware Methodology

technique addresses this increase in pattern count and

The objective of this section is a detailed introduction

has been initially proposed in [6] and the achieved

into the new defect-oriented Cell Aware methodology

results have been presented in [9].

proposed in this paper. Firstly we provide an overview

The major contribution of the EMD-based approach

describing the general flow. This is followed by a

was to increase the defect coverage by exploiting

detailed description of the individual steps.

unused bits in existing patterns, instead of adding

further test patterns as proposed by methods based on

The flow starts with the Layout Extraction step,

N-Detect. The major disadvantage of methods like N-

followed by an Analog Fault Simulation, and a

Detect or EMD is that there exists only a probabilistic

synthesis step to create the CA library models. Finally

relation to actual defects. A technique to quantify this

these CA models are used by the CA-ATPG to generate

relation has been proposed [8], in where a Bridging

high quality test pattern to significantly reduce the

Coverage Estimate (BCE) has been introduced based on

Defect Level of delivered ICs. The complete flow as

the assumption that there exists a 50% probability,

shown in Figure 1, is a mixture of state-of-the-art

when the Stuck-At fault at the victim node is detected

functions/tools and new functions and algorithms that

and the corresponding aggressor node is in the right

we developed for this new methodology.

state to activate the bridge defect. An extension of this

technique is presented in [10]. Since the relation is only

probabilistic, it is difficult to quantify the additional

F2

defect coverage and to predict the benefit for future

Layout Analog

designs. F1

Extraction Fault Simulation

Library cell

In order to find an explicit and deterministic method to layout data F3

cover those un-modeled defects, the results of over one F4

million tested devices of an NXP design have been

discussed and analyzed in [9] to identify the defects

found by EMD test patterns. This analysis has shown TC % Cell Aware Cell Aware

F5

that a significant number of defects, which are only Test ATPG Synthesis

detected by EMD patterns, are intra-cell defects not Coverage

covered by the Stuck-At fault model. The extraction of

intra-cell defects has been the objective of several

Figure 1: Cell-Aware methodology flow

publications [12], [13], [14].

The flow starts with the layout extraction, which

The application of Gate-Exhaustive testing to detect extracts a transistor netlist and a list of possible defects,

intra-cell defects is the objective of [7]. The paper based on the layout data of the individual library cell

compares the efficiency of methods based on N-Detect contained in file F1. The results of the layout extraction

and Gate-Exhaustive testing w.r.t. the detection of intra- operation are the extracted transistor netlist in F2 and

cell defects. Furthermore, the paper demonstrates the the list of defects of the particular library cell in F3.

capability of addressing all gate-input combinations by

the ATPG to find missed defective devices. In practice Next, for each of the previously extracted defects an

this method seems to be not applicable for industrial exhaustive analog simulation is performed in order to

circuits, because there is a high probability in determine the complete set of cell-input combinations

generating a high number of additional patterns and which detect the defect. The resulting detection matrix

consequently higher test costs. for the particular library cell is contained in F4.

Another major gap in using this method is the missing The following “Cell Aware Synthesis” function

relation to real potential defects. The used metric based optimizes the previously generated detection matrix in

on all gate-input combinations can provide a number to order to ease the subsequent CA-ATPG and to generate

quantify the generated patterns, but without a relation to the corresponding CA library view stored in file F5. For

defects. The method proposed in [11] directly targets each cell-internal defect file F5 contains one or more

intra-cell defects which have been extracted from the alternative conditions for detecting the corresponding

actual layout representation of the design.

Paper 1.2 INTERNATIONAL TEST CONFERENCE 2

defect. Note that all previous steps are a one-time effort and the cell-outputs are contained in the defect lists for

for a specific library. each cell as well.

The final Cell-Aware ATPG step generates the high 3.2 Analog Fault Simulation

quality test patterns based on the earlier generated CA This step in the flow simulates the extracted netlist of

library view. Current results achieved by this new CA each cell in presence of its defects. As an example we

methodology show a significant increase of the defect consider again the 3-to-1 multiplexer described in the

coverage. previous section. The extracted netlist is shown in

Figure 3.

3.1 Layout Extraction

The base of every layout extraction is the actual layout P8 P54

view of the library cell under investigation. As an

P24 P38

S0

example we consider the cell MUX31X4 from a 65nm N8

P23 P34

P48

library, representing a 3-to-1 multiplexer. The

corresponding layout is shown in P31

P63

Z

Figure 2. D2 N28 N63

D1

D0

N23 N32 N41

P60

S1 N24 N33 N57

N60

Figure 3: Extracted Transistor Netlist

The extracted netlist, including its parasitic objects, is

used as input for the analog fault simulation, which

simulates the effect of each potential defect for all

possible input combinations. Additionally, each cell is

exhaustively simulated without defects in order to

determine the golden voltage at the cell outputs for

every cell-input combination. The simulations are

Figure 2: MUX31X4 layout Analog DC-analysis simulations which determine the

steady state voltage of the cell output(s).

From this layout data, in our case gds2, we extract the

corresponding netlist of circuit elements. The netlist A defect is considered detected if at least for one input

includes transistors as well as parasitic elements, like combination the cells output voltage deviates from the

capacitors. For this part of the flow we used a state-of- golden voltage by more than 50% of the supply voltage.

the-art commercial EDA extraction tool. The deviation threshold however, can be specified by

the user. The simulations are automated by a set of

The extracted netlist is used as input for the next step in scripts around a state-of-the-art analog simulator.

the flow where defects of interest are extracted. In this

paper we focus on cell-internal short/bridge defects. The resulting defect matrix summarizes the detection

results for each cell. In such detection matrix rows and

Please notice that the whole Cell-Aware methodology columns refer to input combinations and defects,

is capable to deal with many other defects as well, i.e. it respectively. A ‘D’ indicates that the input combination

is just the question of extracting the defects of interest, detects the corresponding defect.

like e.g. opens. But in this paper we concentrate on

bridges only, thus for these kinds of defects an effective For further details please consider the MUX31X4-cell

method to identify realistic locations is based on as an example. The cell contains a total of 48

capacitors in the extracted netlist. The two nodes of the capacitors, where each capacitor can be shorted in order

capacitor are assumed to be shorted in the presence of a to model a potential bridge defect. The list of 48

defect. The individual specification of the bridge potential defects for this cell is presented in Figure 4,

resistances is part of the subsequent analog fault where the capacitor terminals indicate the (potentially)

simulation. Note that Stuck-At faults at the cell-inputs shorted nets.

Paper 1.2 INTERNATIONAL TEST CONFERENCE 3

d1 = S0N, gnd d17 = D0, gnd d33 = net38, D1

3.3 Generation of the Cell-aware Models

d2 = S1N, gnd d18 = vdd, gnd d34 = net81, D0 The following paragraph describes the computation of

d3 = net65, gnd d19 = Z, net65 d35 = net38, D0 an optimized set of input assignments required to detect

d4 = net57, gnd d20 = S1, S0N d36 = S1, S0 individual cell-internal faults. For every fault the

d5 = net19, gnd d21 = S1N, S1 d37 = D2, S1 algorithm extracts necessary constrains from the

d6 = net81, gnd d22 = net65, S1 d38 = S0, D1 detection matrix and maps those onto the corresponding

d7 = net38, gnd d23 = S0N, S0 d39 = vdd, S0N

function implemented by the library cell.

d8 = net85, gnd d24 = net81, S1 d40 = vdd, S1N

d9 = net35, gnd d25 = S1, net38 d41 = vdd, net65

d10 = net31, gnd d26 = D2, S1N d42 = D0, S0 The new technique is specifically tuned to deliver only

d11 = net69, gnd d27 = net81, S0 d43 = net38, vdd necessary input-assignments. This is an essential

d12 = Z, gnd d28 = net65, D2 d44 = vdd, Z property of the algorithm since it significantly relaxes

d13 = S1, gnd d29 = net38, S0 d45 = vdd, S1 the subsequent pattern generation process.

d14 = S0, gnd d30 = S0N, D1 d46 = vdd, S0

d15 = D2, gnd d31 = net81, D1 d47 = vdd, D2

d16 = D1, gnd d32 = S0N, D0 d48 = vdd, D1

Generate F from truth table

For each d∈ D

Figure 4: List of Defects of MUX31X4 Rd = emtpy set;

gd = OR1≤ i ≤ 2n ti if ti detectes d, 0 otherwise;

From this list of potential defects in cell MUX31X4 we gdF = AND(gd, F);

derive 48 additional netlists (hence 49 netlists including

gdF’ = AND(gd, F’);

the golden netlist), where the targeted capacitors are

replaced by a resistor (one per netlist). Each of the 49 Rd = Rd ∪ derive_prime_cubes(gdF’);

netlists is simulated applying all 32 possible input Rd = Rd ∪ derive_prime_cubes(gdF);

patterns, which results in a total of 1568 simulations. End

The outputs are processed and defect detections are // Compression stage

recorded for all input combinations. The final results P = emtpy set;

are stored in the defect matrix of the cell. The table M = emtpy set;

below in the Figure 5 shows a fraction of the defect For each Rd

matrix generated for the cell MUX31X4: For each q ∈ Rd

If ∃ pi ∈ P pi == q

stimuli d1 d2 d3 d4 ... d41 d42 d43 d44 d45 d46 d47 d48

M = M ∪ d; // where d = M|i|

00000 - - - - - - - D - - - -

00001 D D - - D D D - D D - - Else

00010 - - - - - - - D - D - - P = P ∪ q; // where q = P|P|

00011 - D - - D - D - D - - - M = M ∪ d; // where d = M|M|

00100 - - - - - - - D D - - - End

00101 D - - - D D D - - D - -

00110 - - - - - - - D D D - -

End

00111 - - - - D - D - - - - - End

01000 - - - - - - - D - - - D

... Figure 6: Proposed algorithm

11111 - - - - D - - - - - - -

The proposed algorithm, shown in Figure 6, works as

Figure 5: Defect Matrix follows. Assuming a detection matrix D generated w.r.t.

some n-input library cell C implementing the

For example the row describing stimuli ‘00001’ detects, combinational Boolean function F.

among others, defect d41 which is a short between the For every fault d specified in D the algorithm generates

internal net65 and vdd. a detection-function gd(). This detection-function

incorporates all fully defined input-assignments,

Through out this paper, we focus on CA-detectable meaning input assignments without don’t-cares, which

defects. Those defects, that are not detected by any would be required to detect d. Next every detection-

single-cycle input pattern are not considered in further function is combined with function F and its inverse F’

steps of the flow. Therefore all detection figures are in order to find the corresponding output assignment for

normalized with respect to the CA detectable defects. every cube contained in gd(). After that all prime cubes

of the resulting functions gdF() and gdF’() are collected

in the set Rd.

Paper 1.2 INTERNATIONAL TEST CONFERENCE 4

Finally the algorithm compresses identical cubes w.r.t. significant portion of cell-internal defects. The third

all sets Rd and the corresponding fault information in step is the evaluation of the Embedded Multi Detect test

two sets P and M, where P denotes the final set of patterns. As shown in [6] applying EMD test patterns

primes cubes (the union of all prime cubes contained in result in an increase of the defect coverage compared to

all sets Rd, d member of D), and M denotes a set of sets traditional Stuck-At tests. Furthermore these results

containing every fault d detected by the corresponding have been confirmed by experiments [9] during actual

prime cube. The mapping between some element of P IC production. The fourth step evaluates the coverage

and a set in M is defined via their indices. This means gain of CA patterns w.r.t. previous methods such as SA

that the cube Pi detects all faults contained in the set Mi. and EMD. For this additional pattern generation step

Note that the described algorithm can be easily we use a newly developed CA-ATPG engine as

extended to handle sequential detection matrices. described below.

The major difference between the pattern generation for

3.4 Cell-Aware Pattern Generation and Fault a CA fault and a Stuck-At fault is the modeling of the

Simulation fault. To demonstrate those differences, we use the

already discussed 3-to-1 multiplexer and assume it is

To demonstrate the impact of the proposed cell-aware

somewhere instantied in the design.

fault model, we have set up a CA-ATPG flow, which

compares the defect-coverage achieved by previous

methods with the new approach. The investigation

incorporates the traditional SA model as well as the

EMD-based approach described in [6] and is performed

on a large number (1671) library cells and on 10

industrial designs implemented in 90nm and 65nm

technology. The flow is depicted in the figure below:

Fault Simulation FC % Figure 8: ATPG process

of SA pattern

In Figure 8 we show how the SA-ATPG will generate a

Design Fault Simulation FC %

test for detecting a port fault e.g. a stuck-at 0 fault at the

Compilation of EMD pattern cell-input D0. In a traditional Stuck-At ATPG engine

netlist the fault position (initial D-frontier position) and the

Cell Aware

condition for the fault excitation is predefined for every

FC %

ATPG ATPG-primitive. In this example the SA-ATPG would

Cell Aware justify D0=1, S0=0, and S1=0. The other inputs are not

library models required. The generation process of the CA-ATPG for

the same multiplexer is shown in Figure 9 below. In

Figure 7: Defect Coverage evaluation flow for all this case we assume an intra cell bridge between two

library cells and industrial designs nets A and B as indicated in the layout.

The evaluation flow starts with the design compilation

using the Cell-Aware models.

The number of CA-faults is always larger than the

number of faults considered using the traditional SA

model. This is because in the proposed flow, we

additionally consider the layout-based cell-internal

faults. The second step in the flow is the verification of

a set of SA patterns with respect to the CA fault model.

This evaluation is accomplished by a fault-simulation

of the SA-patterns on the corresponding design

considering the cell-internal defects. This fault Figure 9: TPG for an intra cell bridge fault

simulation typically results in a fault coverage drop

(compared to the known Stuck-At coverage) and clearly The initial D-frontier position of a CA fault is always at

shows that SA patterns are insufficient to address a the cell output port. The condition for the fault

Paper 1.2 INTERNATIONAL TEST CONFERENCE 5

excitation and it’s propagation to the cell outputs is Considering the bridge B1 in the above example, the

fully disconnected from any predefined ATPG necessary assignments at the cell inputs are D0=1,

primitive. It strictly applies the necessary conditions at D2=0, S0=0 and S1=0. Meaning the CA-ATPG is

the input-ports of the library cell as defined by the forced to assign an additional cell-input, in this case

corresponding CA model. D2, in order to detect the bridging defect B1. As

described earlier a traditional SA-ATPG would only be

Algorithm: CA-ATPG forced to assign one data input. In other words, in

Given contrast to previous approaches the CA-ATPG

f // actual fault deterministically applies the conditions to detect intra

Sf // List of condition sets of fault f. In difference to a cell faults.

// Stuck-At fault where the excitation condition are hard

// coded and bounded on the fault location, an intra cell To guarantee a very compact set of test patterns, the

// fault is defined with the D-frontier position and a list CA-ATPG algorithm makes use of all possible

// of alternative excitation conditions. These conditions

// have been generated such that the TPG engine will conditions, given by the CA fault definition for

// have the the maximum flexibility to reach the highest detecting a certain defect.

// coverage with the minimum number of test patterns.

Initialization

4 Results

sf := undetected // status of f

i := 0 // actual index of Sf In this section we first present the results of our

C0 := Sf (i) evaluation of all combinational library cells from a

90nm library, followed by the evaluation results from a

// Select the D-frontier position for the fault propagation. 65nm library. And finally we present the results that

// The position defined for a intra cell defect on a cell output. were achieved by evaluating 10 real industrial designs

Define D-frontier position of f with up to 50 million faults.

if D-frontier definition failed then

4.1 Results for 90nm library cells

sf := redundant

end if The CA defect coverage for all 1220 cells of the NXP

standard cell library from a 90nm process technology

while sf = undetected are shown in the diagram below:

// We now using set C i to do the fault excitation. These

// conditions are on the cell inputs and have to be justified

100%

// by the TPG engine.

add condition set C i

90%

apply TPG to do fault excitation and propagation

80%

if TPG failed then

// The TPG did failed. If there are further condition sets,

70%

// we will continue the while otherwise we leave the

// loop with fault status redundant.

60%

sf := redundant

i := i + 1

50%

if Ci ∈ Sf then 0 200 400 600 800 1000 1200

sf := undetected Cell 1 to 1220 of the 90 nm library

end if Figure 11: CA coverage of SA pattern – 90 nm lib

else

// The TPG did successfully apply the fault excitation The horizontal axis represents the individual library

// and propagation. We leave the while loop with fault

// status tested. cells (from cell 1 to cell 1220). The vertical axis

sf := tested represents their coverage figures. The cells are sorted

Store generated test cube by their coverage incrementally from left to right. This

end if evaluation has shown that for 42% of the cells (516 of

end while 1220) the layout-aware defect coverage of SA patterns

is lower than 100%. This leads to a tremendous

coverage loss for these cells if only SA patterns are

Figure 10: Cell-Aware ATPG Algorithm applied. However, using CA patterns, the defect

coverage would be 100% for them.

Paper 1.2 INTERNATIONAL TEST CONFERENCE 6

The following table shows the 10 library cells from the 4.2 Results for 65nm library cells

90nm library with the highest loss of defect coverage: The CA defect coverage achieved by traditional SA-

patterns for 451 cells of a 65nm library are shown in the

Defect Coverage Additional diagram below:

Cell

Standart ATPG Cell Aware ATPG Pattern

mx31nx05 70,73% 100,00% 3

100%

mx31nx1 71,05% 100,00% 3

mx31nx2 74,55% 100,00% 3 90%

mx31nx4 74,55% 100,00% 3

mx31nx3 75,00% 100,00% 3 80%

mx31x4 75,00% 100,00% 5

mx31x05 79,25% 100,00% 4 70%

ao51x05 79,63% 100,00% 7

mx31x3 80,33% 100,00% 4 60%

ao31x1 81,40% 100,00% 5

50%

0 100 200 300 400

Figure 12: Worst 10 cells from the 90nm lib. Cell 1 to 451 of the 65 nm library

As can be seen in the table above, low defect coverage Figure 14: CA coverage of SA patterns – 65nm lib

exists mainly for certain types of library cells, for

example multiplexers. The cells mx31* are all Here the horizontal axis represents the individual

multiplexers with three data inputs and two select library cells (from cell 1 to cell 451) and the vertical

inputs with different drive strengths. The cell ao31x1 is axis represents the corresponding coverage figures. The

a Boolean (AND/OR) gate with five data inputs. The cells are sorted by their coverage from left to right. This

cell ao51x05 is a Boolean AND/OR function with nine graph illustrates again the layout-aware defect-coverage

data inputs. of SA patterns. Even in this library 43% of the cells

(196 out of 451) are below 100%.

Figure 13 shows the number of test patterns generated The following table shows the top 10 cells from the

by SA-ATPG and the CA-ATPG for each of the 1220 65nm library with the highest loss of defect coverage:

cells of the 90nm library.

Defect Coverage Additional

Cell

Standart ATPG Cell Aware ATPG Pattern

25 XNOR2X3 71,43% 100% 1

AO32X4 76,00% 100% 1

AOI32X5 79,31% 100% 1

20

MX41X7 79,66% 100% 8

Num ber of Patterns

MUX31X4 80,00% 100% 2

15 XNOR3X4 80,77% 100% 1

SA MX41X4 81,82% 100% 7

CA AO222X9 82,50% 100% 5

10 AO22X4 82,61% 100% 2

AOI13X15 82,76% 100% 2

5

Figure 15: Worst 10 cells from the 65nm library

0

1 201 401 601 801 1001 1201 Again, it is the same observation as with the 90nm

library and it can be concluded that low defect coverage

is mainly occurring for multiplexers, some AO cells

Figure 13: Number of Patterns – 90nm cells

(Boolean gates) and in this library also for some XOR

gates.

In average over all 1220 cells, the CA-ATPG needs to

generate about 50% more pattern as the SA-ATPG, i.e.

Figure 16 shows the number of test patterns generated

in average 7.3 CA patterns per cell instead of 4.8 SA

by the SA- and CA-ATPG for each cell of the 65nm

patterns.

library.

Paper 1.2 INTERNATIONAL TEST CONFERENCE 7

16 chains, resulting in 37.2 million Stuck-At faults and

14

48.5 million Cell-Aware faults. The designs I1652k,

I1676k, and I6649k are using on-chip test compression;

12

therefore these designs have a high number of internal

Number of Patterns

10 scan chains.

SA

8

CA

6 Considering the last two columns of the table, it can be

4

seen that the number of CA faults is in all cases

significantly higher than the number of SA faults.

2

0 We performed the test coverage analysis that has been

1 51 101 151 201 251 301 351 401 451

discussed in section 3.4 on all designs. The results are

Figure 16: Number of Patterns – 65nm cells listed in Figure 18. All runs were done with the newly

developed ATPG and fault simulator using the CA

On average over all 451 cells, the CA-ATPG needs to library models. First we performed a fault simulation of

generate about 13% more pattern as the SA-ATPG, i.e. the SA patterns followed by a fault simulation of the

on average 4.9 CA patterns instead of 4.3 SA patterns. EMD patterns. Finally we run the CA-ATPG to reach

the highest achievable defect coverage.

For both cell libraries the extraction, the analog fault

simulation, the generation of the cell-aware models and Test Coverage Coverage Increase

the ATPG runs can be done all within one day. Design Stuck-At EMD Cell Aware EMD Cell Aware

I73k 97,44% 97,98% 99,65% 0,54% 2,21%

I247k 98,46% 98,78% 99,49% 0,32% 1,03%

A simple defect coverage translation of the SA patterns

I449k 98,41% 98,75% 99,65% 0,34% 1,24%

from cell level to chip level can not be made. On chip- I671k 98,84% 99,01% 99,30% 0,17% 0,46%

level some of the missed input combination at cell-level I1652k 98,29% 98,30% 99,58% 0,01% 1,29%

might still be applied to that cell, because they are I1676k 98,80% 98,80% 99,26% 0,00% 0,46%

required to test another part of the chip. To quantify the I2181k 98,56% 99,03% 99,89% 0,47% 1,33%

real impact on chip level we created SA patterns for I2183k 98,32% 98,83% 99,35% 0,51% 1,03%

I2986k 98,02% 98,44% 99,85% 0,42% 1,83%

various industrial designs and evaluated these patterns

I6649k 98,20% 98,24% 99,72% 0,04% 1,52%

based on the CA model. The results of this evaluation Average 98,33% 98,62% 99,57% 0,28% 1,24%

are discussed in section 4.3.

Figure 18: Results achieved on Industrial designs

4.3 Results from Industrial Designs

In this section we provide details of our evaluation It can be concluded that the test coverage of the Stuck-

work, using the 90nm and 65nm CA library models for At patterns is on average about 1.2% lower than the

10 real industrial designs. The corresponding design maximal achievable test coverage, which can be

data is shown in Figure 17 . obtained by the CA-ATPG. The test coverage of the

EMD patterns is on average about 0.3% higher than the

Design Data test coverage of the Stuck-At patterns. The reported

Design #gates #FFs #chains #SA-faults #CA faults results indicate that EMD test patterns show no effect

I73k 73k 6k 29 363k 506k on the defect coverage of some designs. This effect is

I247k 247k 21k 34 1.2M 1.7M currently investigated in detail. As expected the CA-

I449k 449k 32k 35 2.0M 2.7M ATPG could target a large number of cell internal faults

I671k 671k 76k 128 3.4M 4.6M explicitly, moreover, the achieved coverage

I1652k 1,6M 135k 300 8.7M 9.8M improvement of 1.2% in average was outperforming

I1676k 1.7M 131k 381 8.6M 11.5M our expectation. An increase of the coverage of about

I2181k 2.1M 148k 70 12.2M 15.4M 1.2% has a significant positive impact on the quality of

I2183k 2.1M 135k 38 10.2M 12.8M the test pattern.

I2986k 2.9M 173k 114 14.9M 18.4M

I6649k 6.6M 457k 1011 37.2M 48.5M

5 Impact on Production Testing

Figure 17: Design data of 10 Industrial designs Of course, an interesting question to answer at this

point is: what will the impact be on test quality. It is

As an example, the last design named “I6649k” has 6.6 difficult to find a straight-forward answer as it is

million gates, 457k flip flops, and 1011 internal scan influenced by many factors, such as defect Pareto of the

Paper 1.2 INTERNATIONAL TEST CONFERENCE 8

underlying fabrication process, composition of the only detected by EMD patterns. Of course, we could

entire test suite, circuit topology, DfM measures taken not simply imply that all of these devices would be

in the cell library design, etc. Hence, we would like to algorithmically detected with cell-aware ATPG.

answer this question in two approximate ways: Therefore we filtered them similarly as explained in

• By a theoretical estimation section 4.4 of [9]. This left us with 4.5 devices/mm2

• By experimental data compatible with cell internal faults. In [9] we have

shown on a larger dataset (namely, all devices surviving

It has to be noted that we explicitly exclude the impact a similar filter, not just EMD-only detects), that ~44%

of fringe coverage through other pattern sets, such as of these devices can be explained with a cell-aware

bridge patterns, delay fault patterns, IddQ test methods, approach. This amounts to ~2.0 devices/mm2.

etc. Although such approaches may arguably reduce the

benefit of cell-aware ATPG, we strongly feel that in a Hence, we did attribute these devices to the incremental

zero defect environment, such as the most challenging coverage improvement of ~0.28% for EMD patterns.

automotive market segment, it is not good practice to We can then also estimate that an additional coverage

rely on fringe effects - the only metric that really counts improvement of 1.2% with explicit CA patterns (as

is a measurable one! achieved in average over 10 real industrial designs) will

detect an additional 8 devices/mm2.

In the following section, we'll scale all results to per

square-millimeter of logic area to allow for easy

comparison between cores and designs. 6 Future work

The next step will be to prove the coverage gain, and

5.1 Theoretical estimation reduction in DPM levels, on real silicon on a large

Defect levels are often estimated with the formula number of tested devices in an production environment

postulated by Williams and Brown [15]: DLWB = 1 – at NXP. A second further task will be to provide the

Y^(1-f). However, Agrawal, Seth, de Sousa and others CA-ATPG and the CA-Model generation as a

postulated other formulas as summarized in [16][17]. commercial feature. A third future task will concentrate

These formulas take additional aspects into account on enhancing the whole Cell-Aware flow to also

such as that defects tend to cluster and that a single consider cell internal faults that require sequential test

defect can cause multiple faults. However, to take these patterns, e.g. for detecting cell internal opens.

aspects into account also additional parameters are

introduced. Whilst none of the various formulas is In addition to sequential patterns we also want to

proven beyond doubt to be superior compared to all evaluate the effect of large defects, e.g. bridges between

others, a common denominator is that they all estimate three or more nets. Furthermore we intend to enhance

defect levels significantly lower than Williams and the CA-ATPG to enable and evaluate an Embedded-

Brown. Hence, we find it convenient and sufficient for Cell-Aware step. This will improve the defect coverage

most practical purposes to approximate defect levels as without increasing the number of test pattern. In

DLpragmatic=DLWB/4. addition we also intend to enhance the layout extraction

step, to include the layout X,Y coordinates for the

If we plug in the achieved coverage rate of 98.33% for individual defects, such that these X,Y coordinates can

traditional stuck-at patterns, and assume an arbitrary be passed on to the Electrical Failure Diagnosis

defect limited yield of 75% for a 100mm2 design, we function to pin point directly to the location with in a

arrive at an escape rate of DLpragmatic = 12.0 library cell.

ppm/mm2. Likewise, with coverage of 98.62% for

EMD patterns, the escape rate will be estimated at 9.9

ppm/mm2 with the difference of 2.1 ppm/mm2 7 Conclusion

attributed to the positive effect of EMD patterns. The We have shown that the quality of test patterns can be

CA-ATPG reaches coverage of 99.57% corresponding improved significantly by explicitly targeting cell

to an escape rate of 3.1ppm/mm2. In other words, it is internal faults, e.g. bridges. We have also proven that

expected to detect an additional 8.4ppm/mm2 compared Stuck-At patterns that only target faults at the library

to SA patterns. cell ports, are not sufficient to detect all detectable cell

internal faults, e.g. bridges. The experiments performed

5.2 Experimental data showed that only about 50% of all 90nm and 65nm

In our previous work [9] we have shown experimental standard library cells are guaranteed to be tested

data based on more than one million tested devices. sufficiently with SA patterns. We further have proven

This data set contained 24.8 devices/mm2, which were that EMD patterns are better than SA pattern, i.e. about

Paper 1.2 INTERNATIONAL TEST CONFERENCE 9

0.3% higher coverage as with SA patterns. However, [7] K.Y. Cho, S. Mitra, E.J. McCluskey, “Gate

Cell-Aware patterns which deterministically target Exhaustive Testing” in Proc. of IEEE Int'l Test

these defects are significantly better, i.e. about 1.2% Conf, ITC, 2005, paper 31.3

higher coverage than SA patterns. To achieve this, a

[8] B. Benware, C. Schuermyer, S. Ranganathan, R.

CA-ATPG has been developed, and CA library models

Madge, N. Tamarapalli, K.-H. Tsai and J. Rajski,

have been created by an automated flow. For an

“Impact of Multiple-Detect Test Patterns on

industrial application it is intended, that the needed CA

Product Quality,” Proc. of ITC, pp.1031-1040,

models are created by library providers, and as such

2003.

design teams can generate high quality and layout

aware test pattern without using layout data. As shown [9] S. Eichenberger, J. Geuzebroek, C. Hora, B.

in section 5.1 the impact on production testing is Kruseman, A. Majhi,“Towards a World Without

significant, a reduction of 8.4ppm/mm2, e.g. 420 ppm Test Escapes, in Proc. of IEEE Int'l Test Conf,

for a 50mm2 design is expected. ITC, 2008, paper 20.1

[10] H. Tang, G. Chen, C. Wang, J. Rajski, I.

Pomeranz, S.M. Reddy, “Defect Aware Test

8 Acknowledgements Patterns”, Proc. of Design, Automation, and Test

The authors would like to thank Erik Jan Marinissen, in Europe (DATE), pages 450–455, Munich,

Bram Kruseman, Peter Weseloh and Michael Wittke for Germany, March 2005.

their assistance, implementations, insight and valuable

discussion over the course of this project. [11] L.-Y. Ko, S.-Y. Huang, J.-L. Chiou, H.-C. Cheng,

“Modeling and Testing of Intra-Cell Bridging

Parts of this work have been supported by the BMBF Defects Using Butterfly Structure”, VLSI Design,

within the project MAYA (Project ID 01M3172). Automation and Test, 2006

[12] F.M. Goncalves, I.C. Teixeira, J.P. Teixeira,

“Integrated Approach for Circuit and Fault

9 References Extraction of VLSI Circuits”, Proc. of IEEE

International Symposium on Defect and Fault

[1] K.Y. Mei, "Bridging and Stuck-at Faults", in IEEE Tolerance in VLSI Systems, Nov. 1996

Trans. On Computers, vol. C-23(7), 1974, pp.720-

727 [13] F.M. Goncalves, I.C. Teixeira, J.P. Teixeira,

“Realistic Fault Extraction for High-Quality

[2] F.J. Ferguson and T. Larrabee. “Test pattern Design and Test of VLSI Systems ”, Proc. of

generation for realistic bridge fault in CMOS ICs”, IEEE International Symposium on Defect and

in Proc. of IEEE Int'l Test Conf, ITC , pages 492- Fault Tolerance in VLSI Systems, Oct. 1997

499, 1991.

[14] Z. Stanojevic, D.M. Walker, “FedEx – A Fast

[3] S. Spinner, I. Polian, P. Engelke, B. Becker, M. Bridging Fault Extractor”, Proc. of IEEE Int’l Test

Keim, and W.-T. Cheng, “Automatic test pattern Conf., ITC, Nov. 2001

generation for interconnect open defects”, In VLSI

Test Symp., pages 181–186, 2008 [15] T.W. Williams, N.C. Brown., “Defect Level as a

function of Fault Coverage”, IEEE Transactions

[4] J.A. Waicukauski, E. Lindbloom, B.K. Rosen and on Computers, Vol. C-30, No. 12, December 1981,

V.S. Iyengar, "Transition Fault Simulation", in pp. 987-988.

IEEE Design & Test of Computers, April 1987, pp.

32-38 [16] J.T. de Sousa and V. D. Agrawal, “Reducing the

Complexity of Defect Level Modeling using the

[5] I. Pomeranz and S.M. Reddy, “On N-detection Clustering Effect”, Proc. of Design, Automation,

Test Sets and Variable N-detection Test Sets for and Test in Europe (DATE), pp. 640-644, Paris,

Transition Faults,” in Proc. of VTS 1999, pp. 173- March 2000.

180

[17] S. C. Seth and V. D. Agrawal. “Characterizing the

[6] J. Geuzebroek, E.J. Marinissen, A. Majhi, A. LSI Yield Equation from Wafer Test Data”, IEEE

Glowatz, F. Hapke, “Embedded Multi-Detect Trans. on CAD, CAD-3(2): 123-1 26, April 1984.

ATPG and Its Effect on the Dection of Unmodeled

Defects” in Proc. of IEEE Int'l Test Conf, ITC,

2007, paper 30.3

Paper 1.2 INTERNATIONAL TEST CONFERENCE 10

View publication stats

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5819)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 12th Chemistry by PlancessDocument1,070 pages12th Chemistry by PlancessUnderworld Don75% (4)

- DKD R 6 2 t5 eDocument9 pagesDKD R 6 2 t5 eSebas BuitragoNo ratings yet

- Gasoline Direct InjectionDocument21 pagesGasoline Direct InjectionhoangNo ratings yet

- ATS48D75QDocument6 pagesATS48D75QAgnewNo ratings yet

- Parts Reference List: Brother Laser MFCDocument41 pagesParts Reference List: Brother Laser MFCNebi aktaşNo ratings yet

- Thomas de Lazzari Architecture and Development of NFC Applications Smart-University 092009Document122 pagesThomas de Lazzari Architecture and Development of NFC Applications Smart-University 092009yernjothiNo ratings yet

- Ingress Protection Chart: The First Character Numeral The Second Character NumeralDocument4 pagesIngress Protection Chart: The First Character Numeral The Second Character Numeralsanu1985No ratings yet

- Health Index CalculationDocument7 pagesHealth Index CalculationManinder ChoudharyNo ratings yet

- 403 CHEAP DIY Homebrew Wire Antennas For Ham Radio K3RRR v3Document292 pages403 CHEAP DIY Homebrew Wire Antennas For Ham Radio K3RRR v3carabetlucian100% (1)

- Hitachi-12 Complete E CatalogDocument196 pagesHitachi-12 Complete E CatalogAcep KasepNo ratings yet

- Care, Maintenance, and Testing OF Hot Line ToolsDocument20 pagesCare, Maintenance, and Testing OF Hot Line ToolsjosefmarqNo ratings yet

- PIC16F873 Flash MicrocontrollerDocument4 pagesPIC16F873 Flash MicrocontrollerAswathy CjNo ratings yet

- Wheatstone BridgeDocument36 pagesWheatstone BridgeJoseph Thomas100% (1)

- Single Line For High Rise BuildingDocument28 pagesSingle Line For High Rise Buildingahmed s. NourNo ratings yet

- BNWQ 3 Ak TZ3 RNG Z4 QGW WaDocument14 pagesBNWQ 3 Ak TZ3 RNG Z4 QGW Wathealtamash21No ratings yet

- 7 5 ConnectorsDocument17 pages7 5 ConnectorsRonal Quispe HuamanNo ratings yet

- 3030 Preliminary Treatment of SamplesDocument8 pages3030 Preliminary Treatment of SamplesOSCAR RUIZNo ratings yet

- Amd20 MeDocument46 pagesAmd20 MeKopi143No ratings yet

- oSCILADOR FUENTE CASERA PWMDocument6 pagesoSCILADOR FUENTE CASERA PWMMaki DominguezNo ratings yet

- Study On The Jamming To Synthetic Aperture RadarDocument4 pagesStudy On The Jamming To Synthetic Aperture Radarapi-19919509No ratings yet

- Socomec AtysDocument2 pagesSocomec AtysmehdivinciNo ratings yet

- 03 Elektor USA May June 2015 PDFDocument132 pages03 Elektor USA May June 2015 PDFvpsampathNo ratings yet

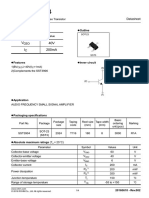

- V 40V I 200ma: OutlineDocument6 pagesV 40V I 200ma: OutlinesikeshkkNo ratings yet

- Ametek 241 PDFDocument2 pagesAmetek 241 PDFJaganathan KrishnanNo ratings yet

- (UFH4003 Africa) BN68 06636E 01ENG 0828 PDFDocument2 pages(UFH4003 Africa) BN68 06636E 01ENG 0828 PDFklkumarNo ratings yet

- Conectores Harting Han E ES ESS EEDocument28 pagesConectores Harting Han E ES ESS EERudimarNo ratings yet

- PLS159ADocument12 pagesPLS159AFrancisco MauroNo ratings yet

- EEE. 2mark and 16 Marks Quest-With AnswerDocument21 pagesEEE. 2mark and 16 Marks Quest-With AnswerPrasanth Govindaraj100% (1)

- CHM13P Learning Task 5Document6 pagesCHM13P Learning Task 5Paolo Gochingco0% (3)

- Lacal Test ManualDocument25 pagesLacal Test ManualAnonymous oX70P4mNo ratings yet