Professional Documents

Culture Documents

Booster 1 V 32

Booster 1 V 32

Uploaded by

Mahi Chapli0 ratings0% found this document useful (0 votes)

18 views12 pagesboost

Original Title

booster1v32

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentboost

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

18 views12 pagesBooster 1 V 32

Booster 1 V 32

Uploaded by

Mahi Chapliboost

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 12

HYDERABAD CAMPUS

RIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI,

First Semester, 2019-2020

Digital Design

Quis -IT (Open Book)

Date: 02/11/2019 Marks:

Times 2:00 ~ 2:40 pm (40 MINUTES)

Nore: :

Q) An write down the answers (only CAPITAL A, B,C

h carrying 2M) and

cr all 12. Questions

1D) inside the BOX given.

0.5) for each wrong answer: For any

‘with pencil leads to Zero (0).

overwriting/answers written

(2) Negative mark

lsewheremultiple answers at different places! writ

(9) Aine sheets without Name & 1D number willbe awarded sro marks

ID Nox Name |

3 3 10

crate

= 6 {7

o 1A TD

{ft register (DOD1D2D3) shown below

The initial contents of the 4-bit synchronous shi v ny

the contents of the shift register will

are 0110, respectively. After three clock pulses,

be:

ae TT

(A) 0000. (B) 0101 (C) 1010 (D) 111

input X and one output Z is defined by state

2. A finite state machine (FSM) with one

A. Given is the following

me the FSM starts in state

diagram shown below. Assu

sequence of input values X: 100101101010. What will be the final state at the end of

the above sequence?

a i

Re

Je Table 1) shown in below. Ifthe state table is reduced, what

0 he state tab

6. Consider the oe ‘ent state combinations

would be all possible Pres

(B) ABCD/ CDEF/ACDF

/BCDF

(p) BCDE/ CDEF/ACDF

(a) ABCD! CDE

CDF

(© ancp/ BCI

ofa sequential circuit

Output

Tnput

state able (Table 1). If the state table is reduced, what would be

ions for the input X=

(B) CDBB/DEED/CDDF

7. Consider the above

all possible next state combinati

(A) 4) DEED/EEDCICDDC

(C) CDBB/CECC/CDDC (D) CDBB/EEDC/DBBC

tial synchronous circuit shown below is initialized with Q3QiQu~

)) for the next 3 clock cycles is

8. The sequen = 000.

‘The state sequence (QQ)

(A) 001, 010, 011 (B) 111,110, 101 (©) 100, 110, 111 (D) 100, O11, OO"

9, Which of the memory holds the information when the power supply is switched off?

(A) Static RAM (B) Dynamic RAM (C)EEROM (0D) All of these

10. How many address lines are needed to address each memory location ina 2048 x 4

©s oF

Digital Desir @arz-2_Selaliown

Drgitel Dsge Garena Se

4° Whol! o\\9

eee NON

meth + 0

east: (\

pus: 1olo

2 Soc

Se. “ GMH2

paSons

ii 5 tales

ee at:

eo pecp [ever [scdF

q canto | PLAS

oo

ees

PC (Q

ems oo :

Oe, +

PD)

b

HYDERABAD CAMPUS

RIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI,

First Semester, 2019-2020

Digital Design

Quis -IT (Open Book)

Date: 02/11/2019 Marks:

Times 2:00 ~ 2:40 pm (40 MINUTES)

Nore: :

Q) An write down the answers (only CAPITAL A, B,C

h carrying 2M) and

cr all 12. Questions

1D) inside the BOX given.

0.5) for each wrong answer: For any

‘with pencil leads to Zero (0).

overwriting/answers written

(2) Negative mark

lsewheremultiple answers at different places! writ

(9) Aine sheets without Name & 1D number willbe awarded sro marks

ID Nox Name |

3 3 10

crate

= 6 {7

o 1A TD

{ft register (DOD1D2D3) shown below

The initial contents of the 4-bit synchronous shi v ny

the contents of the shift register will

are 0110, respectively. After three clock pulses,

be:

ae TT

(A) 0000. (B) 0101 (C) 1010 (D) 111

input X and one output Z is defined by state

2. A finite state machine (FSM) with one

A. Given is the following

me the FSM starts in state

diagram shown below. Assu

sequence of input values X: 100101101010. What will be the final state at the end of

the above sequence?

a i

Re

Je Table 1) shown in below. Ifthe state table is reduced, what

0 he state tab

6. Consider the oe ‘ent state combinations

would be all possible Pres

(B) ABCD/ CDEF/ACDF

/BCDF

(p) BCDE/ CDEF/ACDF

(a) ABCD! CDE

CDF

(© ancp/ BCI

ofa sequential circuit

Output

Tnput

state able (Table 1). If the state table is reduced, what would be

ions for the input X=

(B) CDBB/DEED/CDDF

7. Consider the above

all possible next state combinati

(A) 4) DEED/EEDCICDDC

(C) CDBB/CECC/CDDC (D) CDBB/EEDC/DBBC

tial synchronous circuit shown below is initialized with Q3QiQu~

)) for the next 3 clock cycles is

8. The sequen = 000.

‘The state sequence (QQ)

(A) 001, 010, 011 (B) 111,110, 101 (©) 100, 110, 111 (D) 100, O11, OO"

9, Which of the memory holds the information when the power supply is switched off?

(A) Static RAM (B) Dynamic RAM (C)EEROM (0D) All of these

10. How many address lines are needed to address each memory location ina 2048 x 4

©s oF

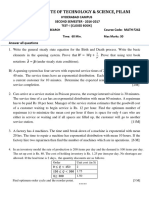

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI HYDERABAD CAMPUS

First Semester, 2019-2020

Digital Design

Quis -11 (Open Book)

“Dime: 2:00 2:40 pm (40 MINUTES) Date: 02/11/2019 Marks: 24

‘0

ne ‘APITAL A, B,C

er all 12. Questions (etch earrying 2M) and write down the answers (only C

(1) Ans

and D) inside the BOX given,

Q ve -0,8) for cach wrong answer, For any overwriting/answers written

‘lsewhere/multiple answers at different places! wnting with peneil leads to Zero (0),

(3) Answer sheets witho » number will be awarded zor

Name:

= teae

pte te

ed by state

the following

ate at the end of

tate machine (

diagram shown below. Assume the FSM starts in state A

sequence of input values X: 100101101010, What will be the final

the above sequence?

010

(A) State C (B)StateA (C)StateB_—_ (D) None of these

2. Aring counter consisting of five flip-flops is fed with input 10000. The number of

different states possible?

(A)6 states (B)4 states (C)5 states (D) 4 or 5 or 6 states

3. The initial contents of the 4-bit synchronous shift register (D0D1D2D3) shown below

te 0110, respectively. After three clock pulses, the aie of the aoe will

Ids the information when the power supply is switched off?

©) EEROM (D) All of these

6. Which of the memory hol

(B) Dynamic RAM

to D flip-flop, instead of connecting an inverter

hile converting JK flip-flop v

Pres ahd nputs a buffer has been connected. The resulting circuit will act

(A)JK flip-flop (B) T Mip-flop

(A) Static RAM

(C)D flip-flops (D) None of these

shown below is initialized with Q2Q1Qo = 000.

‘lock eycles is

8. The sequential synchronous: circuit

‘The state sequence (Q3QiQh) for the next 3 cl

(A) 001, 010, OL (B) 111, 110, 101 (C) 100, 110, 111 (D) 100, 011, 001

9, How many address lines are needed to address each memory location in a 2048 x 4

memory chip?

AIL (B) 10 os D4

10, Consider the below state table (Table 1). Ifthe state table is reduced, what would

be all possible next state combinations for the input_X-

(A) DEED/EEDC/CDDC (8) CDBB/DEEDICDDF-

(C) CDBBICECC/CDDC (D) CDBB/EEDC/DBBC

Table 1: State table of a sequential circuit

Present ‘Next State Output

Input [Input [Input] Input

(X&0) | 1 | 9) | CH)

+3} ] a] >|

92] |]o]-=]o0

a} o |r|}

Jolo|Hlo|—

ole|—|-|ele

11. Consider the state table (Table 1) shown above, If the state table i

would be all possible present state combinations ee

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI, HYDERABAD € AMPUS

2 First Semester, 2019-202

Digital Design

Quis a Book)

.00 — 2:40 pm (40 MINUTES) Date: 02/11/2019

Marks: 24

NOTE:

(1) Answer all 12 Questions (each carrying

‘and D) inside the BOX given. :

2) ive marking (-0.5) for each wrong answer, For any ove

= fing with pencil leads to Zen

be aw: °

M1) and write down the answers (only CAPITAL A. B, €

written

‘elsewhere/multiple answers at different places. w 0 (0)

(3) Answer sheets without Name & ID number wi

TDN:

ynchronous shift register (D0DID2D3) shown below

ft register will

The initial contents of the 4-bit

are 0110, respectively. After three clock pulses, the contents of the s

ate tbe Te

(a) 0101 (B) 1010 (©) 0000 @m nn

2. A finite state machine (FSM) with one input X and one output Z is defined by state

diagram shown below. Assume the FSM starts in state A. Given is the following

sequence of input values X: 100101101010. What will be the final state at the end of

the above sequence?

ar cy

) shown in below. If the state table 18 reduced,

state table (Table |

combinations

Consider th

. | possible present state

would be all

(B) ABCD/ CDEF/ACDF

(A) BCDE/ CDEF/ACDF

(©) ABCD! CDEF/BCDF

‘Table 1: State table of

Present Next St

(p) ABCD/ BCEF/ACDF

ential circuit__

“Output |

Input

ble (Table 1). Ifthe state table is reduced, what would be

forthe input

(B) CDBBIDE! /D/ICDDF

7. Consider the above state tal

all possible next state combinations

(A) DEED/EEDC/CDDC

(©) CDBBICECCICDDC (D) CDBB/EEDC/DBBC

000.

8. ‘The sequential synchronous circuit shown below is initialized with Q:21Q0

‘The state sequence (Q:01Q1) for the next 3 clock cycles is

(A)001, 010,011 B)100, 110, 111, (©) 111, 110, 101 (D) 100, 011, 001

6, Which of the memory holds the information when the power supply is switched off?

(A)Flash —_(B) Static RAM (C)DynamicRAM —_(D) All of these

10, How many address lines are needed to adr ion i

oes address each memory location in a 1024 x 4

(4

BIRLA INSTITUTE OF TEC!

1

Nor!

(1) Answer all 12 ¢

‘and D) inside the BOX given,

(2) Negative marking (0.5) for

(3) Answer

RABAD CAMPUS

TENCE, PLANT, HYDE!

NOLOGY AND S

First Semester, 2019-2020

Digital Design

Quiz -11 (Open Book)

Date: 02/11/2019 Marks: 24

2:0 2:40 pm (40 MINUTES)

E:

Questions (each carrying 2M) and write down the answers (only CAPITAL A, B, C

riting/answers written

‘each wrong answer. For any ove

with pencil leads to Zero (0).

Feewbere'multiple answers at different places! writ

reefs without Name & 1D number w

Name:

te awarded zero marks.

input X and one output Z is defined b;

SSM starts in state A. Given is the following

be the final state at the end of

1. A finite state machine (FSM) with on yy state

diagram shown below. Assume the F

sequence of input values X: 100101101010. What will

the above sequence?

omy wy

(4) 5

(A) State B B)StateA (C)StateC_—_—_(D) None of these

2. Acting counter consisting of five flip-flops is fed with input 10000. The number of

different states possible?

(A)Sstates (B)4 states (C)6states (D) 4 or 5 or 6 states

3, The initial contents of the 4-bit synchronous shift register (DUD1D2D3) shown b

i el

‘are 0110, respectively. After three clock pulses, the contents of the ch register will

be:

ve invformation ote the power aly 10 ww ene OTP

(19) All at thee

6. Which of the memory holds t

(A) EEPROM (B) Dynamic RAM. (©) Sta" WAM

aieuel wf ennneeting AN HNREER

flop to D-flip-flopy ii

wl ve reat ing etreial WHE we

7. While converting JK flip

rere a itz and K inputs a bulTer has Been cone

as

(A) IK flip-flop.

(B)DMip-flop —_-(C) TH» flops (1d) None a ne

below te initialized with QiO)/Qh © O00.

4 clock eyelet

(©) 100,011,001) 100 TE

8, The sequential synchronous citenit shown

The state sequence (Qs) Qy) for the next

(A) 001, 010, O11 (By HLL, LO, or

0 |

hy

6, How many address lines are needed (o address each memory Hoeatton Ik ana

memory chip?

A) 10 (By iL 8 (ya

10. Consider the below state table (Table 1). If the state: table in redueed, what would

be all possible next state combinations for the input Net

(A) DEED/EEDC/CDDC (B) CDBB/DEEDC DDN

(©) CDBBICECC/CDDC (D) CDBB/EEDO/DBBC

‘Table 1: State table ofa sequential citeuit

Present Next State Ont

Input J Input | Tapat | Tapa

(X41) | (X=0) | (X1)

(X0)

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (346)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- ED Quiz 2 Questions and AnswersDocument6 pagesED Quiz 2 Questions and AnswersMahi ChapliNo ratings yet

- Birla Institute of Technology and Science-Pilani, Hyderabad CampusDocument1 pageBirla Institute of Technology and Science-Pilani, Hyderabad CampusMahi ChapliNo ratings yet

- Birla Institute of Technology and Science-Pilani, Hyderabad CampusDocument2 pagesBirla Institute of Technology and Science-Pilani, Hyderabad CampusMahi ChapliNo ratings yet

- Birla Institute OF Technology & Science, Pilani: Hyderabad Campus SECOND SEMESTER - 2016-2017 Course Code: MATH F242Document8 pagesBirla Institute OF Technology & Science, Pilani: Hyderabad Campus SECOND SEMESTER - 2016-2017 Course Code: MATH F242Mahi ChapliNo ratings yet