Professional Documents

Culture Documents

Sn74als133 PDF

Sn74als133 PDF

Uploaded by

Juan Alberto Grande LopezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sn74als133 PDF

Sn74als133 PDF

Uploaded by

Juan Alberto Grande LopezCopyright:

Available Formats

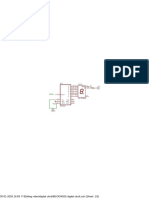

SN54ALS133, SN74ALS133

13-INPUT POSITIVE-NAND GATES

SDAS202B – APRIL 1982 – REVISED DECEMBER 1994

• Package Options Include Plastic SN54ALS133 . . . J PACKAGE

Small-Outline (D) Packages, Ceramic Chip SN74ALS133 . . . D OR N PACKAGE

(TOP VIEW)

Carriers (FK), and Standard Plastic (N) and

Ceramic (J) 300-mil DIPs

A 1 16 VCC

description B 2 15 M

C 3 14 L

These devices contain a 13-input positive-NAND D 4 13 K

gate. They perform the following Boolean E 5 12 J

functions in positive logic: F 6 11 I

Y = A• B• C • D • E• F • G • H• I • J • K• L • M G 7 10 H

GND 8 9 Y

Y = A+ B+ C+ D + E+ F + G + H+ I + J + K+ L + M

The SN54ALS133 is characterized for operation

SN54ALS133 . . . FK PACKAGE

over the full military temperature range of – 55°C

(TOP VIEW)

to 125°C. The SN74ALS133 is characterized for

VCC

operation from 0°C to 70°C.

NC

M

B

A

FUNCTION TABLE

3 2 1 20 19

OUTPUT C 4 18 L

INPUTS A – M

Y D 5 17 K

All inputs H L NC 6 16 NC

One or more inputs L H E 7 15 J

F 8 14 I

9 10 11 12 13

Y

G

H

NC

GND

NC – No internal connection

logic symbol† logic diagram (positive logic)

1

1 & A

A 2

2 B

B 3

3 C

C 4

4 D

D 5

5 E

E 6

6 F

7 9

F Y

7 9 G

G Y 10

10 H

H 11

11 I

I 12

12 J

J 13

13 K

K 14

14 L

L 15

15 M

M

† This symbol is in accordance with ANSI/IEEE Std 91-1984 and

IEC Publication 617-12.

Pin numbers shown are for the D, J, and N packages.

PRODUCTION DATA information is current as of publication date. Copyright 1994, Texas Instruments Incorporated

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

SN54ALS133, SN74ALS133

13-INPUT POSITIVE-NAND GATES

SDAS202B – APRIL 1982 – REVISED DECEMBER 1994

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

Supply voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Input voltage, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Operating free-air temperature range, TA: SN54ALS133 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 55°C to 125°C

SN74ALS133 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 65°C to 150°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

recommended operating conditions

SN54ALS133 SN74ALS133

UNIT

MIN NOM MAX MIN NOM MAX

VCC Supply voltage 4.5 5 5.5 4.5 5 5.5 V

VIH High-level input voltage 2 2 V

0.8‡ 0.8

VIL Low level input voltage

Low-level V

0.7§

IOH High-level output current – 0.4 – 0.4 mA

IOL Low-level output current 4 8 mA

TA Operating free-air temperature – 55 125 0 70 °C

‡ Applies over temperature range – 55°C to 70°C

§ Applies over temperature range 70°C to 125°C

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

SN54ALS133 SN74ALS133

PARAMETER TEST CONDITIONS UNIT

MIN TYP¶ MAX MIN TYP¶ MAX

VIK VCC = 4.5 V, II = –18 mA –1.2 –1.5 V

VOH VCC = 4.5 V to 5.5 V, IOH = – 0.4 mA VCC – 2 VCC – 2 V

IOL = 4 mA 0.25 0.5 0.25 0.4

VOL VCC = 4 5V

4.5 V

IOL = 8 mA 0.35 0.5

II VCC = 5.5 V, VI = 7 V 0.1 0.1 mA

IIH VCC = 5.5 V, VI = 2.7 V 20 20 µA

IIL VCC = 5.5 V, VI = 0.4 V – 0.1 – 0.1 mA

IO# VCC = 5.5 V, VO = 2.25 V – 20 –112 – 30 –112 mA

ICCH VCC = 5.5 V, VI = 0 0.24 0.34 0.24 0.34 mA

ICCL VCC = 5.5 V, VI = 4.5 V 0.56 0.8 mA 0.56 0.08

¶ All typical values are at VCC = 5 V, TA = 25°C.

# The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

2 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54ALS133, SN74ALS133

13-INPUT POSITIVE-NAND GATES

SDAS202B – APRIL 1982 – REVISED DECEMBER 1994

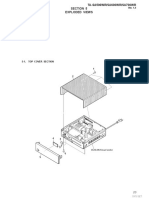

switching characteristics (see Figure 1)

VCC = 4.5 V to 5.5 V,

CL = 50 pF,

FROM TO RL = 500 Ω,

PARAMETER

(INPUT) (OUTPUT) TA = MIN to MAX† UNIT

SN54ALS133 SN74ALS133

MIN MAX MIN MAX

tPLH 1 16 3 11

Any Y ns

tPHL 1 47 5 25

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 3

SN54ALS133, SN74ALS133

13-INPUT POSITIVE-NAND GATES

SDAS202B – APRIL 1982 – REVISED DECEMBER 1994

PARAMETER MEASUREMENT INFORMATION

SERIES 54ALS/74ALS AND 54AS/74AS DEVICES

7V

VCC RL = R1 = R2

S1

RL

R1

From Output Test From Output Test From Output Test

Under Test Point Under Test Point Under Test Point

CL RL CL

CL R2

(see Note A) (see Note A)

(see Note A)

LOAD CIRCUIT FOR

BI-STATE LOAD CIRCUIT LOAD CIRCUIT

TOTEM-POLE OUTPUTS FOR OPEN-COLLECTOR OUTPUTS FOR 3-STATE OUTPUTS

Timing 3.5 V High-Level 3.5 V

Input 1.3 V Pulse 1.3 V 1.3 V

0.3 V 0.3 V

th tw

tsu

3.5 V 3.5 V

Data Low-Level

Input 1.3 V 1.3 V 1.3 V 1.3 V

Pulse

0.3 V 0.3 V

VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES PULSE DURATIONS

3.5 V

Output

Control 1.3 V 1.3 V

(low-level

enabling) 0.3 V 3.5 V

tPZL Input 1.3 V 1.3 V

tPLZ

[3.5 V 0.3 V

tPHL

Waveform 1 tPLH

S1 Closed 1.3 V

In-Phase VOH

(see Note B) 1.3 V 1.3 V

VOL Output

tPHZ 0.3 V VOL

tPZH tPLH

VOH tPHL

Waveform 2 VOH

Out-of-Phase

S1 Open 1.3 V 0.3 V 1.3 V 1.3 V

Output

(see Note B)

[0 V (see Note C) VOL

VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS PROPAGATION DELAY TIMES

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. When measuring propagation delay items of 3-state outputs, switch S1 is open.

D. All input pulses have the following characteristics: PRR ≤ 1 MHz, tr = tf = 2 ns, duty cycle = 50%.

E. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuits and Voltage Waveforms

4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

You might also like

- HAM Radio Tutorial - Hamquick Technician Class TutorialsDocument67 pagesHAM Radio Tutorial - Hamquick Technician Class TutorialsCaptain Crunch86% (7)

- GNS430W GNS400WSeriesMaintenanceManual PDFDocument114 pagesGNS430W GNS400WSeriesMaintenanceManual PDFJEFFREY DEE MAURY NORIEGANo ratings yet

- EsquemaDocument24 pagesEsquemaFábio Menezes100% (6)

- Trouble Code List PDFDocument21 pagesTrouble Code List PDFTun Nay AungNo ratings yet

- Battery Life Enhancer Pulsar Rejuvenator ReconditionerDocument2 pagesBattery Life Enhancer Pulsar Rejuvenator Reconditionerk s s kumarNo ratings yet

- Industrial Maintenance BrochureDocument16 pagesIndustrial Maintenance Brochuremokhtariomid_6303816No ratings yet

- Acuson X300: System Replacement of PartsDocument60 pagesAcuson X300: System Replacement of PartsAdriano R. OrtizNo ratings yet

- 03 04 Faradays Laws of Electrolysis and ApplicationsDocument12 pages03 04 Faradays Laws of Electrolysis and ApplicationsTeoh Ah NgohNo ratings yet

- Elektor USA - October 2014 PDFDocument92 pagesElektor USA - October 2014 PDFJean-Pierre Desrochers100% (4)

- Protective AlarmsDocument2 pagesProtective Alarmsgracia100% (2)

- GBO - 018 - E1 - 1 GSM Paging Problems & Solutions-37Document37 pagesGBO - 018 - E1 - 1 GSM Paging Problems & Solutions-37Clive Mangwiro100% (1)

- SOP GermanyDocument4 pagesSOP GermanyAnkit SinghNo ratings yet

- Active DAS PDFDocument60 pagesActive DAS PDFAmîchYànùmälNo ratings yet

- Sn74als133 NAND GateDocument16 pagesSn74als133 NAND Gatepratik gautamNo ratings yet

- 74hc00 NandDocument5 pages74hc00 NandAs'ad ShidqyNo ratings yet

- SN54F32, SN74F32 Quadruple 2-Input Positive-Or Gates: DescriptionDocument19 pagesSN54F32, SN74F32 Quadruple 2-Input Positive-Or Gates: DescriptionAlfonso BlancoNo ratings yet

- DatasheetDocument4 pagesDatasheetdahdoum dahdoumNo ratings yet

- D D D D D D D: SN54AHCT132, SN74AHCT132 Quadruple Positive-Nand Gates With Schmitt-Trigger InputsDocument10 pagesD D D D D D D: SN54AHCT132, SN74AHCT132 Quadruple Positive-Nand Gates With Schmitt-Trigger InputsStuxnetNo ratings yet

- D D D D D D D D D D: Description/ordering InformationDocument21 pagesD D D D D D D D D D: Description/ordering InformationJoil AlvesNo ratings yet

- SN54HC14, SN74HC14 Hex Schmitt-Trigger Inverters: DescriptionDocument5 pagesSN54HC14, SN74HC14 Hex Schmitt-Trigger Inverters: DescriptionvetchboyNo ratings yet

- D D D D: SN54HC42, SN74HC42 4-LINE TO 10-LINE DECODERS (1 of 10)Document6 pagesD D D D: SN54HC42, SN74HC42 4-LINE TO 10-LINE DECODERS (1 of 10)Eva AvilésNo ratings yet

- SN 74 As 21Document18 pagesSN 74 As 21Rốt Nguyễn CàNo ratings yet

- 74AHCT32DDocument6 pages74AHCT32Dpuh1967No ratings yet

- SN74HC04NDocument5 pagesSN74HC04NRama Tenis CopecNo ratings yet

- Description: SN54HC04, SN74HC04 Hex InvertersDocument5 pagesDescription: SN54HC04, SN74HC04 Hex InvertersLeonardo Andres MagiNo ratings yet

- SN 74 Als 86Document19 pagesSN 74 Als 86shengjunyi1029No ratings yet

- 4-Bit Arithmetic Logic Unit SN54/74LS181: Low Power SchottkyDocument7 pages4-Bit Arithmetic Logic Unit SN54/74LS181: Low Power SchottkyMauro JimenezNo ratings yet

- 74LS375Document3 pages74LS375jaja558No ratings yet

- SN 74 Als 153Document20 pagesSN 74 Als 153priyasumbria46No ratings yet

- PlasmaDocument1 pagePlasmaAndrej HučNo ratings yet

- SN54173, SN54LS173A, SN74173, SN74LS173A 4-Bit D-Type Registers With 3-State OutputsDocument19 pagesSN54173, SN54LS173A, SN74173, SN74LS173A 4-Bit D-Type Registers With 3-State OutputsJanet WaldeNo ratings yet

- SN54173, SN54LS173A, SN74173, SN74LS173A 4-Bit D-Type Registers With 3-State OutputsDocument13 pagesSN54173, SN54LS173A, SN74173, SN74LS173A 4-Bit D-Type Registers With 3-State OutputsMauricio MontañoNo ratings yet

- 74as181a DatasheetDocument13 pages74as181a DatasheetJuan AlberjonNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument6 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataAmirNo ratings yet

- RegisterDocument12 pagesRegisterjairomarcanoNo ratings yet

- AM26LS32AC, AM26LS32AI, AM26LS33AC, AM26LS32AM, AM26LS33AM Quadruple Differential Line ReceiversDocument18 pagesAM26LS32AC, AM26LS32AI, AM26LS33AC, AM26LS32AM, AM26LS33AM Quadruple Differential Line ReceiversTestAutomationSel2020No ratings yet

- D D D D D D D D D D: DescriptionDocument30 pagesD D D D D D D D D D: DescriptionChelaru CosminNo ratings yet

- Wiring Diagram: Noise Filter PowerDocument4 pagesWiring Diagram: Noise Filter Powervoicedont dieNo ratings yet

- SN75172 LCB 2 Ci TransceiverDocument16 pagesSN75172 LCB 2 Ci TransceiverHUGO SOARESNo ratings yet

- Manual BookDocument13 pagesManual Bookhabli abelNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument5 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataPaulo Henrique ValérioNo ratings yet

- 74LS174Document3 pages74LS174jaja558No ratings yet

- Srs Warning Light Circuit Malfunction (Always Light Up, When DTC Is Not Output)Document3 pagesSrs Warning Light Circuit Malfunction (Always Light Up, When DTC Is Not Output)Phang KumwingNo ratings yet

- D D D D D D D D: SN75437A Quadruple Peripheral DriverDocument7 pagesD D D D D D D D: SN75437A Quadruple Peripheral DriverCarlos Luis ColmenaresNo ratings yet

- D D D D D D D D D D D: Description/ordering InformationDocument14 pagesD D D D D D D D D D D: Description/ordering InformationКонстантин МережкоNo ratings yet

- 74LS173Document4 pages74LS173jaja558No ratings yet

- SN54ALS04B, SN54AS04, SN74ALS04B, SN74AS04 Hex Inverters: DescriptionDocument5 pagesSN54ALS04B, SN54AS04, SN74ALS04B, SN74AS04 Hex Inverters: DescriptionXain NiaziNo ratings yet

- MC74HC32A Quad 2-Input OR Gate: High Performance Silicon Gate CMOSDocument7 pagesMC74HC32A Quad 2-Input OR Gate: High Performance Silicon Gate CMOSanthony ramosNo ratings yet

- SN 54 Als 258 ADocument20 pagesSN 54 Als 258 ARenzo AponteNo ratings yet

- MC74HC132A Quad 2-Input NAND Gate With Schmitt-Trigger InputsDocument9 pagesMC74HC132A Quad 2-Input NAND Gate With Schmitt-Trigger InputsCarlos AbrahamNo ratings yet

- 4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyDocument4 pages4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyLoth Matheus Barba MazaNo ratings yet

- MC74HC04A Hex Inverter: High Performance Silicon Gate CMOSDocument9 pagesMC74HC04A Hex Inverter: High Performance Silicon Gate CMOSjavierNo ratings yet

- 4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyDocument5 pages4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyJessica RojasNo ratings yet

- Description: Sn54F283 - . - J Package Sn74F283 - . - D or N Package (Top View)Document15 pagesDescription: Sn54F283 - . - J Package Sn74F283 - . - D or N Package (Top View)VallabhNo ratings yet

- D D D D D D: ULN2803A Darlington Transistor ArrayDocument7 pagesD D D D D D: ULN2803A Darlington Transistor ArrayValentin ValoNo ratings yet

- Automotive ISO 9141 Serial Link Driver: MC33199 SemiconductorDocument12 pagesAutomotive ISO 9141 Serial Link Driver: MC33199 SemiconductorromoNo ratings yet

- SN 74 HC 166Document35 pagesSN 74 HC 166Carlos OrtegaNo ratings yet

- Sn74ls165a PDFDocument16 pagesSn74ls165a PDFRachid RifaiNo ratings yet

- D D D D: SN54165, SN54LS165A, SN74165, SN74LS165A Parallel-Load 8-Bit Shift RegistersDocument23 pagesD D D D: SN54165, SN54LS165A, SN74165, SN74LS165A Parallel-Load 8-Bit Shift RegistersВиктор АгарковNo ratings yet

- 74LS151Document3 pages74LS151Kang RoyNo ratings yet

- sn74hct138 PDFDocument21 pagessn74hct138 PDFpabloNo ratings yet

- SN 74 HCT 138Document21 pagesSN 74 HCT 138pabloNo ratings yet

- Description: SN54F04, SN74F04 Hex InvertersDocument16 pagesDescription: SN54F04, SN74F04 Hex InvertersJoão Oliveira BentesNo ratings yet

- sn74hc151 DatasheetDocument21 pagessn74hc151 DatasheetEzra de GraafNo ratings yet

- 74hc00.PDF DatasheetDocument8 pages74hc00.PDF DatasheetjeffersonNo ratings yet

- 4026 Single SSDDocument1 page4026 Single SSDBond JamesNo ratings yet

- SN 74 BCT 756Document12 pagesSN 74 BCT 756COZLNo ratings yet

- SN54ACT574, SN74ACT574 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsDocument6 pagesSN54ACT574, SN74ACT574 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsYenco Barliza DiazNo ratings yet

- Data SheetDocument2 pagesData SheetzureehanNo ratings yet

- Data SheetDocument2 pagesData SheetzureehanNo ratings yet

- 01 Datasheet TTL IC 5400 7400Document25 pages01 Datasheet TTL IC 5400 7400Adriansyah FadhilahPVTELKANo ratings yet

- Beeprog2C: (Ord - No. 60-0059)Document7 pagesBeeprog2C: (Ord - No. 60-0059)hariz harizNo ratings yet

- Ch24 Sample ExerciseDocument17 pagesCh24 Sample ExerciseRobbin LisondraNo ratings yet

- Racetrack Memory Based Reconfigurable ComputingDocument4 pagesRacetrack Memory Based Reconfigurable ComputingAnonymous 9Yv6n5qvSNo ratings yet

- HelicalDocument8 pagesHelicalAnamiya BhattacharyaNo ratings yet

- Iq System Display Module (Iqdm) Owner'S Manual: Program Test DiagnosticsDocument28 pagesIq System Display Module (Iqdm) Owner'S Manual: Program Test Diagnosticsrwh1015015No ratings yet

- Bharat Heavy Electricals Limited: Thermal Power Plant Industrial TrainingDocument20 pagesBharat Heavy Electricals Limited: Thermal Power Plant Industrial TrainingSaurabh SinghNo ratings yet

- Atu500 Manual Nat39d Mar-01-11Document79 pagesAtu500 Manual Nat39d Mar-01-11conionicaNo ratings yet

- Transmission Lines PDFDocument11 pagesTransmission Lines PDFsadNo ratings yet

- Electromagnetic Waves - JEE Main 2023 January Chapter Wise Questions by MathonGoDocument7 pagesElectromagnetic Waves - JEE Main 2023 January Chapter Wise Questions by MathonGoRavi RajNo ratings yet

- FUNAI PLF-76 Service ManualDocument40 pagesFUNAI PLF-76 Service Manualapi-3711045No ratings yet

- MFB VD01 MANUAL (English)Document2 pagesMFB VD01 MANUAL (English)listentomerijnNo ratings yet

- Asus p5gc-Mx - Rev 2.0Document47 pagesAsus p5gc-Mx - Rev 2.0Paulo Roberto Santos Freire67% (3)

- TA-SA500WR ConsumerDocument2 pagesTA-SA500WR ConsumerJulien Bertinchant0% (1)

- Volvo Data Sheet Pcs460-630vDocument4 pagesVolvo Data Sheet Pcs460-630vRobinson GuanemeNo ratings yet

- Scomi SutraDocument6 pagesScomi SutraclearmeistNo ratings yet

- Hardware Development Guide For The MIMXRT1020 Processor: Application NoteDocument24 pagesHardware Development Guide For The MIMXRT1020 Processor: Application NoteKaganovichNo ratings yet

- Control Lab 2Document7 pagesControl Lab 2Kelvin Ting S BNo ratings yet