Professional Documents

Culture Documents

Instruction Set

Uploaded by

finiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Instruction Set

Uploaded by

finiCopyright:

Available Formats

GAS IA-32 Assembly Language Programming

Tony Richardson

April 19, 2007

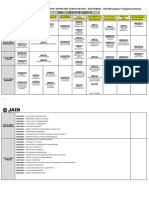

The following table contains a partial list of IA-32 assembly mnemonics. An S in the mnemonic represents a size

specification letter of either b (8 bits), w (16 bits) or l (32 bits). If one of the operands is a register, then the register name

implies an operand size and the specification letter may be omitted. For example, either “movl %eax, count” or “mov

%eax, count” may be used and the 32-bit contents of register EAX will be copied to the memory location labeled count.

However, when using “movS $30, count” then S must be replaced with b, w, or l to indicate if the 30 is being copied to a

byte, a word or an int location in memory.

In the operand columns, i represents an immediate (numeric) operand, r a register and m a memory location. If the operand

is enclosed in brackets, then it is optional. A destination operand appears on the same line as a corresponding source

operand. The adc/add entry below indicates that if the first operand is either immediate or a register then the second

operand can be either a register or memory location. If the first operand is a memory location, then the second operand

must be a register.

Memory references are of the form disp(base, index, scale) where base and index are optional 32-bit base and index

registers, disp is an optional displacement, and scale may have the values 1 (default), 2, 4, or 8. The actual address is equal

to disp + base + index * scale. Here are a few examples (assume that xarray labels the first element of an array of ints):

# Direct addressing

movl xarray, %eax # move first element of array into EAX

# Indexed addressing

movl $0, %edi

movl xarray(,%edi,4), %eax # move first element of array into EAX

incl %edi

movl xarray(,%edi,4), %eax # move second element of array into EAX

movl $10, %edi

movl xarray(,%edi,4), %eax # move eleventh element of array into EAX

# Indirect addressing

movl $xarray, %ebx # move base address into EBX

movl (%ebx), %eax # move first element of array into EAX

movl $0, %edi

movl (%ebx, %edi, 4), %eax # move first element of array into EAX

incl %edi

movl (%ebx, %edi, 4), %eax # move second element of array into EAX

movl $10, %edi

movl (%ebx, %edi, 4), %eax # move second element of array into EAX

# The displacement may be negative.

# This is also an example of indirect addressing.

movl -4(%ebp), %eax # move data from stack frame into EAX

This is only a partial list of mnemonics. Floating-point processor, undocumented, MMX, SSE, and SSE2 instructions have

been omitted. 16-bit mode and privileged mode specific instructions have also been left out. The table was extracted from

the NASM documentation and converted to AT&T syntax. I recommend the NASM documentation (as well as the Intel

documentation) as a complete source of documentation for IA-32 assembly language programming.

Richardson 1 Spring 2006

Mnemonic Op 1 Op 2 Description

(SRC) (DEST)

aaa ASCII Adjustments

aas AAA (ASCII Adjust After Addition) should be used after a one−byte ADD instruction

whose destination was the AL register: by means of examining the value in the low

nibble of AL and also the auxiliary carry flag AF, it determines whether the addition has

overflowed, and adjusts it (and sets the carry flag) if so. You can add long BCD strings

together by doing ADD/AAA on the

low digits, then doing ADC/AAA on each subsequent digit.

AAS (ASCII Adjust AL After Subtraction) works similarly to AAA, but is for use after

SUB instructions rather than ADD.

aam [i] ASCII Adjustments

aad AAM (ASCII Adjust AX After Multiply) is for use after you have multiplied two

decimal digits together and left the result in AL: it divides AL by ten and stores the

quotient in AH, leaving the remainder in AL. The divisor 10 can be changed by

specifying an operand to the instruction: a particularly handy use of this is AAM 16,

causing the two nibbles in AL to be separated into AH and AL.

AAD (ASCII Adjust AX Before Division) performs the inverse operation to AAM: it

multiplies AH by ten, adds it to AL, and sets AH to zero. The multiplier 10 can be

changed.

adcS i/r r/m Add with Carry, Add

addS m r ADC performs integer addition: it adds its two operands together, plus the value of the

carry flag, and leaves the result in its destination operand. The destination operand can

be a register or a memory location. The source operand can be a register, a memory

location or an immediate value.

ADD performs integer addition: it adds its two operands together, and leaves the result

in its destination operand. The destination operand can be a register or a memory

location. The source operand can be a register, a memory location or an immediate

value.

The flags are set according to the result of the operation: in particular, the carry flag is

affected and can be used by a subsequent ADC instruction.

andS i/r r/m Bitwise AND

m r AND performs a bitwise AND operation between its two operands (i.e. each bit of the

result is 1 if and only if the corresponding bits of the two inputs were both 1), and stores

the result in the destination operand. The destination operand can be a register or a

memory location. The source operand can be a register, a memory location or an

immediate value.

boundS r m Check Array Index Against Bounds

BOUND expects its second operand to point to an area of memory containing two

signed values of the same size as its first operand (i.e. two words for the 16−bit form;

two doublewords for the 32−bit form). It performs two signed comparisons: if the value

in the register passed as its first operand is less than the first of the in−memory values,

or is greater than or equal to the second, it throws a BR exception. Otherwise, it does

nothing.

bsfS r/m r Bit Scan

bsrS BSF searches for the least significant set bit in its source operand, and if it finds one,

stores the index in its destination operand. If no set bit is found, the contents of the

destination operand are undefined. If the source operand is zero, the zero flag is set.

Richardson 2 Spring 2006

BSR performs the same function as BSF, but searches from the top instead, so it finds

the most significant set bit.

Bit indices are from 0 (least significant) to 15 or 31 (most significant). The destination

operand can only be a register. The source operand can be a register or a memory

location.

bswapl r Byte Swap

BSWAP swaps the order of the four bytes of a 32−bit register: bits 0−7 exchange places

with bits 24−31, and bits 8−15 swap with bits 16−23. There is no explicit 16−bit

equivalent: to byte−swap AX, BX, CX or DX, XCHG can be used.

btS i r/m Bit Test

btcS r r/m These instructions all test one bit of their second operand, whose index is given by the

btrS first operand, and store the value of that bit into the carry flag. Bit indices are from 0

btsS (least significant) to 15 or 31 (most significant).

In addition to storing the original value of the bit into the carry flag, BTR also resets

(clears) the bit in the operand itself. BTS sets the bit, and BTC complements the bit. BT

does not modify its operands.

The destination can be a register or a memory location. The source can be a register or

an immediate value.

If the destination operand is a register, the bit offset should be in the range 0−15 (for

16−bit operands) or 0−31 (for 32−bit operands). An immediate value outside these

ranges will be taken modulo 16/32 by the processor.

If the destination operand is a memory location, then an immediate bit offset follows the

same rules as for a register. If the bit offset is in a register, then it can be anything within

the signed range of the register used (ie, for a 32−bit operand, it can be (−2^31) to (2^31

– 1)

call i Call Subroutine

CALL calls a subroutine, by means of pushing the current instruction pointer (IP) on the

stack, and then jumping to a given address.

cbw/cbtw Sign Extensions

cwde/cwtl All these instructions sign−extend a short value into a longer one, by replicating the top

cwd/cwtd bit of the original value to fill the extended one.

cdq/cltd

CBW extends AL into AX by repeating the top bit of AL in every bit of AH. CWDE

extends AX into EAX. CWD extends AX into DX:AX by repeating the top bit of AX

throughout DX, and CDQ extends EAX into EDX:EAX.

CBTW is a synonym for CBW. Similarly CWTL, CWTD, CLTD are synonyms for

CWDE, CWD, and CDQ respectively.

clc Clear Flags

cld These instructions clear various flags. CLC clears the carry flag; CLD clears the

cli direction flag; and CLI clears the interrupt flag (thus disabling interrupts).

To set the carry, direction, or interrupt flags, use the STC, STD and STI instructions.

To invert the carry flag, use CMC.

cmc Complement Carry Flag

CMC changes the value of the carry flag: if it was 0, it sets it to 1, and vice versa.

cmovCC r/m r Conditional Move

Richardson 3 Spring 2006

CMOV moves its source (first) operand into its destination (second) operand if the

given condition code is satisfied; otherwise it does nothing.

For a list of condition codes see the jCC (conditional branch) instruction.

These instructions are only available in the P6 family of Pentium processors (Pentium

Pro, Pentium II, and newer).

cmpS i/r r/m Compare Integers

r/m r CMP performs a ‘mental’ subtraction of its first operand from its second operand, and

affects the flags as if the subtraction had taken place, but does not store the result of the

subtraction anywhere

cmpsS Compare Strings

CMPSB compares the byte at %DS:(%ESI) with the byte at %ES:(%EDI), and sets the

flags accordingly. It then increments or decrements (depending on the direction flag:

increments if the flag is clear, decrements if it is set) ESI and EDI.

The segment register used to load from (%ESI) can be overridden by using a segment

register name as a prefix (for example, ES CMPSB). The use of ES for the load from

(%EDI) cannot be overridden.

CMPSW and CMPSL work in the same way, but they compare a word or a doubleword

instead of a byte, and increment or decrement the addressing registers by 2 or 4 instead

of 1.

The REPE and REPNE prefixes (equivalently, REPZ and REPNZ) may be used to

repeat the instruction up to %ECX times until the first unequal or equal byte is found.

cmpxchgS r r/m Compare and Exchange

CMPXCHG compares its destination (second) operand to the value in AL, AX or EAX

(depending on the operand size of the instruction). If they are equal, it copies its source

(first) operand into the destination and sets the zero flag. Otherwise, it clears the zero

flag and copies the destination register to AL, AX or EAX.

CMPXCHG is intended to be used for atomic operations in multitasking or

multiprocessor environments. To safely update a value in shared memory, for example,

you might load the value into EAX, load the updated value into EBX, and then execute

the instruction LOCK CMPXCHG %EBX, VALUE. If value has not changed since

being loaded, it is updated with your desired new value, and the zero flag is set to let

you know it has worked. (The LOCK prefix prevents another processor doing anything

in the middle of this operation: it guarantees atomicity.) However, if another processor

has modified the value in between your load and your attempted store, the store does not

happen, and you are notified of the failure by a cleared zero flag, so you can go round

and try again.

cmpxchg8b m Compare and Exchange Eight Bytes

This is a larger and more unwieldy version of CMPXCHG: it compares the 64−bit

(eight−byte) value stored at m with the value in EDX:EAX. If they are equal, it sets the

zero flag and stores ECX:EBX into the memory area. If they are unequal, it clears the

zero flag and stores the memory contents into EDX:EAX.

CMPXCHG8B can be used with the LOCK prefix, to allow atomic execution. This is

useful in multi−processor and multi−tasking environments.

cpuid Get CPU Identification Code

CPUID returns various information about the processor it is being executed on. It fills

the four registers EAX, EBX, ECX and EDX with information, which varies depending

Richardson 4 Spring 2006

on the input contents of EAX.

CPUID also acts as a barrier to serialise instruction execution: executing the CPUID

instruction guarantees that all the effects (memory modification, flag modification,

register modification) of previous instructions have been completed before the next

instruction gets fetched.

The information returned is as follows:

• If EAX is zero on input, EAX on output holds the maximum acceptable input

value of EAX, and EBX:EDX:ECX contain the string "GenuineIntel" (or not,

if you have a clone processor). That is to say, EBX contains "Genu", EDX

contains "ineI" and ECX contains "ntel".

• If EAX is one on input, EAX on output contains version information about the

processor, and EDX contains a set of feature flags, showing the presence and

absence of various features. For example, bit 8 is set if the CMPXCHG8B

instruction is supported, bit 15 is set if the conditional move instructions are

supported, and bit 23 is set if MMX instructions are supported.

• If EAX is two on input, EAX, EBX, ECX and EDX all contain information

about caches and TLBs (Translation Lookahead Buffers).

daa Decimal Adjustments

das These instructions are used in conjunction with the add and subtract instructions to

perform binary−coded decimal arithmetic in packed (one BCD digit per nibble) form.

DAA should be used after a one−byte ADD instruction whose destination was the AL

register: by means of examining the value in the AL and also the auxiliary carry flag

AF, it determines whether either digit of the addition has overflowed, and adjusts it (and

sets the carry and auxiliary−carry flags) if so. You can add long BCD strings together

by doing ADD/DAA on the low two digits, then doing ADC/DAA on each subsequent

pair of digits.

DAS works similarly to DAA, but is for use after SUB instructions rather than ADD.

decS r/m Decrement Integer

DEC subtracts 1 from its operand. It does not affect the carry flag: to affect the carry

flag, use SUB 1, something. DEC affects all the other flags according to the result.

This instruction can be used with a LOCK prefix to allow atomic execution.

divS r/m Unsigned Integer Divide

DIV performs unsigned integer division. The explicit operand provided is the divisor;

the dividend and destination operands are implicit, in the following way:

• For DIVB, AX is divided by the given operand; the quotient is stored in AL

and the remainder in AH.

• For DIVW, DX:AX is divided by the given operand; the quotient is stored in

AX and the remainder in DX.

• For DIVL, EDX:EAX is divided by the given operand; the quotient is stored in

EAX and the remainder in EDX.

Signed integer division is performed by the IDIV instruction

enter i i Create Stack Frame

ENTER construct a stack frame for a high−level language procedure call. The first

operand gives the amount of stack space to allocate for local variables; the second gives

the nesting level of the procedure (for languages like Pascal, with nested procedures).

The function of ENTER, with a nesting level of zero, is equivalent to

PUSHL %EBP

Richardson 5 Spring 2006

MOVL %ESP, %EBP

SUBL operand1, %ESP

This creates a stack frame with the procedure parameters accessible upwards from EBP,

and local variables accessible downwards from EBP.

With a nesting level of one, the stack frame created is 4 (or 2) bytes bigger, and the

value of the final frame pointer EBP is accessible in memory at –4(%EBP).

This allows ENTER, when called with a nesting level of two, to look at the stack frame

described by the previous value of EBP, find the frame pointer at offset –4 from that,

and push it along with its new frame pointer, so that when a level−two procedure is

called from within a level−one procedure, −4(%EBP) holds the frame pointer of the

most recent level−one procedure call and −8(%EBP) holds that of the most recent

level−two call. And so on, for nesting levels up to 31.

Stack frames created by ENTER can be destroyed by the LEAVE instruction

idivS r/m Signed Integer Divide

IDIV performs signed integer division. The explicit operand provided is the divisor; the

dividend and destination operands are implicit, in the following way:

• For IDIVB, AX is divided by the given operand; the quotient is stored in AL

and the remainder in AH.

• For IDIVW, DX:AX is divided by the given operand; the quotient is stored in

AX and the remainder in DX.

• For IDIVL, EDX:EAX is divided by the given operand; the quotient is stored

in EAX and the remainder in EDX.

Unsigned integer division is performed by the DIV instruction.

imulS r/m Signed Integer Multiply

i/r/m r IMUL performs signed integer multiplication. For the single−operand form, the other

i, r/m r operand and destination are implicit, in the following way:

• For IMULB, AL is multiplied by the given operand; the product is stored in

AX.

• For IMULW, AX is multiplied by the given operand; the product is stored in

DX:AX.

• For IMULL, EAX is multiplied by the given operand; the product is stored in

EDX:EAX.

The two−operand form multiplies its two operands and stores the result in the

destination (second) operand. The three−operand form multiplies its first two operands

and stores the result in the last operand.

In the forms with an 8−bit immediate operand and another longer source operand, the

immediate operand is considered to be signed, and is sign−extended to the length of the

other source operand.

Unsigned integer multiplication is performed by the MUL instruction.

inS i/DX AL Input From I/O Port

i/DX AX IN reads a byte, word or doubleword from the specified I/O port, and stores it in the

i/DX EAX given destination register. The port number may be specified as an immediate value if it

is between 0 and 255, and otherwise must be stored in DX. See also OUT.

incS r/m Increment Integer

Richardson 6 Spring 2006

INC adds 1 to its operand. It does not affect the carry flag: to affect the carry flag, use

ADD $1,something. INC affects all the other flags according to the result.

This instruction can be used with a LOCK prefix to allow atomic execution.

See also DEC.

insS Input String From I/O Port

INSB inputs a byte from the I/O port specified in DX and stores it at %ES:(%EDI). It

then increments or decrements (depending on the direction flag: increments if the flag is

clear, decrements if it is set) EDI.

Segment override prefixes have no effect for this instruction: the use of ES for the load

from (%EDI) cannot be overridden.

INSW and INSL work in the same way, but they input a word or a doubleword instead

of a byte, and increment or decrement the addressing register by 2 or 4 instead of 1.

The REP prefix may be used to repeat the instruction ECX times.

See also OUTSB, OUTSW and OUTSL.

int i Software Interrupt

int3 INT causes a software interrupt through a specified vector number from 0 to 255.

into

INT3 is not precisely equivalent to INT 3: the short form, since it is designed to be used

as a breakpoint, bypasses the normal IOPL checks in virtual−8086 mode, and also does

not go through interrupt redirection.

INTO performs an INT 4 software interrupt if and only if the overflow flag is set.

invd Invalidate Internal Caches

INVD invalidates and empties the processor’s internal caches, and causes the processor

to instruct external caches to do the same. It does not write the contents of the caches

back to memory first: any modified data held in the caches will be lost. To write the

data back first, use WBINVD.

invlpg m Invalidate TLB Entry

INVLPG invalidates the translation lookahead buffer (TLB) entry associated with the

supplied memory address.

iret Return From Interrupt

IRET returns from an interrupt (hardware or software) by means of popping EIP, CS

and the flags off the stack and then continuing execution from the new CS:EIP.

IRET pops EIP as 4 bytes, pops a further 4 bytes of which the top two are discarded and

the bottom two go into CS, and pops the flags as 4 bytes as well, taking 12 bytes off the

stack.

jCC i Conditional Branch

The conditional jump instructions execute a near (same segment) jump if and only if

their conditions are satisfied. For example, JNZ jumps only if the zero flag is not set.

There are 6 status flags that are associated with the conditional jump instructions:

• CF − Carry flag.

Set if an arithmetic operation generates a carry or a borrow out of the

most−significant bit of the result; cleared otherwise. This flag indicates an

overflow condition for unsigned−integer arithmetic. It is also used in

Richardson 7 Spring 2006

multiple−precision arithmetic.

• PF − Parity flag.

Set if the least−significant byte of the result contains an even number of 1 bits;

cleared otherwise.

• AF − Adjust flag.

Set if an arithmetic operation generates a carry or a borrow out of bit 3 of the

result; cleared otherwise. This flag is used in binary−coded decimal (BCD)

arithmetic.

• ZF − Zero flag.

Set if the result is zero; cleared otherwise.

• SF − Sign flag.

Set equal to the most−significant bit of the result, which is the sign bit of a

signed integer. (0 indicates a positive value and 1 indicates a negative value.)

• OF − Overflow flag.

Set if the integer result is too large a positive number or too small a negative

number (excluding the sign−bit) to fit in the destination operand; cleared

otherwise. This flag indicates an overflow condition for signed−integer (two’s

complement) arithmetic.

The condition codes to be used instead of CC are listed below. Many of these condition

codes have synonyms, so several will be listed at a time.

• O indicates the overflow flag is set; NO is the complement.

• B, C and NAE indicate that the carry flag is set; NB, NC and AE are

complements.

• E and Z indicate the zero flag is set; NE and NZ are complements.

• BE and NA indicate that the carry or zero flags is set; NBE and A are

complements.

• S indicates the sign flag is set; NS is complement.

• P and PE indicate that the parity flag is set; NP and PO are complements.

• L and NGE indicate that exactly one of the sign and overflow flags is set; NL

and GE are complements.

• LE and NG indicate that the zero flag is set, or exactly one of the sign and

overflow flags is set; NLE and G are complements.

jcxz i Jump if CX/ECX is Zero

jecxz JCXZ performs a short jump (with maximum range 128 bytes) if and only if the

contents of the CX register is 0. JECXZ does the same thing, but with ECX.

jmp i Jump

JMP jumps to a given address.

lahf Load AH From Flags

LAHF sets the AH register according to the contents of the low byte of the flags word.

The operation of LAHF is:

AH <−− SF:ZF:0:AF:0:PF:1:CF

See also SAHF.

lea m r Load Effection Address

LEA, despite its syntax, does not access memory. It calculates the effective address

specified by its first operand as if it were going to load or store data from it, but instead

it stores the calculated address into the register specified by its second operand. This can

be used to perform quite complex calculations (e.g. LEA 100(%EBX,%ECX,4),

%EAX) in one instruction.

Richardson 8 Spring 2006

LEA, despite being a purely arithmetic instruction which accesses no memory, still

requires that the first operand be written as if it were a memory reference.

leave Destroy Stack Frame

LEAVE destroys a stack frame of the form created by the ENTER instruction. It is

functionally equivalent to MOVL %EBP, %ESP followed by POPL %EBP.

lodsS Load From String

LODSB loads a byte from %DS:(%ESI) into AL. It then increments or decrements

(depending on the direction flag: increments if the flag is clear, decrements if it is set)

ESI.

The segment register used to load from (%ESI) can be overridden by using a segment

register name as a prefix (for example, ES LODSB).

LODSW and LODSL work in the same way, but they load a word or a doubleword

instead of a byte, and increment or decrement the addressing registers by 2 or 4 instead

of 1.

loop i [CX/ECX] LOOP decrements its counter register (either CX or ECX – if one is not specified

loope explicitly, the BITS setting dictates which is used) by one, and if the counter does not

loopz become zero as a result of this operation, it jumps to the given label. The jump has a

range of 128 bytes.

LOOPE (or its synonym LOOPZ) adds the additional condition that it only jumps if the

counter is nonzero and the zero flag is set. Similarly, LOOPNE (and LOOPNZ) jumps

only if the counter is nonzero and the zero flag is clear.

movS i/r r/m Move Data

r/m r MOV copies the contents of its source (second) operand into its destination (first)

operand.

movsS Move String

MOVSB copies the byte at (%ESI) to (%EDI). It then increments or decrements

(depending on the direction flag: increments if the flag is clear, decrements if it is

set) ESI and EDI.

MOVSW and MOVSD work in the same way, but they copy a word or a doubleword

instead of a byte, and increment or decrement the addressing registers by 2 or 4 instead

of 1.

The REP prefix may be used to repeat the instruction ECX times.

movsSS r/m r Move Data with Sign or Zero Extend

movzSS MOVS sign−extends its source operand to the length of its destination operand, and

copies the result into the destination operand. MOVZ does the same, but zero−extends

rather than sign−extending.

Because the source (first) and destination (second) operands are of different sizes two

size specification letters are used in the mnemonic. The first S indicates the size of the

first operand. Possible suffixes are bl (from byte to long), bw (from byte to word), wl

(from word to long), bq (from byte to quadruple word), wq (from word to quadruple

word), and lq (from long to quadruple word).

mulS r/m Unsigned Integer Multiply

MUL performs unsigned integer multiplication. The other operand to the multiplication,

and the destination operand, are implicit, in the following way:

• For MULB AL is multiplied by the given operand; the product is stored in AX.

Richardson 9 Spring 2006

• For MULW, AX is multiplied by the given operand; the product is stored in

DX:AX.

• For MULL, EAX is multiplied by the given operand; the product is stored in

EDX:EAX.

Signed integer multiplication is performed by the IMUL instruction

negS r/m Two's and One's Complement

notS NEG replaces the contents of its operand by the two’s complement negation (invert all

the bits and then add one) of the original value. NOT, similarly, performs one’s

complement (inverts all the bits).

nop No Operation

NOP performs no operation.

orS i/r r/m Bitwise OR

r/m r OR performs a bitwise OR operation between its two operands (i.e. each bit of the result

is 1 if and only if at least one of the corresponding bits of the two inputs was 1), and

stores the result in the destination operand.

out i/DX AL Output Data to I/O Port

i/DX AX OUT writes the contents of the given source register to the specified I/O port. The port

i/DX EAX number may be specified as an immediate value if it is between 0 and 255, and

otherwise must be stored in DX. See also IN.

outsS Output String to I/O Port

OUTSB loads a byte from (%ESI) and writes it to the I/O port specified in DX. It then

increments or decrements (depending on the direction flag: increments if the flag is

clear, decrements if it is set) ESI.

OUTSW and OUTSD work in the same way, but they output a word or a doubleword

instead of a byte, and increment or decrement the addressing registers by 2 or 4 instead

of 1.

The REP prefix may be used to repeat the instruction ECX times.

popS r/m Pop Data From the Stack

POP loads a value from the stack (from (%ESP) and then increments the stack

pointer.

The operand−size attribute of the instruction determines whether the stack pointer is

incremented by 2 or 4.

popa Pop All General Purpose Registers

popaw • POPAW pops a word from the stack into each of, successively, DI, SI, BP,

popal nothing (it discards a word from the stack which was a placeholder for SP),

BX, DX, CX and AX. It is intended to reverse the operation of PUSHAW, but

it ignores the value for SP that was pushed on the stack by PUSHAW.

• POPAL pops twice as much data, and places the results in EDI, ESI, EBP,

nothing (placeholder for ESP), EBX, EDX, ECX and EAX. It reverses the

operation of PUSHAL.

POPA is an alias mnemonic for either POPAW or POPAL, depending on the current

BITS setting.

popf Pop Flags Register

popfw • POPFW pops a word from the stack and stores it in the bottom 16 bits of the

popfl flags register (or the whole flags register, on processors below a 386).

• POPFL pops a doubleword and stores it in the entire flags register.

Richardson 10 Spring 2006

POPF is an alias mnemonic for either POPFW or POPFL, depending on the current

BITS setting. See also PUSHF

pushS i/r/m Push Data on Stack

PUSH decrements the stack pointer, ESP by 2 or 4, and then stores the given value at

(%ESP).

The operand−size attribute of the instruction determines whether the stack pointer is

decremented by 2 or 4.

pusha Push All General-Purpose Registers

pushaw PUSHAW pushes, in succession, AX, CX, DX, BX, SP, BP, SI and DI on the stack,

pushal decrementing the stack pointer by a total of 16.

PUSHAL pushes, in succession, EAX, ECX, EDX, EBX, ESP, EBP, ESI and EDI on

the stack, decrementing the stack pointer by a total of 32.

In both cases, the value of SP or ESP pushed is its original value, as it had before the

instruction was executed.

PUSHA is an alias mnemonic for either PUSHAW or PUSHAL, depending on the

current BITS setting.

pushf Push Flags Register

pushfw • PUSHFW pops a word from the stack and stores it in the bottom 16 bits of the

pushfl flags register (or the whole flags register, on processors below a 386).

• PUSHFD pops a doubleword and stores it in the entire flags register.

PUSHF is an alias mnemonic for either PUSHFW or PUSHFL, depending on the

current BITS setting. See also POPF

rclS 1/CL/i r/m Bitwise Rotate Through Carry Bit

rcrS RCL and RCR perform a 9−bit, 17−bit or 33−bit bitwise rotation operation, involving

the given source/destination (second) operand and the carry bit. Thus, for example, in

the operation RCLB $1,%AL, a 9−bit rotation is performed in which AL is shifted left

by 1, the top bit of AL moves into the carry flag, and the original value of the carry flag

is placed in the low bit of AL.

The number of bits to rotate by is given by the first operand. Only the bottom five bits

of the rotation count are considered by processors above the 8086.

ret [i] Return From Procedure Call

retn RET, and its exact synonym RETN, pop EIP from the stack and transfer control to the

new address. Optionally, if a numeric second operand is provided, they increment the

stack pointer by a further i bytes after popping the return address.

rolS 1/CL/i r/m Bitwise Rotate

rorS ROL and ROR perform a bitwise rotation operation on the given source/destination

(second) operand. Thus, for example, in the operation ROLB 1, AL, an 8−bit rotation is

performed in which AL is shifted left by 1 and the original top bit of AL moves round

into the low bit.

The number of bits to rotate by is given by the first operand. Only the bottom five bits

of the rotation count are considered by processors above the 8086.

sahf Store AH to Flags

SAHF sets the low byte of the flags word according to the contents of the AH register.

The operation of SAHF is:

Richardson 11 Spring 2006

AH −−> SF:ZF:0:AF:0:PF:1:CF

See also LAHF

salS 1/CL/i r/m Bitwise Arithmetic Shifts

sarS SAL and SAR perform an arithmetic shift operation on the given source/destination

(second) operand. The vacated bits are filled with zero for SAL, and with copies of the

original high bit of the source operand for SAR. SAL is a synonym for SHL.

The number of bits to shift by is given by the first operand. Only the bottom five bits of

the shift count are considered by processors above the 8086.

sbbS i/r r/m Subtract With Borrow

r/m r SBB performs integer subtraction: it subtracts its first operand, plus the value of the

carry flag, from its second, and leaves the result in its destination (second) operand. The

flags are set according to the result of the operation: in particular, the carry flag is

affected and can be used by a subsequent SBB instruction.

To subtract one number from another without also subtracting the contents of the carry

flag, use SUB.

scasS Scan String

SCASB compares the byte in AL with the byte at (%EDI), and sets the flags

accordingly. It then increments or decrements (depending on the direction flag:

increments if the flag is clear, decrements if it is set) EDI.

SCASW and SCASD work in the same way, but they compare a word to AX or a

doubleword to EAX instead of a byte to AL, and increment or decrement the addressing

registers by 2 or 4 instead of 1.

The REPE and REPNE prefixes (equivalently, REPZ and REPNZ) may be used to

repeat the instruction up to ECX times until the first unequal or equal byte is found.

setCC r/m Set Register From Condition

SETcc sets the given 8−bit operand to zero if its condition is not satisfied, and to 1 if it

is.

See Jcc for list of condition codes.

shlS 1/CL/i r/m Bitwise Logical Shifts

shrS SHL and SHR perform a logical shift operation on the given source/destination (second)

operand. The vacated bits are filled with zero. A synonym for SHL is SAL.

The number of bits to shift by is given by the second operand. Only the bottom five bits

of the shift count are considered by processors above the 8086.

stc Set Flags

std These instructions set various flags. STC sets the carry flag; STD sets the direction flag;

sti and STI sets the interrupt flag (thus enabling interrupts).

To clear the carry, direction, or interrupt flags, use the CLC, CLD and CLI instructions.

To invert the carry flag, use CMC.

stosS Store Byte to String

STOSB stores the byte in AL at (%EDI), and sets the flags accordingly. It then

increments or decrements (depending on the direction flag: increments if the flag is

clear, decrements if it is set) EDI.

STOSW and STOSD work in the same way, but they store the word in AX or the

Richardson 12 Spring 2006

doubleword in EAX instead of the byte in AL, and increment or decrement the

addressing registers by 2 or 4 instead of 1.

The REP prefix may be used to repeat the instruction ECX times.

subS i/r r/m Subtract Integers

r/m r SUB performs integer subtraction: it subtracts its first operand from its second, and

leaves the result in its destination (second) operand. The flags are set according to the

result of the operation: in particular, the carry flag is affected and can be used by a

subsequent SBB instruction.

testS i/r r/m Test Bits (notional bitwise AND)

TEST performs a “mental” bitwise AND of its two operands, and affects the flags as if

the operation had taken place, but does not store the result of the operation anywhere.

wait Wait for Floating-Point Processor

fwait WAIT, on 8086 systems with a separate 8087 FPU, waits for the FPU to have finished

any operation it is engaged in before continuing main processor operations, so that (for

example) an FPU store to main memory can be guaranteed to have completed before the

CPU tries to read the result back out.

On higher processors, WAIT is unnecessary for this purpose, and it has the alternative

purpose of ensuring that any pending unmasked FPU exceptions have happened before

execution continues.

xaddS r r/m Exchange and Add

XADD exchanges the values in its two operands, and then adds them together and

writes the result into the destination (second) operand. This instruction can be used with

a LOCK prefix for multi−processor synchronisation purposes.

xchgS r/m r Exchange

r r/m XCHG exchanges the values in its two operands. It can be used with a LOCK prefix for

purposes of multi−processor synchronisation.

xlat Translate Byte in Lookup Table

xlatb XLATB adds the value in AL, treated as an unsigned byte, to EBX, and loads the byte

from the resulting address back into AL.

xorS i/r r/m Bitwise Exclusive OR

r/m r XOR performs a bitwise XOR operation between its two operands (i.e. each bit of the

result is 1 if and only if exactly one of the corresponding bits of the two inputs was 1),

and stores the result in the destination (second) operand.

Richardson 13 Spring 2006

You might also like

- ASM Irvine 32 Cheat Sheet (P1)Document43 pagesASM Irvine 32 Cheat Sheet (P1)Zain Arshad SandhuNo ratings yet

- Emu8086 FactorialDocument4 pagesEmu8086 Factorialritik agarwalNo ratings yet

- Operation Security Handbook 1 0Document12 pagesOperation Security Handbook 1 0finiNo ratings yet

- Instruction Set of 8086Document47 pagesInstruction Set of 8086api-249964743No ratings yet

- Instruction Set of 8086Document45 pagesInstruction Set of 8086M Duraipandian MariappanNo ratings yet

- ASM REG, FLAGS, INSTRUCTIONSDocument7 pagesASM REG, FLAGS, INSTRUCTIONSCalvin Ohsey100% (1)

- The Netwide AssemblerDocument21 pagesThe Netwide AssemblerAdarshNo ratings yet

- PS1Document20 pagesPS1Jerome Salazar CaballeroNo ratings yet

- Computer Architecture LabDocument23 pagesComputer Architecture LabHaji ZubairNo ratings yet

- Instruction Set - 8086Document47 pagesInstruction Set - 8086Narsimha PuttaNo ratings yet

- Variables, Arrays and Constants Variables: Name DB Value Name DW ValueDocument9 pagesVariables, Arrays and Constants Variables: Name DB Value Name DW ValuekumarklNo ratings yet

- Chapter 8 - Code GenerationDocument62 pagesChapter 8 - Code GenerationEkansh GuptaNo ratings yet

- Engleza Chap 2 x86 ArchDocument13 pagesEngleza Chap 2 x86 ArchPopulară SălajNo ratings yet

- Compiler Design - Code GenerationDocument62 pagesCompiler Design - Code Generationshanthi prabhaNo ratings yet

- Module - 2 ES - NotesDocument32 pagesModule - 2 ES - Noteslaxmipriya bishoiNo ratings yet

- Sharc ProcessorDocument97 pagesSharc ProcessorTina PrakashNo ratings yet

- CSC3201 - Compiler Construction (Part II) - Lecture 5 - Code GenerationDocument64 pagesCSC3201 - Compiler Construction (Part II) - Lecture 5 - Code GenerationAhmad AbbaNo ratings yet

- Assembler Syntax: Lui $at, 4096 Addu $at, $at, $a1 LW $a0, 8 ($at)Document35 pagesAssembler Syntax: Lui $at, 4096 Addu $at, $at, $a1 LW $a0, 8 ($at)GonzaloDominguezNo ratings yet

- Instruction Set of 8086Document53 pagesInstruction Set of 8086ddeepak82956No ratings yet

- Tugas Konsep Teknologi InformasiDocument7 pagesTugas Konsep Teknologi InformasiNadila AulyaNo ratings yet

- Assemply 2Document6 pagesAssemply 2Ahmed RamadanNo ratings yet

- Arm Cortex MicroprocessorDocument35 pagesArm Cortex MicroprocessorIrrfanNo ratings yet

- Set de Instrucciones DLXDocument2 pagesSet de Instrucciones DLXe1s1v09092023No ratings yet

- LECTURE 2 - MP Architecture - 290220 PDFDocument31 pagesLECTURE 2 - MP Architecture - 290220 PDFFiqa AidaNo ratings yet

- 8086 Instruction SetDocument22 pages8086 Instruction SetlekaNo ratings yet

- Chapter 3.2 Arthemetic and Logic Instruction Instruction SetDocument35 pagesChapter 3.2 Arthemetic and Logic Instruction Instruction SetsagniNo ratings yet

- MIPS ReferenceDocument12 pagesMIPS ReferenceVikash JoshiNo ratings yet

- Assembly - PrereadingDocument60 pagesAssembly - Prereadingbewago9943No ratings yet

- Instruction Set of 8086Document47 pagesInstruction Set of 8086lalit121100% (1)

- 8086 Register Organization (IMPDocument6 pages8086 Register Organization (IMPSukanti PalNo ratings yet

- Register File: ARM Programmer's ModelDocument6 pagesRegister File: ARM Programmer's ModelRajdeep SiddhapuraNo ratings yet

- ARM Architecture: Logical InstructionDocument4 pagesARM Architecture: Logical InstructionNinda KhoirunnisaNo ratings yet

- MP Module 2 - Modified - CorrectDocument24 pagesMP Module 2 - Modified - Correctakhil krishnanNo ratings yet

- Comparing Registers: MIPS vs. ARM AssemblyDocument12 pagesComparing Registers: MIPS vs. ARM Assemblyshruti chouhanNo ratings yet

- Arithmetic and Logical InstructionsDocument4 pagesArithmetic and Logical InstructionsJonalyn MercadoNo ratings yet

- ARM Instruction SetDocument29 pagesARM Instruction SetNeeshank MahajanNo ratings yet

- 8086 Microprocessor Instruction SetDocument175 pages8086 Microprocessor Instruction SetRohtash SethiNo ratings yet

- Microprocessor Design: Simple As Possible-2Document36 pagesMicroprocessor Design: Simple As Possible-2Pantino JoshuaNo ratings yet

- Standard Assembler Program FormatThis provides a concise title for the document within 40 characters by describing the key topic of the standard format of a assembler programDocument23 pagesStandard Assembler Program FormatThis provides a concise title for the document within 40 characters by describing the key topic of the standard format of a assembler programvijaykannamallaNo ratings yet

- Guide To x86 AssemblyDocument13 pagesGuide To x86 AssemblydonifiedNo ratings yet

- Instruction SetDocument69 pagesInstruction SetISHU KUMARNo ratings yet

- Phu Luc - Cac Lenh Assembly Cua CPU NIOS IIDocument19 pagesPhu Luc - Cac Lenh Assembly Cua CPU NIOS IIThành TâmNo ratings yet

- Lab 4Document10 pagesLab 4DavidNo ratings yet

- Instruction Set of 8086Document47 pagesInstruction Set of 8086Mohammed Dyhia AliNo ratings yet

- Asm 6809Document8 pagesAsm 6809karl framptonNo ratings yet

- Opcodes 80537Document57 pagesOpcodes 80537Sebas EuNo ratings yet

- Addressing Mode General Meaning: RegisterDocument27 pagesAddressing Mode General Meaning: RegisterkNo ratings yet

- 3 Instruction SetDocument72 pages3 Instruction SetKernel PultNo ratings yet

- The Intel 8088 Architecture and Instruction SetDocument4 pagesThe Intel 8088 Architecture and Instruction SetSaad AliNo ratings yet

- DATA TRANSFER AND ARITHMETIC INSTRUCTIONSDocument8 pagesDATA TRANSFER AND ARITHMETIC INSTRUCTIONSKhenrick PagelaNo ratings yet

- Assembly Lab 2Document9 pagesAssembly Lab 2Jefferson Medinaceli Malayao100% (1)

- Chapter 2 PDFDocument18 pagesChapter 2 PDFKrishna ChaitanyaNo ratings yet

- Instruction SetDocument104 pagesInstruction SetKrishnaveni DhulipalaNo ratings yet

- 2.1 2.2 8086 Addressing Modes and Instruction SetDocument55 pages2.1 2.2 8086 Addressing Modes and Instruction SetRBTNo ratings yet

- لاب 3.1 +3.2 1Document12 pagesلاب 3.1 +3.2 1vip14No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Shattersecrets spw18Document6 pagesShattersecrets spw18finiNo ratings yet

- Arm CmdrefDocument1 pageArm CmdrefMichaelNo ratings yet

- Vxworks BSP Developers Guide 6.0Document189 pagesVxworks BSP Developers Guide 6.0finiNo ratings yet

- Explaining Cellebrite UFED Data Extraction Processes Final PDFDocument15 pagesExplaining Cellebrite UFED Data Extraction Processes Final PDFenrique ramosNo ratings yet

- Floppy 99Document52 pagesFloppy 99finiNo ratings yet

- Review of assembly language conceptsDocument27 pagesReview of assembly language concepts0esmon0No ratings yet

- Code Generation Issues: Compilation 2014Document19 pagesCode Generation Issues: Compilation 2014finiNo ratings yet

- Apple - Clean Energy and Recycled Products.Document15 pagesApple - Clean Energy and Recycled Products.Sumanyu AgrawalNo ratings yet

- Brief Operating Instructions Vacuum Switch VS-V-D-PNP: 1 DisplayDocument2 pagesBrief Operating Instructions Vacuum Switch VS-V-D-PNP: 1 DisplayJavier MiramontesNo ratings yet

- CC Unit4Document8 pagesCC Unit4Harsh RajputNo ratings yet

- PrePoMax-v1 3 3-ManualDocument43 pagesPrePoMax-v1 3 3-ManualMarcelo ResendeNo ratings yet

- Introduction To Companies - Flipkart and Meesho FlipkartDocument5 pagesIntroduction To Companies - Flipkart and Meesho FlipkartARNAV MISRANo ratings yet

- LEAP-1A - A3 - Modular Design - Rev1.3Document1 pageLEAP-1A - A3 - Modular Design - Rev1.3zeyadNo ratings yet

- Datasheet - HK Pcf7991at 450658Document1 pageDatasheet - HK Pcf7991at 450658Adrian FernandezNo ratings yet

- Release Mode Bundle ErrorDocument11 pagesRelease Mode Bundle ErrorRaman deepNo ratings yet

- Five Traits of Technical WriitngDocument18 pagesFive Traits of Technical WriitngNINETTE TORRESNo ratings yet

- Engg-Exam-December-2022-Odd (Main) - WDDocument35 pagesEngg-Exam-December-2022-Odd (Main) - WDNITEESH YANDRAPUDINo ratings yet

- Python Notes - 1Document364 pagesPython Notes - 1hopefulantonelliNo ratings yet

- B2B Streamlined Bill Sample - Phone Bill Template FormDocument9 pagesB2B Streamlined Bill Sample - Phone Bill Template FormBrendon DrewNo ratings yet

- 4 Special Fire Hazards and PreventionDocument22 pages4 Special Fire Hazards and Preventiondroffilcz27100% (1)

- AVIC-Z150BH, X950BH, X850BT Firmware Update InstructionsDocument4 pagesAVIC-Z150BH, X950BH, X850BT Firmware Update InstructionsEnlight Lab AlbaniaNo ratings yet

- KDS 330 Built for Today, Ready for TomorrowDocument2 pagesKDS 330 Built for Today, Ready for TomorrowBill GetsNo ratings yet

- ESBWR Natural Circulation Fact SheetDocument1 pageESBWR Natural Circulation Fact SheetmanuvildaNo ratings yet

- WS2032D3Document4 pagesWS2032D3Luis David Méndez MirandaNo ratings yet

- Clean CraftsmanshipDocument52 pagesClean CraftsmanshipMartin FernezNo ratings yet

- Proffessional Security Installer - January 2024Document54 pagesProffessional Security Installer - January 2024clubeautomovelviseuNo ratings yet

- GIGABYTE GA-H81M-DS2 Mainboard ManualDocument32 pagesGIGABYTE GA-H81M-DS2 Mainboard Manualcr33pz1llaNo ratings yet

- Raw Mill Vertical Roller Mill PDFDocument58 pagesRaw Mill Vertical Roller Mill PDFganong itbNo ratings yet

- Smartphone IndustryDocument5 pagesSmartphone IndustryChief MaxNo ratings yet

- 2106 Industry Placement Briefing - StudentDocument29 pages2106 Industry Placement Briefing - StudentArsalan JahaniNo ratings yet

- Globalization's growing webDocument3 pagesGlobalization's growing webVince Allen B. FerancoNo ratings yet

- Foxit Reader Quick Start GuideDocument41 pagesFoxit Reader Quick Start GuideMedina BekticNo ratings yet

- Unidrive M200: Integration Through Flexible CommunicationsDocument16 pagesUnidrive M200: Integration Through Flexible CommunicationsValery CarranzaNo ratings yet

- Data Processing Addendum SummaryDocument20 pagesData Processing Addendum SummaryJacimar JuniorNo ratings yet

- Yealink Hybrid-mode Feature Compatible with AudioCodes SBC V15.3Document13 pagesYealink Hybrid-mode Feature Compatible with AudioCodes SBC V15.3jtzondoNo ratings yet

- Industrial Metal Detector: Operator ManualDocument40 pagesIndustrial Metal Detector: Operator ManualINMETRO SACNo ratings yet

- Seeed Can Bus v2Document20 pagesSeeed Can Bus v2Geo AdmNo ratings yet