Professional Documents

Culture Documents

Enhanced ARINC 429 3.3V Serial Transmitter and Dual Receiver

Uploaded by

nmgopiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Enhanced ARINC 429 3.3V Serial Transmitter and Dual Receiver

Uploaded by

nmgopiCopyright:

Available Formats

HI-3584

Enhanced ARINC 429

December 2014 3.3V Serial Transmitter and Dual Receiver

GENERAL DESCRIPTION APPLICATIONS

The HI-3584 from Holt Integrated Circuits is a silicon gate ! Avionics data communication

CMOS device for interfacing a 16-bit parallel data bus to the

ARINC 429 serial bus. The HI-3584 design offers many ! Serial to parallel conversion

enhancements to the industry standard HI-8282 ! Parallel to serial conversion

architecture. The device provides two receivers each with

label recognition, a 32 by 32 FIFO, and an analog line

receiver. Up to 16 labels may be programmed for each PIN CONFIGURATIONS (Top View)

receiver. The independent transmitter also has a 32 by 32 (See page 13 for additional pin configuration)

FIFO. The status of all three FIFOs can be monitored using See Note below

the external status pins or by polling the HI-3584’s status

52 - TXCLK

60 - RIN1A

63 - RIN2B

62 - RIN2A

61 - RIN1B

50 - RSR

58 - VDD

57 - VDD

56 - VDD

51 - CLK

49 - N/C

55 - N/C

54 - N/C

59 - N/C

64 - N/C

53 - MR

register.

Other new features include a programmable option of data N/C - 1 48 - CWSTR

D/R1 - 2

or parity in the 32nd bit, and the ability to unscramble the 32 FF1 - 3

47 - ENTX

46 - 429DO

HF1 - 4 45 - N/C

bit word. Also, versions are available with different values D/R2 - 5 44 - N/C

FF2 - 6 43 - N/C

of input resistance to allow users to more easily add HF2 - 7 HI-3584PCI 42 - N/C

SEL - 8 41 - 429DO

external lightning protection circuitry. EN1 - 9 & 40 - FFT

EN2 - 10 39 - HFT

N/C - 11

BD15 - 12

HI-3584PCT 38 - TX/R

37 - PL2

The 16-bit parallel data bus exchanges the 32-bit ARINC BD14 - 13 36 - PL1

BD13 - 14 35 - BD00

data word in two steps when either loading the transmitter BD12 - 15

BD11 - 16

34 - BD01

33 - N/C

or interrogating the receivers. The databus and all control

N/C - 32

BD02 - 31

BD05 - 28

BD04 - 29

BD03 - 30

N/C - 25

N/C - 26

N/C - 27

BD06 - 22

GND - 23

N/C - 24

BD09 - 19

BD08 - 20

BD07 - 21

N/C - 17

BD10 - 18

signals are CMOS and TTL compatible.

The HI-3584 applies the ARINC protocol to the receivers (Note: All 3 VDD pins must be connected to the same 3.3V supply)

and transmitter. Timing is based on a 1 Megahertz clock.

64 - Pin Plastic 9mm x 9mm

Additional interface circuitry such as the Holt HI-8585 or Chip-Scale Package

HI-8586 is required to translate the transmitter’s 3.3 volt

logic outputs to ARINC 429 drive levels.

43 - TXCLK

48 - RIN1A

49 - RIN1B

50 - RIN2A

51 - RIN2B

52 - D/R1

41 - RSR

47 - VDD

42 - CLK

40 - N/C

45 - N/C

46 - N/C

44 - MR

FEATURES

! ARINC specification 429 compatible

! 3.3V logic supply operation

FF1 - 1 39 - N/C

! Dual receiver and transmitter interface HF1 - 2 38 - CWSTR

D/R2 - 3 37 - ENTX

! Analog line receivers connect directly to ARINC bus FF2 - 4 36 - N/C

! Programmable label recognition

HF2 - 5 HI-3584PQI 35 - 429DO

SEL - 6 34 - 429DO

&

! On-chip 16 label memory for each receiver EN1 - 7

EN2 - 8 HI-3584PQT

33 - N/C

32 - FFT

! 32 x 32 FIFOs each receiver and transmitter BD15 - 9 31 - HFT

BD14 - 10 30 - TX/R

! Independent data rate selection for transmitter BD13 - 11 29 - PL2

BD12 - 12 28 - PL1

and each receiver BD11 - 13 27 - BD00

! Status register

! Data scramble control

BD01 - 26

BD02 - 25

BD03 - 24

BD04 - 23

BD05 - 22

N/C - 21

GND - 20

N/C - 19

BD06 - 18

BD07 - 17

BD08 - 16

BD09 - 15

BD10 - 14

! 32nd transmit bit can be data or parity

! Self test mode

! Low power

! Industrial & full military temperature ranges 52 - Pin Plastic Quad Flat Pack (PQFP)

HOLT INTEGRATED CIRCUITS

((DS3584 Rev. H) www.holtic.com 12 /14

HI-3584

PIN DESCRIPTIONS

SIGNAL FUNCTION DESCRIPTION

VDD POWER +3.3V ±5% (All three VDD pins on the chip-scale package must be connect to the same supply)

RIN1A INPUT ARINC receiver 1 positive input

RIN1B INPUT ARINC receiver 1 negative input

RIN2A INPUT ARINC receiver 2 positive input

RIN2B INPUT ARINC receiver 2 negative input

D/R1 OUTPUT Receiver 1 data ready flag

FF1 OUTPUT FIFO full Receiver 1

HF1 OUTPUT FIFO Half full, Receiver 1

D/R2 OUTPUT Receiver 2 data ready flag

FF2 OUTPUT FIFO full Receiver 2

HF2 OUTPUT FIFO Half full, Receiver 2

SEL INPUT Receiver data byte selection (0 = BYTE 1) (1 = BYTE 2)

EN1 INPUT Data Bus control, enables receiver 1 data to outputs

EN2 INPUT Data Bus control, enables receiver 2 data to outputs if EN1 is high

BD15 I/O Data Bus

BD14 I/O Data Bus

BD13 I/O Data Bus

BD12 I/O Data Bus

BD11 I/O Data Bus

BD10 I/O Data Bus

BD09 I/O Data Bus

BD08 I/O Data Bus

BD07 I/O Data Bus

BD06 I/O Data Bus

GND POWER 0V

BD05 I/O Data Bus

BD04 I/O Data Bus

BD03 I/O Data Bus

BD02 I/O Data Bus

BD01 I/O Data Bus

BD00 I/O Data Bus

PL1 INPUT Latch enable for byte 1 entered from data bus to transmitter FIFO.

PL2 INPUT Latch enable for byte 2 entered from data bus to transmitter FIFO. Must follow PL1.

TX/R OUTPUT Transmitter ready flag. Goes low when ARINC word loaded into FIFO. Goes high after

transmission and FIFO empty.

HFT OUTPUT Transmitter FIFO Half Full

FFT OUTPUT Transmitter FIFO Full

429DO OUTPUT “ONES” data output from transmitter

429DO OUTPUT “ZEROS” data output from transmitter

ENTX INPUT Enable Transmission

CWSTR INPUT Clock for control word register

RSR INPUT Read Status Register if SEL=0, read Control Register if SEL=1

CLK INPUT Master Clock input

TX CLK OUTPUT Transmitter Clock equal to Master Clock (CLK), divided by either 10 or 80.

MR INPUT Master Reset, active low

HOLT INTEGRATED CIRCUITS

2

HI-3584

FUNCTIONAL DESCRIPTION

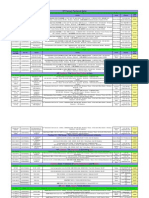

CONTROL WORD REGISTER STATUS REGISTER

The HI-3584 contains a 16-bit control register which is used to con- The HI-3584 contains a 9-bit status register which can be interro-

figure the device. The control register bits CR0 - CR15 are loaded gated to determine the status of the ARINC receivers, data FIFOs

from BD00 - BD15 when CWSTR is pulsed low. The control regis- and transmitter. The contents of the status register are output on

ter contents are output on the databus when SEL = 1 and RSR is BD00 - BD08 when the RSR pin is taken low and SEL = 0. Unused

pulsed low. Each bit of the control register has the following func- bits are output as zeros. The following table defines the status reg-

tion: ister bits.

CR SR

Bit FUNCTION STATE DESCRIPTION Bit FUNCTION STATE DESCRIPTION

CR0 Receiver 1 0 Data rate = CLK/10 SR0 Data ready 0 Receiver 1 FIFO empty

Data clock (Receiver 1)

Select 1 Data rate = CLK/80 1 Receiver 1 FIFO contains valid data

Resets to zero when all data has

CR1 Label Memory 0 Normal operation been read. D/R1 pin is the inverse of

Read / Write this bit

1 Load 16 labels using PL1 / PL2

Read 16 labels using EN1 / EN2 SR1 FIFO half full 0 Receiver 1 FIFO holds less than 16

(Receiver 1) words

CR2 Enable Label 0 Disable label recognition

Recognition 1 Receiver 1 FIFO holds at least 16

(Receiver 1) 1 Enable label recognition words. HF1 pin is the inverse of

this bit.

CR3 Enable Label 0 Disable Label Recognition

Recognition SR2 FIFO full 0 Receiver 1 FIFO not full

(Receiver 2) 1 Enable Label recognition (Receiver 1)

1 Receiver 1 FIFO full. To avoid data

CR4 Enable 0 Transmitter 32nd bit is data loss, the FIFO must be read within

32nd bit one ARINC word period. FF1 pin is

as parity 1 Transmitter 32nd bit is parity the inverse of this bit

CR5 Self Test 0 The 429DO and 429DO digital SR3 Data ready 0 Receiver 2 FIFO empty

outputs are internally connected (Receiver 2)

to the receiver logic inputs 1 Receiver 2 FIFO contains valid data

Resets to zero when all data has

1 Normal operation been read. D/R2 pin is the inverse of

this bit

CR6 Receiver 1 0 Receiver 1 decoder disabled

decoder SR4 FIFO half full 0 Receiver 2 FIFO holds less than 16

1 ARINC bits 9 and 10 must match (Receiver 2) words

CR7 and CR8

1 Receiver 2 FIFO holds at least 16

CR7 - - If receiver 1 decoder is enabled, words. HF2 pin is the inverse of

the ARINC bit 9 must match this bit this bit.

CR8 - - If receiver 1 decoder is enabled, SR5 FIFO full 0 Receiver 2 FIFO not full

the ARINC bit 10 must match this bit (Receiver 2)

1 Receiver 2 FIFO full. To avoid data

CR9 Receiver 2 0 Receiver 2 decoder disabled loss, the FIFO must be read within

Decoder one ARINC word period. FF2 pin is

1 ARINC bits 9 and 10 must match the inverse of this bit

CR10 and CR11

SR6 Transmitter FIFO 0 Transmitter FIFO not empty

CR10 - - If receiver 2 decoder is enabled, empty

the ARINC bit 9 must match this bit 1 Transmitter FIFO empty.

CR11 - - If receiver 2 decoder is enabled, SR7 Transmitter FIFO 0 Transmitter FIFO not full

the ARINC bit 10 must match this bit full

1 Transmitter FIFO full. FFT pin is the

CR12 Invert 0 Transmitter 32nd bit is Odd parity inverse of this bit.

Transmitter

parity 1 Transmitter 32nd bit is Even parity SR8 Transmitter FIFO 0 Transmitter FIFO contains less than

half full 16 words

CR13 Transmitter 0 Data rate=CLK/10, O/P slope=1.5us

data clock 1 Transmitter FIFO contains at least

select 1 Data rate=CLK/80, O/P slope=10us 16 words.HFT pin is the

inverse of this bit.

CR14 Receiver 2 0 Data rate=CLK/10

data clock

select 1 Data rate=CLK/80

CR15 Data 0 Scramble ARINC data

format

1 Unscramble ARINC data

HOLT INTEGRATED CIRCUITS

3

HI-3584

FUNCTIONAL DESCRIPTION (cont.)

The HI-3584 guarantees recognition of these levels with a common

ARINC 429 DATA FORMAT mode Voltage with respect to GND less than ±4V for the worst case

condition (3.0V supply and 13V signal level).

Control register bit CR15 is used to control how individual bits in the

received or transmitted ARINC word are mapped to the HI-3584 The tolerances in the design guarantee detection of the above

data bus during data read or write operations. The following table levels, so the actual acceptance ranges are slightly larger. If the

describes this mapping: ARINC signal is out of the actual acceptance ranges, including the

nulls, the chip rejects the data.

BYTE 1

DATA BD BD BD BD BD BD BD BD BD BD BD BD BD BD BD BD RECEIVER LOGIC OPERATION

BUS 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

ARINC 13 12 11 10 9 31 30 32 1 2 3 4 5 6 7 8 Figure 2 shows a block diagram of the logic section of each receiver.

Parity

BIT

Label

Label

Label

Label

Label

Label

Label

Label

SDI

SDI

CR15=0 BIT TIMING

ARINC 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 The ARINC 429 specification contains the following timing specifi-

BIT cation for the received data:

Label

Label

Label

Label

Label

Label

Label

Label

SDI

SDI

CR15=1

HIGH SPEED LOW SPEED

BYTE 2 BIT RATE 100K BPS ± 1% 12K -14.5K BPS

PULSE RISE TIME 1.5 ± 0.5 µsec 10 ± 5 µsec

DATA BD BD BD BD BD BD BD BD BD BD BD BD BD BD BD BD PULSE FALL TIME 1.5 ± 0.5 µsec 10 ± 5 µsec

BUS 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 PULSE WIDTH 5 µsec ± 5% 34.5 to 41.7 µsec

ARINC 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14

BIT The HI-3584 accepts signals that meet these specifications and re-

CR15=0 jects signals outside the tolerances. The way the logic operation

achieves this is described below:

ARINC 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17

Parity

BIT

CR15=1 1. Key to the performance of the timing checking logic is an ac-

curate 1MHz clock source. Less than 0.1% error is recom-

mended.

THE RECEIVERS

2. The sampling shift registers are 10 bits long and must show

ARINC BUS INTERFACE three consecutive Ones, Zeros or Nulls to be considered valid

data. Additionally, for data bits, the One or Zero in the upper

Figure 1 shows the input circuit for each receiver. The ARINC 429 bits of the sampling shift registers must be followed by a Null in

specification requires the following detection levels: the lower bits within the data bit time. For a Null in the word gap,

three consecutive Nulls must be found in both the upper and

lower bits of the sampling shift register. In this manner the mini-

STATE DIFFERENTIAL VOLTAGE mum pulse width is guaranteed.

ONE +6.5 Volts to +13 Volts

NULL +2.5 Volts to -2.5 Volts 3. Each data bit must follow its predecessor by not less than 8

ZERO -6.5 Volts to -13 Volts samples and no more than 12 samples. In this manner the bit

rate is checked. With exactly 1MHz input clock frequency, the

acceptable data bit rates are as follows:

HIGH SPEED LOW SPEED

VDD DIFFERENTIAL

AMPLIFIERS

COMPARATORS

DATA BIT RATE MIN 83K BPS 10.4K BPS

RIN1A

ONES DATA BIT RATE MAX 125K BPS 15.6K BPS

OR

RIN2A

4. The Word Gap timer samples the Null shift register every 10

GND NULL input clocks (80 for low speed) after the last data bit of a valid

VDD reception. If the Null is present, the Word Gap counter is

ZEROES

incremented. A count of 3 will enable the next reception.

RIN1B

OR

RIN2B

GND

FIGURE 1. ARINC RECEIVER INPUT

HOLT INTEGRATED CIRCUITS

4

HI-3584

FUNCTIONAL DESCRIPTION (cont.)

RECEIVER PARITY RETRIEVING DATA

The 32nd bit of received ARINC words stored in the receive FIFO Once 32 valid bits are recognized, the receiver logic generates an

is used as a Parity Flag indicating whether good Odd parity is End of Sequence (EOS). Depending upon the state of control

received from the incoming ARINC word. register bits CR2-CR11, the received ARINC 32-bit word is then

checked for correct decoding and label matching before being

Odd Parity Received loaded into the 32 x 32 receive FIFO. ARINC words which do not

The parity bit is reset to indicate correct parity was received meet the necessary 9th and 10th ARINC bit or label matching are

and the resulting word is written to the receive FIFO. ignored and are not loaded into the receive FIFO. The following

table describes this operation.

Even Parity Received

The receiver sets the 32nd bit to a “1”, indicating a parity error

and the resulting word is then written to the receive FIFO. CR2(3) ARINC word CR6(9) ARINC word FIFO

matches bits 9,10

Therefore, the 32nd bit retrieved from the receiver FIFO will always label match

be “0” when valid (odd parity) ARINC 429 words are received. CR7,8 (10,11)

0 X 0 X Load FIFO

1 No 0 X Ignore data

1 Yes 0 X Load FIFO

0 X 1 No Ignore data

0 X 1 Yes Load FIFO

1 Yes 1 No Ignore data

1 No 1 Yes Ignore data

1 No 1 No Ignore data

1 Yes 1 Yes Load FIFO

HOLT INTEGRATED CIRCUITS

5

HI-3584

FUNCTIONAL DESCRIPTION (cont.)

TO PINS

SEL MUX CONTROL

32 TO 16 DRIVER R/W

CONTROL CONTROL BITS

EN

HF

FF

D/R

32 X 32

FIFO

LOAD FIFO

CONTROL

CONTROL

BIT / LABEL /

DECODE

COMPARE CONTROLBITS CLOCK

CLK

CR0, CR14 OPTION

CLOCK

16 x 8

LABEL BIT

MEMORY COUNTER

32ND AND

DATA PARITY BIT END OF

32 BIT SHIFT REGISTER CHECK SEQUENCE

BIT CLOCK

EOS

WORD GAP

WORD GAP TIMER

ONES SHIFT REGISTER

BIT CLOCK

START END

NULL SEQUENCE

SHIFT REGISTER CONTROL

ZEROS SHIFT REGISTER ERROR

ERROR

DETECTION CLOCK

FIGURE 2. RECEIVER BLOCK DIAGRAM

HOLT INTEGRATED CIRCUITS

6

HI-3584

FUNCTIONAL DESCRIPTION (cont.)

Once a valid ARINC word is loaded into the FIFO, then EOS READING LABELS

clocks the data ready flag flip flop to a "1", D/R1 or D/R2 (or both)

will go low. The data flag for a receiver will remain low until both After the write that changes CR1 from 0 to 1, the next 16 data

ARINC bytes from that receiver are retrieved and the FIFO is reads of the selected receiver (EN taken low) are labels. EN1 is

empty. This is accomplished by first activating EN with SEL, the used to read labels for receiver 1, and EN2 to read labels for

byte selector, low to retrieve the first byte and then activating EN receiver 2. Label data is presented on BD00 - BD07.

with SEL high to retrieve the second byte. EN1 retrieves data

from receiver 1 and EN2 retrieves data from receiver 2. When writing to, or reading from the label memory, SEL must be a

one, all 16 locations should be accessed, and CR1 must be

Up to 32 ARINC words may be loaded into each receiver’s FIFO. written to zero before returning to normal operation. Label

The FF1 (FF2) pin will go low when the receiver 1 (2) FIFO is full. recognition must be disabled (CR2/3=0) during the label read

Failure to retrieve data from a full FIFO will cause the next valid sequence.

ARINC word received to overwrite the existing data in FIFO

location 32. A FIFO half full flag HF1 (HF2) goes low if the FIFO

contains 16 or more received ARINC words. The HF1 (HF2) pin is TRANSMITTER

intended to act as an interrupt flag to the system’s external

microprocessor, allowing a 16 word data retrieval routine to be FIFO OPERATION

performed, without the user needing to continually poll the HI-

3584’s status register bits. The FIFO is loaded sequentially by first pulsing PL1 to load byte 1

and then PL2 to load byte 2. The control logic automatically loads

LABEL RECOGNITION the 31 bit word (or 32 bit word if CR4=0) in the next available

position of the FIFO. If TX/R, the transmitter ready flag is high

The chip compares the incoming label to the stored labels if label (FIFO empty), then up to 32 words, each 31 or 32 bits long, may

recognition is enabled. If a match is found, the data is processed. be loaded. If TX/R is low, then only the available positions may be

If a match is not found, no indicators of receiving ARINC data are loaded. If all 32 positions are full, the FFT flag is asserted and the

presented. Note that 00(Hex) is treated in the same way as any FIFO ignores further attempts to load data.

other label value. Label bit significance is not changed by the

status of control register bit CR15. Label bits BD00-BD07 are A transmitter FIFO half-full flag HFT is provided. When the

always compared to received ARINC bits 1 -8 respectively. transmit FIFO contains less than 16 words, HFT is high,

indicating to the system microprocessor that a 16 ARINC word

LOADING LABELS block write sequence can be initiated.

After a write that takes CR1 from 0 to 1, the next 16 writes of data In normal operation (CR4=1), the 32nd bit transmitted is a parity

(PL pulsed low) load label data into each location of the label bit. Odd or even parity is selected by programming control

memory from the BD00 - BD07 pins. The PL1 pin is used to write register bit CR12 to a zero or one. If CR4 is programmed to a 0,

label data for receiver 1 and PL2 for receiver 2. Note that ARINC then all 32-bits of data loaded into the transmitter FIFO are

word reception is suspended during the label memory write treated as data and are transmitted.

sequence.

CR4,12

BIT CLOCK DATA AND 429DO

32 BIT PARALLEL PARITY NULL TIMER

LOAD SHIFT REGISTER GENERATOR SEQUENCER 429DO

BIT

AND

WORD CLOCK WORD GAP

COUNTER

START

SEQUENCE

32 x 32 FIFO ADDRESS TX/R

WORD COUNTER HFT

AND

LOAD FIFO CONTROL FFT

ENTX

INCREMENT

WORD COUNT

FIFO PL1

LOADING

SEQUENCER PL2

DATA BUS

DATA

CLOCK DATA CLOCK CLK

CR13 DIVIDER TX CLK

FIGURE 3. TRANSMITTER BLOCK DIAGRAM

HOLT INTEGRATED CIRCUITS

7

HI-3584

FUNCTIONAL DESCRIPTION (cont.)

DATA TRANSMISSION

REPEATER OPERATION

When ENTX goes high, enabling transmission, the FIFO

positions are incremented with the top register loading into the Repeater mode of operation allows a data word that has been

data transmission shift register. Within 2.5 data clocks the first received by the HI-3584 to be placed directly into the transmitter

data bit appears at 429DO and 429DO. The 31 or 32 bits in the FIFO. Repeater operation is similar to normal receiver operation.

data transmission shift register are presented sequentially to the In normal operation, either byte of a received data word may be

outputs in the ARINC 429 format with the following timing: read from the receiver latches first by use of SEL input. During

repeater operation however, the lower byte of the data word must

be read first. This is necessary because, as the data is being

HIGH SPEED LOW SPEED read, it is also being loaded into transmitter FIFO which is always

ARINC DATA BIT TIME 10 Clocks 80 Clocks loaded with the lower byte of the data word first. Signal flow for

DATA BIT TIME 5 Clocks 40 Clocks repeater operation is shown in the Timing Diagrams section.

NULL BIT TIME 5 Clocks 40 Clocks

WORD GAP TIME 40 Clocks 320 Clocks HI-3584-10

The word counter detects when all loaded positions have been The HI-3584-10 option is similar to the HI-3584 with the exception

transmitted and sets the transmitter ready flag, TX/R, high. that it allows an external 10 Kohm resistor to be added in series

with each ARINC input without affecting the ARINC input thresh-

olds. This option is especially useful in applications where light-

TRANSMITTER PARITY ning protection circuitry is also required.

The parity generator counts the Ones in the 31-bit word. If Each side of the ARINC bus must be connected through a 10

control register bit CR12 is set low, the 32nd bit transmitted will Kohm series resistor in order for the chip to detect the correct

make parity odd. If the control bit is, high the parity is even. ARINC levels. The typical 10 volt differential signal is translated

Setting CR4 to a Zero bypasses the parity generator, and allows and input to a window comparator and latch. The comparator

32 bits of data to be transmitted. levels are set so that with the external 10 Kohm resistors, they are

just below the standard 6.5 volt minimum ARINC data threshold

and just above the standard 2.5 volt maximum ARINC null

SELF TEST

threshold.

If control register bit CR5 is set low, the transmitter serial output

Please refer to the Holt AN-300 Application Note for additional

data are internally connected to each of the two receivers,

information and recommendations on lightning protection of Holt

bypassing the analog interface circuitry. Data is passed unmodi-

line drivers and line receivers.

fied to receiver 1 and inverted to receiver 2. The serial data from

the transmitter is always present on the 429DO and 429DO

outputs regardless of the state of CR5. HIGH SPEED OPERATION

The HI-3584 may be operated at clock frequencies beyond that

SYSTEM OPERATION required for ARINC compliant operation. For operation at Master

Clock (CLK) frequencies up to 5MHz, please contact Holt appli-

The two receivers are independent of the transmitter. Therefore,

cations engineering.

control of data exchanges is strictly at the option of the user. The

only restrictions are:

MASTER RESET (MR)

1. The received data will be overwritten if the receiver FIFO

is full and at least one location is not retrieved before the On a Master Reset data transmission and reception are

next complete ARINC word is received. immediately terminated, all three FIFOs are cleared as are the

FIFO flags at the device pins and in the Status Register. The

2. The transmitter FIFO can store 32 words maximum and Control Register is not affected by a Master Reset.

ignores attempts to load additional data if full.

HOLT INTEGRATED CIRCUITS

8

HI-3584

TIMING DIAGRAMS

DATA RATE - EXAMPLE PATTERN

429 DATA

ARINC BIT

429 DATA

DATA NULL DATA NULL DATA NULL

BIT 1

BIT 31 BIT 32 WORD GAP

BIT 30 NEXT WORD

RECEIVER OPERATION

ARINC DATA BIT 31 BIT 32

D/R, HF, FF

tD/R tEND/R

SEL DON'T CARE

tEN

tSELEN tENSEL tSELEN tENSEL tSELEN

EN

tD/REN tENEN tREADEN

tDATAEN tDATAEN

DATA BUS BYTE 1 VALID BYTE 2 VALID BYTE 1

tENDATA tENDATA tENDATA

TRANSMITTER OPERATION

DATA BUS BYTE 1 VALID BYTE 2 VALID

tDWSET tDWSET

tDWHLD tDWHLD

PL1

tPL tPL12

PL2

tPL12 tPL tTX/R

TX/R, HFT, FFT

LOADING CONTROL WORD

DATA BUS VALID

tCWSET tCWHLD

CWSTR

tCWSTR

HOLT INTEGRATED CIRCUITS

9

HI-3584

TIMING DIAGRAMS (cont.)

STATUS REGISTER READ CYCLE

BYTE SELECT SEL DON'T CARE DON'T CARE

tSELEN tENSEL

RSR

tDATAEN

DATA BUS DATA VALID

tENDATA

CONTROL REGISTER READ CYCLE

BYTE SELECT SEL DON'T CARE DON'T CARE

tSELEN tENSEL

RSR

tDATAEN

DATA BUS DATA VALID

tENDATA

LABEL MEMORY LOAD SEQUENCE

tCWSTR

CWSTR

tCWHLD

tCWSET

DATA BUS Set CR1=1 Label #1 Label #2 Label #16 Set CR1=0

tDWSET

tDWHLD

PL1 / PL2

tPL tLABEL

LABEL MEMORY READ SEQUENCE

tCWSTR

CWSTR

tREADEN

EN1 / EN2

tCWHLD

tDATAEN

tCWSET

DATA BUS Set CR1=1 Label #1 Label #2 Label #16 Set CR1=0

tENDATA

HOLT INTEGRATED CIRCUITS

10

HI-3584

TIMING DIAGRAMS (cont.)

TRANSMITTING DATA

PL2

tDTX/R

tPL2EN

TXR

tENTX/R

ENTX

tENDAT

ARINC BIT ARINC BIT ARINC BIT

DATA DATA DATA

BIT 1 BIT 2 BIT 32

429DO

429DO

One Null Zero Null One Null

REPEATER OPERATION TIMING

RIN BIT 32

tEND/R

D/R

tD/R tD/REN tEN tENEN tEN

EN

tSELEN tENSEL

SEL DON'T CARE DON'T CARE

tSELEN

tENPL tPLEN tENSEL

PL1

tENPL tPLEN

PL2

tTX/R

TXR

tTX/REN tENTX/R

ENTX

tENDAT tDTX/R

429DO BIT 1 BIT 32

429DO

tNULL

HOLT INTEGRATED CIRCUITS

11

HI-3584

ABSOLUTE MAXIMUM RATINGS

Supply Voltages VDD ........................................... -0.3V to +4V Power Dissipation at 25°C .......................................... 500 mW

Voltage at pins RIN1A, RIN1B, RIN2A, RIN2B ... -120V to +120V DC Current Drain per pin .............................................. ±10mA

Voltage at any other pin ............................... -0.3V to VDD +0.3V Storage Temperature Range ........................ -65°C to +150°C

Solder temperature (Reflow) ............................................. 260°C Operating Temperature Range (Industrial): .... -40°C to +85°C

(Extended): ....-55°C to +125°C

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only.

Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DC ELECTRICAL CHARACTERISTICS

VDD = 3.3V , GND = 0V, TA = Operating Temperature Range (unless otherwise specified).

LIMITS

PARAMETER SYMBOL CONDITIONS UNIT

MIN TYP MAX

ARINC INPUTS - Pins RIN1A, RIN1B, RIN2A, RIN2B

Differential Input Voltage: ONE VIH Common mode voltage 6.5 10.0 13.0 V

(RIN1A to RIN1B, RIN2A to RIN2B) ZERO VIL less than ±4V with -13.0 -10.0 -6.5 V

NULL VNUL with respect to GND -2.5 0 2.5 V

Input Resistance: Differential RI 12 46 KW

To GND RG 12 38 KW

To VDD RH 12 38 KW

Input Current: Input Sink IIH 200 µA

Input Source IIL -450 µA

Input Capacitance: Differential CI (RIN1A to RIN1B, RIN2A to RIN2B) 20 pF

(Guaranteed but not tested) To GND CG 20 pF

To VDD CH 20 pF

BI-DIRECTIONAL INPUTS - Pins BD00 - BD15

Input Voltage: Input Voltage HI VIH 70% V

Input Voltage LO VIL 30% V

Input Current: Input Sink IIH 1.5 µA

Input Source IIL -1.5 µA

OTHER INPUTS

Input Voltage: Input Voltage HI VIH 70% V

Input Voltage LO VIL 30% V

Input Current: Input Sink IIH 1.5 µA

Input Source IIL -1.5 µA

Input Capacitance: CI 15 pF

OUTPUTS

Output Voltage: Logic "1" Output Voltage VOH IOH = -1.0mA VDD - 0.2V V

Logic "0" Output Voltage VOL IOL = 1.6mA 10%VDD V

Output Current: Output Sink IOL VOUT = 0.4V 1.6 mA

(Bi-directional Pins) Output Source IOH VOUT = VDD - 0.4V -1.0 mA

Output Current: Output Sink IOL VOUT = 0.4V 1.6 mA

(All Other Outputs) Output Source IOH VOUT = VDD - 0.4V -1.0 mA

Output Capacitance: CO 15 pF

Operating Supply Current

VDD IDD 4 20 mA

HOLT INTEGRATED CIRCUITS

12

HI-3584

AC ELECTRICAL CHARACTERISTICS

VDD = 3.3V, GND = 0V, TA = Oper. Temp. Range and fclk=1MHz +0.1% with 60/40 duty cycle

LIMITS

PARAMETER SYMBOL UNITS

MIN TYP MAX

CONTROL WORD TIMING

Pulse Width - CWSTR tCWSTR 50 ns

Setup - DATA BUS Valid to CWSTR HIGH tCWSET 100 ns

Hold - CWSTR HIGH to DATA BUS Hi-Z tCWHLD 40 ns

RECEIVER FIFO AND LABEL READ TIMING

Delay - Start ARINC 32nd Bit to D/R LOW: High Speed tD/R 16 µs

Low Speed tD/R 128 µs

Delay - D/R LOW to EN LOW tD/REN 0 ns

Delay - EN HIGH to D/R HIGH tEND/R 420 520 ns

Setup - SEL to EN LOW tSELEN 10 ns

Hold - SEL to EN HIGH tENSEL 10 ns

Delay - EN LOW to DATA BUS Valid tENDATA 180 ns

Delay - EN HIGH to DATA BUS Hi-Z tDATAEN 80 ns

Pulse Width - EN1 or EN2 tEN 60 ns

Spacing - EN HIGH to next EN LOW (Same ARINC Word) tENEN 65 ns

Spacing -EN HIGH to next EN LOW (Next ARINC Word) tREADEN 200 ns

TRANSMITTER FIFO AND LABEL WRITE TIMING

Pulse Width - PL1 or PL2 tPL 120 ns

Setup - DATA BUS Valid to PL HIGH tDWSET 150 ns

Hold - PL HIGH to DATA BUS Hi-Z tDWHLD 70 ns

Spacing - PL1 or PL2 tPL12 110 ns

Spacing between Label Write pulses tLABEL 150 ns

Delay - PL2 HIGH to TX/R LOW tTX/R 240 ns

TRANSMISSION TIMING

Spacing - PL2 HIGH to ENTX HIGH tPL2EN 0 µs

Delay - 32nd ARINC Bit to TX/R HIGH tDTX/R 50 ns

Spacing - TX/R HIGH to ENTX LOW tENTX/R 0 ns

Delay - ENTX HIGH to TXAOUT or TXBOUT: High Speed tENDAT 25 µs

Delay - ENTX HIGH to TXAOUT or TXBOUT: Low Speed tENDAT 200 µs

REPEATER OPERATION TIMING

Delay - EN LOW to PL LOW tENPL 0 ns

Hold - PL HIGH to EN HIGH tPLEN 0 ns

Delay - TX/R LOW to ENTX HIGH tTX/REN 0 ns

MASTER RESET PULSE WIDTH tMR 160 ns

ARINC DATA RATE AND BIT TIMING ± 1%

HOLT INTEGRATED CIRCUITS

13

HI-3584

ADDITIONAL HI-3584 PIN CONFIGURATION

(See page 1 for additional pin configurations)

50 - TXCLK

3 - RIN1A

4 - RIN1B

5 - RIN2A

6 - RIN2B

7 - D/R1

48 - RSR

2 - VDD

49 - CLK

47 - N/C

52 - N/C

1 - N/C

51 - MR

FF1 - 8 46 - N/C

HF1 - 9 45 - CWSTR

D/R2 - 10 44 - ENTX

FF2 - 11 43 - N/C

HF2 - 12 42 - 429DO

SEL - 13

HI-3584CJI

41 - 429DO

EN1 - 14 & 40 - N/C

EN2 - 15 HI-3584CJT 39 - FFT

BD15 - 16 38 - HFT

BD14 - 17 37 - TX/R

BD13 - 18 36 - PL2

BD12 - 19 35 - PL1

BD11 - 20 34 - BD00

BD01 - 33

BD02 - 32

BD03 - 31

BD04 - 30

BD05 - 29

N/C - 28

GND - 27

N/C - 26

BD06 - 25

BD07 - 24

BD08 - 23

BD09 - 22

BD10 - 21

52 - Pin Cerquad J-lead

ORDERING INFORMATION

HI - 3584 xx x x - xx

PART INPUT SERIES RESISTANCE

NUMBER BUILT-IN REQUIRED EXTERNALLY

No dash number 35K Ohm 0

-10 25K Ohm 10K Ohm

PART PACKAGE

NUMBER DESCRIPTION

Blank Tin / Lead (Sn / Pb) Solder

F 100% Matte Tin (Pb-free RoHS compliant)

PART TEMPERATURE BURN

NUMBER RANGE FLOW IN

I -40°C TO +85°C I No

T -55°C TO +125°C T No

PART PACKAGE

NUMBER DESCRIPTION

CJ 52 PIN J-LEAD CERQUAD (52U) not available Pb-free

PC 64 PIN PLASTIC CHIP-SCALE LPCC (64PCS)

PQ 52 PIN PLASTIC QUAD FLAT PACK PQFP (52PQS)

HOLT INTEGRATED CIRCUITS

14

HI-3584

REVISION HISTORY

Revision Date Description of Change

DS3584 Rev. G 04/10/13 Clarified description of receiver parity. Updated PQFP and QFN package

drawings. Fixed truncated text on page 7 of Rev F. (see page 8).

Rev. H 12/4/14 Updated Absolute Maximum Ratings Table (Voltage on pins RIN1A, RIN1B, RIN2A,

RIN2B changed from +/-29V to +/-120V; Clarified solder reflow temperature).

Update 52PQS and 64PCS package drawings.

Delete heat sink reference on p. 13.

HOLT INTEGRATED CIRCUITS

15

HI-3584 PACKAGE DIMENSIONS

52-PIN J-LEAD CERQUAD inches (millimeters)

Package Type: 52U

7 1 52 47

.788 max .720 ±.010

(20.0) SQ. (18.29 ±.25)

.750 ±.007

(19.05 ±.18)

.190 max

.040 ± .005 (4.826)

(1.02 ± .013)

.019 ±.002 .050 BSC BSC = “Basic Spacing between Centers”

(.483 ±.051) (1.27) is theoretical true position dimension and

has no tolerance. (JEDEC Standard 95)

52-PIN PLASTIC QUAD FLAT PACK (PQFP) millimeters (inches)

Package Type: 52PQS

0.65

BSC

(0.026)

13.200 10.000

BSC SQ BSC SQ

(.520) (0.394) 0.310 ± 0.090

(0.012 ± 0.004)

0.880 ± 0.150

(0.035 ± 0.006)

1.60

typ

(0.063)

0.20

min

(0.008)

See Detail A

0.30

2.70

MAX. (0.012)R max

(0.106) 2.00 ± 0.20

(0.079 ± 0.008)

0° £ Q £ 7°

0.13

R min

(0.005)

BSC = “Basic Spacing between Centers”

is theoretical true position dimension and DETAIL A

has no tolerance. (JEDEC Standard 95)

HOLT INTEGRATED CIRCUITS

16

HI-3584 PACKAGE DIMENSIONS

64-PIN PLASTIC CHIP-SCALE PACKAGE (QFN) millimeters (inches)

Package Type: 64PCS

Electrically isolated heat

sink pad on bottom of

package

Connect to any ground or

power plane for optimum

9.00

BSC thermal dissipation 7.25 ± 0.50

(0.354)

(0.285 ± 0.020)

0.50

BSC

(0.0197)

9.00 7.25 ± 0.50

(0.354)

BSC Top View (0.285 ± 0.020)

Bottom 0.25

typ

View (0.10)

0.40 ± 0.10

(0.016 ± 0.004)

0.20

typ

(0.008)

BSC = “Basic Spacing between Centers”

1.00 is theoretical true position dimension and

max

(0.039) has no tolerance. (JEDEC Standard 95)

HOLT INTEGRATED CIRCUITS

17

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (589)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5806)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- R12 Extend Oracle Applications Customizing OA Framework Applications Ed1 Student Guide - Volume 3 PDFDocument302 pagesR12 Extend Oracle Applications Customizing OA Framework Applications Ed1 Student Guide - Volume 3 PDFmariocelisNo ratings yet

- LACP Configuration GuideDocument2 pagesLACP Configuration Guidethiago_sampaioNo ratings yet

- Emmc - 4gb 64gb - CTRD - 441 It - OrIGINAL 169-Ball 14x18mmDocument24 pagesEmmc - 4gb 64gb - CTRD - 441 It - OrIGINAL 169-Ball 14x18mmnmgopiNo ratings yet

- Ftp-628Mcl401/451: Battery Driven, Ftp-608 Series 2" High Speed Thermal PrinterDocument8 pagesFtp-628Mcl401/451: Battery Driven, Ftp-608 Series 2" High Speed Thermal PrinternmgopiNo ratings yet

- Thermal Table AnalogDocument1 pageThermal Table AnalognmgopiNo ratings yet

- Via PDFDocument9 pagesVia PDFnmgopiNo ratings yet

- Sintetizador Con PicDocument7 pagesSintetizador Con Picbotmaster100% (1)

- PUNCOM1Document6 pagesPUNCOM1ashish118No ratings yet

- Export Final BD Alarmas RepsolDocument9 pagesExport Final BD Alarmas RepsolRoberto Carrasco OlanoNo ratings yet

- Lifetime and Support Matrix For SAP GUI For JavaDocument3 pagesLifetime and Support Matrix For SAP GUI For Javal3uoNo ratings yet

- Oculus Mobile v0.5.0 SDK Documentation PDFDocument84 pagesOculus Mobile v0.5.0 SDK Documentation PDFnixonjl03No ratings yet

- OOP Lab ManualDocument7 pagesOOP Lab ManualAlexandraNo ratings yet

- Computer Architecture LAB 2Document4 pagesComputer Architecture LAB 2Abdul HayeeNo ratings yet

- Data Analytics Unit-3 NotesDocument21 pagesData Analytics Unit-3 Notes18R11A0530 MUSALE AASHISHNo ratings yet

- Books PHPDocument53 pagesBooks PHPV.M.B.SNo ratings yet

- Wireless Quiz IIIDocument3 pagesWireless Quiz IIIAlishba RehmanNo ratings yet

- HYCU For Azure User GuideDocument88 pagesHYCU For Azure User GuideRatnodeep RoyNo ratings yet

- NullDocument1 pageNullapi-16223719No ratings yet

- Maayoke Technologies (P) LTD: Project Title List (Java/J2Ee/Dotnet)Document14 pagesMaayoke Technologies (P) LTD: Project Title List (Java/J2Ee/Dotnet)Srinu GovinduNo ratings yet

- Summary of Conclusions Case 1Document7 pagesSummary of Conclusions Case 1jonabramsonNo ratings yet

- TaglibDocument145 pagesTaglibNguyen Minh Trieu (K15 HCM)No ratings yet

- Laptop ListDocument20 pagesLaptop List_arzuriel_No ratings yet

- Advance Computer Architecture Homework 2 SolutionDocument8 pagesAdvance Computer Architecture Homework 2 SolutionJahanzaib AwanNo ratings yet

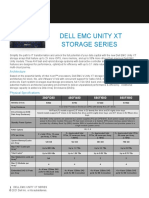

- Dell Emc Unity XT Storage Series: ArchitectureDocument10 pagesDell Emc Unity XT Storage Series: Architecturesiddy8108No ratings yet

- Configure An Opc Ua Server On A Compactlogix 5480 Controller Using Factorytalk Linx GatewayDocument17 pagesConfigure An Opc Ua Server On A Compactlogix 5480 Controller Using Factorytalk Linx Gatewayeng abctechNo ratings yet

- ACID PropertiesDocument3 pagesACID Propertiesberhe2121No ratings yet

- ModelSim® Command Reference Manual V10.3aDocument484 pagesModelSim® Command Reference Manual V10.3akiritoNo ratings yet

- Sifive S76-Mc Manual 20G1.03.00Document149 pagesSifive S76-Mc Manual 20G1.03.00Ivan Vera de los SantosNo ratings yet

- 11.1.10 Packet Tracer - Implement Port SecurityDocument2 pages11.1.10 Packet Tracer - Implement Port SecurityMazen NabeelNo ratings yet

- Forensic XDocument2 pagesForensic XSaksham RawatNo ratings yet

- Newvhdl Syllabus (It&Cse)Document2 pagesNewvhdl Syllabus (It&Cse)Mude Kishore NaikNo ratings yet

- GitHub - Juliandewit - Kaggle - Criteo - Software For The Kaggle Criteo ChallengeDocument2 pagesGitHub - Juliandewit - Kaggle - Criteo - Software For The Kaggle Criteo ChallengePiNo ratings yet

- Belal Final PDFDocument123 pagesBelal Final PDFmhabdouNo ratings yet