Professional Documents

Culture Documents

Vlsi 2

Vlsi 2

Uploaded by

abhinav kumar0 ratings0% found this document useful (0 votes)

7 views2 pagesOriginal Title

vlsi2

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

7 views2 pagesVlsi 2

Vlsi 2

Uploaded by

abhinav kumarCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 2

SRN

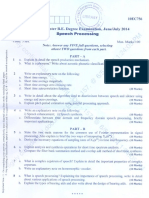

PES University, Bangalore UE14EC303

PES (Established under Kamataka Act No. 16 of 2013)

December 2016: END SEMESTER ASSESSMENT (ESA) B.TECH. V SEMESTER

UE14EC303- VLSI Design

If the Boolean function of a complex gate is X = (4+ B)C + DEF (GH +1) then

) Write the circuit diagram using CMOS to implement the expression given above

Time: 3 Hrs ‘Answer All Questions Max Marks: 100

)] Waite the Threshold Voltage (Va) expression (NMOS or PMOS). Write all the | 05

parameters involved in Va calculation along with default value (if applicable).

Determine pullup to pulldown ratio (ZpwZpd) for an NMOS Inverter driven by another | 05

nMOS Inverter. Inverter is constructed using enhancement driver and depletion load

nMOSFET.

y | Caleulate Ip and Vps for Vip= -1V, pnCox=200A/V? for the below shown circuit | 05

structure. The value 200 represents resistance in ohm i.e., R=200 ohm.

bv

4.5V

Vo

200

) | Titustrate enhancement NMOS transistor operation using relevant diagrams with standard | 5

layer encoding and mention the voltage conditions.

@) | Write the symbolic diagram of 1 bit CMOS Shift Register Cell. 05

) | Explain al types of contact cuts with respect to their requirement in layout. Write lambda | 0°

based design rules for contact cut used for metall to poly or metall to diffusion layer.

) | For the function F=aeb-+e write the stick diagram (only monochrome). 05

@ | Explain the fabrication of enhancement NMOS transistor with relevant figures using 05

standard encoding for layers.

) | Explain the following 05

1. Need for Scaling

2. Scaling models

1 | Find the scaling factors for the below mentioned parameters for combined (in terms of a, | 05

8) scaling model. Write all the steps required to arrive at the final scaling factor .

1. Saturation current

2. Switching Energy

3._Power dissipation per unit area

Define the standard unit of delay t using the concept of sheet resistance and standard | 05

unit of capacitance. Write the expression for +. Evaluate the value of for Sum, 2 um,

1.2 um technologies using the table given at the end.

i) 05

SRN [

ii) If the output of the above complex gate ie., X is driving a load of 20Cg units,

what will be the worst-case rising delay and falling delay in t units? Assume that

all NMOS and PMOS transistors are of same size . consider the resistance of

PMOS channel (Rp ) is 2 times of the resistance of NMOS channel (Rn).

2)

‘Explain Dynamic Manchester carry chain circuit for 4 Dit addition with relevant circuit.

05

b)

Explain area / floor plan optimization with a relevant diagram showing the proper

placement of components in array multiplier

°)

‘Write Carry Save Adder addition flow/block diagram using 3:2 reduction and 7:2

reduction. Give an example for 3:2 carry save addition.

05

®

Explain Baugh-Wooley Multiplier with relevant expression and example.

a)

Explain Funnel Shifter operation using Pass transistor based circuit and table showing

the operation and offset.

05

b)

Explain operation of ‘C’MOS based static and dynamic latches with circuit diagram.

05

°)

1) What is the minimum clock period at which the following circuit can be operated

correctly? The parameters of the components are as follows.

Inverter: tpd = 200ps, tod = 100ps, 2-input NOR: tpd = 200ps, ted = 150ps

Deflop: tpeq = 200ps ted = Ops, Setup time = 300 ps, Hold time = 100 ps.

meh Hees

ew LS

Il) The circuit can be optimized by removing the pair of inverters and connecting the

Q output of the left register directly to the D input of the right register. If the

clock period could be adjusted appropriately, would the optimized circuit operate

correctly? If yes, explain the adjustment to the clock period that would be needed.

IfNo, justify your answer.

05

Explain the Max -Delay and Min-Delay constraints with relevant expressions and

waveforms with reference to Flip Flop based design.

“Typ wen capacance val fr MOS es

Copaciance Tee pF 10a ate vs race)

Tse 2 72pm

‘Gus w damsel 4+ dm § 0 16 Go

ion (ev) 1 @25 178 @2y 375 029

Pobilleen to abst 04 G1) 06 C07) 06 GOH

Metal Up sbeonte 03 ors) 033 (0H) 033 aD

Meal2 to esate 02 (a0 017 @@2) 017 @O)

Mant 2 metal} ta @ as (0) 05 aD

Mata 21 pion 03 (G75) 03 (0038) _ 03 OOH

“ype het resoaces , of MOS liye for 5 yt, and Orbit 2 punt and

TZ jo etasloies

tae Bohm por guar

Sim ‘Ors Orb 2 pm

Mat 003 006 008

ison oe atvy?® oso 0s BS

Side a = =

Polyion 15910015930 1s900

sransistr canoe wt ax" 2x10"

vane ehumel asxiot —asxiot asx tot

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- em Waves R S Shevgaonkar PDFDocument505 pagesem Waves R S Shevgaonkar PDFabhinav kumar0% (1)

- Engineering Management 2 C Assignment QuestionsDocument3 pagesEngineering Management 2 C Assignment Questionsabhinav kumarNo ratings yet

- Assignment 2 DIP 2019Document9 pagesAssignment 2 DIP 2019abhinav kumarNo ratings yet

- 2 3 DNSDocument14 pages2 3 DNSabhinav kumarNo ratings yet

- CODE ArduinoDocument11 pagesCODE Arduinoabhinav kumarNo ratings yet

- RSPM/PM10 by GRID1 (Week 4 Mar)Document14 pagesRSPM/PM10 by GRID1 (Week 4 Mar)abhinav kumarNo ratings yet

- Lec7-8 Speech ProcessingDocument54 pagesLec7-8 Speech Processingabhinav kumarNo ratings yet

- Lec5 6Document32 pagesLec5 6abhinav kumarNo ratings yet

- Logic DesignDocument80 pagesLogic Designabhinav kumarNo ratings yet

- Lec9-10 Speech ProcessingDocument34 pagesLec9-10 Speech Processingabhinav kumarNo ratings yet

- Kijrary: Speech ProcessingDocument1 pageKijrary: Speech Processingabhinav kumarNo ratings yet

- Speech Processing: at Least TWO Questions From Each PartDocument1 pageSpeech Processing: at Least TWO Questions From Each Partabhinav kumarNo ratings yet