Professional Documents

Culture Documents

基于Calibre 工具的系统级芯片物理验证 PDF

Uploaded by

Mandy Wu0 ratings0% found this document useful (0 votes)

37 views3 pagesOriginal Title

基于Calibre 工具的系统级芯片物理验证.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

37 views3 pages基于Calibre 工具的系统级芯片物理验证 PDF

Uploaded by

Mandy WuCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 3

基于 Calibre 工具的系统级芯片物理验证

编者按:随着芯片集成度和规模的不断提高,在设计的各个层次上所需运行的验证也相应增

多,DRC 和版图与电路图(LVS)的对比检查变得越来越重要,它对于消除错误、降低设计成

本和减少设计失败的风险具有重要作用,本文介绍了基于 Calibre 工具的 DRC 和 LVS 验证

方法。

一般地说,SoC 芯片中包含了几个乃

至几十个 IP 核。在本文提到的系统级

芯片(SoC)中,除了采用了三个厂家的

IP 硬核外,还自行设计开发了十余个

IP 硬核。在 SoC 芯片开发的实际商业

运作中,设计方购买的是 IP 硬核在一

个产品中的使用权。IP 硬核提供商为

了保护自己的版权,通常不会将其 IP

硬核的物理版图用 GDSII 格式交给用

户。他们所提供的只是 IP 硬核的几个

框图和引出端的位置和属性。这就带

来一个问题,在进行 SoC 芯片的版图设计验证时,最重要的问题是验证工具必须能让用户

进行“层次化”验证。即用户可以把他们完成版图设计后的 SoC 分成若干模块或者区域,对

他们进行多层次的验证。

在集成电路从 ASIC 进入到 SoC 阶段(当然在 SoC 阶段中 ASIC 还是会存在下去的)的时候,

这种可以进行“层次化”版图验证的工具就显得十分必要。甚至可以说,不具备“层次化”验证

功能的工具,是无法用于 SoC 芯片的版图设计验证的。本文首先介绍 Calibre 软件所具备

的“层次化”验证功能,然后说明其在对 SoC 芯片进行版图设计验证时就所发挥的作用。

Calibre DRC 简介

目前,Calibre 工具已经被众多设计公司、单元库和 IP 开发商、晶圆代工厂采用为深亚微

米集成电路的物理验证工具。Calibre 具有先进的分层次处理功能,是唯一能在提高验证速

率的同时,可优化重复设计层次化的物理验证工具。

Calibre DRC 用于版图的设计规则检查,具有高效能、高容量和高精度,还具有足够的弹性,

即便是系统芯片包含有设计方法差异极大的模拟与数字电路,也可以方便地进行验证。具体

表现在以下几个方面:

(1) 检查内容丰富准确:既包括简单的 DRC 规则检查,如宽度、间距、包含关系等的检查,

又包括一些复杂的 DRC 检查,如天线规则、电流流向规则和导线密度规则等。本公司所设

计的 SoC 为数模混合电路,采用 Calibre DRC 除进行了宽度、间距、包含关系等简单的 DRC

检查外,也进行了一些复杂的 DRC 检查。其结果得到了 TSMC 等代工厂的认可。

(2) 文件运行方式可选:运行 DRC 文件时,可以采用命令行的方式,也可以采用图形界面

方式, Calibre Interactive-DRC 是 Mentor Graphics 公司推出的 Calibre 物理验证的新版本

(Calibre Interactive),它已作为

Cadence Design Systems 公司全定

制设计环境 Virtuoso 的插件。现在,

Virtuoso 的用户能够直接从 Virtuoso

中调用 Calibre Interactive 进行工作。

对于规模较小的版图应用 Interactive

非常方便而且直观的图形化接口便于

初学者使用。 在我们的项目开发过程

中,同时用到了这两种方式。对于全定制版图,经常要选用图形界面工具 Calibre

Interactive-DRC,对于自动布局布线出来的 SoC 版图,我们采用了命令行的形式,可以快

速地得到 DRC 检查报告。

(3) 结果浏览快捷方便:通过 Calibre RVE(Results Viewing Environment,验证结果视图环

境)和版图编辑器分析 DRC 的结果进行查错, 准确快捷,一目了然。RVE 可以指出出错类

型和数目,使用 Highlight 命令可以直接标明版图中的出错地方(图 2),可以很方便地修正版

图中的错误。无论是规模不大的模拟电路,还是大规模的 SoC 电路,其 DRC 检查都可以

通过启动 RVE,对照版图和分析 DRC 结果文件,可以快速修改错误或进行优化。

RVE 能够同常见的版图环境实现自动整合,这些版图环境包括:Mentor Graphics 的 Calibre

DESIGNrev 和 IC Station 以及 Cadence 的 Virtuoso 和 Seiko,Avant!的 Apollo 和 Enterprise

等工具。在我们的设计中使用的是 Virtuoso。

(4) 多线程能力:Calibre 的多线程技术(CalibreMT)提供多 CPU 环境下的杰出性能。Calibre

几何划分版图层次化使之成为上千个独立的“线程”支持多处理器工作站或者服务器应用,每

一个线程可以在独立的处理器上运行,这样的结构对性能的提高是巨大的。简单的“turbo”

命令行选项就可以实现高性能的 CalibreMT 的调用,而不需要任何辅助文件或者设置约束

信息的支撑。CalibreMT 支持多 CPU 高度灵活的结构并且不会导致 RAM 的大量增加。

Calibre LVS 简介

Calibre LVS 是一个出色的版图与线路图对比检查工具,具有高效率、高准确度和大容量等

优点。Calibre LVS 不仅可以对所有的“元件”进行验证,而且还能在不影响性能的条件下,

处理无效数据。主要表现在以下几个方面:

(1) 运行模式快捷方便:Calibre LVS 有两种运行模式,即命令行模式和界面模式(Calibre

Interactive-LVS)。采用命令行模式可以快速输入控制命令,快速运行,其结果精确稳定。

Calibre Interactive-LVS 能够自动选择验证正被编辑的单元,并且能够选择所有的 Calibre

运行时间选项以及标准文件的规范。该验证技术,允许用户选择特定标准文件以及独立规则

和规则组的任何子集。GUI 可控制普通使用的 LVS 选项,并记录运行设置过程。当采用修

改控制或冻结标准文件时,它可将运行配置数据传给 Calibre。其界面友好,使用方便。我

们在做 LVS 过程中,对于规模较小的模拟电路和数模混合电路,一般采用方便的图形界面

模式(Calibre Interactive-LVS)进行对比检查,这样可以在启动 RVE 后,对照 LVS 结果文件

和版图,将电路(或者网表)和版图直接对应起来检查,非常方便;对于大规模的 SoC 电路,

由于命令行方式输入简单直接,运行速度更快,运行结果稳定精确,这次就采用了命令行方

式来运行 LVS,获得了极大的成功。

(2) 多种比较方式可选:Calibre LVS 可以进行版图与电路图(layout vs shematic)和网表与

网表(netlist vs netlist)的方式对比检查,还可以单独从版图提取网表。而且,通过 v2lvs 命

令,可以将自动布局布线所产生的 verilog 网表转换成 spice 网表,然后与自动布局布线的

版图进行对比,操作简单方便,结果精确。由此可见,可以根据不同需要,在 LVS 验证过

程的不同阶段,灵活地选择比较方式,以获得最有效的运行和最佳的结果。

(3) 侦错方便快捷:当运行完 LVS 后,Calibre LVS 会产生一个结果报告,明确指出出错类

型和数目,并且可以对层次化中的每个模块都有一个完整的 LVS 报告,简单明了。这个报

告还能明确指出短路(特别是电源和地短路的情况)、开路、浮空或孤立的 nets、pin swapping

以及软连接等问题。Calibre LVS 还能产生一个详细的结果数据库,其中包括原理图网表、

从版图抽取的网表、结果报告、版图中的器件及连接关系等。这样通过 RVE 来读取这些数

据,就可以在版图和网表中准确地 Highlight 有错误的地方(图 1)。

由此可见,Calibre LVS 所产生的结果文件结构清晰,又可以通过 RVE 来准确定位,能有

效地帮助用户快速地消除错误以降低设计风险,这在我们项目的开发过程中得到了完全的体

现。由于时间紧迫,致使后端设计的时间相当紧张,正是 Calibre LVS 能准确无误、快速地

查出短路、开路、浮空或孤立的网络、引脚、软连接等问题,还能很好地识别晶体管、门级

电路和模块级电路,才使得我们按时地完成了百万门级的信息安全 SoC 的设计。

在反复使用 Calibre LVS 的图形界面的运行方式和命令行方式过程中,发现 Calibre LVS 图

形界面的运行方式方便快捷,但是其稳定性不如命令行方式好,若能加以改进,则能进一步

提高验证精准度。

本文小结

Calibre 工具作为 ASIC 特别是 SoC 的物理验证工具,正在成为设计公司的设计与半导体制

造公司交接的标准框架。Calibre DRC 和 Calibre LVS 使用方式灵活快捷,验证准确精度高,

结果浏览一目了然; 加上 Mentor Graphics 公司能及时提供高水平的技术支持,从而可以

快速地消除错误,降低设计成本,减少设计失败的风险。

作者:郁群慧

Email: yuqh@hongsi-ic.com

谭静荣

Email: donna1cn@yahoo.com

张建人

Email: zhangjr@hongsi-ic.com

北京宏思电子技术有限公司

李丽

技术工程师

Mentor Graphics 公司

Email: li_li@mentor.com

You might also like

- 第02讲 软件工程概述2Document66 pages第02讲 软件工程概述2lolonowasolongNo ratings yet

- Wind - 未来自治网联汽车的ecu整合方案Document3 pagesWind - 未来自治网联汽车的ecu整合方案Shawn WuNo ratings yet

- D8 软件开发安全Document50 pagesD8 软件开发安全Kevin HuangNo ratings yet

- NI LabVIEW High-Performance FPGA User's GuideDocument94 pagesNI LabVIEW High-Performance FPGA User's GuidevnetawzNo ratings yet

- 构建基于eBPF的应用可观测系统Document26 pages构建基于eBPF的应用可观测系统eskyheroNo ratings yet

- 艾瑞咨询:2021年中国企业级无代码白皮书Document62 pages艾瑞咨询:2021年中国企业级无代码白皮书黄俊No ratings yet

- 2 张鹏 以二进制为中心的CICD和安全Document34 pages2 张鹏 以二进制为中心的CICD和安全RogerZhuoNo ratings yet

- 火线沙龙第27期 业务出海的安全新挑战 曾垚Document24 pages火线沙龙第27期 业务出海的安全新挑战 曾垚eferfrewferNo ratings yet

- Lynx设计系统用户手册中文翻译Document291 pagesLynx设计系统用户手册中文翻译hukuhei youNo ratings yet

- 第一章 概述Document34 pages第一章 概述张浩象No ratings yet

- 轻舟低代码平台外宣Document64 pages轻舟低代码平台外宣cckunNo ratings yet

- Ug 908Document48 pagesUg 908l690931789No ratings yet

- 多环境下的CI CD自动化集成部署设计 刘万里Document5 pages多环境下的CI CD自动化集成部署设计 刘万里Benson LiNo ratings yet

- 微處理器原理與應用-C語言與PIC18微控制器 Microprocessors Fundamentals and Applications-Using C Language and PIC18 MicrocontrollersDocument31 pages微處理器原理與應用-C語言與PIC18微控制器 Microprocessors Fundamentals and Applications-Using C Language and PIC18 MicrocontrollersSTM Works0% (1)

- 03 第三讲 微处理器指令集设计Document44 pages03 第三讲 微处理器指令集设计Xiang LiNo ratings yet

- 思码逸Merico产品手册Document6 pages思码逸Merico产品手册dkjlllNo ratings yet

- 01 第一讲 SOC技术概述Document45 pages01 第一讲 SOC技术概述Xiang LiNo ratings yet

- 基于移动平台的轴承故障诊断系统设计 李雨田Document4 pages基于移动平台的轴承故障诊断系统设计 李雨田魏泽涵No ratings yet

- 111?????????e-Learning???? - 1101208 2Document14 pages111?????????e-Learning???? - 1101208 2吳東翰No ratings yet

- CH 1Document25 pagesCH 1Lubo1983No ratings yet

- CN Model Based Design With Simulation White PaperDocument12 pagesCN Model Based Design With Simulation White Paperlin nanjuNo ratings yet

- APICloud 低代码开发行业白皮书 2019Document39 pagesAPICloud 低代码开发行业白皮书 2019Some One Like YouNo ratings yet

- 第02课:深入分析软件的复杂度Document5 pages第02课:深入分析软件的复杂度woshizhangzhang0829No ratings yet

- Thinkcore TC-RV1106 IPC 38板 500w一体化机芯 规格书Document10 pagesThinkcore TC-RV1106 IPC 38板 500w一体化机芯 规格书Rostislav NikitinNo ratings yet

- 07 云巧工程体系-云巧组件标准与度量Document10 pages07 云巧工程体系-云巧组件标准与度量huangjiehui92No ratings yet

- Asip Designer Ds CNDocument6 pagesAsip Designer Ds CN魏震榮No ratings yet

- CodeWarrior 基本使用教程Document58 pagesCodeWarrior 基本使用教程c790629782No ratings yet

- Lowcode WPDocument41 pagesLowcode WPLu HenryNo ratings yet

- 【C 中 - 高级开发工程师 - 北京】戴先生 6年Document4 pages【C 中 - 高级开发工程师 - 北京】戴先生 6年370994944No ratings yet

- 思科集成客服平台 UCCXDocument60 pages思科集成客服平台 UCCX吳明璁No ratings yet

- Cadence 实验系列10 Verilog设计平台 NC-VerilogDocument48 pagesCadence 实验系列10 Verilog设计平台 NC-Veriloghukuhei youNo ratings yet

- 嵌入式航空电子系统的趋势和进展:ATR 圆桌会议 - 航空航天技术评论Document8 pages嵌入式航空电子系统的趋势和进展:ATR 圆桌会议 - 航空航天技术评论陈杰No ratings yet

- Auto Network and SDNDocument80 pagesAuto Network and SDNa70180No ratings yet

- 15 SystemC語言概論 下155530Document11 pages15 SystemC語言概論 下155530jasonturfNo ratings yet

- 敏捷软件开发Document11 pages敏捷软件开发liuyonglogNo ratings yet

- 密码学论文Document7 pages密码学论文nlxkoxengNo ratings yet

- IPC CFX工業4.0標準初探Document21 pagesIPC CFX工業4.0標準初探vincent.tseng118No ratings yet

- Oracle Acs Aiops Solution Sharing ZhsDocument53 pagesOracle Acs Aiops Solution Sharing Zhs50224274No ratings yet

- 05 第五讲 SOC系统的结构设计Document20 pages05 第五讲 SOC系统的结构设计Xiang LiNo ratings yet

- 手把手教你设计cpu.risc V处理器Document426 pages手把手教你设计cpu.risc V处理器LEENo ratings yet

- 褚向阳 基于K8s原生扩展的机器学习平台引擎MLEngineDocument31 pages褚向阳 基于K8s原生扩展的机器学习平台引擎MLEngineejibo112586No ratings yet

- PDFDocument179 pagesPDF贝贝宋No ratings yet

- Go 微服务框架 Kitex 扩展性设计和实践Document40 pagesGo 微服务框架 Kitex 扩展性设计和实践yao samuelNo ratings yet

- SSTIC2019 Article IDRACKAR Iooss ZHDocument55 pagesSSTIC2019 Article IDRACKAR Iooss ZHwenchang.1979No ratings yet

- Data PDFDocument256 pagesData PDFlllxxxlllNo ratings yet

- NI DevelopingProficiency PDFDocument10 pagesNI DevelopingProficiency PDFchen joeNo ratings yet

- Product Guide Vision Software ENDocument12 pagesProduct Guide Vision Software ENchaoxiangdong45No ratings yet

- 处理器全面介绍 CPU研究框架Document110 pages处理器全面介绍 CPU研究框架Hannah YuNo ratings yet

- 在产业升级大潮中寻求自我突破的中国工业软件产业20231017Document47 pages在产业升级大潮中寻求自我突破的中国工业软件产业20231017letian940No ratings yet

- 04-PAM-ADMIN Access Control (Safes) 1 37 TranslateDocument37 pages04-PAM-ADMIN Access Control (Safes) 1 37 TranslateyaohangNo ratings yet

- 任天兵 基于ES的搜索平台在哈啰的应用Document22 pages任天兵 基于ES的搜索平台在哈啰的应用Fang YongNo ratings yet

- 亿赛通产品报价手册 V3.0Document23 pages亿赛通产品报价手册 V3.0Dawn HernandezNo ratings yet

- 01、软件工程概述Document24 pages01、软件工程概述ying tianNo ratings yet

- nacos架构与原理Document326 pagesnacos架构与原理Yuan JianHuaNo ratings yet

- 2022年車企數字化轉型趨勢系列研究之研發數字化篇Document58 pages2022年車企數字化轉型趨勢系列研究之研發數字化篇acerNo ratings yet

- 轻松管理软件项目 -Ch2-了解软件生命周期Document66 pages轻松管理软件项目 -Ch2-了解软件生命周期孙启立No ratings yet

- 329091087 CISSP培训 1访问控制Document49 pages329091087 CISSP培训 1访问控制jripperxNo ratings yet

- 华为FPGA设计流程指南Document24 pages华为FPGA设计流程指南lieshi2958100% (1)

- 第1章 嵌入式系统基础知识 - 1.3嵌入式微处理器的结构和类型1Document20 pages第1章 嵌入式系统基础知识 - 1.3嵌入式微处理器的结构和类型1Mjk Zizzy ZionJrNo ratings yet

- special report and work summary: LOGO 可替换 / 工作汇报 / 述职等模板Document26 pagesspecial report and work summary: LOGO 可替换 / 工作汇报 / 述职等模板唐骏蔚MickeyNo ratings yet

- GEN Control System FiguresDocument14 pagesGEN Control System FigureshalimberdiNo ratings yet

- 王品 最新方案Document3 pages王品 最新方案Testgame GameonlyNo ratings yet

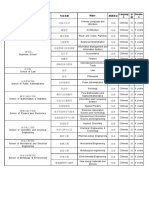

- 2021年中南大学国际学生本科生专业目录 2021 CSU Bachelor ProgramsDocument3 pages2021年中南大学国际学生本科生专业目录 2021 CSU Bachelor ProgramsOmar RefayNo ratings yet