Professional Documents

Culture Documents

Design and Implementation of A Configurable Platform For Embedded

Uploaded by

gameOverOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design and Implementation of A Configurable Platform For Embedded

Uploaded by

gameOverCopyright:

Available Formats

Design and Implementation of a Configurable Platform for Embedded

Communication Systems

Visvanathan Subramanian, Joseph G. Tront, Charles W. Bostian, Scott F. Midkiff

Bradley Department of Electrical & Computer Engineering

Virginia Tech

Blacksburg, VA 24061-0111

Abstract to energy considerations is another factor to be dealt with

Broadband wireless technologies have the potential to in making architectural choices. All of these requirements

provide integrated data and multimedia services in several necessitate a flexible, low energy architecture and a

niche areas. The rapid emergence of many new protocols system level design methodology upon which novel

in this area has created a growing need to develop high communication systems can be built.

performance communication systems that can satisfy The communication system application used here as an

high-end data processing requirements inherent in these example has several design constraints that dictate the use

technologies within ever decreasing time to market of a reconfigurable architecture. One of the applications

windows. A methodology used to develop a configurable for the architecture requires that the device interact with a

platform for embedded communication system designs is variety of other components that may communicate using

discussed here. One of the applications for the a variety of different protocols. Varying geographic

architecture requires that the device interact with a variety deployment of the device may also require dynamic

of components that may communicate using variety of adjustment of the operating behavior of the system

different protocols. Varying geographic deployment of hardware. Thus, the example architecture is built with the

the device may also require dynamic adjustment of the ability to be rapidly reconfigured in order to optimize its

operating behavior of the system hardware. Thus the functionality and performance. The design philosophy

architecture is built with the ability to be rapidly described herein is used to develop each of the

reconfigured in order to optimize its functionality and architectural configurations that the system reconfigures

performance. into.

1 Introduction 2 Platform-based Design

Designers of embedded wireless communication The emergence of a number of wireless standards like

systems face several difficult and interesting challenges Bluetooth [1], IEEE 802.11 [2] and IEEE 802.16 [3] has

before high-level protocol descriptions can be translated created a market for numerous applications and products.

into hardware and software that implement the system. However, they have also taught us that the lifetime of

Several issues related to access mechanisms, error rates, these products is rapidly decreasing even as the time-to-

transmission rates and bandwidth, need to be addressed. market budgets are decreasing. One of the solutions

The speed and complexity of these systems requires suggested by Ferrari et al. [4] and Kuetzer et al. [5] is

designers to break away from traditional architectures and platform-based design by orthogonalization or separation

design methodologies. A more comprehensive and of design space concerns. Platform-based design aims to

cohesive design process including both hardware and reduce design time by facilitating reuse using abstractions

software is required to overcome these challenges. called platforms consisting of functionally unique entities

Moreover designers must also contend with rapidly that may be used in different configurations throughout an

changing or evolving standards and specifications. This architecture. For example, a set of parameterizable

requires that the target hardware platform allow architectures that satisfy the constraints and support the

maximum flexibility to incorporate future design or functional specifications of a design is called a hardware

algorithmic changes. Increasing importance being given platform. Similarly a software platform is a software layer

0-7695-1926-1/03/$17.00 (C) 2003 IEEE

Proceedings of the International Parallel and Distributed Processing Symposium (IPDPS’03)

consisting of the real-time operating system (RTOS) and 3 Configurable Platform Design for

device drivers that allows for abstraction of the hardware Communication Systems

platform through an interface called the Application

Program Interface (API). The combination of the

hardware and software platforms constitutes the system 3.1 Functional Profiling

platform.

Functions in communication systems can be broadly

classified into data processing and control functions [7].

2.1 Platform-based Design Methodology

Most communication systems perform “packet

processing” parallel operations as well as bit serial data

The platform-based design methodology can be processing operations. They can be further classified as

broadly classified into three phases viz., platform operations that modify data and those that don’t alter it.

conception, platform instantiation and implementation Control functions include event processing and decision

[6]. The design flow is represented in Fig.1. ‘Platform making functions. These functions are then represented as

conception’ is the process of developing hardware and finite state machines that can be mapped to either

software platforms. It is imperative that the target hardware or software. The functions identified are helpful

application be fully understood before embarking on a in understanding the complexity and the requirements for

platform design. The first step in the development of a the system.

hardware platform, functional profiling, is to identify and

extract common functionality and features of the

application domain. The next step, architecture 3.2 Architectural Exploration

exploration, is to identify architectures for these functions

that would deliver adequate performance while satisfying Before considering the architecture topologies, the

the constraints of the application domain. Once the design space for the application domain must be

hardware platform is clearly defined the software identified. In this case the design space includes general

platform can be developed. ‘Platform instantiation’ and specialized microprocessors, digital signal processors,

involves mapping functionality to specific modules that programmable logic devices and custom application

results in optimal performance under the given specific integrated circuits. For a platform-based design

constraints. The mapping process involves the methodology to be robust it must be able to handle

development of platforms with varying performance from application redesigns and improvements without much

architecture modules in the system platform and then change to the base platform elements. Therefore, the

selecting an optimal platform for the application. When platform must be built on a foundation of configurable

all the design constraints are satisfied, the implementation architecture and parameterizable elements that allow for

of an application becomes software based. The easy integration and scaling.

application designer only needs to focus his attention on

the application software compilation and hardware

synthesis to create an application.

Efficiency

Functional Design/ Custom ASIC

Feature Specification Architecture Definition

Hybrid

(Processor +

FPGA)

FPGA

Programmable Network/

Logic Devices Communication

Mapping Process DSP Processors

Microprocessor

Flexibility

Physical Implementation

Fig.2 Architecture Design Space for

Communication Designs

Fig.1 Platform-based System Design

The simplest and most common architecture employed

Methodology in traditional designs is a microprocessor or DSP with a

0-7695-1926-1/03/$17.00 (C) 2003 IEEE

Proceedings of the International Parallel and Distributed Processing Symposium (IPDPS’03)

set of application specific peripherals. In this scenario all

CPU CPU Memory

the system blocks are mapped to software running on the

processor or DSP. Though this provides a lot of flexibility

the serial processing model of software-based design

limits system performance to a great extent. On the other

hand, ASICs yield very high performance but require

significant NRE cost and effort. ASICs offer no flexibility

to the designer and require tremendous redesign efforts in Peripheral Controller/

the face of changing specifications or standard updates. DMA

This makes the ASIC option unsuitable for the

development of applications that are based on standards

that have not yet stabilized or undergoing development –

Peripherals

a trend that is common in today’s industry. Further, the

ASIC offers little or no ability to dynamically reconfigure

the hardware. Given these requirements programmable

logic devices like FPGAs offer an excellent alternative. Fig. 3. Design A: Single Microprocessor

High density FPGAs and readily available configurable IP

cores provide significant performance improvement by Design A consisted of a single general-purpose

allowing designers to take advantage of parallelism and microprocessor with all functionality mapped into

pipelining processing stages. software. Even initial analysis of the design suggested

that the system would not be able to handle very high

bandwidth data processing requirements. The major

Designers can also take advantage of hybrid problem was the processor bus bottleneck and the serial

architectures involving a processor and a FPGA co- processing model. Design A was not analyzed in detail

processor to achieve almost triple performance for certain further even though it may have been suitable for lower

“cycle-intensive” operations [8]. The choice of the bandwidth applications as our goal was to identify designs

processor is crucial and determines whether a system that satisfied high bandwidth requirements.

block is implemented as hardware or software. The

processor choice also determines system parameters like

voltage levels, I/O standards and most importantly the bus CPU Memory Peripherals

protocol. The new breed of specialized network and

communication processors are ideally suited for control

and some “packet processing” operations in high

bandwidth applications and have built-in network

interfaces that simplify design.

Once the microprocessor target is identified, the

software platform, which interfaces the hardware to the

FPGA

programmer through device drivers and Application Coprocesor

Peripherals

Program Interface (API), can be developed. RTOS

choices and multiple OS support for the target hardware

platform must be weighed before developing the software Fig. 4 Design B: General Purpose

platform. Processor and FPGA Co-processor

Design B consisted of a general-purpose processor

3.3. Mapping along with an FPGA co-processor. Various processors

like the i960 and PowerPC family and bus protocols were

Various iterations (Designs A, B and C) of considered. The FPGA co-processor implemented on a

the design process were considered for the Xilinx Virtex FPGA acted like a DMA controller by

configurable hardware platform and their suitability moving data and reducing the processor load and by being

to the application domain was studied. the flexible hardware location where various high speed

and potentially different communication protocol

operations would take place. Control operations were

implemented in software running on the processor. Some

bit-serial operations, like the modulation symbol mapping

and radio interface, were moved to hardware logic on the

0-7695-1926-1/03/$17.00 (C) 2003 IEEE

Proceedings of the International Parallel and Distributed Processing Symposium (IPDPS’03)

FPGA in order to provide the flexibility of network interfaces with support for Fast Ethernet, ATM

reconfiguration when appropriate. This helped to simplify and T1 / HDLC protocols. The Xilinx Virtex XCV600

the serial interfaces and also reduce bus bottlenecks. FPGA [10] offers high densities up to 1M+ gates, 512

I/Os and up to 16 KB of Internal Single/Dual Port SRAM

embedded memory.

Functional Unit Processor Program Memory

The Software Platform consists of a Board Support

Package (BSP) developed for VxWorks RTOS from

Processor Bus

Wind River Systems and device drivers for Ethernet,

UART and other common functions. This can then be

FPGA used to generate and compile the application software.

Dual Port

Memory

Processing

Element

Processor 4 Applications: Emergency Response

Bus Bridge

Communications Gateway

4.1 System Overview

Functional

Unit

Processing This section presents the results of the application of

Element Functional Unit

the reconfigurable platform to the development of a

broadband wireless Gateway prototype for a rapidly

Memory Unit

deployable LMDS wireless high-speed communications

system [11] to support emergency management. The

Processing

Functional Unit system utilizes surviving network infrastructure to

Element

provide network connectivity to field workers in the

aftermath of emergencies or disasters for applications

such as Internet Access, Audio/Video conferencing,

Fig.5 Design C: featuring a memory- Geographic Information System (GIS) access. The

centric architecture network topology consists of a base station or hub and

multiple field units. Field units may be of a single type

The third iteration, Design C, was proposed to take and communication protocol, but may also be from

greater advantage of IP core reuse and further simplifies several different responding agencies, all with different

interfaces to promote easier integration of heterogeneous communications protocols. To allow the communication

system blocks. Essentially we analyzed the system and interface to operate with a variety of possible protocols,

identified the functions which are likely to be constant the device must be dynamically reconfigurable. The base

over the expected variety of operation modes – the station has a high data rate connection to the surviving

functions that would never be required to be part of a terrestrial network. The field units provide PDAs or

reconfiguration. In order to achieve this objective, a laptops carried by field personnel with LAN services

“memory-centric” architecture with combination of a ranging from 10/100 Mbps Ethernet to IEEE 802.11

Virtex FPGA and a specialized communication processor wireless connectivity. A radio sounder unit is attached to

was implemented. A shared dual-port RAM that allowed each field unit. The sounder device senses the viability of

the processor and FPGA logic to read and write data the radio path and dynamically reconfigures the base

simultaneously was introduced. Further, embedded dual station and field units to change the bit rates, protocol,

port SRAM memory available within the FPGA was used etc. to optimize communication based on tolerable error

to create distributed buffers between various processing levels seen in the current channel configuration. Sounder

stages. Most control functions were implemented in testing, and thus possible reconfiguration typically takes

software while some critical functions like timing place at the rate of once every ten seconds.

references were mapped to the FPGA blocks. Also to take

advantage of the optimizations in the specialized 4.2 Gateway Prototype Implementation

processor the packet processing functions are retained in

software. Many communication and network processors The Gateway design implements a complex time

were considered, but the Motorola PowerQuicc II division multiple access MAC scheme with different

processor family was found to be most suitable for the uplink and downlink frequencies on the wireless link and

application. The Motorola PowerQuicc II 8255 an Ethernet interface on the wire line side. The TDMA

communication processor [9] consists of a high MAC protocol implements various physical layer

performance 64-bit, 200MHz PowerPC core and a 32-bit, adaptation techniques like variable forward error

133 MHz communication processor that simplifies correction (FEC) and optional link level Automatic

0-7695-1926-1/03/$17.00 (C) 2003 IEEE

Proceedings of the International Parallel and Distributed Processing Symposium (IPDPS’03)

Repeat Request (ARQ) capability. The gateways are resources. This effort will be further reduced once more

capable of handling data rates up to 120 Mbps. Given the intellectual property blocks are available for use in

high bandwidth required and the amount of data that producing the system platform.

needs to be transported between blocks, the hybrid

architecture of Design C was used with processing 6 Acknowledgement

elements implemented partly in software and partly in

FPGA hardware. The Ethernet PHY device and RS232 The authors gratefully acknowledge the contributions

transceiver directly connect to the Motorola of all members of the project team, including other faculty

communication processor through standard interfaces. and students at Virginia Tech. We also gratefully

The serial interfaces are implemented in the FPGA. Table acknowledge the support of the National Science

1 provides a summary of the logic resources utilized by Foundation’s Digital Government program (grant

the design and does not include test or expansion pins. #9983463) and the National Response Center. Generous

The Motorola 60x system bus protocol used by the donations by Motorola Wireless Initiative and Wind River

processor is well defined and allows multiple masters and Systems also aided this project.

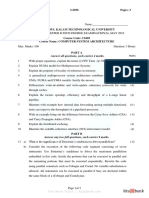

cache support. The system architecture is shown in Fig.6.

7 References

FPGA Element Utilization

Number of Slices 426 [1] The Bluetooth Special Interest Group

Slice Flip Flops 415 http://www.bluetooth.com/

4 input LUTs 622 [2] IEEE 802.11 Working Group for WLAN

Number of bonded IOBs 256 http://grouper.ieee.org/groups/802/11/

Number of Block RAMs 16 [3] IEEE 802.16 Working Group on Broadband Wireless

Access Standards http://grouper.ieee.org/groups/802/16/

Total equivalent gate count 273,288

[4] Ferrari A., Sangiovanni-Vincentelli A., “ System

Design: Traditional Concepts and New Paradigms”, Intl.

Table 1. Virtex XCV600 FPGA Device Utilization Conf. on Computer Design (ICCD 1999), 1999.

Summary for Gateway Prototype Design [5] Kuetzer et al., “System Level Design:

Orthogonalization of Concerns and Platform-based

Design”, IEEE Transactions on Computer Aided Design

of Integrated Circuits and Systems, Vol.9, No.2,

December 2000.

5 Conclusion [6] Rabaey J.M., et al., “Challenges and Opportunities in

Broadband and Wireless Communication Designs”,

IEEE/ACM Conf on Computer Aided Design (ICCAD

Individual system components and protocols have

2000). 2000.

been simulated and found to be satisfactory for targeted

[7] Iliopoulos M., Antonakopoulos T., “ A Methodology

data rates and expected channel conditions. Several of the

of Implementing Medium Access Protocols Using a

hardware components including the modems and the

General Parameterized Architecture”. Proceedings of the

sounder have been built and tested. The overall system

11th International Workshop on Rapid System

controller is currently undergoing board manufacture

Prototyping (RSP 2000), 2000.

testing and will be field tested in December 2002.

[8] Knapp S.K., “Using Programmable Logic to

Using the platform design strategy, the design effort

Accelerate DSP Functions”, Xilinx Inc., 1996.

needed to develop a platform instance such as a disaster

[9] Motorola Inc., “MPC8255 Hardware Specifications”,

communications gateway prototype from the baseline

rev 0.3, May 2002. www.motorola.com/

platform was greatly reduced, thereby reducing

[10] Xilinx Inc., “Virtex 2.5V Field Programmable Gate

development time for the product. This includes the time

Arrays”, Product Specifications v2.5, April 2001.

required for performing tradeoff comparisons between

www.xilinx.com/

various implementations strategies as described in

[11] S. F. Midkiff and C. W. Bostian, “Rapidly-

Designs A,B,and C. No hardware/software design tools

Deployable Broadband Wireless Networks for Disaster

were used for partitioning and exploration; the system

and Emergency Response”, First IEEE Workshop on

was implemented based on estimation of complexity of

Disaster Recover Networks (DIREN '02), 2002.

the functional blocks. However, the effort required is still

mostly manual design and does require some design

0-7695-1926-1/03/$17.00 (C) 2003 IEEE

Proceedings of the International Parallel and Distributed Processing Symposium (IPDPS’03)

100 Mbps 10/100 Mbps Media

Ethernet Ethernet PHY Independe

nt Interface Motorola

(MII) PowerQuicc II

Host RS 232 Processor

Interface Transceiver

EEPROM

SDRAM

/Flash

60x Processor Address Bus (32)

60x Processor Data Bus (64)

Reed DUAL PORT

Solomon SRAM

Codec

Xilinx Virtex

FPGA

Turbo Codec Radio

Interface

Fig.6 Physical Implementation of Disaster Response Gateway Prototype

0-7695-1926-1/03/$17.00 (C) 2003 IEEE

Proceedings of the International Parallel and Distributed Processing Symposium (IPDPS’03)

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Real-Time Software Design For Embedded Systems - Hassan GomaaDocument1,172 pagesReal-Time Software Design For Embedded Systems - Hassan GomaaAhmad Abdulrahem100% (1)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- V Rajaraman Fundamentals of Computers Sample PDFDocument16 pagesV Rajaraman Fundamentals of Computers Sample PDFज्योति राय63% (8)

- CC111 Introduction To Computers: Lecturer: Dr. EMAD OSMAN E-Mail: 01025830256Document413 pagesCC111 Introduction To Computers: Lecturer: Dr. EMAD OSMAN E-Mail: 01025830256Mohamed elalamyNo ratings yet

- Nokia, Qualcomm and T-Mobile Achieve Industry-First 5G Carrier Aggregation Combining 5 Component Carriers #MWC23 - Qualcomm PDFDocument7 pagesNokia, Qualcomm and T-Mobile Achieve Industry-First 5G Carrier Aggregation Combining 5 Component Carriers #MWC23 - Qualcomm PDFgameOverNo ratings yet

- 87-27161-1 Rev A Snapdragon X75 5G Modem-Rf System Product Brief PDFDocument1 page87-27161-1 Rev A Snapdragon X75 5G Modem-Rf System Product Brief PDFgameOverNo ratings yet

- Global Mobile Industry Leaders Commit To Support 5G Mmwave in Collaboration With QualcommDocument2 pagesGlobal Mobile Industry Leaders Commit To Support 5G Mmwave in Collaboration With QualcommgameOverNo ratings yet

- P410G8TS81 TimeSync Server Adapter STS2 PDFDocument4 pagesP410G8TS81 TimeSync Server Adapter STS2 PDFgameOverNo ratings yet

- 87-27160-1 Rev A Snapdragon X35 5G Modem-Rf System Product Brief PDFDocument1 page87-27160-1 Rev A Snapdragon X35 5G Modem-Rf System Product Brief PDFgameOverNo ratings yet

- Kumu Networks Awarded Department of Defense Contract To Prototype 5G Full-Duplex IAB - Business WireDocument1 pageKumu Networks Awarded Department of Defense Contract To Prototype 5G Full-Duplex IAB - Business WiregameOverNo ratings yet

- Satellite Communication in The Age of 5G: Marc HofmannDocument6 pagesSatellite Communication in The Age of 5G: Marc HofmanngameOverNo ratings yet

- Rach Procedures For Non-Terrestrial NetworksDocument30 pagesRach Procedures For Non-Terrestrial NetworksgameOverNo ratings yet

- Mesh Networks: Moving From Ad Hoc To Fixed Infrastructure: BrochureDocument5 pagesMesh Networks: Moving From Ad Hoc To Fixed Infrastructure: BrochuregameOverNo ratings yet

- 5G millimeter wave: delivering gigabit speeds from kilometers awayDocument6 pages5G millimeter wave: delivering gigabit speeds from kilometers awaygameOverNo ratings yet

- Design and Implementation of A Configurable Platform For EmbeddedDocument6 pagesDesign and Implementation of A Configurable Platform For EmbeddedgameOverNo ratings yet

- Evolution of Carrier Aggregation (CA) For 5G: What's New in Mobile CADocument4 pagesEvolution of Carrier Aggregation (CA) For 5G: What's New in Mobile CAtriple_patteNo ratings yet

- Edited Transcript: Refinitiv StreeteventsDocument35 pagesEdited Transcript: Refinitiv StreeteventsgameOverNo ratings yet

- FSM200xx - 5G Platform For Small Cells - QualcommDocument4 pagesFSM200xx - 5G Platform For Small Cells - QualcommgameOverNo ratings yet

- Energy-Efficienct Link Adaptation in Frequency-Selective ChannelsDocument10 pagesEnergy-Efficienct Link Adaptation in Frequency-Selective ChannelsgameOverNo ratings yet

- On The Performance Limitations of Realistic Massive Mimo Deployments in 5G Mmwave Wireless Cellular NetworksDocument5 pagesOn The Performance Limitations of Realistic Massive Mimo Deployments in 5G Mmwave Wireless Cellular NetworksgameOverNo ratings yet

- ICC08 - Energy Efficienct Design For OFDMA PDFDocument6 pagesICC08 - Energy Efficienct Design For OFDMA PDFgameOverNo ratings yet

- Cross-Layer Energy-Efficient Wireless CommunicationsDocument13 pagesCross-Layer Energy-Efficient Wireless CommunicationsgameOverNo ratings yet

- Interference EE - ICC09Document5 pagesInterference EE - ICC09gameOverNo ratings yet

- 书签Document2 pages书签gameOverNo ratings yet

- Cochannel Interference Avoidance MAC in Wireless Cellular NetworksDocument11 pagesCochannel Interference Avoidance MAC in Wireless Cellular NetworksgameOverNo ratings yet

- Wireless Communications Interoperability StatusDocument33 pagesWireless Communications Interoperability StatusgameOverNo ratings yet

- Future Challenges of Signal Processing and Communications in Wireless NetworksDocument15 pagesFuture Challenges of Signal Processing and Communications in Wireless NetworksgameOverNo ratings yet

- An Overview of The WIDENS MACPHY Layer For Rapidly Deployable Broadband Public Safety Communication SystemsDocument22 pagesAn Overview of The WIDENS MACPHY Layer For Rapidly Deployable Broadband Public Safety Communication SystemsgameOverNo ratings yet

- Demonstrating Rapidly Deployable Broadband Wireless Communications For Emergency ManagementDocument6 pagesDemonstrating Rapidly Deployable Broadband Wireless Communications For Emergency ManagementgameOverNo ratings yet

- A Configurable Architecture For High-Speed Communication SystemsDocument8 pagesA Configurable Architecture For High-Speed Communication SystemsgameOverNo ratings yet

- Wireless DEployable Network SystemDocument2 pagesWireless DEployable Network SystemgameOverNo ratings yet

- "Evolution of Signaling (TDM To Ip/Sigtran) ": Stephen Madden Technical Marketing EngineerDocument33 pages"Evolution of Signaling (TDM To Ip/Sigtran) ": Stephen Madden Technical Marketing EngineergameOverNo ratings yet

- NETWORK SLICING 5G-NR-in-BulletsDocument2 pagesNETWORK SLICING 5G-NR-in-BulletsgameOverNo ratings yet

- Unit-I DATADocument35 pagesUnit-I DATAPrakash giriNo ratings yet

- C G1056 Pages: 3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G1056 Pages: 3: Answer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- Lecture 1 Parallel DatabasesDocument30 pagesLecture 1 Parallel DatabasesKumkumo Kussia KossaNo ratings yet

- Cse SyllabusDocument34 pagesCse SyllabusVaishnavi MittalNo ratings yet

- AI Expert System Architecture and DevelopmentDocument138 pagesAI Expert System Architecture and DevelopmentRonit SinghNo ratings yet

- Problem Solving and Programming: Dr. A. Nayeemulla KhanDocument192 pagesProblem Solving and Programming: Dr. A. Nayeemulla KhanMassSomeshNo ratings yet

- Cray XC 30 BrochureDocument6 pagesCray XC 30 Brochurergr3gg4gNo ratings yet

- 15CS34 Computer FundamentalsDocument109 pages15CS34 Computer FundamentalsIndraja JNo ratings yet

- Chapter-5 Multithreading in JavaDocument28 pagesChapter-5 Multithreading in JavaNaoly GetNo ratings yet

- Generation of Computer ': Rajiv Academy For Technology and Management, Mathura ONDocument26 pagesGeneration of Computer ': Rajiv Academy For Technology and Management, Mathura ONsouarvNo ratings yet

- Cuda C/C++ Basics: NVIDIA CorporationDocument67 pagesCuda C/C++ Basics: NVIDIA Corporationrj jNo ratings yet

- Open MPDocument30 pagesOpen MPmacngocthanNo ratings yet

- Multithreading Superscalar Processors Intel-S Hyper ThreadingDocument18 pagesMultithreading Superscalar Processors Intel-S Hyper ThreadingSouthern Vermont CollegeNo ratings yet

- DDS Lecture 2Document38 pagesDDS Lecture 2SajjadAbdullah0% (1)

- EC527 Spring 2014Document6 pagesEC527 Spring 2014deepim4No ratings yet

- FPGA Paper PDFDocument18 pagesFPGA Paper PDFDhayanandhNo ratings yet

- Introduction to Operations SchedulingDocument252 pagesIntroduction to Operations SchedulingSyphax TensaoutNo ratings yet

- Computer Architecture: First EditionDocument6 pagesComputer Architecture: First EditionThangavel MuruganNo ratings yet

- Unit 4 - Cloud Programming ModelsDocument21 pagesUnit 4 - Cloud Programming ModelsMag CreationNo ratings yet

- Understanding Inherent ParallelismDocument12 pagesUnderstanding Inherent ParallelismAravind RajkumarNo ratings yet

- The Design of Optimized RISC Processor For Edge Artificial Intelligence Based On Custom Instruction Set ExtensionDocument13 pagesThe Design of Optimized RISC Processor For Edge Artificial Intelligence Based On Custom Instruction Set Extensionmadupiz@gmailNo ratings yet

- t1 Brief Essay On x86 ProcessorsDocument1 paget1 Brief Essay On x86 Processorshiyig71969No ratings yet

- OpenMP Tutorial for Parallel ProgrammingDocument30 pagesOpenMP Tutorial for Parallel ProgrammingVictor Manuel Chavez BrunoNo ratings yet

- TelemacDocument6 pagesTelemacArturo Campusano BaltazarNo ratings yet

- CH17-COA10e - Parallel ProcessingDocument45 pagesCH17-COA10e - Parallel ProcessingFirmanNo ratings yet

- Pub Parallel-Programming PDFDocument242 pagesPub Parallel-Programming PDFJoemon JoseNo ratings yet