Professional Documents

Culture Documents

MP1482DS Datasheet PDF

MP1482DS Datasheet PDF

Uploaded by

charly36Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MP1482DS Datasheet PDF

MP1482DS Datasheet PDF

Uploaded by

charly36Copyright:

Available Formats

MP1482

2A, 18V Synchronous Rectified

Step-Down Converter

The Future of Analog IC Technology

DESCRIPTION FEATURES

The MP1482 is a monolithic synchronous buck 2A Output Current

regulator. The device integrates two 130mΩ Wide 4.75V to 18V Operating Input Range

MOSFETs, and provides 2A of continuous load Integrated 130mΩ Power MOSFET Switches

current over a wide input voltage of 4.75V to Output Adjustable from 0.923V to 15V

18V. Current mode control provides fast Up to 93% Efficiency

transient response and cycle-by-cycle current Programmable Soft-Start

limit. Stable with Low ESR Ceramic Output Capacitors

Fixed 340kHz Frequency

An adjustable soft-start prevents inrush current

at turn-on, and in shutdown mode the supply Cycle-by-Cycle Over Current Protection

current drops to 1µA. Input Under Voltage Lockout

8–Pin SOIC

This device, available in an 8-pin SOIC

package, provides a very compact solution with APPLICATIONS

minimal external components. Distributed Power Systems

Networking Systems

FPGA, DSP, ASIC Power Supplies

Green Electronics/ Appliances

Notebook Computers

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green

status, please visit MPS website under Products, Quality Assurance page.

“MPS” and “The Future of Analog IC Technology” are registered trademarks of

Monolithic Power Systems, Inc.

TYPICAL APPLICATION

Efficiency vs

INPUT Load Current

100

95 VOUT = 3.3V

2 1 90

EFFICIENCY (%)

IN BS

7 3 85 VOUT = 2.5V

EN SW

MP1482 80

8 5 75

SS FB

GND COMP 70

4 6

65

60

55

50

0 0.5 1.0 1.5 2.0 2.5

LOAD CURRENT (A)

MP1482 Rev. 1.31 www.MonolithicPower.com 1

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

ORDERING INFORMATION

Part Number Package Top Marking Free Air Temperature (TA)

MP1482DS* SOIC8 MP1482DS -40C to +85C

* For Tape & Reel, add suffix –Z (e.g. MP1482DS–Z);

For RoHS Compliant Packaging, add suffix –LF (e.g. MP1482DS–LF–Z)

PACKAGE REFERENCE

TOP VIEW

BS 1 8 SS

IN 2 7 EN

SW 3 6 COMP

GND 4 5 FB

SOIC8

ABSOLUTE MAXIMUM RATINGS (1) Thermal Resistance

(4)

θJA θJC

Supply Voltage VIN ........................-0.3V to +20V SOIC8..................................... 90 ...... 45... C/W

Switch Node Voltage VSW ............................ 21V

Boost Voltage VBS ..........VSW – 0.3V to VSW + 6V Notes:

1) Exceeding these ratings may damage the device

All Other Pins ..................................-0.3V to +6V 2) The maximum allowable power dissipation is a function of the

Junction Temperature ...............................150°C maximum junction temperature TJ(MAX), the junction-to-

ambient thermal resistance θJA, and the ambient temperature

Continuous Power Dissipation (TA = +25°C)(2) TA. The maximum allowable continuous power dissipation at

SOIC8……………………………………….1.38W any ambient temperature is calculated by

Lead Temperature ....................................260°C PD(MAX)=(TJ(MAX)-TA)/ θJA. Exceeding the maximum

allowable power dissipation will cause excessive die

Storage Temperature .............. -65°C to +150°C temperature, and the regulator will go into thermal shutdown.

(3) Internal thermal shutdown circuitry protects the device from

Recommended Operating Conditions permanent damage..

Input Voltage VIN ............................4.75V to 18V 3) The device is not guaranteed to function outside of its

operating conditions.

Output Voltage VOUT .....................0.923V to 15V 4) Measured on JESD51-7, 4-layer board.

Operating Junct. Temp (TJ)........-40°C to +125°C

MP1482 Rev. 1.31 www.MonolithicPower.com 2

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

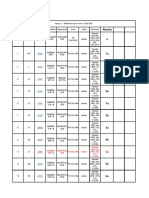

ELECTRICAL CHARACTERISTICS

VIN = 12V, TA = +25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

Shutdown Supply Current VEN = 0V 1 3.0 μA

Supply Current VEN = 2.0V; VFB = 1.0V 1.3 1.5 mA

Feedback Voltage VFB 4.75V VIN 18V 0.900 0.923 0.946 V

Feedback Overvoltage Threshold 1.1 V

Error Amplifier Voltage Gain (5) AEA 400 V/V

Error Amplifier Transconductance GEA IC = 10μA 800 μA/V

(5)

High-Side Switch On Resistance RDS(ON)1 130 mΩ

Low-Side Switch On Resistance (5) RDS(ON)2 130 mΩ

High-Side Switch Leakage Current VEN = 0V, VSW = 0V 10 μA

Upper Switch Current Limit Minimum Duty Cycle 2.4 3.4 A

Lower Switch Current Limit From Drain to Source 1.1 A

COMP to Current Sense

GCS 3.5 A/V

Transconductance

Oscillation Frequency Fosc1 305 340 375 kHz

Short Circuit Oscillation Frequency Fosc2 VFB = 0V 100 kHz

Maximum Duty Cycle DMAX VFB = 1.0V 90 %

Minimum On Time (5) 220 ns

EN Shutdown Threshold Voltage VEN Rising 1.1 1.5 2.0 V

EN Shutdown Threshold Voltage

210 mV

Hysteresis

EN Lockout Threshold Voltage 2.2 2.5 2.7 V

EN Lockout Hysterisis 210 mV

Input Under Voltage Lockout

VIN Rising 3.80 4.10 4.40 V

Threshold

Input Under Voltage Lockout

210 mV

Threshold Hysteresis

Soft-Start Current VSS = 0V 6 μA

Soft-Start Period CSS = 0.1μF 15 ms

Thermal Shutdown (5) 160 °C

Note:

5) Guaranteed by design, not tested.

MP1482 Rev. 1.31 www.MonolithicPower.com 3

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

PIN FUNCTIONS

SOIC8

Name Description

Pin #

High-Side Gate Drive Boost Input. BS supplies the drive for the high-side N-Channel MOSFET

1 BS

switch. Connect a 0.01μF or greater capacitor from SW to BS to power the high side switch.

Power Input. IN supplies the power to the IC, as well as the step-down converter switches.

2 IN Drive IN with a 4.75V to 18V power source. Bypass IN to GND with a suitably large capacitor to

eliminate noise on the input to the IC. See Input Capacitor.

Power Switching Output. SW is the switching node that supplies power to the output. Connect

3 SW the output LC filter from SW to the output load. Note that a capacitor is required from SW to BS

to power the high-side switch.

4 GND Ground.

Feedback Input. FB senses the output voltage to regulate that voltage. Drive FB with a resistive

5 FB voltage divider from the output voltage. The feedback threshold is 0.923V. See Setting the

Output Voltage.

Compensation Node. COMP is used to compensate the regulation control loop. Connect a

series RC network from COMP to GND to compensate the regulation control loop. In some

6 COMP

cases, an additional capacitor from COMP to GND is required. See Compensation

Components.

Enable Input. EN is a digital input that turns the regulator on or off. Drive EN high to turn on the

7 EN

regulator, drive it low to turn it off. Pull up with 100kΩ resistor for automatic startup.

Soft-Start Control Input. SS controls the soft start period. Connect a capacitor from SS to GND

8 SS to set the soft-start period. A 0.1μF capacitor sets the soft-start period to 15ms. To disable the

soft-start feature, leave SS unconnected.

MP1482 Rev. 1.31 www.MonolithicPower.com 4

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, VO = 3.3V, L = 10µH, C1 = 10µF, C2 = 22µF, TA = +25°C, unless otherwise noted.

Steady State Test Startup through Enable Shutdown through Enable

VIN = 12V, VOUT = 3.3V VIN = 12V, VOUT = 3.3V VIN = 12V, VOUT = 3.3V

IOUT = 0A, IIN= 8.2mA IOUT = 1A (Resistance Load) IOUT = 1A (Resistance Load)

VIN

20mV/div. VEN VEN

5V/div. 5V/div.

VOUT

20mV/div. VOUT VOUT

1V/div. 2V/div.

IL

1A/div. IL IL

1A/div. 1A/div.

VSW

VSW

10V/div. VSW

10V/div.

10V/div.

Heavy Load Operation Medium Load Operation Light Load Operation

2A Load 1A Load No Load

VIN, AC VIN, AC VIN, AC

200mV/div. 200mV/div. 20mV/div.

VO, AC VO, AC

VO, AC

20mV/div. 20mV/div.

20mV/div.

IL IL

IL

1A/div. 1A/div.

1A/div.

VSW VSW VSW

10V/div. 10V/div. 10V/div.

Short Circuit Short Circuit Load Transient

Protection Recovery

VOUT

VOUT VOUT

2V/div.

2V/div. 200mV/div.

IL

IL 1A/div.

2A/div. IL

2A/div. ILOAD

1A/div.

MP1482 Rev. 1.31 www.MonolithicPower.com 5

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

OPERATION

FUNCTIONAL DESCRIPTION The converter uses internal N-Channel

The MP1482 is a synchronous rectified, MOSFET switches to step-down the input

current-mode, step-down regulator. It regulates voltage to the regulated output voltage. Since

input voltages from 4.75V to 18V down to an the high side MOSFET requires a gate voltage

output voltage as low as 0.923V, and supplies greater than the input voltage, a boost capacitor

up to 2A of load current. connected between SW and BS is needed to

drive the high side gate. The boost capacitor is

The MP1482 uses current-mode control to charged from the internal 5V rail when SW is low.

regulate the output voltage. The output voltage

is measured at FB through a resistive voltage When the MP1482 FB pin exceeds 20% of the

divider and amplified through the internal nominal regulation voltage of 0.923V, the over

transconductance error amplifier. The voltage at voltage comparator is tripped and the COMP

the COMP pin is compared to the switch current pin and the SS pin are discharged to GND,

measured internally to control the output forcing the high-side switch off.

voltage.

+

CURRENT IN

OVP SENSE

-- AMPLIFIER +

1.1V

RAMP 5V

OSCILLATOR

FB + --

CLK

340KHz

BS

0.3V --

+ S Q

-- R Q SW

SS + -- CURRENT

ERROR COMPARATOR

0.923V + AMPLIFIER

COMP

-- GND

EN

EN OK 1.2V OVP

IN < 4.1V

LOCKOUT

2.5V + COMPARATOR

IN

+

INTERNAL

REGULATORS

1.5V -- SHUTDOWN

COMPARATOR

Figure 1—Functional Block Diagram

MP1482 Rev. 1.31 www.MonolithicPower.com 6

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

APPLICATIONS INFORMATION

COMPONENT SELECTION Choose an inductor that will not saturate under

Setting the Output Voltage the maximum inductor peak current. The peak

The output voltage is set using a resistive inductor current can be calculated by:

voltage divider from the output voltage to FB pin. VOUT V

The voltage divider divides the output voltage ILP ILOAD 1 OUT

2 f S L VIN

down to the feedback voltage by the ratio:

R2 Where ILOAD is the load current.

VFB VOUT

R1 R2 The choice of which style inductor to use mainly

Where VFB is the feedback voltage and VOUT is depends on the price vs. size requirements and

the output voltage. any EMI requirements.

Thus the output voltage is: Optional Schottky Diode

During the transition between high-side switch

R1 R2 and low-side switch, the body diode of the low-

VOUT 0.923

R2 side power MOSFET conducts the inductor

R2 can be as high as 100kΩ, but a typical value current. The forward voltage of this body diode

is 10kΩ. Using the typical value for R2, R1 is is high. An optional Schottky diode may be

determined by: paralleled between the SW pin and GND pin to

improve overall efficiency. Table 1 lists example

R1 10.83 ( VOUT 0.923 ) (kΩ) Schottky diodes and their Manufacturers.

For example, for a 3.3V output voltage, R2 is Table 1—Diode Selection Guide

10kΩ, and R1 is 26.1kΩ.

Voltage/Current

Part Number Vendor

Inductor Rating

The inductor is required to supply constant B130 30V, 1A Diodes, Inc.

current to the output load while being driven by SK13 30V, 1A Diodes, Inc.

the switched input voltage. A larger value

International

inductor will result in less ripple current that will MBRS130 30V, 1A

Rectifier

result in lower output ripple voltage. However,

the larger value inductor will have a larger Input Capacitor

physical size, higher series resistance, and/or The input current to the step-down converter is

lower saturation current. A good rule for discontinuous, therefore a capacitor is required

determining the inductance to use is to allow to supply the AC current to the step-down

the peak-to-peak ripple current in the inductor converter while maintaining the DC input

to be approximately 30% of the maximum voltage. Use low ESR capacitors for the best

switch current limit. Also, make sure that the performance. Ceramic capacitors are preferred,

peak inductor current is below the maximum but tantalum or low-ESR electrolytic capacitors

switch current limit. The inductance value can may also suffice. Choose X5R or X7R

be calculated by: dielectrics when using ceramic capacitors.

VOUT V Since the input capacitor (C1) absorbs the input

L 1 OUT switching current it requires an adequate ripple

f S I L VIN

current rating. The RMS current in the input

Where VOUT is the output voltage, VIN is the capacitor can be estimated by:

input voltage, fS is the switching frequency, and

ΔIL is the peak-to-peak inductor ripple current. VOUT VOUT

I C1 ILOAD 1

VIN VIN

MP1482 Rev. 1.31 www.MonolithicPower.com 7

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

The worst-case condition occurs at VIN = 2VOUT, The characteristics of the output capacitor also

where IC1 = ILOAD/2. For simplification, choose affect the stability of the regulation system. The

the input capacitor whose RMS current rating MP1482 can be optimized for a wide range of

greater than half of the maximum load current. capacitance and ESR values.

The input capacitor can be electrolytic, tantalum Compensation Components

or ceramic. When using electrolytic or tantalum MP1482 employs current mode control for easy

capacitors, a small, high quality ceramic compensation and fast transient response. The

capacitor, i.e. 0.1μF, should be placed as close system stability and transient response are

to the IC as possible. When using ceramic controlled through the COMP pin. COMP pin is

capacitors, make sure that they have enough the output of the internal transconductance

capacitance to provide sufficient charge to error amplifier. A series capacitor-resistor

prevent excessive voltage ripple at input. The combination sets a pole-zero combination to

input voltage ripple for low ESR capacitors can control the characteristics of the control system.

be estimated by:

The DC gain of the voltage feedback loop is

ILOAD V V given by:

VIN OUT 1 OUT

C1 fS VIN VIN VFB

A VDC R LOAD G CS A EA

Where C1 is the input capacitance value. VOUT

Output Capacitor Where AVEA is the error amplifier voltage gain;

The output capacitor is required to maintain the GCS is the current sense transconductance and

DC output voltage. Ceramic, tantalum, or low RLOAD is the load resistor value.

ESR electrolytic capacitors are recommended. The system has two poles of importance. One

Low ESR capacitors are preferred to keep the is due to the compensation capacitor (C3) and

output voltage ripple low. The output voltage the output resistor of the error amplifier, and the

ripple can be estimated by: other is due to the output capacitor and the load

VOUT V 1 resistor. These poles are located at:

VOUT 1 OUT R ESR

fS L VIN 8 f S C2 GEA

fP1

2 C3 A VEA

Where C2 is the output capacitance value and

RESR is the equivalent series resistance (ESR) 1

value of the output capacitor. fP2

2 C2 R LOAD

In the case of ceramic capacitors, the

Where GEA is the error amplifier transconductance.

impedance at the switching frequency is

dominated by the capacitance. The output The system has one zero of importance, due to the

voltage ripple is mainly caused by the compensation capacitor (C3) and the compensation

capacitance. For simplification, the output resistor (R3). This zero is located at:

voltage ripple can be estimated by:

1

f Z1

VOUT V 2 C3 R3

ΔVOUT 2

1 OUT

8 fS L C2 VIN The system may have another zero of

importance, if the output capacitor has a large

In the case of tantalum or electrolytic capacitors, capacitance and/or a high ESR value. The zero,

the ESR dominates the impedance at the due to the ESR and capacitance of the output

switching frequency. For simplification, the capacitor, is located at:

output ripple can be approximated to:

1

V V fESR

ΔVOUT OUT 1 OUT R ESR 2 C2 R ESR

fS L VIN

MP1482 Rev. 1.31 www.MonolithicPower.com 8

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

In this case (as shown in Figure 2), a third pole 3. Determine if the second compensation

set by the compensation capacitor (C6) and the capacitor (C6) is required. It is required if the

compensation resistor (R3) is used to ESR zero of the output capacitor is located at

compensate the effect of the ESR zero on the less than half of the switching frequency, or the

loop gain. This pole is located at: following relationship is valid:

1 1 f

fP 3 S

2 C6 R3 2 C2 R ESR 2

The goal of compensation design is to shape If this is the case, then add the second

the converter transfer function to get a desired compensation capacitor (C6) to set the pole fP3

loop gain. The system crossover frequency at the location of the ESR zero. Determine the

where the feedback loop has the unity gain is C6 value by the equation:

important. Lower crossover frequencies result

in slower line and load transient responses, C2 R ESR

C6

while higher crossover frequencies could cause R3

system instability. A good rule of thumb is to set External Bootstrap Diode

the crossover frequency below one-tenth of the An external bootstrap diode may enhance the

switching frequency. efficiency of the regulator, and it will be a must

To optimize the compensation components, the if the applicable condition is:

following procedure can be used. VOUT is 5V or 3.3V, and duty cycle is high:

1. Choose the compensation resistor (R3) to set VOUT

D= >65%

the desired crossover frequency. VIN

Determine the R3 value by the following In these cases, an external BST diode is

equation: recommended from the output of the voltage

2 C2 fC VOUT 2 C2 0.1 fS VOUT regulator to BST pin, as shown in Figure.2

R3

GEA GCS VFB GEA GCS VFB External BST Diode

IN4148

Where fC is the desired crossover frequency BST

which is typically below one tenth of the CBST

MP1482

switching frequency.

SW 5V or 3.3V

L +

2. Choose the compensation capacitor (C3) to COUT

achieve the desired phase margin. For

applications with typical inductor values, setting

the compensation zero, fZ1, below one-forth of Figure 2—Add Optional External Bootstrap

the crossover frequency provides sufficient Diode to Enhance Efficiency

phase margin. The recommended external BST diode is

Determine the C3 value by the following equation: IN4148, and the BST cap is 0.1~1µF.

4

C3

2 R3 f C

Where R3 is the compensation resistor.

MP1482 Rev. 1.31 www.MonolithicPower.com 9

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

TYPICAL APPLICATION CIRCUIT

INPUT

2 1

IN BS

7 3

EN SW

MP1482

8 5

SS FB

GND COMP

4 6

Figure 3—MP1482 with 3.3V Output, 22µF/6.3V Ceramic Output Capacitor

MP1482 Rev. 1.31 www.MonolithicPower.com 10

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

PCB LAYOUT GUIDE

PCB layout is very important to achieve stable 2) Bypass ceramic capacitors are suggested

operation. It is highly recommended to duplicate to be put close to the Vin Pin.

EVB layout for optimum performance.

3) Ensure all feedback connections are short

If change is necessary, please follow these and direct. Place the feedback resistors

guidelines and take Figure 4 for reference. and compensation components as close to

the chip as possible.

1) Keep the path of switching current short and

minimize the loop area formed by input cap, 4) Route SW away from sensitive analog

high-side MOSFET and low-side MOSFET. areas such as FB.

5) Connect IN, SW, and especially GND

respectively to a large copper area to cool

the chip to improve thermal performance

and long-term reliability.

C5

INPUT

4.75V to 18V

R4

2 1

IN BS L1

7 3

EN SW OUTPUT

MP1482 R1

8 5

SS FB

C1 GND COMP

4 6

D1 R2 C2

C3 (optional)

C4

R3

MP1482 Typical Application Circuit

R4 C3 R3

PGND

SS 8

EN 7

COMP 6

FB 5

C4 R1

R2

SGND

R1

PGND

4 GND

3 SW

D1

1 BS

2 IN

C2

C5 C1

L1

Top Layer Bottom Layer

Figure 4—MP1482 Typical Application Circuit and PCB Layout Guide

MP1482 Rev. 1.31 www.MonolithicPower.com 11

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP1482 – 2A, 18V SYNCHRONOUS RECTIFIED, STEP-DOWN CONVERTER

PACKAGE INFORMATION

SOIC8

0.189(4.80)

0.024(0.61) 0.050(1.27)

0.197(5.00)

8 5

0.063(1.60)

0.150(3.80) 0.228(5.80)

0.213(5.40)

PIN 1 ID 0.157(4.00) 0.244(6.20)

1 4

TOP VIEW RECOMMENDED LAND PATTERN

0.053(1.35)

0.069(1.75)

0.0075(0.19)

SEATING PLANE

0.0098(0.25)

0.004(0.10)

0.013(0.33) 0.010(0.25)

0.020(0.51) SEE DETAIL "A"

0.050(1.27)

BSC

FRONT VIEW SIDE VIEW

0.010(0.25)

x 45o NOTE:

0.020(0.50)

GAUGE PLANE 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN

0.010(0.25) BSC BRACKET IS IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS.

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH

0.016(0.41) OR PROTRUSIONS.

0o-8o 0.050(1.27) 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING)

SHALL BE 0.004" INCHES MAX.

5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA.

DETAIL "A" 6) DRAWING IS NOT TO SCALE.

NOTICE: The information in this document is subject to change without notice. Please contact MPS for current specifications.

Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS

products into any application. MPS will not assume any legal responsibility for any said applications.

MP1482 Rev. 1.31 www.MonolithicPower.com 12

7/9/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

You might also like

- BaTiO3 Ceramica ArtigoDocument7 pagesBaTiO3 Ceramica ArtigoLays de AraújoNo ratings yet

- Datasheet CM6802Document18 pagesDatasheet CM6802Gilson3DNo ratings yet

- Dell Inspiron 5150 Motherboard Schematics Document Compal LA-1682Document44 pagesDell Inspiron 5150 Motherboard Schematics Document Compal LA-1682Claudiu Petrache100% (1)

- 2.75V To 17V, 6A, 1.2Mhz, Synchronous, Ultra-Thin Power Module Description FeaturesDocument22 pages2.75V To 17V, 6A, 1.2Mhz, Synchronous, Ultra-Thin Power Module Description FeaturesEugene FlexNo ratings yet

- 2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyDocument10 pages2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyAnonymous aP1FSUPoNo ratings yet

- 3A, 50V, 100Khz Step-Down Converter With Programmable Output Ovp ThresholdDocument14 pages3A, 50V, 100Khz Step-Down Converter With Programmable Output Ovp Thresholdnan keNo ratings yet

- M2303ADNDocument15 pagesM2303ADNffyddNo ratings yet

- DC DC ConverterDocument9 pagesDC DC ConverterLotteDomineNo ratings yet

- MP2225GJ-Z Circuito IntegratoDocument20 pagesMP2225GJ-Z Circuito IntegratoMimmo FracchiollaNo ratings yet

- Datasheet MP2380DNDocument11 pagesDatasheet MP2380DNchevicitNo ratings yet

- Data Sheet MKP1584Document17 pagesData Sheet MKP1584aafeletronicaNo ratings yet

- MP1472 r1.0 PDFDocument13 pagesMP1472 r1.0 PDFAdyel PujolNo ratings yet

- Data SheetDocument10 pagesData Sheetmudasir iftikharnbuttNo ratings yet

- High Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterDocument15 pagesHigh Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterkadirovNo ratings yet

- 3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyDocument13 pages3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyIoan TivgaNo ratings yet

- MP28167GQ ADocument32 pagesMP28167GQ AHamouda MahmodNo ratings yet

- MP6001 r1.0Document13 pagesMP6001 r1.0nan keNo ratings yet

- MP2303Document12 pagesMP2303Sophie GelNo ratings yet

- High Current Power Half Bridge: The Future of Analog IC TechnologyDocument8 pagesHigh Current Power Half Bridge: The Future of Analog IC Technologyقناة احترف بنفسكNo ratings yet

- Features Description: Ltc3565 1.25A, 4Mhz, Synchronous Step-Down DC/DC ConverterDocument22 pagesFeatures Description: Ltc3565 1.25A, 4Mhz, Synchronous Step-Down DC/DC Converterferney_09No ratings yet

- Cost Effective Hall Effect-Based Linear Current Sensor IC Description FeaturesDocument19 pagesCost Effective Hall Effect-Based Linear Current Sensor IC Description FeaturesMartin NährNo ratings yet

- Offline, Primary-Side Regulator With CC/CV Control and A 700V MOSFETDocument21 pagesOffline, Primary-Side Regulator With CC/CV Control and A 700V MOSFETsluz2000No ratings yet

- MP2212 r1.01Document14 pagesMP2212 r1.01Joseni FigueiredoNo ratings yet

- 3A, 28V, 340Khz Synchronous Rectified Step-Down Converter: The Future of Analog Ic TechnologyDocument14 pages3A, 28V, 340Khz Synchronous Rectified Step-Down Converter: The Future of Analog Ic TechnologyFranklin AlvaradoNo ratings yet

- Mp1584en LF Z-2945524Document18 pagesMp1584en LF Z-2945524samuelRODNo ratings yet

- 2.8V-22V V, 3A I, 4-Switch Integrated Buck-Boost Converter With Fixed 5V Output Description FeaturesDocument19 pages2.8V-22V V, 3A I, 4-Switch Integrated Buck-Boost Converter With Fixed 5V Output Description FeaturesBrbrHuehue SzzNo ratings yet

- 3A, 28V, 925Khz Step-Down Converter: The Future of Analog Ic TechnologyDocument13 pages3A, 28V, 925Khz Step-Down Converter: The Future of Analog Ic TechnologyGabriel GodoyNo ratings yet

- Synchronous Step Down Converter: High Efficiency 3A, 24V, 500KhzDocument16 pagesSynchronous Step Down Converter: High Efficiency 3A, 24V, 500KhzAnonymous 8bbVmLtQNo ratings yet

- 3A, 23V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyDocument11 pages3A, 23V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyfixfixitNo ratings yet

- Sungrow - SG - 5 6 7 8 10 12RTDocument2 pagesSungrow - SG - 5 6 7 8 10 12RTchris dascalopoulosNo ratings yet

- Sungrow RT DatasheetDocument2 pagesSungrow RT Datasheetonlineearningbusiness857No ratings yet

- 5V/12V Synchronous-Rectified Buck Controller With Reference InputDocument19 pages5V/12V Synchronous-Rectified Buck Controller With Reference InputIgor LabutinNo ratings yet

- Fast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesDocument14 pagesFast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesKwun Hok ChongNo ratings yet

- Sungrow-SG3 0RT-SG4 0RTDocument2 pagesSungrow-SG3 0RT-SG4 0RTchris dascalopoulosNo ratings yet

- NB679Document18 pagesNB679Tri Nguyen Real EstateNo ratings yet

- MP3312 - r1.02 BU BUDocument15 pagesMP3312 - r1.02 BU BUnan keNo ratings yet

- Nb679a MpsDocument19 pagesNb679a MpswarkeravipNo ratings yet

- A4960 A Automotive DatasheetDocument34 pagesA4960 A Automotive DatasheetCanerNo ratings yet

- Arduino Driving Power Mosfet uRiZsEVG6kDocument11 pagesArduino Driving Power Mosfet uRiZsEVG6kahas viyanaNo ratings yet

- 28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDDocument24 pages28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDElla Wijaya ChandraNo ratings yet

- 2A, 23V Synchronous Rectified Step-Down Converter: The Future of Analog IC TechnologyDocument12 pages2A, 23V Synchronous Rectified Step-Down Converter: The Future of Analog IC TechnologyKerlin SanabriaNo ratings yet

- Manufacturer CatalogueDocument5 pagesManufacturer CatalogueRohit OjhaNo ratings yet

- MR2520 DatasheetDocument7 pagesMR2520 DatasheetOxkar YetiNo ratings yet

- ACT6311 Datasheet-345839Document11 pagesACT6311 Datasheet-345839rcgruwanNo ratings yet

- Ez6303qi 14122Document30 pagesEz6303qi 14122dd1663No ratings yet

- EN DS SG110CX Datasheet V152 20200714 PDFDocument2 pagesEN DS SG110CX Datasheet V152 20200714 PDFPhani ArvapalliNo ratings yet

- TPS65133 5-V, 250-Ma Dual-Output Power Supply: 1 Features 3 DescriptionDocument27 pagesTPS65133 5-V, 250-Ma Dual-Output Power Supply: 1 Features 3 DescriptionCarlos IbaNo ratings yet

- MP6908 同步整流Document14 pagesMP6908 同步整流857462946No ratings yet

- MP1471Document18 pagesMP1471freddyNo ratings yet

- NOT Recommended For New Designs Refer TO MP1477Document17 pagesNOT Recommended For New Designs Refer TO MP1477Yuber RaptorazorNo ratings yet

- MP24943Document13 pagesMP24943Agus OksNo ratings yet

- Snubber AN062 r1.2Document29 pagesSnubber AN062 r1.2Marcelo Flavio GuepfrihNo ratings yet

- AP62200/AP62201/AP62200T: 4.2V To 18V Input, 2A Low Iq Synchronous Buck ConverterDocument24 pagesAP62200/AP62201/AP62200T: 4.2V To 18V Input, 2A Low Iq Synchronous Buck ConverterAarsol AdvanceNo ratings yet

- MP5048GUDocument24 pagesMP5048GUHeraclio Camacho UlloaNo ratings yet

- Mp2565dn LF ZDocument20 pagesMp2565dn LF ZnvkjhejfjNo ratings yet

- sc4525c 1278277Document23 pagessc4525c 1278277Paulo OliveiraNo ratings yet

- U1 Xbox OneDocument14 pagesU1 Xbox OneCheckpoint Game CenterNo ratings yet

- INVERSOR DS - SG250HX-US Datasheet - V11 - ENDocument2 pagesINVERSOR DS - SG250HX-US Datasheet - V11 - ENErika RondónNo ratings yet

- A4950 DatasheetDocument9 pagesA4950 DatasheetIndra KurniawanNo ratings yet

- AP8012ADocument13 pagesAP8012ASamerNo ratings yet

- Tech 501 To 600Document3 pagesTech 501 To 600Jevan CalaqueNo ratings yet

- Surface Mount - Mounting Pad Dimensions and Considerations: Ceramic CapacitorsDocument16 pagesSurface Mount - Mounting Pad Dimensions and Considerations: Ceramic CapacitorssivaramNo ratings yet

- Repartizare BOM - 2019Document9 pagesRepartizare BOM - 2019Andrei SerbanNo ratings yet

- Capacitor Calculation For Buck Converter IC: Application NoteDocument7 pagesCapacitor Calculation For Buck Converter IC: Application NoteTahera SiddiquiNo ratings yet

- CapacitoresDocument48 pagesCapacitoresEnos Marcos BastosNo ratings yet

- Avx Rad Cer ThomsonDocument10 pagesAvx Rad Cer ThomsonΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- X2Y F & D C: Ilter Ecoupling ApacitorsDocument4 pagesX2Y F & D C: Ilter Ecoupling ApacitorsamirNo ratings yet

- Assembly InstructionsDocument4 pagesAssembly InstructionsAghzuiNo ratings yet

- Component Identification ElectronicsDocument23 pagesComponent Identification ElectronicsManjunatha Swamy VNo ratings yet

- Murata High Voltage CeramicDocument38 pagesMurata High Voltage CeramictycristinaNo ratings yet

- Electrostatics Electrical Multiple Choice Questions and Answers PDF Preparation For EngineeringDocument20 pagesElectrostatics Electrical Multiple Choice Questions and Answers PDF Preparation For EngineeringPatel DipenNo ratings yet

- AOZ1267QI-01: General Description FeaturesDocument16 pagesAOZ1267QI-01: General Description Featuresvictory_1410No ratings yet

- Noise Meter Full ProjectDocument24 pagesNoise Meter Full ProjectRobsson Banzi100% (2)

- CapacitorDocument7 pagesCapacitorFery YelyantoNo ratings yet

- IRS2092 Stereo AmplifierDocument10 pagesIRS2092 Stereo AmplifierĐoàn Minh CươngNo ratings yet

- Electrical & Electronic ComponentsDocument242 pagesElectrical & Electronic ComponentsAkash AdakNo ratings yet

- Capacitor Disk Ceramic Blue Safety CS Series E4b3 - CSDocument2 pagesCapacitor Disk Ceramic Blue Safety CS Series E4b3 - CSQuasar105No ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesMarcius RodriguesNo ratings yet

- Chapter-I Literature Survey: Department of EceDocument25 pagesChapter-I Literature Survey: Department of EceAnusha RudrarapuNo ratings yet

- MLCC - Tantalum Chip Substitution Common Footprints: © 2018 AVX ConfidentialDocument9 pagesMLCC - Tantalum Chip Substitution Common Footprints: © 2018 AVX ConfidentialrNo ratings yet

- Locker SystemDocument31 pagesLocker SystemAyush SinghNo ratings yet

- C2 - Condensatoare CeramiceDocument8 pagesC2 - Condensatoare CeramiceSneezy DwarfNo ratings yet

- Bill of Material: Designator ValueDocument12 pagesBill of Material: Designator ValueThanga rajNo ratings yet

- JBL Authentics l16Document40 pagesJBL Authentics l16doctorpc11112222No ratings yet

- DatasheetDocument12 pagesDatasheetWAN MOZESNo ratings yet

- Circuit Drawing of Stepper Motor ControllerDocument24 pagesCircuit Drawing of Stepper Motor Controlleranon-814167100% (5)

- Ceramic CapDocument155 pagesCeramic Capcamiloc320No ratings yet

- Datasheet Mosfet Driver ADP3110A Dual Bootstrapped, 12 V MOSFETDocument12 pagesDatasheet Mosfet Driver ADP3110A Dual Bootstrapped, 12 V MOSFETdouglasNo ratings yet