Professional Documents

Culture Documents

DLD Workbook

DLD Workbook

Uploaded by

Sudhanshu Ranjan0 ratings0% found this document useful (0 votes)

107 views32 pagesOriginal Title

Dld workbook

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

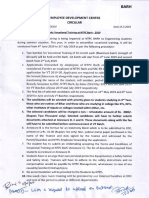

107 views32 pagesDLD Workbook

DLD Workbook

Uploaded by

Sudhanshu RanjanCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 32

2021

workbook Digital Logic

_ za

Digital Logic

Sa

1. Number Systems and Binary Codes 44

| 2. Boolean Algebra, Logic Gates and K-Maps 48

3. Combinational Logic Circuits 56

4, Sequential CircUits smn 63

3000

© copyright Sujet mate to ADE EASY Pubicatons, New Dh No part tisteckray reproduced outed nan orm aha he itor gems.

Chapter-1 : Number Systems and Binary Codes

Conversion decimal number to any radix

number, any radix number to decimal number

(1) and 's complements - their requirements

Signed binary number representation sign

magnitude, signed 1's and signal2’s complement

range ol number in various representation

BCD codes: Weighted and non-weighted codes,

self complementary codes, reflective codes

Code conversion

+ BCD to Excess-3

+ Excess-3 to BCD

+ Binary to gray

+ Graytobinary

+ Any weighted BCD to natural BCD codes

Chapter-2 : Boolean Algebra, Logic Gates and

| www.madeeasypublications.org

K-Maps

Boolean Algebra:

+ Boolean basic operators

* Basic logic gates

+ Boolean algebra

= Sum of product and Product of sum form

‘rom Truth table

+ Minterms and Maxterms

* Literal and variables

+ Derived operators

+ Simplification of boolean functions and

equations using properties

+ Universal logie gate

+ Simplification and equality properties on

EX-OR and EX-NOR

K-Map:

+ Definition of irredundant and minimal

expression

MADE EASY

Digital Logic

Description Sheet

= Necessity of K-map

+ K-map on 2, 3 and 4 variables

* Definition of implicants, prime implicants ana

essential prime implicants

+ Finding prime implicants and essential prime

implicants

* Finding minimal expressions using k-map

SOP and POS

* Don't care combinations definition and

problems.

+ Five variable k-map

Chapter-3 : Combinational Logic Circuits

* Hall-adder, Fullkadder, Half subtractor, Full

subtractor

+ Binary adder

= Serial adder

= Ripple carry adder

= Carry look ahead adder

= Binary subtractor: Problems with 1's and 2s

complement, advantage of 2's complement

= 4-bit binary adder and binary subtractor

circuit

= BCD to Excess-3 and Excess-3 to BCD

circuit

= BCD adder and subtractor circuit design

* Binary comparator circuit

Multiplexer:

= MUX circuit with logic gates - Active low and

Active high enable

= Different applications of MUX's

= Realizing functions using MUX

= Analysis of MUX problems

Decoder/DE-MUX circuits and their applications

Eneader and priority encoders

© Copyright

MADE EASY

Chapter-4 : Sequential Circuits

© Flip-Flops:

Binary latch and S-R and J-K flip-flop circuits

with NAND gates : Truth table, characteristic

table, excitation table, affect of clear and

preset input

Race around condition and its solution

Master slave J-K flip-flop,

Dand Tflip-fop

State diagram of flip-flop

General procedure for converting one tlip-

flop to another fip-lop

Analysis of flip-flap circuits for finding truth

table, characteristic equation, excitation

table

MADE EASY

Workbook 43

Registers

+ SISO, SIPO, PISO and PIPO operations and

timing diagrams

= Universal shift registers

= Application of shift registers

Asynchronous counter

+ Difference botween asynehronous.and ripple

counter

= p-bit ripple up/down counter with timing

diagram

= MOD-N counter: Ripple counter design using

clear and preset terminals

‘Synchronous counter:

Design pracedure for simple sequence and

regular sequence

= Analysis of synchronous counter state

ciagram

wewwmadeeasypublications.org

Number Systems

and Binary Codes

wi Multiple Choice Questions | |

Q.1. Whatare the values of Fi, and ff, respectively,

nthe expression (235) q; = (565) 9 = (1065)?

(a) 8,16 (b) 16,8

{c) 6,16 (@) 12,6

[ESE-2004 (EE)] | 2

Q.2 (2)3+ B= (5

(a4 () 11

{c) None of these (a) Not possible z

@.3 Convert the octal number 127543 into the |

hexadecimal form. a

(a) AF63 (b) AF53

(c) AFDS {d) BCDS

Q4 if(itxty)y= nthe values x and y |

ae d

(a) 3and1 (b) Sand? r

(©) 7and5 (d) 1 ands f

[ESE-2012) |"

Q5 W2BMeauvat 1 2os what is the |2

value of y? 2

fa) 104 (o) 1001 3

(ce) 102 {d) 1.02

[ESE-2005] | z

Q.6 How many 1's are present in the binary

representation of

(4x 4096) + (9x 256) +(7 x 16)+5?

fa) 8 (b) 9

© 10 (a 1 ;

[ESE-2004]

www.madeeasypublications.org

ees

a7

The binary equivalent of hexadecimal number

4F20.

(@) 0101 11140010 1100

(b) 0100 11110070 1100

() 010011100010 1101

(@) 010011170010 1101 (ESE-2002]

In signed magnitude representation, th

equivalent of 22,5625 is (the bit before comma

represents the sign)

binary

(@) 0,10110.1011 (b) 0, 10110.1001

(©) 1,10101.1001 (¢) 1, 10110.1001

{ESE-2002]

The 2's complement representation of -17 is

(@) 101110 (bo) 101111

() 111110 (@) 110001

[GATE-2001]

Q.10 The 2's complement representation (-539) pi"

hexadecimal

fa) ABE

(c) DES

() DBC.

[GATE-2001}

Q.11 F's compler

(@) £3904 (8) D403

{o) D402 (a) C408 [ESE-2001]

Q.12 (FE35),,.XOR(CB15),, is equal to

(2) (B320),5 ) (FFR5)g

) (FBO) (0) (3520),,

{ESE-2000]

Q.13 11001, 1001 and 111001 correspond tothe 25

complement representation af which one of the

following sets of number?

(@) 25,9 and 57 respectively

(b} -6, -6 and -6 respectively

(©) -7,-7 and -7 respectively

(0) -25, -@ and -87 respectively

MADE EASY

[GATE-2004]

© Copyright

MADE EASY

Q.14 Which of the following represents 'E3,,"?

(2) (ICE) ys + (A2)5

(0) (1BC),,~(DE) 5

(©) (2BC),- (IDE),

(d) (200),¢-11D),

(ESE-2002)

Q.15 Which of the following subtraction operations

result in F NOT > AND > OR

(©) ()< NOT < AND NOT >OR

a2

What logic epresented by the circuit

shown below?

Qow

L_,_ Sa

(a) AND (b) NAND

(c) NOR (d) EQUIVALENCE

@)

{) Z=0

[GATE-2009}

www.madeeasypublications.org

2

:

:

Tinie foes snmp AGEL

i

as

as

ag

MADE EASY

The Boolean expression

ABCD + ABCD + ABCD + ABCD

‘5 equivalent to

aA () AC

(@) ABC @1 [ESE-2008)

Hvand yare Boolean variables, which one of

the following is the equivalent of x @ y@ xy?

(@) x+¥ () x+y

@o 1

[ESE-2004 (EE)]

The Boolean expression ¥Z+XY¥+XZ is

logically equivalentto

(@ yz+x

(©) XVZ+RVZ+XV2+

~ =

@A+B+C — (b) A¥BC

(©) A+BC (d) A+B+E

Hf the output of a logic gate is "1! when all its

inputs are at logic ‘0’, the gate is either

© Copyright

MADE EASY

Qo

att

a2

a.13

a1

Q.15

© Copyright

(a) ANAND or ANOR

(6) An ANDor an EX-NOR

(©) An ORor an NAND

(0) AnEX-OR oan EX-NOR

[ESE-2014]

Consider the statement below:

1. Ifthe output wavetorm from an OR gate is

the same as the waveform at one of its

inputs, the other input is being held

permanently LOW.

2. Ifthe output waveform from an OR gate is

always HIGH, one of its input is being held

permanently HIGH

The statement/statements, which is/or always | =

true 2

(@) Both tand2 —(b) Only 1 3

(c) Only2 (d) None of these g

Consider: 3

Y¥=A@A®ADADABAGABABA EYE

is equivalent io |=

fa) 10RA (0) AEX ORO 2

(c) 1NORA {d) AAND A g

The function z

= (ABC + 280+ ABC + ABC)@ A can be |®

written as S

(a) B@C (&) A@B@A 5

fo) A (0) None of these

[(4+ABKA+ AB)] + [(CO +) +10 @ 0)] =

f@) &

0

(b) A 3

@1

Ifa variable is having Ex-OR operation itself 'r

number of times, then the result is

(a) Complement of variable if ‘nis even

(©) Uncomplement of variable it 'n! is even.

(c) Complement of the variable if ‘n'is odd.

(d) Uncomplement of the variable if‘n'is od.

Black box inverts the phase of input V when

contro|’4'is 1 and lets it pass through uninverted

when control ‘A’ is 0 then circuit is

Workbook 49

v— |

LT LJ) enttor oan

Contra a —.|

(@) XNORgate —(b) KOR gate

(©) NANDgate — (d) NOR gate

Q.16 All the logic gates in the circuit shown below

have finite propagation delay, The circuit can

be used as a clock generator, if

Le

po

—>

x

fa) 0 (b) X= 1

{e) X=Oor1 (a) X=Y

[GATE-IN : 2006]

Q.17 For the logie circuit shown in figure below, the

output is a to

@ WB+BC41B+C (©) AB+BC

(©) A+B+C (2) All of these

Q.18 Whatis the boolean expression for the output

of the combinational logic circuit of NOR gates

given below?

() P40

() P+O+R

IGATE-2010]

www.madeeasypublications.org

50 Computer Science & IT @ Digital Logic MADE ERSY

Q.19 Statement (I): XOR gate is not a universal gate 1 — rc

Statement (I): Ibis not possible to realize any @ o—+ + + 1+—

Boolean function using XOR gates only. bh & f

{a} Both Statement (1) and Statement (II) aro — 7 =

Bah Siena) Caeeeeresee| qa

correct explanation of Statement (I) bof ob &

(©) Both Statement (1) and Statement ll} are

individually true but Statement (I!) is not the | 2

correct explanation of Statement ().

(©) Statement (I) is true but Staternent (I) is

[GATE-2002]

Q.22 The Boolean expression AC + BC is ecuivalent

to

false. & (a) AC+B0+AC

tetement (I) is false but Statement (ll) is | - a.

(9 Stee (is fase but Statement) is | ey BC+ Ac+BO+ 7B

[ESE-2012] (c) AC+BC+BC+ ABC

(d) ABC+ABC+ ABC + ABC

@.20 In the circuit shown in the figure, if C= 0, the |

the circuit shown in the figure. i the TGATE-EC : 2004)

expression for Yis

>

>

L

Q.23 The switching expression corresponding 10

(A,B, C, 2) = 30, 4,5,9, 11, 12)i8

(@) BCD +ACD+ ABD

{b) ABC’ + ACD + B'C’D

(c} AC + ABC + ACD

(@) A'BD+ ACD + BCD

ean

|

1p, i>:

—p—P

<7

f@ Y=AB+AB (b) Y=A+8

{) Y=A+B (o) Y= AB

[GATE-2014]

[ISRO-2009]

Q.24 What is the minimized logic expression

corresponding to the given Karnaugh Map?

@.21 The gates @, and G, in the figure have

propagation delays of 10 nsec and 20nsoc

respectively. If the input ¥, makes an abrupt

change trom logic 010 1 at time f= fy, then the

output waveform Yyis

(ty = + 10s, t= f+ 20ns, t, = % + 30s)

@) xz

(b) Way + Wye net way

() Wa + Wye s Wy 2 Wey

() xz+ yt Way way ye

{ESE-2005]

@.25 The tunction (A, 8, 6, D) = 26, 7,9, 11,13, 15)

is independent of varianle(s)

@ 8 ) c

(©) Aandc @D

{DRDO-2009]

wonnsmadeeasypublications.org MADE EASY © Copyright

sae

Q.26 An odd funetion involving three Boolean variables

is

(@ £(1,3,5.7) () Z(G, 2, 4,6)

(©) £0,247) (a) £(0,3,5,6)

[DRDO-2009]

Q.27 Themin term of (P,Q, R) = PO+ OR’ + PAT is

(a) m, +m, +m,+m,

(0) m +m, +m, +m,

() my +m, +m, +m,

@) m,+m,4+m, +m,

[GATE-2010}

Q.28 The Boolean funstions can be expressed in

canonical SOP (sum of products) and POS

{product of sums} form, For the functions,

Y= A+BC, which are such two forms

(@) Y=2(1, 2,6, 7) and ¥= (0, 2, 4)

©) (1,4,5,6, Zand Y= 11(0, 2,3)

(©) Y=2(1,2,5,6, and ¥=1(0, 1,3)

© Y=2(1,2,4,5,6, Nand Y=11(0,2,3,4) |3

IGATE-2008]

Q.29 Tho SOP (sum of products) form of a Boolean

function is (0, 1,3, 7, 11), where inputs are A,

B.C, D(Ais MSB, and Dis LSB). The equivalent

minimized expression of the function is

(a) B+O(A+C)(A+ BC+ D)

©) B+ OA OA HC+D)

(©) B+ OV(Ar A+ (C+D)

(d) (B+ Q(A+B)(A+B(C+D)

[GATE-2014]

Q.30 What is the minimum number of NAND gates

saan yaa

peanpavd

way hae

required to implement A+ AB+BC(A+C)?

fa) 0 (b) 2

(o) 4 (a) 6

[GATE-2004]

Linked Answer Questions (31 and 32):

The following Karnaugh map represents a function F

ryt

Won or 1 10 z

+ z

ofaq [sto 5S

ifefel ato

© Copyright

MADE EASY

Workbook 51

Q.31 A minimized form of the tunction F

@) FEKY+YZ (0) FaX-V+¥Z

(©) F=X¥+¥Z (a) F=X¥+¥2

[GATE-2010]

Q.32 Which af the following circuits is a realization of

the above function F?

[GATE-2010]

Q.33 Which are the essential prime implicants of the

following Boolean function?

fla, b, o)= 0+ ac’ + Be:

(@ d¢candac {) acandb'c

(© fonly {d) a’ and be"

[GATE-2004]

Q.34 Consider the Boolean function:

Flix, YZ) = Wy + x¥ + ye Way +24 EP 2,

Which one of the following is the complete set

oj essential prime implicants?

(@) WyaZFZ (D) wm yaz

©) YRFZ (@) yazFz

Q.35 The output of the combinational circuit given

below is,

A

wwwmadeeasypublications.org

52 Computer Science & IT @ Digital Logic MADE ERSY

(@ A+B+C — (b) AB+O) Q.41 The minimum number of 2 input NOR gates

(@ B(C+A — @) CA+8) required to realize the Boolean function

[GATE-2016] | ° {A,B 0)= ABC

Q.36 The minimum number af 2-input NAND gates

required to implement a 2-input XOR gate is 0.48 Consider the function

t= ABC+BCD)+ BD(A+C)+ ABC

@4 ©) 5 KBC + BCD

6 a7 2 d= ABCD + CD)+ ACD

[GATE-2016) | = Where 'f represents Boolean function and ‘a

Q.37 Consider the Boolean operator # with the | represents con'trara condiion.

following properties 5 Then simplified Boolean expression 'f' is

R reduced to __ literals,

x#Oexx812 80820 and #5

Thon x# yis equivalent to

1S

Q.43 The number of prime-implicants for the given

function (A, BC) =¥,,(0.2,5,6, 79's

(a) x+y {b) XY +a

@ xyty (@® wtTy Q.44 The number of essential prime-implicantsin the

(GATE-2016] given function (wx, ¥. 2) = £ (0, 2,6, 7, 8,9,

Q.38 The minimized function f obtained from the 18. ISR

K-map given below is Q.45 A cyclic prime implicant Boolean function is

« ea having how many minimal forms?

|_|" : Q.46 The function KA, B,C, D) =, (3.4.5.7. 9, 13,

[a 1 14, 15) is realised with following digital logic

a block circuit, Each digital logic block is

t 7 7 implemented with minimum number of 2 input

EL l Ld NAND gates, The number of NAND gates

(a) CE’ + BCE + BCDE required are

(b) BC'E’ + A’'BCE + ABCD'E + BCE ee BD

(@) CE + ABCD + BCDE i Li

(d) BCE + NBCE + ABCDE + BCE a | *,

[DRDO-2008} | "Be Pe eet

Questions

Numerical Data Type

Q.39 Consider the logical functions given below:

F(A, B,C) = 312, 3, 4)

£(A, B,C) = nO, 1, 3,6, 7)

f

‘=D-

f

If Fis logic zero, then maximum number of

possible minterms in funetion f, are

Ti. Ininputto digital circuit consisting of a cascade

of 20 EXOR gates is xX’ then output 'Y’ is:

Q.40 Minimum number of 2 input NAND gates fa) 0 ©) 1

required to implement the logic function xX (d) x

FaA+B+C+ Dare _# [Ans: (b)]

wwwmadeeasypublications.org MADE EAS © Copyright

eee

MADE EASY

T2.

73.

14.

Define the connective * for the Boolean variables

X and ¥ as X *¥ = XY + X'Y" Let Z = K * ¥.

Consider the following expressions P, Q and R.

PiX=YeZ Q: Y=X*Z

RiX#YaZ=4

Which of the following is TRUE?

(a) Only P and Q are valid

(b) Only Q and Rare valid

(©) Only Pand R are valid

(0) All, Q, Rare valid

IGATE-2007, Ans: (d)]

Which one af the following figures represents

the coincidence logic?

@ a—

a

Ge

°

[ESE-2000, Ans: (a)]

Ii the waveforms A, 8, Cshown in figure below

are applied to the Ex-NOR gates. Find the

frequency of output.

[Ans: 125 kHz]

| ©Copyright

Taco

Sea save

7 99 Fe 00

15.

17.

Workbook

53

Des stevdt

4—pe—

f(s, Y= IMO, 1,35),

foley 2 = Zm(4, Sand

As, ¥, 2) = Em(1, 4,9)

Thon f (x, ¥, 28

(a) Em, 4,5)

(b) TIM (1, 4, 5)

(©) EMU, 4,5) + o2,6,7)

(0) TIM(A, 4, 5).4(2, 6,7)

[Ans: (c)]

Determine the function f,if ,=wxz+yZ+x2

and the overall transmission function of the given

logic circuit is tobe Aw, x, y, 2)=Em1.3, 5.6,

9, 12, 13)

i _.

& ‘e. Fw x2)

spo!

Lm (0, 2, 4, 7, 8, 10, 11, 14, 15)

Em (6.9, 12)

Sm (0,2,4,7,8,10,11,14,15) +6, 9,12)

(0) f= EG, 9, 12) + HO, 2, 4, 7,8, 10, 11

14, 15)

[Ans: (c)]

The average propagation delay of each NOR.

gate shown below Is 10 ns. The frequency of

the output signal Vy is, MHz

SDD DDD,

[Ans: 10]

A Boolean function fof two variables x and yis

defined as follows:

AQ, 0) = 0, 1) = KA, 1)= 1: (1, 0)=0

Assuming complements of x and y are not

available, a minimum cost solution for realizing

www.madeeasypublications.org |

54

19.

T10.

rm

112.

| www.madeeasypublications.org

Computer Science & IT * Digital Logic

fusing only 2-input NOR gates and 2-Input OR,

gates (each having unit cost) would have a total | ¢

cost of

(@) t unit

(c) unit

(b) Aunit

(a) unit

[GATE-2004, Ans: (d)]

oe

A T gate is having the output 14, 8) = AB

Which of the following is/are have about T gate.

{@) {This functionally complete

{b) (7, t}is functionally complete

(c) {7,0} is functionally complete

(d) Both (a) and (b)

(Ans: (b)]

The simplification of Boalean expressions.

avab+abe+

fa) a+b+e+

(c) atbece

is

(b) a+0+0+

(d) a+ b+o+

[Ans: (d)]

The following labelled 1, 2, 8and 4 in the network

shown in the figure is redundant

Feu 0a

[ESE-1999, Ans: (3)]

For the box shown the output Dis true if and

only if a majority of the inputs are true.

We :

Input a Ir D output 3

om Z

The Boolean function for the output is

(a) D= ABC + ABC+ ABC

(b) D= ABC+ ABC + ABC + ABC

(c) D=ABC+AB+ AC+ BC

{d) D= ABC+ ABC + ABC+ ABC

[ESE-2013, Ans: (b)]

2

MADE EASY

MADE ERSY

113, Whatis the Boolean expression for the truth table

shown below?

Alolojojol [if 14]

Blofo[t{t]ojoj1|4

fejo[t[oj1[o[1[o]4

[Ffofofolt {ofa} t[o}

fa) BA+C)(A+0)

(0) BAr CALC)

(©) BA+C)(AtC)

(@) BIA+C)(A+C)

[GATE-2006, Ans: (a)]

14, A bank has 3 locks with 1 key for each lock

Each keyis owned by a different person. In order

toopen the vault atleast two people must insert

their keys into the assigned looks, All the keys

arenotinearted atthe same time. If the system

is to be designed with only two input NAND

gates, then find the number of NAND gates

required

[Ans: 6]

115. Alogi circuit implements the following Boolean

function:

F(A BC,D)= AC+ACD

tis found thatin the circuit the input combination

A= can never occur. Find a simpler

‘expressian for F

[ESE-2014, Ans: AC+AC= A®C]

T16. The standard sum of products of the function

f= A+ BCis expressed as:

(@ Em(1, 4.5.6.7) + 2,3)

(0) Em(1, 4, 5,6, 7)

fo) Lm(O, 2,3) + alt, 4.5.6.7)

(a) Tmt, 4,5,6.7)

[DRDO-2008, Ans: (b)]

717. The black box in the below figure consists of a

minimum complexity circuit that uses only AND

OR and NOT gates. The function flx, y, 2)= 1

whenever x, yare different and 0 otherwise. in

© Copyright |

MADE EASY Workbook 55

addition the 3 inputs x, y, 2 are never all the | | T20. A Boolean function AA, B,C, Dyis given in the

same value. Which one of the folowing equations map shown below, Identify how many minimum

leads to the correct design for the minimum number of 2 input NAND gates required to

complexity circuit? realize the function?

. Ac

Bd\ 00 1 10 11

y BLACK BOX F642) lala tee

ofafitata

(a) vy #ay’ (be) x+y¥z vol [4 7

(©) xyz tx¥z aye y¥za7 wit 4

[GATE-2007, Ans: (a)] | = Ans: (2)]

T18, Lets; @ xy 8. y= 0 where x... 2,010 | | TT Following ft ei ofa utc

Boolean variables, and @ is the XOR operator. | © {Wve variables F Q,R, Stend.X The minimum

Which onavat the telauna'mlstiaiwape bale sum-of product (SOP) expression for the function

TRUE? a &

{@) sxx = 0 8] gghP 00 or 1 0 peo 1 11 10

{E) aap Page z m0 000 00110

© HO%m = ¥ Oxy 3 on 1 0 oF oo 0 0 0

@) x, +2 + 45,20 $ nioo01 nooao

z 0 0 0 10 10

[Gate-2016, Ans: (c)] | 5 eR at

T19, Consider the following circuit composed of XR (@) PQSK+POSX +QRSX+QRSX

gates and non-inverting buffers. i (o) O8%+ 08x

4p : (0) Q8X+Q5X

Betee Beds ie () QS+05

The non-inverting buffers have delays 8, = 2 ns | = [GATE-2016, Ans: (b)]

and 6, = 41ns as shownin the figure. Both XOR

gates and all wites have zero delay. Assume: ome

that ll gate inputs, outputs and wires are stable

atlogiclevelO al time 0, Ifthe folowing waveform

is applied at input A, now many transition(s)

(change of logic levels) occur(s) at 8 during the

interval trom 0 to 10 ns

— Logit

at —teaio

Tid 12.3.4 5 6 7 BO 10 Tre

fa) 1 (b) 2

fe) 3 (a) 4

[GATE-2003, Ans: (4)]

©Copyright MADE EASY swww.madeeasypublications.org |

Combinational Logic Circuits

©] Q.3 xand yare two n-bitnumbers. These numbers

are added by a n-bit carry-lookahed adder,

\8] which uses & logic-levels. If the average gate

delay of carry-lookahead adder is o then what

will be the maximum delay of carry-lookahead

adder circuit?

[Vf Muttipte Choice Questions

Q1. The circuit shown in the figure converts

E @ (b) kd

8] () aka (6) na

21@4 Ina look-ahead carry generator, the cary

generate function G, and the carry propagale

function P, tor inputs, A, and 8, are given by

P= A @B and G=AB,

The expressions for the sum bit S, and carry bt

C,,, , ofthe look-ahead cary adder are given by

2 $.=P.@C,and G,, = G+ PO, where Cis

the input carry.

Consider a two-level logic implementation of the

look-ahead carry generator. Assume that all P,

and G,are available for the camry generator circuit

and that the AND and OR gates can have any

number of inputs. The number of AND gates

and OR gates needed to implement the look:

ahead carry generator for a 4-bit adder with $,

S,, $, S,and C, as its outputs are respectively

(@) 6.3 (©) 10,4

O64 (a) 10,5

(a) BCD to binary code

(0) Binary to excess -3 code

(0) Excess - 3 10 Gray code

(d) Gray to Binary code

Q2 Identify the correct statement with respect to

following circuit? Numbers are represented in

signed magnitude format

lerteeter!

YY

Japan | a

[aes 7],

z(btop)

QS Consider two4-bit numbers A= A, AyA,A and

B=8,8,8,B, and the expression

x, =AB +4 G tori=0, 1.2.3. Theexpression

ABs +134 Bb + xy + xaxoms Ai

evaluates to 1 if

(@) Iroutputs x + y (b) Itoutputs yx

{6} loutputsx +1 (d) outputs y +1

¢ se

( www.madeeasypublications.org MADE EASY © Copyright

MADE EASY Workbook 57

@ A=8 (b) Aee Q.9. Thecircuit shown below does not represent

© A>B () A— | 2 SS |

ae i “TTI

Tes fs (@ 2(3,8,9, 10)

. 4s 3 (b) £(3,8, 10, 14)

SS 3 {e) 110, 1,2, 4, 5,6, 7, 11, 12, 13, 15)

5 (d) 1100, 1,2, 4, 5,6, 7, 10, 12, 13, 18)

b Z

Q.11 Consider the multiplexer with Xand Yas data

inputs and Zas control input. Z= O selects input

Xand Z= 1 selects input Y. What are the

connections required to realize the 2-variable

Boolean function f= T+ R, without using any

additional hardware?

@ orc me

{) 1.0.6.6, @C1e

Q.8 The Boolean expression for the output fof the

multiplexer shown below is

R (a) Rtox, 110, TioZ

R t {b) TtoX,Rto ¥, TtoZ

R © Ttox,Rto ¥,0toZ

& {d) RtoX,0to ¥, TtoZ

| 5 [ESE-2009]

_ ee 2 | @.12 Suppose only one multiolexer and one inverter

() POQOR b) PEQER 8 are allowed to be used to implement any

(©) P+O+R (@) PxOVR ? Boolean function of n variables. What is the

[GATE-2010} minimum size of the multiplexer needed?

“ ecopyright MADE EASY wwwmadeeasypublicationsorg

58

Q.13 Consider the following statements

(a) 1 2end4 (@) 2.8.andd :

{c) 1,3and4 (@) 1, 2and3 =

[ESE-2000] |

Q.14 An 810-1 multiplexer is used to implement a |=

logical function ¥ as shown in the figure. The | =

output 3

ot, a

on

oy,

oft

ot, J

on

1—e

ott ss, Is

Q.15 Inthe circuit shown, Wand Yare MSBs of the

control inputs. The output is given by

‘wivwmadeeasypublications.org

Computer Science & IT @ Digital Logic

(@) 2" line to 1 line

(b) 2" "fine to 1 line

(©) 2°" ine to 4 fine

(a) 2°? line to 1 tine

Bult

[GATE-2007]

Amuttiplexer

1, Selects one of the several inputs and

transmits it to a single output.

2. Routes the data from a single input to one

of many output

3. Converts parallel data into serial data

4. Isacombinational circuit.

Which of these statements are correct?

Tava a0"

A Bc

(a) Y=ABC+ATD (b) Y= ABC+ ABD

(0) Y= ABC+ACD (a) Y= ABD+ ABC

[GATE-2014]

16

Quiz

aia

MADE EASY

MADE EASY

(a) F=WX+WX+¥2

(0) F=WK+WK+YZ

fc) FWY +TIXY

(d) F=(W+XV¥Z

The Boolean function ‘f implemented as shown

in the figure using two input multiplexers is

c—fo o—fo ]

axa ) 2x1 |

MUX MUX

—F

I L____Te

(a) ABC+ABC (b) ABC+ ABC

(©) ABC+ABC (oc) ABC+ ABC

The minimum number of 2 x 1 multiplexers

required (o implement a haif adder circuit are

[when only basic inputs are available

compliments are not available]

(a 4 () 2

3 @ 5

4:1 multiplexer is to be used for generating

the output camry ofa full adder. Aand Bare the

bits to be acded while C,, is the input carry and

C,,, (8 the output carry. Aand Bare to be used

as the select bits with A being the most

significant select bit

i |

OT) aes t— Gout

y |

ss 5)

A i"

Which one of the following statements correctly

describes the choice of signals to be connected

tothe inputs Jy J, , and J, so that the output is

G,

(@) 4)= 0,1, = Gy p= C, and l,=1

(0) E11, = Gy I= Cand ly =1

(©) y= Cy. = O.p= Vand l,=C

Dh Tend f,

[GATE-2016)

© Copyright

MADE EASY

Q.19 Alogic circuit consist of wo 2 x4 decoders as

shown in the figure. The output of decoder are

as follow:

5

z A =

° é

twhen Ay = 1, A, =0 is

when Ay= 0,4, = 1 é

twhen 4,=4,A;=1

The value of f(x, y, 2) is

fa} 0 (b) z

© Zz (pt

Q.20 The building block shown in figure is a active

High ouput decoder

a ae

ot, BOM :

a ;

“re E> :

Lae a

The output Xis

{@) AB+BC+CA (bd) A+ B +O

(c) ABC (d) Noneof these

Q.21 The functionality implemented by the circult

belowis,

pp

es

ak———_—

T

&

[

D> is atistate puter |

Q.22

Q.23

Workbook 59

{a} 210-1 multiplexer

(0) 410-1 multiplexer

(©) 7-10-1 multiplexer

(A) 610-1 multiplexer

IGATE-2016]

Consider the two cascaded 2-0-1 multiplexers

as shown in the figure

t t

The minimal sum of products form of the output

xis

fa) PQ+PQR (b) PQ+OR

() PQ+PQR (d) QR+PQR

[GATE-2016]

Who two 8-bit numbers A, ... Ay and 8, .... B,

in 28 complement representation (with A,and

By as the leas! significant bits) are added using

a tipple-carry adder, the sum bits obtained

are S, ... Sand the carry bits are C, ... Gy. An

overflow is said to have occurred if

(@) The carry bit C;is 1

(©) Allthe carry bits (C, ... G,) are 1

{e) (4-8-5 +A, -B,-S,)18 1

(@) (Ay S+Ay Be S)is 1

[GATE-2017]

Numerical Data Type

Q.24

25

Questions

‘Aone bit full adder takes 75 nsec to produce

sum and 50 nsec to produce carry. A4 bit paralic!

adder is designed using this type of full adder

The maximum rate af additions per second can

be provided by 4 bit parallel adder is A x 10°

additions/sec. The value of Ais__.

A person wants to design a 4 x 1 multiplexer

using only NAND gates. If NAND gates with any

number of inputs are available, then total number

of NAND gates reauired are _.

“© copyright MADE ERSY wwrwmadeeasypublications.org

ee

MADE ERSY

60 Computer Science & IT © Digital Logic

Q.26 The numberof 2-to-4-line decodes with enable (0) ajby + Bab, + Ba ayo, +B.aB.d, +

input are needed to construct a 410-16-line | 6 aoe ——

decoder are 2 a,b, + 3,a,B b+ Abad, by

[DRDO-2009] | = [GATE-2006, Ans: (a)]

Q.27 Minimum number of 2 x 1 multiplexers required || T4, A 4-bit carry lookahead adder, which adds two.

to realize the following function is = 4-bit numbers, is designed using AND, OR,

ABC) = ABC+ ABC 5 NOT, NAND, NOR gates only. Assuming that

(Assume that inputs are available only in true | = Oline huis AIS eNaEH Ein bolt conGlemnented

form ind ‘Boolean’ constants’ and 0 arel@ and uncomplemented forms and the delay of

sonable’ z each gate is | time unit, what is the overall

R propagation delay of the adder? Assume that

= the carry network has been implemented using

(a) 4 time units (0) 6 times units

11. The circuit shown below converts. (here @is XOR) See!) 12 times unis

[GATE-2004, Ans: (a))

4 i Fi 4 |F

| [3] 75. Consider an eight bit ripple-carry adder for

—__ S— pe a) |F ‘computing the sum of A and B, where A

A 5 and B are integers represented in 2's

2 complement form, If the decimal value of A

2 is one, the decimal value of Bthat leads to

% o co Om |e the longest latency for the sum to stabilize

(@) Binary to gray (b) Binary toExcess3 |= is

(c) Excess 3to gray (d) Grayto binary 2 [Gate-2016, Ans: (-1)]

ans: (d)] | =

& | 16... TwoHalf Adders are connected in cascade as

T2. A 1bitfull adder takes 20 ns to generate carry- | 2 shown in figure below. The output “S" and "C" are

‘ut bit and 40 ns for the sum bit, What is the | 2 ai ao

maximum rate of addition per second, when four mm, [_

1 bit full address are cascade? iS a Je

[ESE-2005, Ans: 107] | = (@ S=A@B C=AB

73. Given two 3-bit numbers 2,24, and 6,6,b, and | 4 O) SAGE &

the carry in, the function that represents the |2| «(©): S= A+B, C=0

ccarty generate function when these twonumbers | £ ) 8=48,6-0

are added is Ans: (c)]

@) a,b, + a)4,0, + a,2,8,0, + 4,a9b,0,|%| 17, A 4bitbinary adder is adding two BCD numbers

+ a,Dpb, + aasb.by + a,b,b,0, and producing the sum output S,5,5,5, along

(©) a,b, + a,0,b, + a8,0,D) + a,ajbsb, |= with the carry output G,, tis required to design

+4,a,0, + 2,40, + 24,0,0, 3 a checking circuit such that the checking circuit

(0) a +b, +(a,@6,) [a, +, +(a,@d) 8 output must be zero, whenever the binary adder

le A Dae RE Tey A AN ‘output is invalid BCD, the boolean expression

oF of checking circuit is

MADE EASY

www.madeeasypublications.org

© Copyright

(a) GBy+ CSS,

(0) 6) + 8,5, + 8,5,

©) (+B )(G+S+5)

(a) None of the above

[Ans: (b)]

TB, A 2-t0-1 digital multiplexer having a switching

delay of 1 usis connected as shown in the figure

The output of the multiplexer is tied to its own

select input S. The input which gets selected

when $= Ois tied to 1 and the input that gets

selected when $= 1 istied to 0. The output Yy

willbe

2t01 MUX

@o

On

{¢) Pulse train of frequency 0.5 MHz

(@) Pulse train of frequeney 1.0 MHz

[Ans: (c)]

19. For the given multiplexer, Yis equal to

a ae ae

(a) ACD+ ABC + AD

(b) ABC+ ACD + AD

(©) ABC+ ACB +A0

(d) ACD+ ABD +AD

[Ans: (a)]

10. Without any additional circuitry, an 8-1 MUX

can be used to obtain

© Copyright

Tajeu 198lar WEUAGDO

San

iaiens a

2

ig poshadides ee RBUNORS

ay ATS

TH

T12.

Workbook 61

(a) Some but not all Boolean functions of

3 variables

All functions of 3 variables but none of

variables

All functions of 3 variables and some but

rot all of 4 variables

All functions of 4 variables

IGATE-EC : 2003, Ans: (c)]

(b)

©

cc

For the circuit shown in the following figure, /,—25

are inputs to the 4 : 1 multiplexer. R(MSB) and

Sara control bits.

if

The output Z can be represented by

(@) PQ+POS+ ORS

(0) PO+PQR+POS

{e) PQR+POQR+PORS+ ORS

(@) PQR+PQRS+PORS+ ORS

[GATE-2008, Ans: (a)]

The Boolean funotion f(A, B, C) realisea by the

given 4: 1 MUX, is

2 asa

Mux

ABO)

—+0s,

Lot

A

HA, BQ) = AB+ BC

KA, B,C) = AB+ BC

fA, B,C) = AB+BC

f(A, B,C) = AB+ BE

fa)

(b)

©

[Ans: (a)]

‘wwamadeeasypublicationsorg |

el

ee

62 Computer Science &IT © Digital Logic MADE EASY

Statement for Linked Answer Question(T13andT14): | | 114, What are the minimum numbers of NOT gates

Two products are sold from a vending machine, which and 2-ingut OR gates required to design the

has two push buttons P, and P,.. When a button is logic of the driver for this 7-segment display?

pressed, the price of the corresponding product is {a) 3NOT and40OR (b) 2NOT and 4 OR

displayed in a 7-segment display. (6) 1NOTand3OR (d) 2NOTand 30R

If no buttons are pressed, ‘0’ is displayed, (Ans: (d)]

ignitying ‘Rs.

Sania 8 a T15. The number of 3-0-8 line decoders with an

\fonly Fis pressed, '2"is displayed, signitying enable input are needed to construct a 6-10-64

Eine line decoder without using any other logic gates

tonly P,is pressed, 'S'is displayed, signifying ae

Ass

both P, and P, are pressed, 'E’is displayed,

signifying ‘Error

The names of the segments in the 7-segment

display, and the glow of the display for 0’, ‘2

'S' and 'E' are shown below,

a

Consider

(@)_ push button pressedinot pressed in equivalent

tologic 1/0 respectively,

(2) asegment giowinginot glawing in the display

is equivalent o logic 1/0 respectively

[Ans: (9)]

T16. The logic function (A, B. C, D) implemented

by the circuit shown below is

J ASV AGUA A

aN Sn

(a) Biawec) (} DASO

(c) ASB) (0) KA2B)

[Ans: (b)]

TAT. Consider the logic circuit given below:

Bi

1x4 py 1

De

T13. |fsegments ato gare consideredas functions of

P. and P,, then which ofthe following is correct?

(@ g=F+P,d=c+0

(b) 9=F.+P,d=cre

© g=P+P.e MUX 0,

(d) g=P4+P,0=b+e of

[Ans: (b)] ©

Aa

The minimized expression for Fis

fa) C ib) by

oc d)

[Ans: (a)]

7

www.madeeasypublications.org MADE EASY © Copyright

Sequential Circuits

Multiple Choice Ques!

Q.1 The following binary values were applied to the

and Yinputs of the NAND latch shown in the

figure in the sequence indicated bolow:

X=0, ¥=1;:X=0, Y=;

The corresponding stable P, Q outputs will be

,Q=00r

P=0,Q=1

() P=1,0=0,P=0,02101P=0,0=1

P=0.Q=1

(©) P=1,0=0;P=1,0=1;P=1,Q=00r

P=0,Q=1

() Pat, Q=0;P=1,Q=1;P=1,0

[GATE-2007]

Q.2 Theoutput @, of av-K tip-fiop is 2er0. Itchanges

to 1 when a clack pulse is applied. The input J,

aK, are respectively (X represents don't care

condition):

fa) tand X (©) Oand x

(c) Xando (@) Xand 1

[ESE-2013]

Q.3. The input Aand clock applied tothe Dtlip-lop

are shown in igure below. The output Qis,

© Copyright

eS

TASHA SON

ed on PEN SH

MADE EASY

look |]

0.4 Infgue assume that = 1. Win clock

pulses beng gon, te subsequent sate of

Cibo

- 2

' ofp.

Clock |

2 5

—t

(@) 1,0,1,0,1,0,1

(b) 0,0, 1,0,0, 1,0

©) 11,011,014

() 0, 1,0,1,0, 1,0.

The circuit acts as

PP

ck a

(@) DFlip Flop

(©) Both Aand B

‘www.madeeasypublications.org

64 Computer Science & IT © Digital Logic

Q.6 A secuential circuit using D flip-flop and logic

gates is shown in figure where Xand Yare the

inputs and Zis the output. The circult is

— Publications

Q.8 To realize the given truth table from the circuit

shown in the figure, the input to J in terms of

Aand B would have to be

(@) S-RFF with inputs X= Rand ¥= $

(b) S-RFF with inputs X

(0) HK FF with inputs x=

(d) J-K FF with inputs x:

Q.7. The circuit realization of the combination logic

block shown in figure to obtain the following truth

fe 42 | Compratona jy a}-e

2 8 ge} —k al

2 rock —!

g Truth Table

cux z A[B [Onn

a ofo] a,

‘an & J |

ere |a Tole,

and Y= £ ;

: @ A 0) 8

Z (o) AB (a) AB

table willbe,

ALB One

ofo} a,

ofip4

1/0, Q,

a)

A0o—| Combinations} 7 o}—0

i logic 3

(a) aeo——[ p»—

>

idan aa eu yooa si jo ued oN

Gein 9 HaUATH Wie) ADB | PASIIN

_ MADE ERSY

Q.9_V'lip flop, whose Characteristic Table is given

below is to be implement using a J-K flip flop

a

0

0

1

1

=/e|=[el =|

fa) x

r (b)

lo) J=Y.K=X

() J=XKa¥

Q.10 The clock frequency applied to he digital circut

shown in figure below is 1 kHz. ifthe initial state

of the output @ of the flip-flop is ‘0’ then the

frequency of the output waveform Qin kHz is

xe a.

cue

Rg ;

(@) 0.25 {by 05

4 (ne

[GATE-2013]

ant

12

a3

1

ok

ai4

i

Match List-! with List-Il and select the correct,

answer using the codes given below the lists:

List-1

A. Shiftregister

B. Counter

C. Decoder

List-II

1, Frequency division

2. Addressing in memory chips

3. Serial to parallel data conversion

Codes:

ABC

3 21

(o) 1 2 2

213

@3 12

{EC : GATE-2004]

Latches constructed with NOR and NAND

gates tend to remain in the latched condition

‘due to which configuration feature?

(@) Asynchronous operation

(b) Low input voltage

(©) Gateimpedance

(¢) Cross coupling [ESE-2013]

itis set high is circuit given below then Q,, ,i8

—p-F ae

=

{@) complementary (b) Q,

(6) high (2) low

For the intial state of 000, the function performed

by the arrangement ofthe JK tip fopsinthe figure

{5 a}+s of 7]

(18d ON TOG MON SUOTBIanG ASVS TEWA 61 aREW yS8TaNE WUBUAGOD @)

‘anno Uo) KOR UIP

aaiseqanad

Workbook 5

(a) Shift Register (b) Mod-3counter

(©) Mod-6counter (d) Mod-2counter

[EC : GATE-1993]

Q.15 The shift register shown in the given figure is

initially loaded with the bit pattern 1010

Subsequently the shift register is clocked, and

with each clock pulse the pattern gets shifted

by one bit position to the right. With each shift,

the bit at the serial input is pushed to the left

most position (msb). After how many clock

pulses will the content of the shitt register

become 1010.again?

lock

aa “ToT ite

inpst

fa) 4 &) 5

(e) 6 @7

Q.16 Thenumber of unused states ina 4-bit Johnson

counter is

(@) 2 @) 4

(8 (a) 12

[ESE-2003]

Q.17 The figure below shows a 3-bit ripple counter,

with Q,asthe MSB. The flip-flop are rising-edge

triggered. The counting direction is

tea He

(@) always down

(0) alwaysup

(©) upor down depending on the initial state of

Q, only

(d) up or down depending on the initial states

of Q,, Q, and Q,

[GATE-IN: 2009]

‘Common Data for Questions (18 and 19):

A-counter is shown below:

Je

Computer Science & IT

66

Q.18 The counter shown is

(a) Mod-12 (b) Mod-9

{e) Mod-14 (d)_ None of these

Q.19 Frequency of output Q, for 1 MHz clock is

{a) 63.3 kHz (b) 88.3 kHe

(6) 73.3kHz (d} None of these

Q.20 In the modulo-6 ripple counter shown in the

figure, the outout of the 2-input gate is used to

clear the -K flip-flops,

1— a

© Ho ad

J lock

k K Kp! inoue

yf Rinpat

gate

The 2-input gate is

(@) ANAND gate

(} anOR gate

{b) aNOR gate

(a) an AND gate

[GATE-2004]

Q.21 Astate diagram of a logic which exhibits a delay

in the output is shown in the figure, where is

the do not care condition, and Qs the output

representing the state,

oxi, 10/1

nol ots 04

WA

“10

The logic gate represented by the state

diagram is

(a) XOR (b) OR

() AND (@) NAND. [GATE-2014]

Q.22 Consider the partial implementation of a 2-bit

counter using T flip-flops following the sequence

0-2--1-0, as shown below

To complete the circuit, the input X should be

| www.madeeasypublications.org

jaa Wen fuoIBOI Ara Aaa Sa

ipowcles 2@ AB 9008 SATO

Tope.

MADE ERSY

MADE EASY

(@) Q,"

(©) (2,60,

(b) O, + Q,

(d) QQ,

[GATE-2004]

Q.23 Two D-tiip flops, as shown below are to be

connected as a synchronous counter that goes

through the following Q, Q, sequence

00 +01 11 > 1000

The inputs D, and D, respectively should be

connected as

By

(a) O QandQ, Q(b) Ganda,

© GQ, and@,a, (a) QandQ,

[EC : GATE-2006)

@.24 Asynchronous counter using two J-K flip-flops

that goes through the sequence of states

Q,Q,=00-> 10-901 11-00. isrequired

To achieve this, the inputs to the flip flops are:

is a,

|

K, o

Clock a

(@) J = Q,, K, =0; =O, K,

tb) y= 1, Ky = 15 de

(0) f= Q K, = Bs

Qk

Qa,

(0) y=Q5, K,= QJ q

[GATE-2016]

Q.25 The next state table of a 2-bit saturating up

counter is given below.

a[al[a[@]

of ofof7!

ao} afar )o|

a fofa]a

af afar}

© Copyright

MADE EASY

The counter isbuil asa synchronous sequential

circuit using Tflip-tops. The expressions for 7,

and 7, are

@ T=0Q, — h= 0

(b) 1-00), p-A+Q

©) T=Q+Q, H=Q+Q

(@) T%=0Q, — h=Q+@

[GATE-2017]

Q.26 For the circuit shown, the counter state (,Q,)

follows the sequence

a

ro

Laat

oux—¢——_

(@) 00,01, 10, 11, 00

(b) 00,01, 10,00, 01

{c} 00, 01, 11, 00, 01

(@) 00, 10, 11,00, 10...

[GATE-2007]

Q.27 What are the counting states (2, @,) for the

counter shown in the figure below?

—

ee

(a) 01, 10, 11,00, 01

(©) 00, 11,01, 10, 00,

(b) 11, 10,00, 11, 10.

(d) 01, 10,00, 01, 10.

[EC GATE-2008]

Q.28 The output of Moore sequential machine is a

function of

(a) all present states of machine

(b) all inputs

(c) all combination of inputs and present state

{d) few combination of inputs and present state

| copyright

00 @

7 3a fw 980 5

MADE EASY

Workbook

67

Q.29 Synchronous counters eliminate the delay

problems encountered with asynchronous

(ripple) counter because the

{a) input clock pulses are applied only to the

first and the last stages

(6) input clock pulses are applied only to the

last stage

(©) input clock pulses are not used to activate

any of the counter stages

(@) input clock

simultaneously

pulses are applied

[ESE-2013]

Q.30 Following state diagram shows clocked

squential circuit,

Howimany minimum number of states the

sequential cireuit has?

as

os

©) 7

(4

Q.31 A 4 bit ripple counter and a 4 bit synchronous

counter are made using flip flops having @

propagation delay of 10ns each. Iftne worst case

delay in the ripple counter and the synchronous

counter be R and 5 respectively. then

(a) A=10ns, S=40ns

(b) R= 400s, $= 10ns

(c) Re 10ns, S=30ns

(d) R= 30ns, S=10ns

[GATE-2003]

Q.32 The state transition diagram for a finite state

machine with states A, 8 and C, and binary

inputs X, Yand Z, is shown in the figure

‘www.madeeasypublications.org

68

Which one of the following statements is

correct?

(@) Transitions trom State A are ambiguously

defined

(©) Transitions from State B are ambiguously

defined

(0) Transitions from State C are ambiquously

defined,

(2) All of the state transitions are defined

unambiguously,

[GATE-2016]

Q.38 For the circuit shown in the figure, the delay of

the bubbled NAND gate is 2ns and that of the

counter is assumed to be zero.

= ees

3-bit

‘Synchronous:

‘Counter

a

2, (uss)

= |

If the clock (Cik) frequency is 1 GHz, then the

{a) mod-Scounter (b) mod-6 counter

(c) mod-7 counter (d) mod-8 counter

[GATE-2016)

ck +t

Numerical Data Type

Questions :

A

Q.34 Three 4 bit shift registers are connected in |# 7

cascade as shown in figure below. Each register |” 11M %

is applied with a common clock pulse. cux

¢ MADE ERSY

Computer Science & IT © Digital Logic

SECON

(3 ASV SOHN OF

rou] S50 ‘SPO so |

Shit ‘Shit ‘Shit

iter] [“|Regisior2] “Resist 3

Clock.

A 4 bit data 1011 is applied to the shift

register 1 The minimum numberof clock pulses

required to get same input data at output with

same clock are,

Output

36

Five JK fip-fops are cascaded to form the circult

shown in Figure. Clock pulses at a frequency ot

‘1M are applied as shown. The frequency (in KH2)

of the waveform at Q, is

clea LLIN

[GATE-2014)

Q.36 A digital circuit is designed with three D-tlip

flops and an Ex-OR gate as shown in below

figure. Ifthe initial value of Q, Q, Q.,was 110

then the minimum number of clock pulses

required to get Q, Q, Qp as 011 is

Q.37 A certain J-K FF has t,., 128, The largest MOD

‘counter that can be constructed fram such FF's

and stil operate up to 10 MH? is

[ISRO]

Q.38 A counter circuit is shown is below figure

if the propagation delay of flip-flops and AND.

gate are 2 ns and 1 ns respectively, what is the

maximum clock rate possible to apply so that

counter will operate satisfactorily in MHz?

‘Common Data for Questions (39 and 40):

‘Mealy system produces a 1 output if the input has

been 0 for at least two consecutive clocks followed

immediately by two or more consecutive 1.

Q.39 The minimum number of states for this system

is

Q.40 The flip-flops required to implement this system

Q.41 In figure shown in below Q = A =

are

0. After

3 clock pulses Q, A and B are respectively

tf ap

2

cuKe ‘pple

— counter

TT

aoa 8

Try Yourself

1.

12,

| w Copyright

Infigure initially A= 1 and 8= 1, theinput Bis

now replaced by a sequence 10.1010...the

outputs Xand ¥ will be

“=

(@) Fixed at O and 1 respectively

(b) Fixed at 1 and 0, respectively

(©) X=1010...while Y= 1010

(d) X=1010... while ¥=0101

[Ans: (a)

Refer to the NAND and NOR latches shown in

the figure, The inputs (P,, P,) for both the latches

are first made (0, 1) and then atter a few second,

made (1, 1). The corresponding stable

outputs (Q,, Q,) are

aahdoo @

STEEL

aq feu y000 SIO WEG ON HBO WBN "RUORE

TTT il

Tenia ea

73.

14.

MADE EASY

Workbook

Py

(@) NAND:first(0, 1) then (0, 1) NOR: first (1, 0)

then (0, 0)

(b) NAND: first (1, 0) then (1, 0) NOR: first (1, 0)

then (0, 0)

(©) NAND: first (1, 0) then (1, 1) NOR first (0, 1)

then (0, 1)

(d) NAND: first (1, 0) then (1,0) NOR: first (0, 1)

then (0, 0)

[EC : GATE-2009, Ans: (b)]

‘An AB flip-flop is constructed from an SR flip-

flop as shown in figure. The expression for next

state O* is

AB+ AQ

AB+BQ

Both Aand B

None of the above

(a)

(o)

©

@

[Ans: (d)]

Anew flip-lop is having behaviour as described

below. It has two inputs Xand Yand when both

inputs are same and they are 1,1, the flip-flop

is going to set else fip-tlop resets. If both inputs

are different and they are 0, 1, flip-flop

complements itself otherwise itis going to retain

the last state, Which of the following expression

is the characteristic expression for the new flip

flop?

(@) xQ+¥O

©) xG+¥a

() xO+¥O

(a) None of these

[Ans: (a)]

70

15. For the circuit shown in the figure below, two

4-bit parallel-in-serial-out shift registers loaded

with the data shown are used to feed the data

to a full adder. Initially, all the flip-flops are in

the clear state. After applying two clock pulses,

the outputs of the full adder should be

benno

Shift Registers ore

Hofoys

ee

|_ermmie a

(a) S=0 C,=1 (b) S=0 C,=0

() $=1 G=1 @ S=1 G=0

[EC GATE-2006, Ans. (c)]

T6. Consider the flip-flop circuit diagram shown

below. Draw output waveform far the circuit,

wed m

L a

17. A4 bit right shift, shift register is shifting the

data to the right for every clock pulse The serial

input Dis derived by using Ex-OR gates as

| www.madeeasypublications.org

Computer Science & IT * Digital Logic

LOO

aera ABV AG

18

Ve DEON RONEN

19.

7051 99 Res 90

MADE EASY

shown in the figure. After three clock pulses the

content in the shift register is to be 1010 at

Q,0,0,,,whatwill be the initial contont of tha

register.

| @ @ 2 90

? a cit shift register

Clock |

(@) 1100 (b) 1010

(©) conn (@) 0101

[Ans: (c)]

The given figure shows a ripple counter using

positive edge triggered flip-flops.

If the present state of the counter is Q, Q,

011, then its next state (Q, Q, Q,) will be

[GATE-2008, Ans: (100)]

‘The mod-number of the asynchronous counter

T10,

m1

MADE EASY

shownin figure

bah 4|

our LR

[ans: (a)]

Consideramod-1000 ripple up counter. The duty

cycle for its MSB is %

Ans: (48.8)]

(a) 24

(0) 26

(b) 48

(d) 36

Consider the circuit in the diagram. The ©

operator represents Ex-OR, The D flip-flops ere

initialized to zeroes (cleared)

© Copyright

MADE EASY

112,

113.

114.

{ ©copyright

ei

(to ohfe o

al? la

ox | Lae}

The following data : 1001 10000 is supplied to

the “data” terminal in nine clock oycles. After

that the values of gp a) dy are

(a) 000 tb) 001

© 010 (a) 101

[GATE-2006, Ans: (c)]

How many pulses are needed to change the

contents of a 8-bit up-counter from 10101 100 to

(00100111 (right most bit is the LSB)?

[IT GATE-2005, Ans: (123)]

Ifa counter having 10 FF'sis initially at 0, what

count will it hold after 2060 pulses?

fa) 000.000 1100

(b) 900001 1100

(©) 090001 1000

(a) 900000 1110

[Ans: (a)]

The digital block in figure realized using two

positive edge triggered D flip-flop, Assume that

for t< b, Q)= Q

LILD 24 388 Ry

bh &

The circuit in the digital block is given by

115.

16.

MADE ERSY

Workbook 71

1—fo, af fa, @}—y

td) x —b b

a,

[Ans: (b)]

Consider the following state transition table with

two state variables A and B and the input

variable x and the output variable y

Present State | Input | Next State ‘Ouiput_|

aT ets talely

ope fete }e |

o ° 4 o 1] 0

of fe te trp 4

Ce

+o pe fete,

ope pa t+

Fo

ia be eft

If tho initial state is A = 0 and B = 0, what is the

minimum length ofan input string which will take

the machine to the state A= 1 and B= 1 with

output y = 1?

3 () 4

@s (6

[DRDO-2009, Ans: (b)]

Reduce the following state diagram and also

write the reduced state table.

[Ans: (5)]

‘yeww.madeeasypublications.org

72 | Computer Science & IT # Digital Logic MADE ERSY

T17. Consider the circuit given below: T18, The frequency of the pulse at z in the network

shown in figure is Hz

®

3 ane Ta aL Lifes,

4 2 (Ans: (5)

Moo 10 5

inp Up 2

(Clock —P> Counter

7a0yNo%

MSB and LSB of MOD 1Oripple up counter acts as

clockto4 bitripple down and up counter respective

Initially all he counter were cleared and output

of comparator was A = B. The clock pulse is

applied, Find the minimum number of clock

pulses required to make A = Bagain

[Ans: 17]

cides oq Feu ye0R 8

pe

Tasejued waiia Bi

MADE EASY

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- FINAL450Document45 pagesFINAL450Sudhanshu RanjanNo ratings yet

- An Approach Towards Detection of Indian PDFDocument4 pagesAn Approach Towards Detection of Indian PDFSudhanshu RanjanNo ratings yet

- Vehicle Number Plate Recognition SystemDocument4 pagesVehicle Number Plate Recognition SystemSudhanshu RanjanNo ratings yet

- Top 17 Linked List Interview Questions & AnswersDocument4 pagesTop 17 Linked List Interview Questions & AnswersSudhanshu RanjanNo ratings yet

- Sil Char NocDocument1 pageSil Char NocSudhanshu RanjanNo ratings yet

- Modified Number Plate Localization Algorithm and Its Implementation Using FPGADocument5 pagesModified Number Plate Localization Algorithm and Its Implementation Using FPGASudhanshu RanjanNo ratings yet

- Top 50 Data Structures Interview Questions & Answers: 1) What Is Data Structure?Document8 pagesTop 50 Data Structures Interview Questions & Answers: 1) What Is Data Structure?Sudhanshu RanjanNo ratings yet

- Academic Calendar 2018 19 PDFDocument1 pageAcademic Calendar 2018 19 PDFSudhanshu RanjanNo ratings yet

- Top 50 Oops Interview Questions & AnswersDocument8 pagesTop 50 Oops Interview Questions & AnswersSudhanshu RanjanNo ratings yet

- Voc 2019Document6 pagesVoc 2019Sudhanshu RanjanNo ratings yet