Professional Documents

Culture Documents

Using IIC To Read ADC Values On MC9S08QG8: Application Note

Uploaded by

Kawann CostaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Using IIC To Read ADC Values On MC9S08QG8: Application Note

Uploaded by

Kawann CostaCopyright:

Available Formats

Freescale Semiconductor AN3048

Rev. 1.00, 11/2005

Application Note

Using IIC to Read ADC Values on

MC9S08QG8

by Donnie Garcia

Application Engineering

Microcontroller Division

1 Introduction 1

Table of Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

The MC9S08QG8 is a small pin-count, yet feature rich, 1.1 Requirements . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 IIC Features . . . . . . . . . . . . . . . . . . . . . . . . . . 2

microcontroller. The properties of this MCU make it

1.3 Implementing IIC Communication . . . . . . . . . 2

ideal for an application such as a stand-alone 1.3.1 Master and Slave Initialization . . . . . . . 3

inter-integrated circuit (IIC) analog-to-digital converter 1.4 Defining the Messaging Strategy. . . . . . . . . . 3

(ADC). 1.4.1 Master-to-Slave Communication . . . . . 3

1.4.2 Slave-to-Master Communication . . . . . 3

This document demonstrates how the MC9S08QG8 can 2 Demonstrating the Stand-Alone ADC Application. 4

be used as a stand-alone ADC accessed by the IIC. In this 2.1 Slave Board . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2 Master Board . . . . . . . . . . . . . . . . . . . . . . . . . 4

demonstration application, commands sent via IIC will 2.3 Connecting the Demo Boards . . . . . . . . . . . . 5

select different ADC channels and set a threshold limit to 2.4 Starting the Demonstration . . . . . . . . . . . . . . 5

be used for an alarm indicator. 3 Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.1 Requirements

To run this demo, you need:

• Two DEMO9S08QG8 demo boards

• DEMO9S08QG8 Quick Start Guide (comes with

demo board)

• MC9S08QG8 data sheet from freescale.com.

• IIC driver code used in this document —

available as AN3048SW.zip from freescale.com.

• True-Time Simulator CW3.1 with MC9S08QG8

patch

© Freescale Semiconductor, Inc., 2005. All rights reserved.

Introduction

1.2 IIC Features

The IIC communications protocol is a standard that can be used to interface an MCU with other devices

such as temperature sensors, EEPROMS, LCDs, other MCUs, and A/D or D/A devices. This protocol

makes it easy to add additional devices onto an existing IIC bus because each device contains a unique

slave address. All devices on the IIC bus monitor activity, but slaves only respond to messages that are

addressed to them. IIC communication is accomplished through a simple two-line interface. Data is

relayed through the SDA pin, and the clock is supplied by the master on the SCL pin.

The MC9S08QG8 contains the standard IIC module that is in the HCS08 Family of microcontrollers. The

features of this module include:

• Compatibility with the IIC bus standards

• Multi-master operation

• Flexible baud rate generator

• Interrupt-driven byte-by-byte transfer

The interrupt capabilities of this peripheral provide a very important feature that allows interrupts to occur

at address match, arbitration loss, and data transfers. All of these features together allow IIC

communication to be handled by an interrupt service routine (ISR) that can be used for both master and

slave operation.

NOTE

For additional information on IIC module initialization, functionality, and

registers and control and status bits, please see the IIC chapter of the

MC9S08QG8 data sheet (available from freescale.com).

1.3 Implementing IIC Communication

The IIC chapter of the MC9S08QG8 data sheet provides an “IIC Module Quick Start” figure and “Typical

IIC Interrupt Routine” flow chart. These detail the most straight-forward method to implement IIC

communications. Because the application described in this document uses that method, please have the IIC

chapter of the MC9S08QG8 data sheet near for reference.

The IIC master and slave code examples for this demonstration (AN3048SW.zip) use the documented

method to create the interrupt service routine (ISR) for IIC. For example, the first decision in the “Typical

IIC Interrupt Routine” flow chart is whether the device is set as a master or slave. This is accomplished in

the example ISR with the code:

if (IICC_MST){ ... } else {...}

This checks the status of the MST bit in the IIC control register:

• If it is set (MST = 1), the code will proceed to execute what is defined inside the curly brackets,

i.e., master mode operation will be handled.

• If MST is not set (MST = 0), code will execute the else statement, i.e., slave mode operation will

be handled.

It is important to note that not all decisions that are defined in this flow chart can be made by the status

and control bits that are provided in the IIC registers. For example, when in master mode, you must know

when the second-to-last byte and the last byte to be read are received. This is accomplished in the example

Using IIC to Read ADC Values on MC9S08QG8, Rev. 1.00

2 Freescale Semiconductor

Introduction

ISR by a variable, num_to_rec, which defines the number of bytes to receive. This variable is used to

compare against a count variable that keeps track of the amount of data that has passed from slave to

master. So in the example code provided, you will see that variables are used along with status and control

bits to achieve the routine depicted in the IIC chapter of the MC9S08QG8 data sheet.

1.3.1 Master and Slave Initialization

Both master and slave can use the same ISR routine as shown in the demo code, but there is a difference

in the initialization and startup sequence between these two. See the “IIC Module Quick Start” figure in

the IIC chapter of the MC9S08QG8 data sheet for complete initialization sequence.

As soon as the slave device is initialized, it is ready to receive IIC data. A master device must initiate

communication by setting up a master transmit or a master receive. This is done in the addressing sequence

because the LSB of the address is the R/W bit. So, to initiate IIC communication, the address along with

the R/W bit must be written to the IIC data register by the master device.

1.4 Defining the Messaging Strategy

The goal of this application is to get an analog reading from a MC9S08QG8 MCU via IIC communication.

The master MCU will be allowed to select the ADC channel and set a threshold value that can be used to

compare against. A very important step in accomplishing this is defining the messages that will be sent

and received. For this application, the following messaging strategy was used.

1.4.1 Master-to-Slave Communication

Table 1 shows the messages that will pass from master to slave. All possible values are shown in the data

range.

Table 1. Master-to-Slave Communication

Address (upper 7bits)

Threshold Threshold Channel Select

R/W(1bit)

Byte

1 2 3 4

Data Range Address (0xFE–0x00), 0x03–0x00 0xFF–0x00 0x01–0x00

R/W (0x1–0x0)

Description Concatenation of address Upper byte of a 10-bit Lower byte of a 10-bit A/D channel

and read/write threshold threshold to be read

1.4.2 Slave-to-Master Communication

Table 2 shows all data that will pass from slave to master. Not shown here is the address that must first

pass from master to slave; all IIC communication is initiated by the master.

Table 2. Slave-to-Master Communication

Result Result Alarm

Byte 1 2 3

Data Range 0x03-0x00 0xFF-0x00 0x01-0x00

Description Upper byte of a 10-bit Lower byte of a 10-bit Status of the compare

result result to the threshold

Using IIC to Read ADC Values on MC9S08QG8, Rev. 1.00

Freescale Semiconductor 3

Demonstrating the Stand-Alone ADC Application

With the messaging strategy defined, software development is as simple as parsing the data that is received

by the master or slave. The ISR that has been created is pre-configured to create receive arrays with the

data. Both slave and master contain a receive data array that can be examined while the IIC bus is inactive.

It is important to wait for the IIC bus to be inactive to ensure a valid data reading. The arrays allow easy

access to the messages that have been received, and C code is used to look at individual bytes in the receive

data array. For example, the Alarm byte is examined with the following code:

This code accesses the Alarm byte in the receive data array using an “if” statement. The same method can

be used on the other bytes in the receive array so that the application code can complete the necessary

tasks.

2 Demonstrating the Stand-Alone ADC

Application

To demonstrate this application, you will need to connect and configure the two MC9S08QG8 demo

boards. Designate one of the boards to be the master board, and the other as the slave board.

2.1 Slave Board

Program the slave code (QG_IIC_Slave.c) into the slave board. Follow the directions for programming the

demo board provided by the quick start guide included with the demo board. This should guide you

step-by-step through opening a project, connecting through USB, and programming a demo board. This

board must be powered externally, so after you have programmed it, connect an external power supply

(9 V, nominally) to the power connector.

2.2 Master Board

The master code should be programmed into the master board. To visualize our demonstration, we will use

the True-Time Simulator interface and a visualization tool. So, after the board is programmed, we will be

using the debug environment.

The master board must be modified to contain pullup resistors on the SDA and SCL pins. The IIC driver

code in AN3048SW.zip uses PTB6 and PTB7 as the IIC pins. This is configured in software by setting the

IICPS bit in SOPT2. This is a useful feature of the MC9S08QG8 that allows the IIC pins to be switched

from PTA2/PTA3 to PTB6/PTB7. For IIC communication to operate, you must connect pullups on the

PTB6 and PTB7 pins.

Using IIC to Read ADC Values on MC9S08QG8, Rev. 1.00

4 Freescale Semiconductor

Demonstrating the Stand-Alone ADC Application

2.3 Connecting the Demo Boards

After the pullups have been added to the PTB6 and PTB7 pins on the master board, three connections must

be made, as shown in Figure 1:

• PTB6, PTB7, and GND must be connected between the two boards.

• GND must be connected; connect GND from J1 pin 3 to J1 pin 3 of the slave board.

• PTB7 and PTB6 are J1 pins 8 and 10, respectively; connect them as shown in Figure 1.

Master Board Slave Board

• Programmed with master code • Programmed with slave code

(QG_IIC_Master) (QG_IIC_Slave)

• Add pullup resistors on SDA and SCL • Must be powered externally

pins, PTB6 and PTB7, respectively • Uses PTB6 and PTB7 as IIC pins

• Remove jumpers on LED1 and LED2 • Remove jumpers on LED1 and LED2

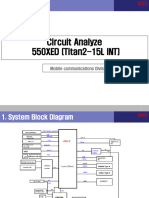

Figure 1. Connecting the Two MC9S08QG8 Demo Boards

2.4 Starting the Demonstration

1. Turn on the slave board by moving the PWR_SEL jumpers to the VDD side.

2. Press the green run arrow in the True-Time Simulator to begin the master code (see Figure 2).

In the visualization tool, the LED shows the status of the ALARM indicator; the graph is a visual

representation of the ADC data. You can switch between channel 1 and channel 0 by pressing the

SW1 (channel 0) or SW2 (channel 1) on the master demo board:

— When channel 0 is selected, the potentiometer of the slave board is being read.

Vary the potentiometer to see the result on the graphical representation (Figure 2) change.

— When channel 1 is selected, the photo sensor is being read.

Cover the photo sensor to see the graphical representation (Figure 2) change.

Using IIC to Read ADC Values on MC9S08QG8, Rev. 1.00

Freescale Semiconductor 5

Conclusion

Green Arrow

Figure 2. Visualization Tool in True-Time Simulator & Real-Time Debugger

3 Conclusion

This document and provided application code (AN3048SW.zip) demonstrate how the MC9S08QG8 is

well suited for an IIC application. The provided IIC driver code and application example can be used to

accelerate understanding of IIC and development time.

Using IIC to Read ADC Values on MC9S08QG8, Rev. 1.00

6 Freescale Semiconductor

Conclusion

Using IIC to Read ADC Values on MC9S08QG8, Rev. 1.00

Freescale Semiconductor 7

How to Reach Us:

Home Page:

www.freescale.com

E-mail:

support@freescale.com Information in this document is provided solely to enable system and software

implementers to use Freescale Semiconductor products. There are no express or

USA/Europe or Locations Not Listed:

Freescale Semiconductor implied copyright licenses granted hereunder to design or fabricate any integrated

Technical Information Center, CH370 circuits or integrated circuits based on the information in this document.

1300 N. Alma School Road

Chandler, Arizona 85224 Freescale Semiconductor reserves the right to make changes without further notice to

+1-800-521-6274 or +1-480-768-2130

support@freescale.com any products herein. Freescale Semiconductor makes no warranty, representation or

guarantee regarding the suitability of its products for any particular purpose, nor does

Europe, Middle East, and Africa: Freescale Semiconductor assume any liability arising out of the application or use of any

Freescale Halbleiter Deutschland GmbH product or circuit, and specifically disclaims any and all liability, including without

Technical Information Center limitation consequential or incidental damages. “Typical” parameters that may be

Schatzbogen 7 provided in Freescale Semiconductor data sheets and/or specifications can and do vary

81829 Muenchen, Germany in different applications and actual performance may vary over time. All operating

+44 1296 380 456 (English) parameters, including “Typicals”, must be validated for each customer application by

+46 8 52200080 (English)

+49 89 92103 559 (German) customer’s technical experts. Freescale Semiconductor does not convey any license

+33 1 69 35 48 48 (French) under its patent rights nor the rights of others. Freescale Semiconductor products are

support@freescale.com not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

Japan: or for any other application in which the failure of the Freescale Semiconductor product

Freescale Semiconductor Japan Ltd. could create a situation where personal injury or death may occur. Should Buyer

Headquarters purchase or use Freescale Semiconductor products for any such unintended or

ARCO Tower 15F unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064 its officers, employees, subsidiaries, affiliates, and distributors harmless against all

Japan claims, costs, damages, and expenses, and reasonable attorney fees arising out of,

0120 191014 or +81 3 5437 9125 directly or indirectly, any claim of personal injury or death associated with such

support.japan@freescale.com unintended or unauthorized use, even if such claim alleges that Freescale

Semiconductor was negligent regarding the design or manufacture of the part.

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

2 Dai King Street All other product or service names are the property of their respective owners.

Tai Po Industrial Estate © Freescale Semiconductor, Inc. 2005. All rights reserved.

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

AN3048

Rev. 1.00, 11/2005

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- K3596 01L FujiElectricDocument4 pagesK3596 01L FujiElectricLAN JR HOUSENo ratings yet

- TMP89FH42UG TMP89FM42UG en Summary Catalog 080701-50633Document3 pagesTMP89FH42UG TMP89FM42UG en Summary Catalog 080701-50633Nurjaman ElektroNo ratings yet

- Service Manual: Accusync Lcd72VmDocument165 pagesService Manual: Accusync Lcd72VmreyervNo ratings yet

- Automating Infrastructure Deployments in The Cloud With Terraform and Azure PipelinesDocument12 pagesAutomating Infrastructure Deployments in The Cloud With Terraform and Azure PipelinesabacusdotcomNo ratings yet

- Wiring DiagramDocument9 pagesWiring Diagramtecnicajna7No ratings yet

- Knight RiderDocument7 pagesKnight RiderCyrel Christian NavarroNo ratings yet

- Samsung Bonn-Int Rev 1.0Document56 pagesSamsung Bonn-Int Rev 1.0camilo jimenez catañoNo ratings yet

- Available Schematic Diagrams and "Board View" FilesDocument9 pagesAvailable Schematic Diagrams and "Board View" FilesRa Kham0% (1)

- Toll Services PDFDocument5 pagesToll Services PDFNitin VashisthNo ratings yet

- Gaia Scheduler: A Kubernetes-Based Scheduler FrameworkDocument8 pagesGaia Scheduler: A Kubernetes-Based Scheduler FrameworkIshak HariNo ratings yet

- ZE550KL Update Error Temporary FixDocument7 pagesZE550KL Update Error Temporary FixИгорь КуприяновNo ratings yet

- ENGD1009 Communication System Lab Session: 1 Introduction To ANACOM BoardDocument9 pagesENGD1009 Communication System Lab Session: 1 Introduction To ANACOM Boardعبدالله شھزادNo ratings yet

- Oran ChartDocument2 pagesOran ChartgsmripperNo ratings yet

- Project Report On Intelligent Conference HallDocument45 pagesProject Report On Intelligent Conference HallNikil.A HadiNo ratings yet

- Interlocking&SF6 PDFDocument3 pagesInterlocking&SF6 PDFmaherianto 29No ratings yet

- Claro Perú Routers Cisco CUBEDocument1 pageClaro Perú Routers Cisco CUBECristian Campos AguadoNo ratings yet

- A Survey On Resource Allocation and Task Scheduling Algorithms in Cloud EnvironmentDocument7 pagesA Survey On Resource Allocation and Task Scheduling Algorithms in Cloud EnvironmentDeep PNo ratings yet

- SSD-4000-26Tei Index ErrorDocument5 pagesSSD-4000-26Tei Index ErrorMario RodríguezNo ratings yet

- 74ABT377A: Octal D-Type Flip-Flop With EnableDocument12 pages74ABT377A: Octal D-Type Flip-Flop With EnableStuxnetNo ratings yet

- Intro To 8085Document43 pagesIntro To 8085Elisha NdhlovuNo ratings yet

- FChapter 10 - Design of InputOutput System - DEGDocument23 pagesFChapter 10 - Design of InputOutput System - DEGShashitharan PonnambalanNo ratings yet

- XPT System - Application Notes - R6.0 PDFDocument118 pagesXPT System - Application Notes - R6.0 PDFCamilo TNo ratings yet

- nrf24l01 Transceiver NetworkingDocument5 pagesnrf24l01 Transceiver Networkingapi-255502508No ratings yet

- Epixfab: Pieter DumonDocument14 pagesEpixfab: Pieter Dumonkirt wirk skythomasNo ratings yet

- Cost-Saving Multichemistry Battery-Charger SystemDocument12 pagesCost-Saving Multichemistry Battery-Charger SystemMarco GonzalezNo ratings yet

- Lenovo Thinkpad X200T LCM CARAMEL-1 07251-2-0731Document62 pagesLenovo Thinkpad X200T LCM CARAMEL-1 07251-2-0731Carlos PassosNo ratings yet

- NPN Silicon AF and Switching Transistor: V V V I I I I T PDocument7 pagesNPN Silicon AF and Switching Transistor: V V V I I I I T PPeter JordanNo ratings yet

- MPI Unit 5Document213 pagesMPI Unit 5NIETECEHOD NehruNo ratings yet

- Solarwinds Variable ListDocument4 pagesSolarwinds Variable Listpawan143No ratings yet

- Applications Deployment On The SaaS PlatformDocument6 pagesApplications Deployment On The SaaS Platformeyetea68No ratings yet