Professional Documents

Culture Documents

17s50apc - Ic Nho Cpu - XG5000

Uploaded by

thanh sơn trầnOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

17s50apc - Ic Nho Cpu - XG5000

Uploaded by

thanh sơn trầnCopyright:

Available Formats

0

R

Spartan-II/Spartan-IIE Family

OTP Configuration PROMs

(XC17S00A)

DS078 (v1.8) November 18, 2002 0 5 Advance Product Specification

Features

• Configuration one-time programmable (OTP) read-only • Available in compact plastic 8-pin DIP, 8-pin VOIC,

memory designed to store configuration bitstreams for 20-pin SOIC, or 44-pin VQFP packages.

Spartan-II/Spartan-IIE FPGA devices • Programming support by leading programmer

• Simple interface to the Spartan device manufacturers.

• Programmable reset polarity (active High or active • Design support using the Xilinx Alliance and

Low) Foundation series software packages.

• Low-power CMOS floating gate process • Guaranteed 20-year life data retention

• 3.3V PROM

Introduction

The XC17S00A family of PROMs provide an easy-to-use, configuration. Once configured, it disables the PROM.

cost-effective method for storing Spartan-II/Spartan-IIE When a Spartan device is in Slave Serial mode, the PROM

device configuration bitstreams. and the Spartan device must both be clocked by an

When the Spartan device is in Master Serial mode, it incoming signal.

generates a configuration clock that drives the Spartan For device programming, either the Xilinx Alliance or the

PROM. A short access time after the rising clock edge, data Spartan device design file into a standard HEX format

appears on the PROM DATA output pin that is connected to which is then transferred to most commercial PROM

the Spartan device D IN pin. The Spartan device generates programmers.

the appropriate number of clock pulses to complete the

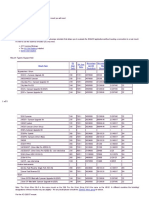

Spartan-II/IIE FPGA Configuration Bits Compatible Spartan-II/IIE PROM

XC2S15 197,696 XC17S15A

XC2S30 336,768 XC17S30A

XC2S50 559,200 XC17S50A

XC2S100 781,216 XC17S100A

XC2S150 1,040,096 XC17S150A

XC2S200 1,335,840 XC17S200A

XC2S50E 630,048 XC17S50A

XC2S100E 863,840 XC17S100A

XC2S150E(1) 1,134,496 XC17S200A

XC2S200E 1,442,016 XC17S200A

XC2S300E 1,875,648 XC17S300A

XC2S400E 2,693,440 XC17V04(2)

XC2S600E 3,961,632 XC17V04(2)

Notes:

1. Due to the higher configuration bit requirements of the XC2S150E device, an XC17S200A PROM is required to configure this FPGA.

2. See XC17V00 series configuration PROMs data sheet at: http://direct.xilinx.com/bvdocs/publications/ds073.pdf

© 2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at http://www.xilinx.com/legal.htm. All other

trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature,

application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may

require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties

or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

DS078 (v1.8) November 18, 2002 www.xilinx.com 1

Advance Product Specification 1-800-255-7778

R

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

Pin Description

Pins not listed are "no connects."

Table 1: XC17S00A PROM Pinouts

8-pin

PDIP (PD8)

and 20-pin 44-pin

VOIC/TSOP SOIC VQFP

Pin Name (VO8) (SO20) (VQ44) Pin Description

DATA 1 1 40 Data output, High-Z state when either CE or OE are inactive.

During programming, the DATA pin is I/O. Note that OE can be

programmed to be either active High or active Low.

CLK 2 3 43 Each rising edge on the CLK input increments the internal

address counter, if both CE and OE are active.

RESET/OE 3 8 13 When High, this input holds the address counter reset and puts

(OE/RESET) the DATA output in a high-impedance state. The polarity of this

input pin is programmable as either RESET/OE or OE/RESET. To

avoid confusion, this document describes the pin as RESET/OE,

although the opposite polarity is possible on all devices. When

RESET is active, the address counter is held at zero, and the

DATA output is in a high-impedance state. The polarity of this input

is programmable. The default is active High RESET, but the

preferred option is active Low RESET, because it can be

connected to the FPGAs INIT pin and a pull-up resistor.

The polarity of this pin is controlled in the programmer interface.

This input pin is easily inverted using the Xilinx HW-130

programmer software. Third-party programmers have different

methods to invert this pin.

CE 4 10 15 When High, this pin resets the internal address counter, puts the

DATA output in a high-impedance state, and forces the device into

low-ICC standby mode.

GND 5 11 18, 41 GND is the ground connection.

VCC 7, 8 18, 20 38, 35 The VCC pins are to be connected to the positive voltage supply.

2 www.xilinx.com DS078 (v1.8) November 18, 2002

1-800-255-7778 Advance Product Specification

R

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

Pinout Diagrams Controlling PROMs

Connecting the Spartan device with the PROM:

• The DATA output of the PROM drives the DIN input of

DATA (D0) 1 8 VCC the lead Spartan device.

PD8/ • The Master Spartan device CCLK output drives the

CLK 2 7 VCC CLK input of the PROM.

VO8

Top View • The RESET/OE input of the PROM is connected to the

OE/RESET 3 6 NC

INIT pin of the Spartan device and a pull-up resistor.

CE 4 5 GND This connection assures that the PROM address

counter is reset before the start of any

(re)configuration, even when a reconfiguration is

DS078_04_111502 initiated by a VCC glitch.

• The CE input of the PROM is connected to the DONE

pin of the Spartan device and a pull-up resistor. CE can

also be permanently tied Low, but this keeps the DATA

output active and causes an unnecessary supply

DATA(D0) 1 20 current of 10 mA maximum.

VCC

NC 2 19 NC

CLK 3 18 VCC FPGA Master Serial Mode Summary

NC 4 17 NC

NC SO20 16 The I/O and logic functions of the Configurable Logic Block

5 NC

NC 6 Top View 15 (CLB) and their associated interconnections are established

NC

NC 7 14 by a configuration program. The program is loaded either

NC

OE/RESET 8 13 NC automatically upon power up, or on command, depending

NC 9 12 NC on the state of the Spartan device mode pins. In Master

CE 10 11 GND Serial mode, the Spartan device automatically loads the

DS078_05_111502

configuration program from an external memory. The

XC17S00A PROM has been designed for compatibility with

the Master Serial mode.

Upon power-up or reconfiguration, the Spartan device

enters the Master Serial mode when the mode pins are set

to Master Serial mode. Data is read from the PROM

DATA(D0)

sequentially on a single data line. Synchronization is pro-

vided by the rising edge of the temporary signal CCLK,

GND

VCC

VCC

CLK

which is generated during configuration.

NC

NC

NC

NC

NC

NC

Master Serial mode provides a simple configuration inter-

face (Figure 1). Only a serial data line, two control lines, and

44

43

42

41

40

39

38

37

36

35

34

a clock line are required to configure the Spartan device.

NC 1 33 NC

Data from the PROM is read sequentially, accessed via the

NC 2 32 NC

NC 3 NC

internal address and bit counters which are incremented on

31

NC 4 30 NC every valid rising edge of CCLK.

NC 5 VQ44 29 NC If the user-programmable, dual-function DIN pin on the

NC 6 Top View 28 NC Spartan device is used only for configuration, it must still be

NC 7 27 NC held at a defined level during normal operation. The

NC 8 26 NC Spartan-II/Spartan-IIE family takes care of this

NC 9 25 NC

automatically with an on-chip pull-up/down resistor or

NC 10 24 NC

NC 11 NC

keeper circuit.

23

12

13

14

15

16

17

18

19

20

21

22

NC

OE/RESET

NC

CE

NC

NC

GND

NC

NC

NC

NC

DS073_06_101002

DS078 (v1.8) November 18, 2002 www.xilinx.com 3

Advance Product Specification 1-800-255-7778

R

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

Spartan-II/

Spartan-IIE

Master Serial 3.3V

3.3V VCC

M0

M1 3.3K

M2

3.3K

VCC

DIN DATA

CCLK CLK XC17S00A

DONE CE PROM

INIT OE/RESET

Notes:

1. If the DriveDone configuration option is not active, pull up DONE with a 3.3kΩ resistor.

(Low Resets the Address Pointer)

CCLK

(Output)

DIN

DOUT

(Output)

DS078_01_110601

Figure 1: Master Serial Mode

The one-time-programmable XC17S00A PROM in Figure 1 early DONE inhibits the PROM data output one CCLK cycle

supports automatic loading of configuration programs. An before the Spartan FPGA I/Os become active.

4 www.xilinx.com DS078 (v1.8) November 18, 2002

1-800-255-7778 Advance Product Specification

R

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

Standby Mode Programming Spartan-II/Spartan-IIE

The PROM enters a low-power standby mode whenever CE Family PROMs

is asserted High. The output remains in a high-impedance The devices can be programmed on programmers supplied

state regardless of the state of the OE input. by Xilinx or qualified third-party vendors. The user must

ensure that the appropriate programming algorithm and the

latest version of the programmer software are used. The

wrong choice can permanently damage the device.

VCC GND

RESET/

OE CE

or

OE/

RESET

Address Counter

CLK TC

EPROM OE

Output

Cell DATA

Matrix

DS030_02_011300

Figure 2: Simplified Block Diagram (does not show programming circuit)

Important: Always tie the two VCC pins together in your application.

Table 2: Truth Table for XC17S00A Control Inputs

Control Inputs Outputs

RESET(1) CE Internal Address(2) DATA ICC

Inactive Low If address < TC: increment Active Active

If address > TC: don’t change High-Z Reduced

Active Low Held reset High-Z Active

Inactive High Not changing High-Z Standby

Active High Held reset High-Z Standby

Notes:

1. The XC17S00A RESET input has programmable polarity

2. TC = Terminal Count = highest address value. TC + 1 = address 0.

DS078 (v1.8) November 18, 2002 www.xilinx.com 5

Advance Product Specification 1-800-255-7778

R

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

XC17S15A, XC17S30A, XC17S50A, XC17S100A, XC17S150A, XC17S200A, and

XC17S300A

Absolute Maximum Ratings(1)

Symbol Description Value Units

VCC Supply voltage relative to GND –0.5 to +4.0 V

VIN Input voltage with respect to GND –0.5 to VCC +0.5 V

VTS Voltage applied to High-Z output –0.5 to VCC +0.5 V

TSTG Storage temperature (ambient) –65 to +150 °C

TSOL Maximum soldering temperature (10s @ 1/16 in.) +260 °C

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.

Operating Conditions(1)

Symbol Description Min Max Units

VCC Commercial Supply voltage relative to GND (TA = 0°C to +70°C) 3.0 3.6 V

Industrial Supply voltage relative to GND (TA = –40°C to +85°C) 3.0 3.6 V

TVCC VCC rise time from 0V to nominal voltage 1.0 50 ms

Notes:

1. During normal read operation, both V CC pins must be connected together.

2. At power-up, the device requires the VCC power supply to monotonically rise from 0V to nominal voltage within the specified V CC rise

time. If the power supply cannot meet this requirement, then the device may not perform a power-on-reset properly.

DC Characteristics Over Operating Condition

Symbol Description Min Max Units

VIH High-level input voltage 2.0 VCC V

VIL Low-level input voltage 0 0.8 V

VOH High-level output voltage (IOH = –3 mA) 2.4 - V

VOL Low-level output voltage (IOL = +3 mA) - 0.4 V

ICCA Supply current, active mode (at maximum frequency) - 15 mA

ICCS Supply current, standby mode - 1 mΑ

IL Input or output leakage current –10 10 µA

CIN Input Capacitance (VIN = GND, f = 1.0 MHz) - 10 pF

COUT Output Capacitance (VIN = GND, f = 1.0 MHz) - 10 pF

6 www.xilinx.com DS078 (v1.8) November 18, 2002

1-800-255-7778 Advance Product Specification

R

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

AC Characteristics Over Operating Condition(1)

TCEH

CE

TSCE TSCE THCE

ESET/OE

THOE

TLC THC TCYC

CLK

TOE TCAC TOH TDF

TCE

DATA

TOH

DS030_03_111502

Symbol Description Min Max Units

TOE RESET/OE to Data Delay - 45 ns

TCE CE to Data Delay - 60 ns

TCAC CLK to Data Delay - 80 ns

TOH Data Hold From CE, RESET/OE, or CLK(2) 0 - ns

TDF CE or RESET/OE to Data Float Delay(2,3) - 50 ns

TCYC Clock Periods 100 - ns

TLC CLK Low Time(2) 50 - ns

THC CLK High Time(2) 50 - ns

TSCE CE Setup Time to CLK (to guarantee proper counting) 25 - ns

THCE CE Hold Time to CLK (to guarantee proper counting) 0 - ns

THOE RESET/OE Hold Time (guarantees counters are reset) 25 - ns

TCEH CE High time (guarantees counters are reset) 20 - ns

Notes:

1. AC test load = 50 pF

2. Guaranteed by design, not tested.

3. Float delays are measured with 5 pF AC loads. Transition is measured at ±200 mV from steady state active levels.

4. All AC parameters are measured with VIL = 0.0V and VIH = 3.0V.

5. If TCEH High < 2µs, TCE = 2 µs.

6. If THOE High < 2µs, TCE = 2 µs.

DS078 (v1.8) November 18, 2002 www.xilinx.com 7

Advance Product Specification 1-800-255-7778

R

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

Ordering Information

XC17S15A VO8 C

Device Number Operating Range/Processing

XC17S15A C = Commercial (TA = 0°C to +70°C)

XC17S30A I = Industrial (TA = –40°C to +85°C)

XC17S50A

XC17S100A

XC17S150A Package Type

XC17S200A PD8 = 8-pin Plastic DIP

XC17S300A VO8 = 8-pin Plastic Small-Outline Thin Package

SO20 = 20-pin Plastic Small-Outline Package

VQ44 = 44-pin Plastic Quad Flat Package

Spartan-II 3.3V Valid Ordering Combinations

XC17S15APD8C XC17S50APD8C XC17S150APD8C

XC17S15AVO8C XC17S50AVO8C XC17S150AVO8C

XC17S15ASO20C XC17S50ASO20C XC17S150ASO20C

XC17S15APD8I XC17S50APD8I XC17S150APD8I

XC17S15AVO8I XC17S50AVO8I XC17S150AVO8I

XC17S15ASO20I XC17S50ASO20I XC17S150ASO20I

XC17S30APD8C XC17S100APD8C XC17S200APD8C

XC17S30AVO8C XC17S100AVO8C XC17S200AVO8C

XC17S30ASO20C XC17S100ASO20C XC17S200AVQ44C

XC17S30APD8I XC17S100APD8I XC17S200APD8I

XC17S30AVO8I XC17S100AVO8I XC17S200AVO8I

XC17S30ASO20I XC17S100ASO20I XC17S200AVQ44I

XC17S300AVQ44C

XC17S300AVQ44I

8 www.xilinx.com DS078 (v1.8) November 18, 2002

1-800-255-7778 Advance Product Specification

R

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

Marking Information

Due to the small size of the PROM package, the complete The XC prefix is deleted and the package code is simplified.

ordering part number cannot be marked on the package. Device marking is as follows.

17S15A V C

Device Marking Operating Range/Processing

17S15A C = Commercial (TA = 0°C to +70°C)

17S30A I = Industrial (TA = –40°C to +85°C)

17S50A

17S100A

17S150A Package Mark

17S200A P = 8-pin Plastic DIP

17S300A V = 8-pin Plastic Small-Outline Thin Package

S = 20-pin Plastic Small-Outline Package

VQ = 44-pin Plastic Quad Flat Package

Revision History

The following table shows the revision history for this document.

Date Revision Revision

09/14/00 1.0 Initial Xilinx release.

11/13/00 1.1 Updated configuration bits.

04/07/01 1.2 Added to features: “Guaranteed 20 year life data retention”, removed “Programming the FPGA

with counters” and related text.

06/20/01 1.3 Revised Figure 1 resistor values to match Spartan-II data sheet.

10/09/01 1.4 Added note for unlisted pins, changed ICCA and ICCS, and added power-on supply requirements

and note regarding power-on reset.

11/15/01 1.5 Updated for Spartan-IIE FPGA family.

06/25/02 1.6 Changed Table 1.

10/15/02 1.7 Changed Table 1. Added Pinout Diagrams, page 3.

11/18/02 1.8 Added XC2S400E and XC2S600E to Compatible FPGAS table. Modified document title.

DS078 (v1.8) November 18, 2002 www.xilinx.com 9

Advance Product Specification 1-800-255-7778

You might also like

- Cisco 8000 Series RoutersDocument18 pagesCisco 8000 Series Routersrolando_ricapaNo ratings yet

- Spartan Family of One-Time Programmable Configuration Proms (Xc17S00)Document9 pagesSpartan Family of One-Time Programmable Configuration Proms (Xc17S00)saikumarNo ratings yet

- 8.8R1 Release Notes RevcDocument71 pages8.8R1 Release Notes RevcVillage MegdoulNo ratings yet

- Catalyst 9k Troubleshooting - DGTL BRKARC 3190Document77 pagesCatalyst 9k Troubleshooting - DGTL BRKARC 3190Test TestNo ratings yet

- Platform Flash In-System Programmable Configuration Proms: FeaturesDocument35 pagesPlatform Flash In-System Programmable Configuration Proms: FeaturesVk BrainNo ratings yet

- 7 - Hardware TroubleshootingDocument22 pages7 - Hardware TroubleshootingMostafaEl-sayedNo ratings yet

- FPGA Product Selection GuideDocument34 pagesFPGA Product Selection Guidesandeepscribd123No ratings yet

- Using Block RAM in Spartan-3 Generation FpgasDocument40 pagesUsing Block RAM in Spartan-3 Generation FpgasSreedhar PathaNo ratings yet

- Arria 10 Product TableDocument2 pagesArria 10 Product Tablesmith1011No ratings yet

- XilinxDocument20 pagesXilinxAvila Cruz JaimeNo ratings yet

- OS6900 AOS 8.9.107.R02 Release NotesDocument71 pagesOS6900 AOS 8.9.107.R02 Release Notesmenage.gillesNo ratings yet

- List PersediaanDocument15 pagesList Persediaanonlen ctvNo ratings yet

- XC 5200Document73 pagesXC 5200venkateshNo ratings yet

- Virtex6 Product TableDocument1 pageVirtex6 Product Tablemrgrace1No ratings yet

- Xilinx Programmer Qualification Specification: DescriptionDocument16 pagesXilinx Programmer Qualification Specification: DescriptionsaikumarNo ratings yet

- Ice 40 LP HX Family Data SheetDocument45 pagesIce 40 LP HX Family Data SheetPablo AquevequeNo ratings yet

- PC40-III Service Manual 314134-01 (1989 Mar)Document127 pagesPC40-III Service Manual 314134-01 (1989 Mar)AlanNo ratings yet

- CAT25C32/64: 32K/64K-Bit SPI Serial CMOS E Prom FeaturesDocument9 pagesCAT25C32/64: 32K/64K-Bit SPI Serial CMOS E Prom FeaturesTeyfik koyuncuNo ratings yet

- Arnet Equipment List 2011 03 15Document2 pagesArnet Equipment List 2011 03 15arnetconsultingNo ratings yet

- 8662D06112038B 976329Document34 pages8662D06112038B 976329ManunoghiNo ratings yet

- Platform Flash In-System Programmable Configuration Proms: FeaturesDocument35 pagesPlatform Flash In-System Programmable Configuration Proms: FeaturesUstaz RockNo ratings yet

- Dyadics SCN6 DatasheetDocument2 pagesDyadics SCN6 DatasheetElectromateNo ratings yet

- Arnet Equipment List 2010-07-13Document2 pagesArnet Equipment List 2010-07-13arnetconsultingNo ratings yet

- Brkarc 3190Document81 pagesBrkarc 3190ahmedNo ratings yet

- BRKSPG 2280Document44 pagesBRKSPG 2280ali partoviNo ratings yet

- Cours3 - Prise - en Main - Xilinx - FinalDocument43 pagesCours3 - Prise - en Main - Xilinx - FinalsoundouselhammanyNo ratings yet

- FAQ IOP-Versionen 2019-07-01 ENDocument3 pagesFAQ IOP-Versionen 2019-07-01 ENGlauco SantiagoNo ratings yet

- Brkarc 3465Document182 pagesBrkarc 3465astyamixNo ratings yet

- DatasheetDocument92 pagesDatasheetStuxnetNo ratings yet

- Cyclone IV Product TableDocument1 pageCyclone IV Product TablePedro NogueiraNo ratings yet

- Cat® Technician Newsletter Edition 1Document2 pagesCat® Technician Newsletter Edition 1jesus mamani meza100% (1)

- 7 Series Product Selection GuideDocument12 pages7 Series Product Selection GuidematrixNo ratings yet

- PC Ref 1Document13 pagesPC Ref 1mika cabelloNo ratings yet

- Cyclone IV Product TableDocument1 pageCyclone IV Product Table15767340887No ratings yet

- GD25LQ40 Rev1.5Document63 pagesGD25LQ40 Rev1.5mirage0706No ratings yet

- Geared Motors Power Distribution: V V V VDocument2 pagesGeared Motors Power Distribution: V V V VShamim Ahsan ParvezNo ratings yet

- LatticeXP2FamilyDataSheet PDFDocument92 pagesLatticeXP2FamilyDataSheet PDFvictor SanmiguelNo ratings yet

- Thinksystem Broadcom 57416 10Gbase-T Ethernet Adapters: Product GuideDocument18 pagesThinksystem Broadcom 57416 10Gbase-T Ethernet Adapters: Product GuidedoegoodNo ratings yet

- Ol 17 12 9600Document50 pagesOl 17 12 9600radzjobsNo ratings yet

- SET UP EQMOD SOFTWARE FOR ASTROPHOTOGRAPHYDocument5 pagesSET UP EQMOD SOFTWARE FOR ASTROPHOTOGRAPHYMechtatel HrenovNo ratings yet

- Computer SpecsDocument2 pagesComputer SpecsRicarte Pillos IIINo ratings yet

- Product Selection GuideDocument34 pagesProduct Selection Guidechgk16No ratings yet

- SJ - V Series Spindle MotorsDocument3 pagesSJ - V Series Spindle MotorsCesar MessiasNo ratings yet

- Cisco Catalyst 9400 Series SwitchDocument18 pagesCisco Catalyst 9400 Series Switchtortuguita9No ratings yet

- Introduction To FPGADocument34 pagesIntroduction To FPGAMuhammad Hamza KhanNo ratings yet

- OK Cisco 1600 Series Router ArchitectureDocument13 pagesOK Cisco 1600 Series Router Architecturezaba9awNo ratings yet

- 9000@nettrainDocument79 pages9000@nettrainelahi elahiNo ratings yet

- SIMOTICS S-1FK7 Servomotors: &Rpsdfw6/Qfkurqrxv0Rwruviru0Rwlrq&Rqwuro$SsolfdwlrqvDocument6 pagesSIMOTICS S-1FK7 Servomotors: &Rpsdfw6/Qfkurqrxv0Rwruviru0Rwlrq&Rqwuro$SsolfdwlrqvDaniel FernándezNo ratings yet

- WS-C6513-E Datasheet: Check Its PriceDocument5 pagesWS-C6513-E Datasheet: Check Its PriceJoseph SibilaNo ratings yet

- 25Q16BSIGDocument34 pages25Q16BSIGRiiandaArifSNo ratings yet

- IX4340Document10 pagesIX4340Angelė LNo ratings yet

- Qgudnd Rqvxowlqj Urxs QF: SMPTE-292 Scrambler and Descrambler/FramerDocument3 pagesQgudnd Rqvxowlqj Urxs QF: SMPTE-292 Scrambler and Descrambler/FramerLaurentiu IacobNo ratings yet

- 360BAP Manual - GeneralDocument17 pages360BAP Manual - GeneralLucasNo ratings yet

- Data BookDocument750 pagesData BookSwarup PalNo ratings yet

- 40MX and 42MX FPGA Families: FeaturesDocument143 pages40MX and 42MX FPGA Families: FeaturesMahemehr MehrNo ratings yet

- IntelDocument17 pagesIntelAngel Lazarte DueñasNo ratings yet

- Compactlogix™ 5370 L3 Programmable Automation ControllersDocument2 pagesCompactlogix™ 5370 L3 Programmable Automation ControllersJemeraldNo ratings yet

- Old Cisco Chassis MibDocument52 pagesOld Cisco Chassis MibJohn SmithNo ratings yet

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- RTOSDocument6 pagesRTOSAkanksha SinghNo ratings yet

- Lab #3 File Carving With Prodiscover Basic Last Name - First NameDocument3 pagesLab #3 File Carving With Prodiscover Basic Last Name - First NamedotrinufyaNo ratings yet

- B250 BrochureDocument8 pagesB250 BrochureDavid GrahamNo ratings yet

- 10EC65Document7 pages10EC65Swamy SlrNo ratings yet

- Tuning Red Hat Enterprise Linux For Oracle and Oracle RAC PerformanceDocument12 pagesTuning Red Hat Enterprise Linux For Oracle and Oracle RAC Performancedeepeshkumarpal5194No ratings yet

- Chapter 5: Switch Configuration: Routing and Switching Essentials v6.0Document39 pagesChapter 5: Switch Configuration: Routing and Switching Essentials v6.0AbeyMulugetaNo ratings yet

- Main Unit 3Document76 pagesMain Unit 3Aanjan Kumar 100432No ratings yet

- ATOMixia PDFDocument8 pagesATOMixia PDFM Arief WibawaNo ratings yet

- Invent A RioDocument6 pagesInvent A Rionilver25No ratings yet

- BrochureDocument4 pagesBrochureJasmine RaiNo ratings yet

- Manado and Bali Computer Store LocationsDocument106 pagesManado and Bali Computer Store LocationsBarnabas GuloNo ratings yet

- Importing Core Configuration Files Into Nagios XI PDFDocument5 pagesImporting Core Configuration Files Into Nagios XI PDFarun_sakreNo ratings yet

- Disaster Recovery Plan SummaryDocument15 pagesDisaster Recovery Plan Summaryfawas hamdiNo ratings yet

- YCE01 - PC Programming Reference ManualDocument20 pagesYCE01 - PC Programming Reference Manualtroywoll100% (1)

- Debug Batch Jobs in Dynamics AxDocument5 pagesDebug Batch Jobs in Dynamics AxJordi Reig SaisNo ratings yet

- Project Work: Class 10 Computer ApplicationDocument10 pagesProject Work: Class 10 Computer ApplicationSantosh JhaNo ratings yet

- SN e Reference PDFDocument1,269 pagesSN e Reference PDFPMNo ratings yet

- Two Pass Assembler CodeDocument4 pagesTwo Pass Assembler CodeAshish KatlamNo ratings yet

- Live web app testing with CucumberDocument8 pagesLive web app testing with CucumberVasilica BoaghiNo ratings yet

- Devops Transformation: Engage Your Ibm I Teams: ArcadDocument17 pagesDevops Transformation: Engage Your Ibm I Teams: ArcadManuel VegaNo ratings yet

- Microchip Webinar - Machine Learning With MCHP MCU & MPU - Oct - 23 - 2020Document32 pagesMicrochip Webinar - Machine Learning With MCHP MCU & MPU - Oct - 23 - 2020Raj Kumar JainNo ratings yet

- Recursive SolutionsDocument11 pagesRecursive SolutionsergrehgeNo ratings yet

- Interfacing A Buzzer Using 8051 Microcontroller: AbstractDocument3 pagesInterfacing A Buzzer Using 8051 Microcontroller: AbstractRenu PeriketiNo ratings yet

- Mydoom VirusDocument2 pagesMydoom VirusDan PantanoNo ratings yet

- Acuity Educare Advanced Web Programming Sem V Unit 2Document25 pagesAcuity Educare Advanced Web Programming Sem V Unit 2Darshana RavindraNo ratings yet

- VLSI Implementation of Turbo Coder For LTE Using Verilog HDLDocument5 pagesVLSI Implementation of Turbo Coder For LTE Using Verilog HDLSamreen FarhanaNo ratings yet

- Red Hat OpenStack Platform-13-Director Installation and Usage-en-USDocument212 pagesRed Hat OpenStack Platform-13-Director Installation and Usage-en-USDali HadricheNo ratings yet

- 25+ Notepad Virus Script (Just Copy & Paste) 2020: ResponsesDocument29 pages25+ Notepad Virus Script (Just Copy & Paste) 2020: Responsesmuna cliff100% (1)

- ASSEMBLING COMPUTER: HOW TO BUILD A PCDocument48 pagesASSEMBLING COMPUTER: HOW TO BUILD A PCCeejaay PelinaNo ratings yet

- Arbitrary Waveform ProgramDocument8 pagesArbitrary Waveform ProgramSea Lo Quesea Pero ChevereNo ratings yet