Professional Documents

Culture Documents

S72Xs-R Based MCPS: Mirrorbit Flash Memory and Dram

S72Xs-R Based MCPS: Mirrorbit Flash Memory and Dram

Uploaded by

momosOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

S72Xs-R Based MCPS: Mirrorbit Flash Memory and Dram

S72Xs-R Based MCPS: Mirrorbit Flash Memory and Dram

Uploaded by

momosCopyright:

Available Formats

S72XS-R Based MCPs

MirrorBit® Flash Memory and DRAM

128/256 Mb (8/16M x 16 bit), 1.8 Volt-only, Address-High,

Address-Low, Data Multiplexed Simultaneous Read/Write,

Burst Mode Flash Memory

128/256 Mb (8/16M x 16 bit) DDR DRAM on Split Bus

S72XS-R Based MCPs Cover Sheet

Data Sheet (Advance Information)

Notice to Readers: This document states the current technical specifications regarding the Spansion

product(s) described herein. Each product described herein may be designated as Advance Information,

Preliminary, or Full Production. See Notice On Data Sheet Designations for definitions.

Publication Number S72XS-R_00 Revision 05 Issue Date August 19, 2010

Data Sheet (Advan ce Infor m a tio n)

Notice On Data Sheet Designations

Spansion Inc. issues data sheets with Advance Information or Preliminary designations to advise readers of

product information or intended specifications throughout the product life cycle, including development,

qualification, initial production, and full production. In all cases, however, readers are encouraged to verify

that they have the latest information before finalizing their design. The following descriptions of Spansion data

sheet designations are presented here to highlight their presence and definitions.

Advance Information

The Advance Information designation indicates that Spansion Inc. is developing one or more specific

products, but has not committed any design to production. Information presented in a document with this

designation is likely to change, and in some cases, development on the product may discontinue. Spansion

Inc. therefore places the following conditions upon Advance Information content:

“This document contains information on one or more products under development at Spansion Inc.

The information is intended to help you evaluate this product. Do not design in this product without

contacting the factory. Spansion Inc. reserves the right to change or discontinue work on this proposed

product without notice.”

Preliminary

The Preliminary designation indicates that the product development has progressed such that a commitment

to production has taken place. This designation covers several aspects of the product life cycle, including

product qualification, initial production, and the subsequent phases in the manufacturing process that occur

before full production is achieved. Changes to the technical specifications presented in a Preliminary

document should be expected while keeping these aspects of production under consideration. Spansion

places the following conditions upon Preliminary content:

“This document states the current technical specifications regarding the Spansion product(s)

described herein. The Preliminary status of this document indicates that product qualification has been

completed, and that initial production has begun. Due to the phases of the manufacturing process that

require maintaining efficiency and quality, this document may be revised by subsequent versions or

modifications due to changes in technical specifications.”

Combination

Some data sheets contain a combination of products with different designations (Advance Information,

Preliminary, or Full Production). This type of document distinguishes these products and their designations

wherever necessary, typically on the first page, the ordering information page, and pages with the DC

Characteristics table and the AC Erase and Program table (in the table notes). The disclaimer on the first

page refers the reader to the notice on this page.

Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal changes

are expected, the Preliminary designation is removed from the data sheet. Nominal changes may include

those affecting the number of ordering part numbers available, such as the addition or deletion of a speed

option, temperature range, package type, or VIO range. Changes may also include those needed to clarify a

description or to correct a typographical error or incorrect specification. Spansion Inc. applies the following

conditions to documents in this category:

“This document states the current technical specifications regarding the Spansion product(s)

described herein. Spansion Inc. deems the products to have been in sufficient production volume such

that subsequent versions of this document are not expected to change. However, typographical or

specification corrections, or modifications to the valid combinations offered may occur.”

Questions regarding these document designations may be directed to your local sales office.

2 S72XS-R Based MCPs S72XS-R_00_05 August 19, 2010

S72XS-R Based MCPs

MirrorBit® Flash Memory and DRAM

128/256 Mb (8/16M x 16 bit), 1.8 Volt-only, Address-High,

Address-Low, Data Multiplexed Simultaneous Read/Write,

Burst Mode Flash Memory

128/256 Mb (8/16M x 16 bit) DDR DRAM on Split Bus

Data Sheet (Advance Information)

Features

Power supply voltage of 1.7 V to 1.95 V Packages

Burst Speeds – 8.0 x 8.0 mm, 133-ball MCP

– Flash = 83 MHz or 108 MHz Operating Temperature of –25°C to +85°

– DDR DRAM = 166 MHz

General Description

This document contains information on the S72XS-R MCP stacked products. Refer to the S29VS/XS-R data sheet

(S29VS_XS-R_00) for full electrical specifications of the Flash memory component.

The S72XS Series is a product line of stacked products (MCPs), and consists of:

S29XS family Address-High, Address-Low, Data Multiplexed Flash memory die

DDR DRAM

The products covered by this document are listed in the tables below.

DRAM Density

Flash Density 128 Mb 256 Mb

128 Mb S72XS128RD0

256 Mb S72XS256RE0

DDR Specification Reference

Spansion Documentation

Density Reference Name Publication Number

128 Mb (8M x 16 bit) LPDDR333 SDRAM SDM128D166D1R

128 Mb

128 Mb (8M x 16-bit) DDR Mobile RAM SDM128D166D1K (Note 1)

256 Mb 256 Mb (16M x 16-bit) DDR DRAM TBD

Note:

1.Products using this DRAM are not recommended for new designs.

Publication Number S72XS-R_00 Revision 05 Issue Date August 19, 2010

This document contains information on one or more products under development at Spansion Inc. The information is intended to help you evaluate this product. Do not design in

this product without contacting the factory. Spansion Inc. reserves the right to change or discontinue work on this proposed product without notice.

Data Sheet (Advan ce Infor m a tio n)

1. Product Selector Guide

Flash DDR DRAM Flash Speed DDR DRAM

Device OPN Flash Boot Density Density (MHz) Speed (MHz) Supplier Package

S72XS128RD0AHBHE SDM128D166D1R

128 Mb 128 Mb 83 8.0 x 8.0 mm

S72XS128RD0AHBH60 (1) Top 166 SDM128D166D1K 133-ball MCP

(RSC133)

S72XS256RE0AHBH1 256 Mb 256 Mb 108 TBD

Note:

1. This OPN is not recommended for new designs.

2. Electronic Serial Number

The Factory Secured Silicon Area contains a random, 128-bit ESN, stored in the address range

000000h-000007h.

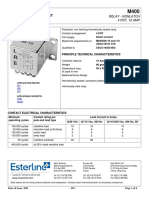

3. Product Block Diagram

F -R S T# RS T# A DQ 1 5 - A DQ 0 A D Q 15-A D Q 0

A ma x - A 1 6 ( No Co n n e c t)

F -V P P V PP CL K F -C LK

NOR RDY F -R D Y

F -C E #

F -O E #

CE#

O E#

FLASH

F -W E # W E# X S -R

F -A V D # A V D#

(A A D M )

V CC F -V C C

V CCQ F -V C C Q

V SS VSS

V SSQ

D -R A S # RA S # CK D -C LK

D -C A S # CA S # CK # D -C LK #

D -B A 0 BA 0 L DQ S D -LD Q S

D -B A 1 BA 1 DDR UDQ S D -U D Q S

D -C K E D -LD Q M

D -W E #

CK E

W E#

DRAM L DM

UDM D -U D Q M

D -C E # CS # M EM ORY

D -A m ax - D -A 0 A ma x - A 0 DQ 1 5 - DQ 0 D -D Q 15 - D -D Q 0

D -V C C V DD V SS VSS

D -V C C Q V DDQ V SSQ

Notes:

1. Amax indicates highest address bit for memory component:

a. Amax = A11 for 128 Mb DDR DRAM, A12 for 256 Mb DDR DRAM.

2. For Flash, A15 - A0 is tied to DQ15 - DQ0.

4 S72XS-R Based MCPs S72XS-R_00_05 August 19, 2010

D at a S hee t (Adva nce In for m ation)

4. Connection Diagrams

Figure 4.1 133-ball Fine-Pitch Ball Grid Array MCP

1 2 3 4 5 6 7 8 9 10 11 12 13 14 Legend

A

DNU DNU VSS D-VCCQ D-DQ9 D-DQ8 VSS D-VCC D-VCC D-DQ5 D-DQ3 VSS DNU DNU Index Location

B

DNU VSS D-DQ13 D-UDQS D-DQ10 VSS D-VCCQ D-VCCQ D-LDQM D-DQ6 D-DQ4 D-DQ1 D-VCCQ DNU Do Not Use

C

D-VCC D-DQ15 D-DQ14 D-DQ12 D-DQ11 D-UDQM VSS D-VCC VSS D-DQ7 D-LDQS D-DQ2 D-DQ0 VSS

No Connect

D

RFU NC NC INDEX F-OE# ADQ8 D-VCC

DRAM Only

E

RFU RFU RFU ADQ9 ADQ1 ADQ0

Code Flash Only

F

RFU RFU RFU VSS ADQ3 ADQ2

G Reserved for Future Use

F-CE# RFU F-WE# F-VCCQ ADQ11 ADQ10

H VSS

F-VPP F-VCC F-CLK ADQ13 ADQ12 ADQ4

J

RFU VSS NC VSS VSS ADQ5

K

RFU F-AVD# NC NC ADQ7 ADQ6

L

RFU F-RST# D-CE# F-VCCQ ADQ15 ADQ14

M

NC RFU D-A3 D-A6 D-A9 D-CKE VSS D-WE# D-A10 D-A1 RFU RFU F-RDY VSS

N

DNU VSS D-VCC D-A5 D-A8 D-CAS# D-CLK# D-BA1 D-A11 D-A2 D-A12 RFU F-VCC DNU

P

DNU DNU NC D-A4 D-A7 D-RAS# D-CLK D-VCC D-BA0 D-A0 D-VCC VSS DNU DNU

MCP DDR DRAM Density D-Amax

S72XS128RD0 128 Mb D-A11

S72XS256RE0 256 Mb D-A12

August 19, 2010 S72XS-R_00_05 S72XS-R Based MCPs 5

Data Sheet (Advan ce Infor m a tio n)

5. Input/Output Descriptions

Symbol Description Flash RAM

ADQ15 – ADQ0 Flash multiplexed Address and Data X

F-CE# Flash Chip-enable input. X

F-OE# Flash Output Enable input. Asynchronous relative to CLK for Burst mode. X

F-WE# Flash Write Enable input X

F-VCC Flash device power supply (1.7 V to 1.95 V) X

F-VCCQ Flash Input/Output Buffer power supply X

VSS Ground X X

Flash ready output. Indicates the status of the Burst read. VOL = data invalid. VOH = data

F-RDY X

valid.

Flash Clock. The first rising edge of CLK in conjunction with AVD# low latches the address

input and activates burst mode operation. After the initial word is output, subsequent rising

F-CLK X

edges of CLK increment the internal address counter. CLK should remain low during

asynchronous access.

Flash Address Valid input. Indicates to device that the valid address is present on the

address inputs. VIL = for asynchronous mode, indicates valid address; for burst mode,

F-AVD# X

causes starting address to be latched on rising edge of CLK. VIH= device ignores address

inputs

F-RST# Flash hardware reset input. VIL= device resets and returns to reading array data X

Flash accelerated input. At VHH, accelerates programming; automatically places device in

F-VPP unlock bypass mode. At VIL, disables all program and erase functions. Should be at VIH for X

all other conditions.

D-Amax – D-A0 DRAM Address inputs. X

D-DQ15 – D-DQ0 DRAM Data input/output X

D-CLK DRAM System Clock X

D-CE# DRAM Chip Select X

D-CKE DRAM Clock Enable X

D-BA1 – BA0 DRAM Bank Select X

D-RAS# DRAM Row Address Strobe X

D-CAS# DRAM Column Address Strobe X

D-UDQM – D-LDQM DRAM Data Input Mask X

D-WE# DRAM Write Enable input X

D-VCCQ DRAM Input/Output Buffer power supply X

D-VCC DRAM device power supply X

D-UDQS DRAM Upper Data Strobe, output with read data and input with write data X

D-LDQS DRAM Lower Data Strobe, output with read data and input with write data X

D-CLK# DDR Clock for negative edge of CLK X

Reserved for Future Use. No device internal signal is currently connected to the package

connector but there is potential future use for the connector for a signal. It is recommended

RFU

to not use RFU connectors for PCB routing channels so that the PCB may take advantage

of future enhanced features in compatible footprint devices.

Not Connected. No device internal signal is connected to the package connector nor is

NC there any future plan to use the connector for a signal. The connection may safely be used

for routing space for a signal on a Printed Circuit Board (PCB).

Do Not Use. A device internal signal may be connected to the package connector. The

connection may be used by Spansion for test or other purposes and is not intended for

connection to any host system signal. Any DNU signal related function will be inactive when

DNU

the signal is at VIL. The signal has an internal pull-down resistor and may be left

unconnected in the host system or may be tied to VSS. Do not use these connections for

PCB signal routing channels. Do not connect any host system signal to these connections.

6 S72XS-R Based MCPs S72XS-R_00_05 August 19, 2010

D at a S hee t (Adva nce In for m ation)

6. Ordering Information

The order number (Valid Combination) is formed by the following:

S72XS 128 R D0 AH B H E 3

PACKING TYPE

0 = Tray

3 = 13-inch Tape and Reel

FLASH and DDR SPEED, DDR DRAM Specification Reference

E = 83 MHz Flash, 166 MHz DDR DRAM, SDM128D166D1R

6 = 83 MHz Flash, 166 MHz DDR DRAM, SDM128D166D1K (Note 4)

1 = 108 MHz Flash, 166 MHz DDR DRAM, TBD

RAM Bus and Flash Boot

H = x16 DDR DRAM, Top Boot

PACKAGE MODIFIER

B = 133-ball, 8x8 mm, FBGA MCP

PACKAGE AND MATERIAL TYPE

AH = Thin profile Fine-pitch BGA Pb-free Low-Halogen MCP (0.5 mm pitch)

DDR DRAM AND DATA FLASH DENSITY

D0 = 128 Mb DDR, No Data Flash

E0 = 256 Mb DDR, No Data Flash

PROCESS TECHNOLOGY

R = 65 nm, MirrorBit® Technology

CODE FLASH DENSITY

128 = 128 Mb

256 = 256 Mb

PRODUCT FAMILY

S72XS Multi-Chip Product (MCP)

1.8 V Address-High, Address-Low, Data Multiplexed, SRW, Burst Mode Flash and DDR

DRAM on Split Bus

Valid Combinations

Flash and

Product Code Flash Process DDR Density Package Type/ RAM Bus and DDR Speed,

Family Density (Mb) Technology (Mb) Material Flash Boot DDR Vendor Packing Type

128 D0 E, 6 (Note 4)

S72XS R AHB H 0, 3 (Note 1)

256 E0 1

Notes:

1. Packing Type 0 is standard. Specify other options as required.

2. BGA package marking omits leading “S” and packing type designator from ordering part number.

3. Valid Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm

availability of specific valid combinations and to check on newly released combinations.

4. Flash and DDR Speed/Vendor combination '6' is not recommended for new designs.

August 19, 2010 S72XS-R_00_05 S72XS-R Based MCPs 7

Data Sheet (Advan ce Infor m a tio n)

7. Physical Dimensions

7.1 RSC133—133-ball Fine-Pitch Ball Grid Array (FBGA) 8.0 x 8.0 mm

8 S72XS-R Based MCPs S72XS-R_00_05 August 19, 2010

D at a S hee t (Adva nce In for m ation)

8. Revision History

Section Description

Revision 01 (October 7, 2008)

Initial release

Revision 02 (January 13, 2009)

Global Added section Electronic Serial Number

Revision 03 (December 18, 2009)

Global Added SDM128D166D1K OPN

Figure: Updated D-VSS and D-VSSQ connections

Product Block Diagram

Removed D-TEST signal

Physical Dimensions Updated with RSC133

Revision 04 (February 1, 2010)

Connection Diagrams Updated figure: changed Ball A2 with DNU

Revision 05 (August 19, 2010)

Global Updated references for Low Power DDR SDRAM to SDM128D166D1R

DDR Specification Reference Added reference for 256 Mb DDR DRAM

Added “not recommended for new designs” note to OPN S72XS128RD0AHBH60

Product Selector Guide Added OPN S72XS256RE0AHBH1

Removed OPN S72XS256RD0AHBHE

Updated block diagram to show common Ground

Product Block Diagram

Updated Note 1b

Updated connection diagram to show common Ground

Updated to show D-A12

Connection Diagrams

Added table to show D-Amax value for related MCP

Balls F1, M2 and M12 changed from NC to RFU

Replaced F-VSS, D-VSS, D-VSSQ with VSS

Input/Output Descriptions Corrected F-ACC to F-VPP

Refreshed descriptions for DNU, NC, RFU

Ordering Information/Valid

Updated for new OPN S72XS256RE0AHBH1

Combinations

August 19, 2010 S72XS-R_00_05 S72XS-R Based MCPs 9

Data Sheet (Advan ce Infor m a tio n)

Colophon

The products described in this document are designed, developed and manufactured as contemplated for general use, including without

limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as

contemplated (1) for any use that includes fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the

public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility,

aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for

any use where chance of failure is intolerable (i.e., submersible repeater and artificial satellite). Please note that Spansion will not be liable to

you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products. Any semiconductor

devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design

measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal

operating conditions. If any products described in this document represent goods or technologies subject to certain restrictions on export under

the Foreign Exchange and Foreign Trade Law of Japan, the US Export Administration Regulations or the applicable laws of any other country,

the prior authorization by the respective government entity will be required for export of those products.

Trademarks and Notice

The contents of this document are subject to change without notice. This document may contain information on a Spansion product under

development by Spansion. Spansion reserves the right to change or discontinue work on any product without notice. The information in this

document is provided as is without warranty or guarantee of any kind as to its accuracy, completeness, operability, fitness for particular purpose,

merchantability, non-infringement of third-party rights, or any other warranty, express, implied, or statutory. Spansion assumes no liability for any

damages of any kind arising out of the use of the information in this document.

Copyright © 2008-2010 Spansion Inc. All rights reserved. Spansion®, the Spansion logo, MirrorBit®, MirrorBit® Eclipse™, ORNAND™, EcoRAM™

and combinations thereof, are trademarks and registered trademarks of Spansion LLC in the United States and other countries. Other names

used are for informational purposes only and may be trademarks of their respective owners.

10 S72XS-R Based MCPs S72XS-R_00_05 August 19, 2010

You might also like

- BMW Icom ManualDocument16 pagesBMW Icom ManualbebeptdiverseNo ratings yet

- GME Electrophone CX294 GX294 CB Radio ImDocument12 pagesGME Electrophone CX294 GX294 CB Radio ImraymihregNo ratings yet

- Spansion SLC NAND Flash Memory For Embedded: Data SheetDocument77 pagesSpansion SLC NAND Flash Memory For Embedded: Data SheetsupNo ratings yet

- S34ML04G100TFI000Document77 pagesS34ML04G100TFI000José EduardoNo ratings yet

- Cervoz Industrial SSD 2.5inch SATA M310 Datasheet Rev2.0Document12 pagesCervoz Industrial SSD 2.5inch SATA M310 Datasheet Rev2.0liviuturcuNo ratings yet

- S25FL128S and S25FL256SDocument154 pagesS25FL128S and S25FL256SAlex JinNo ratings yet

- S29AL016D: 16 Megabit (2 M X 8-Bit/1 M X 16-Bit) CMOS 3.0 Volt-Only Boot Sector Flash MemoryDocument55 pagesS29AL016D: 16 Megabit (2 M X 8-Bit/1 M X 16-Bit) CMOS 3.0 Volt-Only Boot Sector Flash MemoryAndyNo ratings yet

- KFG 1 G 16 U 2 BDocument127 pagesKFG 1 G 16 U 2 BmbruknerNo ratings yet

- Manual Memória ddr2Document19 pagesManual Memória ddr2leoNo ratings yet

- Sata 6Gb/S SSD Controller With Nandxtend Technology: Key FeaturesDocument2 pagesSata 6Gb/S SSD Controller With Nandxtend Technology: Key FeaturesMJ ServaNo ratings yet

- Datasheet - HK S29al016j70tfi020 6599589Document58 pagesDatasheet - HK S29al016j70tfi020 6599589SAABNo ratings yet

- m500 2 5 SSDDocument37 pagesm500 2 5 SSDMark ReinhardtNo ratings yet

- Cervoz - Industrial - SSD - 2.5inch - PATA - M120 - Datasheet - Rev2.0Document12 pagesCervoz - Industrial - SSD - 2.5inch - PATA - M120 - Datasheet - Rev2.0Butterfly DraculaNo ratings yet

- Infineon-S25fl128p 128 Mbit 3.0 V Flash Memory-datasheet-V14 00-EnDocument44 pagesInfineon-S25fl128p 128 Mbit 3.0 V Flash Memory-datasheet-V14 00-EnAlexNo ratings yet

- 16gb Nand K9HBG08U1M PDFDocument45 pages16gb Nand K9HBG08U1M PDFValoha VlNo ratings yet

- Kfg1G16U2B: 1Gb Onenand B-DieDocument127 pagesKfg1G16U2B: 1Gb Onenand B-DieVeronicaGonzalezNo ratings yet

- DataSheet-Samsung SSD 840 PRO Rev12 PDFDocument4 pagesDataSheet-Samsung SSD 840 PRO Rev12 PDFMuhammad Salman SaeedNo ratings yet

- S29CD016J0MQFM01 - Flash MemoryDocument78 pagesS29CD016J0MQFM01 - Flash MemoryJhecko BalbinotNo ratings yet

- 16 Mbit / 32 Mbit / 64 Mbit (x16) Multi-Purpose Flash PlusDocument32 pages16 Mbit / 32 Mbit / 64 Mbit (x16) Multi-Purpose Flash PlussaikumarNo ratings yet

- DDR SDR Sdram ComparisionDocument12 pagesDDR SDR Sdram ComparisionSrinivas CherukuNo ratings yet

- ddr3 Product Guide Dec 12-0 PDFDocument32 pagesddr3 Product Guide Dec 12-0 PDFArturo AvilaNo ratings yet

- 5400 SSD Tech Prod SpecDocument10 pages5400 SSD Tech Prod SpecCalfin JustinusNo ratings yet

- Aps1845008g Safd18s4 - 20120323 779454Document21 pagesAps1845008g Safd18s4 - 20120323 779454Sergio AcunaNo ratings yet

- DM - SM2258XTDocument2 pagesDM - SM2258XTMarcos Henrique Aristides50% (2)

- Hitachi Accelerated Flash 2.0Document26 pagesHitachi Accelerated Flash 2.0KurniaNo ratings yet

- Id SD Catalog eDocument4 pagesId SD Catalog ealltheloveintheworldNo ratings yet

- Kingston SSD 480gb Sm2280s3g2 - enDocument2 pagesKingston SSD 480gb Sm2280s3g2 - enengg.aliNo ratings yet

- C400 2.5-Inch SATA NAND Flash SED SSDDocument34 pagesC400 2.5-Inch SATA NAND Flash SED SSDPatricio CarrascoNo ratings yet

- 2Gb DDR2Document140 pages2Gb DDR2Simas ŽalaNo ratings yet

- SST 39VF1601Document32 pagesSST 39VF1601rogj19No ratings yet

- M600 2.5-Inch SATA NAND Flash SSD: Mtfddak128Mbf, Mtfddak256Mbf, Mtfddak512Mbf, Mtfddak1T0Mbf FeaturesDocument37 pagesM600 2.5-Inch SATA NAND Flash SSD: Mtfddak128Mbf, Mtfddak256Mbf, Mtfddak512Mbf, Mtfddak1T0Mbf Featuressvetislav_vuksanovicNo ratings yet

- MTFDDAV128MBF MicronDocument38 pagesMTFDDAV128MBF MicronishtarfordrNo ratings yet

- ACPI Embedded SATAIII mSATA SSD MSS4Q-L 3K PE Datasheet 20190611Document16 pagesACPI Embedded SATAIII mSATA SSD MSS4Q-L 3K PE Datasheet 20190611Daniel CrespoNo ratings yet

- Cervoz - Industrial - SSD - 2 5 - Inch - SATA - M335 - Datasheet - Rev2Document20 pagesCervoz - Industrial - SSD - 2 5 - Inch - SATA - M335 - Datasheet - Rev2saqib khalilNo ratings yet

- Travelstar 7K320: 2.5-Inch High-Performance Hard DrivesDocument2 pagesTravelstar 7K320: 2.5-Inch High-Performance Hard Drivesamerican_guy10No ratings yet

- Samsung PDFDocument23 pagesSamsung PDFMALIK TASNEEMNo ratings yet

- Prix 1.1.19 Serveur Rackable (Serveur de Gestion) - 08022024Document2 pagesPrix 1.1.19 Serveur Rackable (Serveur de Gestion) - 08022024y.semlaliNo ratings yet

- M500it - mSATA - IndustrialDocument37 pagesM500it - mSATA - IndustrialTomasVileikisNo ratings yet

- 512mb Ddrii Sdram A3r12e30cbf-ZentelDocument74 pages512mb Ddrii Sdram A3r12e30cbf-ZentelYonathan CoronaNo ratings yet

- Multi Tier Caching Technology White Paper 2017Document5 pagesMulti Tier Caching Technology White Paper 2017Nael SianiparNo ratings yet

- 256 MB DDR2Document128 pages256 MB DDR2dhdeshanmugamNo ratings yet

- Embedded Memory: Integrated Circuit Engineering CorporationDocument15 pagesEmbedded Memory: Integrated Circuit Engineering Corporationjt_cute273759No ratings yet

- ds890 Ultrascale Overview-1591529Document52 pagesds890 Ultrascale Overview-1591529paulbluefieldNo ratings yet

- XCKU115-1FLVF1924 I in Stock at Kynix - XILINX IC FPGA KINTEX-U 1924FCBGADocument44 pagesXCKU115-1FLVF1924 I in Stock at Kynix - XILINX IC FPGA KINTEX-U 1924FCBGAling1995No ratings yet

- Continuity of SpecificationsDocument61 pagesContinuity of Specificationsshatruddha123No ratings yet

- 200b z11m Non-Auto Lpddr4 Lpddr4xDocument304 pages200b z11m Non-Auto Lpddr4 Lpddr4xAkash Sky GajjarNo ratings yet

- Apacer SH250 CFast BiCS5 AA2 259XXX XXXF8 Spec v1 - 3107240Document24 pagesApacer SH250 CFast BiCS5 AA2 259XXX XXXF8 Spec v1 - 3107240ManunoghiNo ratings yet

- General Description: Ultrascale Architecture and Product Data Sheet: OverviewDocument50 pagesGeneral Description: Ultrascale Architecture and Product Data Sheet: Overviewismail topcuNo ratings yet

- DDR4 vs. DDR5 - BlogDocument6 pagesDDR4 vs. DDR5 - BlogFelipe GonzalezNo ratings yet

- SAMSUNG K4AAG045WB-MCRC x4 DDP 16G B DDR4 R1.0 Oct.16Document69 pagesSAMSUNG K4AAG045WB-MCRC x4 DDP 16G B DDR4 R1.0 Oct.16Luis Nguyen (UHAN)No ratings yet

- 100-xBMSH-VDCTM - MUSE-D MsataDocument14 pages100-xBMSH-VDCTM - MUSE-D MsataRivaldo GomesNo ratings yet

- X25-E DataSheet PDFDocument24 pagesX25-E DataSheet PDFbilllanadeNo ratings yet

- S29AL016J - bootSectorFlashDocument58 pagesS29AL016J - bootSectorFlashqwertyuNo ratings yet

- 1H'09 Product CatalogDocument20 pages1H'09 Product Catalogmartinm76uyNo ratings yet

- DiskOnChip Based MCP01 Rev0.4Document146 pagesDiskOnChip Based MCP01 Rev0.4spotNo ratings yet

- Flash Fmnd2go8u3dDocument40 pagesFlash Fmnd2go8u3dGuilherme Ribeiro BarbosaNo ratings yet

- AS2258Document7 pagesAS2258Gunter BragaNo ratings yet

- S29AL032D: 32 Megabit CMOS 3.0 Volt-Only Flash Memory 4 M X 8-Bit Uniform Sector 4 M X 8-Bit/2 M X 16-Bit Boot SectorDocument68 pagesS29AL032D: 32 Megabit CMOS 3.0 Volt-Only Flash Memory 4 M X 8-Bit Uniform Sector 4 M X 8-Bit/2 M X 16-Bit Boot SectorDiego Armando MoralesNo ratings yet

- s846 SAS SSD DSDocument2 pagess846 SAS SSD DSsdkfkdsNo ratings yet

- Administrator & Helpdesk Interview Questions You'll Most Likely Be AskedFrom EverandAdministrator & Helpdesk Interview Questions You'll Most Likely Be AskedNo ratings yet

- Fuzzy Mras PMSMDocument6 pagesFuzzy Mras PMSMFrancisco Liszt Nunes JuniorNo ratings yet

- ET7102-Microcontroller Based System Design PDFDocument11 pagesET7102-Microcontroller Based System Design PDFRamKumarNo ratings yet

- Design of 400 220 132 KV 1316 MW Power SubstationDocument117 pagesDesign of 400 220 132 KV 1316 MW Power SubstationAHMED YOUSEF100% (1)

- HMI Cab 49 ProfaceDocument1 pageHMI Cab 49 ProfaceTung HoangNo ratings yet

- EE1/EIE1: Introduction To Signals and Communications MATLAB ExperimentsDocument9 pagesEE1/EIE1: Introduction To Signals and Communications MATLAB ExperimentsHemanth pNo ratings yet

- Program For Interfacing 8279: 1. 8085 Microprocessor Kit 2. 8279 Interfacing Module 3. Power SupplyDocument21 pagesProgram For Interfacing 8279: 1. 8085 Microprocessor Kit 2. 8279 Interfacing Module 3. Power SupplySubhashini MurugesanNo ratings yet

- Manual Do Coletor de Dados mc9090gDocument96 pagesManual Do Coletor de Dados mc9090gVirginia BarbosaNo ratings yet

- Q4 Grade9 W1 CSSDocument8 pagesQ4 Grade9 W1 CSSREYNALDO R. DE LA CRUZ JR.No ratings yet

- Upper Khimti-2 HPP Desk StudyDocument11 pagesUpper Khimti-2 HPP Desk StudyManoj BaralNo ratings yet

- XGB 20,30-40 112,122Document303 pagesXGB 20,30-40 112,122re_jackNo ratings yet

- Thin Light Catalog 2 2019 LamparasDocument33 pagesThin Light Catalog 2 2019 LamparasWIlliam RosasNo ratings yet

- Rapid Electrochemical Assessmentof PaintDocument27 pagesRapid Electrochemical Assessmentof PaintGennady KozyukinNo ratings yet

- 1830 PSS-4 R5-1 EN DataSheetDocument6 pages1830 PSS-4 R5-1 EN DataSheetramthe1No ratings yet

- Super ElfDocument56 pagesSuper ElfbillybobwackadooNo ratings yet

- Saffire Usb ManualDocument1 pageSaffire Usb ManualClaudio Villagra Revisor ArqNo ratings yet

- M400 D4N 003Document19 pagesM400 D4N 003Mian FahimNo ratings yet

- Simence CatalogueDocument76 pagesSimence CatalogueMadhabdi power plantNo ratings yet

- Wohnerusa Busbars PDFDocument40 pagesWohnerusa Busbars PDFwmNo ratings yet

- Final YearDocument13 pagesFinal YearYoudhishter RajNo ratings yet

- 07 - LTE Radio Planning CapacityDocument16 pages07 - LTE Radio Planning CapacityAdil EljaafariNo ratings yet

- KENWOOD TS 870S Mods1 SchematicDocument6 pagesKENWOOD TS 870S Mods1 SchematicLuis CarlosNo ratings yet

- HEF 4894BT Painel AxorDocument15 pagesHEF 4894BT Painel AxorJoil LeandroNo ratings yet

- ZCAR-1600A Six Phase Protective Relay Tester IntroductionDocument4 pagesZCAR-1600A Six Phase Protective Relay Tester IntroductionMagidiel AraujoNo ratings yet

- TE32 Full flow -measure points (điểm đo và vị trí solennoi)Document7 pagesTE32 Full flow -measure points (điểm đo và vị trí solennoi)Nguyễn Văn HùngNo ratings yet

- Answer Any Fivefull Questions.: Lo, G 0dband F 900 MHZ, FindpDocument2 pagesAnswer Any Fivefull Questions.: Lo, G 0dband F 900 MHZ, FindpRuturajNo ratings yet

- NSH 7 Element 2 Meter Beam AntennaDocument3 pagesNSH 7 Element 2 Meter Beam AntennaGeroldo 'Rollie' L. QuerijeroNo ratings yet

- Thermal Equivalent CurrentDocument12 pagesThermal Equivalent CurrentFiko007No ratings yet

- Current ElectricityDocument8 pagesCurrent Electricityhj48khy8jjNo ratings yet