Professional Documents

Culture Documents

Electronic System Design: Instructions: Five Questions To Be Answered With at Least One Full Question From Each Unit

Uploaded by

santosh sarafOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electronic System Design: Instructions: Five Questions To Be Answered With at Least One Full Question From Each Unit

Uploaded by

santosh sarafCopyright:

Available Formats

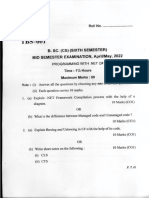

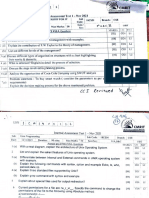

USN 16EC751

Seventh Semester B.E. Semester End Examination, Dec./Jan. 2019-20

Electronic System Design

Time: 3 Hours Max. Marks: 100

Instructions Five questions to be answered with at least one full question from each

: unit

UNIT - I L CO PO M

1 a. With an example explain Modules of SystemC

(2) (1) (1) (10 )

b. Explain Channels in SystemC

(2 ) (1) ( 1) ( 10)

OR

2 a. With example explain Processes in SystemC

(2 ) (1 ) ( 1) ( 10)

b. With example explain Events in SystemC

(2 ) ( 1) (1 ) (10 )

UNIT – II L CO PO M

3 a. Explain RTL Model of Computation

(2 ) (2) (1) (10 )

b. Explain Static Data Flow Model

(2 ) (2 ) (1 ) (10 )

OR

4 a. Explain General Structure of RTL Model

(2) (2) (1 ) (10)

b. Explain the structural diagram of Robot Controller

(2) (2) (1) (10)

UNIT - III L CO PO M

5 a. With example explain untimed dataflow model

(2) (3 ) (1) (10)

b. Explain Timed Functional Model and Process of stopping the DataFlow simulation.

Note: L (Level), CO (Course Outcome), PO (Programme Outcome), M (Marks)

(2) (3 ) (1) (10)

OR

6 a. With example explain Compile-Time Resolution of Parameters

(2) (3 ) (1) (10)

b. With example explain Elaboration-Time resolution of Parameters

(2) (3 ) (1) (10)

UNIT - IV L CO PO M

7 a. Explain basic guidelines to design an interface class

(2) (4 ) (1) (10)

b. Compare Primitive and Hierarchical Channels

(2) (4 ) (1) (10)

OR

8 a. With example explain Primitive Channels

(2) (4 ) (1) (10)

b. With example explain Hierarchical Channels

(2) (4 ) (1) (10)

UNIT -V L CO PO M

9 a. Explain the steps involved in Communication Refinement Process

(2) (5 ) (1) (10)

b. Explain Hardware-Hardware Communication Refinement Process

(2) (5 ) (1) (10)

OR

10 a. Explain the uses of high-level models in test bench

(2) (5 ) (1) (10)

b. Explain importance and the process of Tracing

(2) (5 ) (1) (10)

Note: L (Level), CO (Course Outcome), PO (Programme Outcome), M (Marks)

You might also like

- Abending Evaluation and ResolutionDocument20 pagesAbending Evaluation and Resolutionrams7869No ratings yet

- Online Voting SystemDocument26 pagesOnline Voting SystemVenkatesh Hanumandla96% (27)

- Mazak Fusion 640 Series How To Create A Backup Using RS232Document5 pagesMazak Fusion 640 Series How To Create A Backup Using RS232sunhuynh100% (2)

- Hitachi Aloka F37 - Ver.3.0-DCS PDFDocument172 pagesHitachi Aloka F37 - Ver.3.0-DCS PDFRene Galindo100% (1)

- Introduction To Information TechnologyDocument19 pagesIntroduction To Information Technologycornel tancoviciNo ratings yet

- HollySys MACS Distributed Control System 2019Document20 pagesHollySys MACS Distributed Control System 2019ASU2010No ratings yet

- Machine Learning Algorithms: Instructions: 1 - Unit I and II CompulsoryDocument3 pagesMachine Learning Algorithms: Instructions: 1 - Unit I and II Compulsorysantosh sarafNo ratings yet

- Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Document6 pagesModel Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Anshul Kumar NeekharaNo ratings yet

- Unix Modelqp@Azdocuments - inDocument9 pagesUnix Modelqp@Azdocuments - inCatherine CavyaNo ratings yet

- 18EI54Document6 pages18EI54Rocky BhaiNo ratings yet

- DIVP Model Question Paper 2023 Nov 28Document2 pagesDIVP Model Question Paper 2023 Nov 28Bujjibabu NannepagaNo ratings yet

- 18EC56Document3 pages18EC56sha istaNo ratings yet

- Computer Networks and Security: Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Document3 pagesComputer Networks and Security: Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)study materialNo ratings yet

- 6TH Sem Mid Term BSC CS 2022 April MayDocument9 pages6TH Sem Mid Term BSC CS 2022 April MayAditi RawatNo ratings yet

- 2019 May EC308-CDocument1 page2019 May EC308-CRohini JosephNo ratings yet

- Model Question Paper - With Effect From 2020-21 (CBCS Scheme)Document3 pagesModel Question Paper - With Effect From 2020-21 (CBCS Scheme)Bindu m.kNo ratings yet

- 21CS51 (Automata Theory and Compiler Design)Document4 pages21CS51 (Automata Theory and Compiler Design)Kavana KnNo ratings yet

- ML33/ML54 (O) : RamaiahDocument3 pagesML33/ML54 (O) : Ramaiahsaikar.challaNo ratings yet

- ADP T1 QPDocument2 pagesADP T1 QPAnshul Kumar NeekharaNo ratings yet

- Process Control System: Model Question Paper - 1 With Effect From 2020-21 (CBCS Scheme)Document6 pagesProcess Control System: Model Question Paper - 1 With Effect From 2020-21 (CBCS Scheme)CHAITRA G DNo ratings yet

- Digital Image Processing: Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Document3 pagesDigital Image Processing: Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)bmbzogfxhbufiwsltuNo ratings yet

- Computer Networks Kcs603 2021Document2 pagesComputer Networks Kcs603 2021Lucky rawatNo ratings yet

- Question Paper Code: 18041: Reg. NoDocument4 pagesQuestion Paper Code: 18041: Reg. NoSivakumar NNo ratings yet

- Computer Networks Kcs603Document2 pagesComputer Networks Kcs603Vijay Kumar YadavNo ratings yet

- Automata Theory and Computability: Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Document4 pagesAutomata Theory and Computability: Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)vsbNo ratings yet

- Master of Computer Applications (Revised) / Bachelor of Computer Applications (Revised) (MCA/BCA) Term-End Examination June, 2021Document2 pagesMaster of Computer Applications (Revised) / Bachelor of Computer Applications (Revised) (MCA/BCA) Term-End Examination June, 2021Krishnagopal KarNo ratings yet

- Management and Entrepreneurship For It IndustryDocument6 pagesManagement and Entrepreneurship For It IndustryShreya msNo ratings yet

- Cmrit: (B) Discuss About TheDocument7 pagesCmrit: (B) Discuss About TheSAKSHI RAINANo ratings yet

- CSC315 356 144-CSC315Document5 pagesCSC315 356 144-CSC315Aniket AmbekarNo ratings yet

- Nov Dec 20194545Document2 pagesNov Dec 20194545pecoxor808No ratings yet

- Management and Entrepreneurship For It IndustryDocument6 pagesManagement and Entrepreneurship For It Industrystudy materialNo ratings yet

- 18CS51Document6 pages18CS51Atul JhaNo ratings yet

- Os - Set 2Document2 pagesOs - Set 2saraswathiNo ratings yet

- IET DAVV 2012 MayDocument25 pagesIET DAVV 2012 Mayjainam dudeNo ratings yet

- DD&CO Model Set1 Paper 2022 SchemeDocument2 pagesDD&CO Model Set1 Paper 2022 Schemeanveshrao024No ratings yet

- BCS302 Set 1Document2 pagesBCS302 Set 1Mina KimNo ratings yet

- 18AS56Document6 pages18AS56Chand OfficialNo ratings yet

- CN QP Pattern IIDocument2 pagesCN QP Pattern IISivakumar MuthuNo ratings yet

- Automata Theory and Computability: Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Document4 pagesAutomata Theory and Computability: Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Sushmitha AcharyaNo ratings yet

- Cadcam Iat - 3 Question PaperDocument1 pageCadcam Iat - 3 Question PaperSelvaraj GNo ratings yet

- MCS 218Document2 pagesMCS 218Ujjwal BarmanNo ratings yet

- Es Iat-1Document2 pagesEs Iat-1rajaprasath560No ratings yet

- 3rd Sem Bca BSC It Jan 2023Document27 pages3rd Sem Bca BSC It Jan 2023yATHARTH TyagiNo ratings yet

- 18ec71 Test 1 2021Document3 pages18ec71 Test 1 2021Nadeem PashaNo ratings yet

- Explain About UDP and TCP Features With Neat Diagrammatic Representation.Document1 pageExplain About UDP and TCP Features With Neat Diagrammatic Representation.dineshkumarhclNo ratings yet

- Bvrajuinstitute Oftechnology, Narsap UR: Code No: A27AF R15Document1 pageBvrajuinstitute Oftechnology, Narsap UR: Code No: A27AF R15rajeshNo ratings yet

- Low - Power - VLSI - JUNE 2023Document2 pagesLow - Power - VLSI - JUNE 20231ms21ec132No ratings yet

- MAKEUPDocument3 pagesMAKEUPsaikar.challaNo ratings yet

- Communication Engineering Kec401Document2 pagesCommunication Engineering Kec401Priyanshu YadavNo ratings yet

- 18BT55Document5 pages18BT55Dr. PRADEEP M JNo ratings yet

- Os MergedDocument8 pagesOs Mergedatulo1308No ratings yet

- BAE302Document4 pagesBAE302khadkaashok72No ratings yet

- Department of Electronics and Communication Engineering: MarksDocument1 pageDepartment of Electronics and Communication Engineering: MarksGahan A V GowdaNo ratings yet

- IP - PVP23 Question BankDocument9 pagesIP - PVP23 Question Bank23501a0568No ratings yet

- FIRSTIASEP18Document1 pageFIRSTIASEP18saifz2012No ratings yet

- 02ec304 Vlsi QP 2Document2 pages02ec304 Vlsi QP 2AbhijithNo ratings yet

- Ect203 Scheme 2021Document9 pagesEct203 Scheme 2021ShakiraNo ratings yet

- Data Analytics Kit601Document2 pagesData Analytics Kit601Vijay Kumar YadavNo ratings yet

- 17me62 - Cim - I Ia - QPDocument1 page17me62 - Cim - I Ia - QPPrashanth JNo ratings yet

- Time: 1 HR 15 Min Max Marks: 20Document1 pageTime: 1 HR 15 Min Max Marks: 20Sumit JainNo ratings yet

- Ect203 Scheme 2020Document8 pagesEct203 Scheme 2020ShakiraNo ratings yet

- MCS-034 2 MCA (Revised) Term-End Examination December, 2011 Mcs-034: Software EngineeringDocument2 pagesMCS-034 2 MCA (Revised) Term-End Examination December, 2011 Mcs-034: Software Engineeringriten mitraNo ratings yet

- Share OS Model Paper2 V18Document3 pagesShare OS Model Paper2 V18Pavansaikumar SamudrapuNo ratings yet

- CT2355Document4 pagesCT2355Yash WaghmareNo ratings yet

- Design and Algo 2022 DecDocument4 pagesDesign and Algo 2022 DecMd Nisu AhmadNo ratings yet

- Attainable Region Theory: An Introduction to Choosing an Optimal ReactorFrom EverandAttainable Region Theory: An Introduction to Choosing an Optimal ReactorNo ratings yet

- Add, Assign, and Delete Project Categories - Atlassian SupportDocument1 pageAdd, Assign, and Delete Project Categories - Atlassian SupportShyamsundar VenkataramanNo ratings yet

- 0409 E12529 Ux561ua Un Q505 525 D PDFDocument104 pages0409 E12529 Ux561ua Un Q505 525 D PDFRabar TahaNo ratings yet

- Hands On Exercises 1 - Getting Started: 1. EquipmentDocument8 pagesHands On Exercises 1 - Getting Started: 1. EquipmentDoru IrimescuNo ratings yet

- Bhushan ResumeDocument7 pagesBhushan Resumebhushan.katariyaNo ratings yet

- SEBI Grade A IT 2024 Complete Guide PDFDocument16 pagesSEBI Grade A IT 2024 Complete Guide PDFsamwelch1819No ratings yet

- 104KM-QCase Study 1 CU202Document1 page104KM-QCase Study 1 CU202quaser79No ratings yet

- IIEE - IOT Legal IssuesDocument5 pagesIIEE - IOT Legal IssuesalejandroNo ratings yet

- Installing Indraworks SoftwareDocument11 pagesInstalling Indraworks SoftwareakshilNo ratings yet

- Python Course - VII Lists and TuplesDocument9 pagesPython Course - VII Lists and TuplesSwapnilSauravNo ratings yet

- Humans Bow Down To Tiktok: By: Tanisha Kulasegaran (L), Raajeshri Chandrasegaran, Rajeev Anil, Lew Wei YangDocument3 pagesHumans Bow Down To Tiktok: By: Tanisha Kulasegaran (L), Raajeshri Chandrasegaran, Rajeev Anil, Lew Wei YangTristan Brendon TannNo ratings yet

- Web Designing Course in DelhiDocument3 pagesWeb Designing Course in Delhineeti08kumariNo ratings yet

- New Method For Mobile Application Testing Using Lean Canvas To Improving The Test StrategyDocument4 pagesNew Method For Mobile Application Testing Using Lean Canvas To Improving The Test StrategyalejandraNo ratings yet

- Kaprekar NumberDocument107 pagesKaprekar Numberashwinsiva.2k23No ratings yet

- Money Making E-BookDocument7 pagesMoney Making E-BookAbdullateef IbraheemNo ratings yet

- Install STEP7 WinCC V18 enUSDocument124 pagesInstall STEP7 WinCC V18 enUSJulian David Rocha OsorioNo ratings yet

- Athlon PDFDocument12 pagesAthlon PDFEquipo 7No ratings yet

- SQL (Structured Query Language)Document11 pagesSQL (Structured Query Language)StefaniaNo ratings yet

- Sipoc Diagram: Supplier Input Process OutputDocument4 pagesSipoc Diagram: Supplier Input Process OutputAshu DeshawerNo ratings yet

- Free Google Docs Project Management Templates - SmartsheetDocument13 pagesFree Google Docs Project Management Templates - SmartsheetramsankarkmNo ratings yet

- Installation Instructions: Windows Loader 3.1.exeDocument2 pagesInstallation Instructions: Windows Loader 3.1.exekumaraNo ratings yet

- Sick LMS 511 DSDocument28 pagesSick LMS 511 DSAndrew PasqualeNo ratings yet

- CobolDocument13 pagesCobolThrinadh B JNo ratings yet

- Large Deployment of Superdoctor 5 On Windows User'S Guide: Revision 1.0DDocument16 pagesLarge Deployment of Superdoctor 5 On Windows User'S Guide: Revision 1.0DEvandro Amaral RodriguesNo ratings yet

- J58 S4hana2022 BPD en MXDocument160 pagesJ58 S4hana2022 BPD en MXIvonne Rocio MeloNo ratings yet