Professional Documents

Culture Documents

Appendix C

Appendix C

Uploaded by

Roohan Adeel0 ratings0% found this document useful (0 votes)

11 views6 pagesAppendix RTOS

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentAppendix RTOS

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

11 views6 pagesAppendix C

Appendix C

Uploaded by

Roohan AdeelAppendix RTOS

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 6

8 fege |2)2) 3) 413 e278 (Fron ayia 116] 17] 18 [19/20

28

x LO |F \D\x W

=

> DAppI \F\D \S |xX\m)S |e

os

& SD £\s |D\s|sis|x|m|e

8 . [

= DADE Els| [sl ax\m{w

ss

= DSuUB LID|s|s|x|mw

5 |

see PNG F\sisiol si slam

Bs - L012) | esis iF ip ix MW

IAD | |

+ The ftsst DADDE onwst wait until LD gets

fo the We stage to obtain the Value. of RE-

© SP must wait unt +1 the fisst DADDI Computes

dhe value of R41 curd reaches ihe Lo stage

(mo foswosdirg) :

+ DSuB must wait until. the second DADDL

- computes the value ce R2, and seaches the WB

stage:

+ BNEZ must welt util DSUB Corvputes

the value of RU and seaches the WR stage .

* LD from next ttesation is’ ve-fetched after

Hhe beanh is vesdved as taken.

Loop execctes 99 Iterations ( 3496/ %,

. ltesations Ob 98.

Total umber of cycle fos while. Loop

Is (48 +IS D418 = 1488 cycles.

Pooblem 4

C)r

Inet [1712/44 Is |o@| TS] [rwoypltfle [13 | Ie

Lo fe fol felia}

Ppa Ip \< lw

om | E SID 1X lalw

oe | > Ip D(x ml wlw

pe tt FID IX Aw

BNEX FID |S |x fray}

Lp(2) FIS|EIDI% vo

* |_}

+

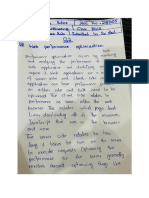

« The fist ADDL still vnust wart until (D gets

fp the WB stage to oblatn the valve of A4, but

mow shall is implemented in Ex stage »and value

is frovended divoctly to Ex slatge.

+ SD now waits Untill the fissl ADDL cornpules

and forwards the value fsom Ex fo mem,

2 PSU B mow gets the value of R2. faswaxds by

gecond APPL anc does rt need fo waits

Total Cydes ic (9Bx%9)4 12 = B44 cyeles.

Pooble

m 2,

(+ A cimple 4 stage pipe line with

pescentage -

listeve | Types Veo) 7» | Loops

i V2) 4

Non- - — |84% “i O

byanch R —

i «2 fiefs

i fiz Be

Poanchall Cals aml | |] my as fo U I

Jumps ca fi BE)

Branched Lo ante Svvoe4 1 (2 TI)

nchel] Conate-coral ly, ¢ qu, [t+ @& 2

kt (PEW

ean we 13% x ; (PRL)

Beandell Conditional No | #o% |i! in) 1

il k+l Pe) —

| OO EEO eeVOOOO

Problem 3

a):

Given

Oviginal clock cycle =

IF — 1ns, ED — dns, €x —? {ns , MEM > 2ns-

WR —> ASns and pipeline segisler delay o-4ns

Ovt of given Stage. 5

MEM. has late execvtion Five of 2ns .

Clock cycle 1 Hime = time taken by MEPA-4

pipeline vogisles delery ,

ins ( fo non- pipetinect)

=2 +04

= Ded ns

b)s We know CPE= Tleal CPL + stall cycle

“ CPL is assumed as 4,

As these is a stall ewry 4 instovetions,

So, sball cycle pes Instovetton = 1 = oy

7 >

oom CUE. 1 Os: lou

C) Speedup = Execution time fos non - rion ~ pipelined,

Executibn tine fos “pifelined

Execution time - I xcCPl xc cle

CPL =1

Speed up = Ex Ixl

Tx '2 v24

> |

2-628

Speed ep= 2-67 tines.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Sell Your CarDocument3 pagesSell Your CarRoohan AdeelNo ratings yet

- Five Band Equalizer: Signal Processing and Circuits UFMFMA-15-2 CW (Group Assignment) Small Scale ProjectDocument5 pagesFive Band Equalizer: Signal Processing and Circuits UFMFMA-15-2 CW (Group Assignment) Small Scale ProjectRoohan AdeelNo ratings yet

- Web PaperDocument22 pagesWeb PaperRoohan AdeelNo ratings yet

- Website Design Quotation TemplateDocument2 pagesWebsite Design Quotation TemplateRoohan AdeelNo ratings yet

- Agreement For RidersDocument4 pagesAgreement For RidersRoohan AdeelNo ratings yet

- Tag Line:: Haseen HabibDocument4 pagesTag Line:: Haseen HabibRoohan AdeelNo ratings yet

- MK InvoiceDocument1 pageMK InvoiceRoohan AdeelNo ratings yet