Professional Documents

Culture Documents

8-Channel Darlington Driver for Relays & Motors

Uploaded by

RogerOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8-Channel Darlington Driver for Relays & Motors

Uploaded by

RogerCopyright:

Available Formats

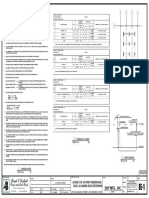

8-Channel Darlington Current Driver TD62783A

FEATURES

• 8 Darlington Arrays per Package

• Minus 500 mA (Source) Output Current (Single Output)

• Output voltage 50V

• Output Clamp Diodes

• Input Compatible with Various Types of Logic

• Relay-Driver Applications SOP-18

• Input pins placed opposite to output pins to simplify

layout

APPLICATION

• Relay Drivers

• Stepper and DC Brushed Motor Drivers DIP-18

• Lamp Drivers

• Display Drivers

• Line Drivers

• Logic Buffers

ORDERING INFORMATION

Device Package

DESCRIPTION

TD62783AD SOP-18

The TD62783A is monolithic high-voltage, high-current

TD62783AN DIP-18

Darlington transistor arrays. Each consists of eight

NPN Darlington pairs that feature high-voltage outputs

with common-anode clamp diodes for switching

inductive loads. The collector-current rating of a single

Darlington pair is minus 500 mA. The Darlington pairs

may be paralleled for higher current capability.

Applications include relay drivers, hammer drivers,

lamp drivers, display drivers (LED and gas discharge),

line drivers, and logic buffers.

ABSOLUTE MAXIMUM RATINGS (Note 1,2)

CHARACTERISTIC SYMBOL MIN. MAX. UNIT

Supply Voltage VCC - 50 V

Input Voltage VIN - 15 V

Output Current IOUT - −500 mA

Clamp Diode Reverse Voltage VR - 50 V

Clamp Diode Forward Current IF - 500 mA

Maximum Junction Temperature TJ - 150 °C

Jun. 2020 – R1.0 1/8 HTC

8-Channel Darlington Current Driver TD62783A

RECOMMENDED OPERATIONG CONDITIONS (Note 2)

CHARACTERISTIC SYMBOL MIN. MAX. UNIT

Supply Voltage VCC - 50 V

Output Current IOUT - −350 mA

Clamp Diode Reverse Voltage VR - 50 V

Clamp Diode Forward Current IF - 400 mA

Junction Temperature TJ −40 125 °C

Operating Free-Air Temperature Range TA −40 85 °C

ORDERING INFORMATION

Package Order No. Description Package Marking Status

SOP-18 TD62783AD 8-Channel Darlington Current Driver TD62783A Active

DIP-18 TD62783AN 8-Channel Darlington Current Driver TD62783A Contact Us

Jun. 2020 – R1.0 2/8 HTC

8-Channel Darlington Current Driver TD62783A

PIN CONFIGURATION

I1 1 18 O1

I2 2 17 O2

I3 3 16 O3

I4 4 15 O4

I5 5 14 O5

I6 6 13 O6

I7 7 12 O7

I8 8 11 O8

VCC 9 10 GND

SOP-18 / DIP-18

PIN DESCRIPTION

Pin No.

Pin Name Pin Function

SOP-18 DIP-18

1 1 I1

2 2 I2

3 3 I3

4 4 I4

Channel 1 through 8 Darlington Base Input

5 5 I5

6 6 I6

7 7 I7

8 8 I8

9 9 VCC Power Supply

10 10 GND Ground

11 11 O8

12 12 O7

13 13 O6

14 14 O5

Channel 1 through 8 Darlington Emitter Output

15 15 O4

16 16 O3

17 17 O2

18 18 O1

Jun. 2020 – R1.0 3/8 HTC

8-Channel Darlington Current Driver TD62783A

PIN CONNECTION DIAGRAM

1 18

IN1 OUT1

2 17

IN2 OUT2

3 16

IN3 OUT3

4 15

IN4 OUT4

5 14

IN5 OUT5

6 13

IN6 OUT6

7 12

IN7 OUT7

8 11

IN8 OUT8

9 10

VCC GND

BLOCK DIAGRAM

VCC

(C)

R3

Input R1: 10 kΩ

(B) R1 R2: 2.6 kΩ

R3: 20 kΩ

R2 R4: 10 kΩ

Output

(E) R5: 5.0 kΩ

R4 R5

GND

(COM)

Jun. 2020 – R1.0 4/8 HTC

8-Channel Darlington Current Driver TD62783A

ELECTRICAL CHARACTERISTICS (Note 3)

Limits in standard typeface are for TA=25°C, unless otherwise specified.

TEST

PARAMETER SYMBOL TEST CONDITION MIN. TYP. MAX. UNIT

FIGURE

Output Leakage Current ICEX Fig. 1 VCC = 50V, VIN = 0.4V - - 100 µA

VIN = 2V, IOUT = −100mA - - 1.8

Collector-Emitter

VCE(SAT) Fig. 2 VIN = 2V, IOUT = −225mA - - 1.9 V

Saturation Voltage

VIN = 2V, IOUT = −350mA - - 2.0

VIN = 2.4V - - 52

Input Current IIN(ON) Fig. 3 µA

VIN = 3.85V - - 260

Input Voltage at ON state VIN(ON) Fig. 4 VCE = 2.0V, IOUT = −350mA - - 2.0 V

Input Voltage at OFF state VIN(OFF) Fig. 4 IOUT = −500µA 0.8 - - V

Supply Current ICC(ON) Fig. 3 VCC = 50V, VIN = 2V - - 2.5 mA

Clamp Diode Reverse

IR Fig. 5 VR = 50V - - 50 µA

Current

Clamp Diode Forward

VF Fig. 6 IF = 350mA - - 2.0 V

Voltage

Turn-On Propagation

tON Fig. 7 VCC = 50V, RL = 125, CL = 15pF - 0.15 -

Delay Time

µs

Turn-Off Propagation

tOFF Fig. 7 VCC = 50V, RL = 125, CL = 15pF - 3.0 -

Delay Time

Note 1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These

are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated

under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for

extended periods may affect device reliability.

Note 2. All voltage values are with respect to the GND, unless otherwise noted.

Note 3. The device is not guaranteed to function outside its operating ratings.

Jun. 2020 – R1.0 5/8 HTC

8-Channel Darlington Current Driver TD62783A

PARAMETER MEASUREMENT INFORMATION

VCC VCC

VCE(SAT)

IOUT

VIN ICEX VIN

Fig. 1. ICEX Test Circuit Fig. 2. VCE(SAT) Test Circuit

VCC VCC

ICC

IIN(ON) VCE

VIN VIN IOUT

Fig. 3. IIN(ON), ICC Test Circuit Fig. 4. VIN(ON), VIN(OFF) Test Circuit

VCC Open

Open Open

IR VR IF VF

Fig. 5. IR Test Circuit Fig. 6. VF Test Circuit

tr tf

VCC 90%

VIH

VIN 50%

10%

0

Pulse Width

Generator tON tOFF

VIN RL CL VOH

VOUT 50%

VOL

* CL includes probe and jig capacitance. * Pulse Width 50µs, Duty Cycle 10%, tr ≤ 5ns, tf ≤ 10ns

Fig. 7. tON, tOFF Test Circuit Fig. 8. Propagation Delay Time Waveform

Jun. 2020 – R1.0 6/8 HTC

8-Channel Darlington Current Driver TD62783A

TYPICAL OPERATING CHARACTERISTICS

T.B.D.

Jun. 2020 – R1.0 7/8 HTC

8-Channel Darlington Current Driver TD62783A

REVISION NOTICE

The description in this data sheet is subject to change without any notice to describe its electrical characteristics

properly.

Jun. 2020 – R1.0 8/8 HTC

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Td62083ap J SDocument13 pagesTd62083ap J SCarlos MatosNo ratings yet

- Dual Power MOSFET Driver Features: File Number Data Sheet April 1999Document8 pagesDual Power MOSFET Driver Features: File Number Data Sheet April 1999tommyhghNo ratings yet

- Toshiba 8-channel high-voltage source driver datasheetDocument10 pagesToshiba 8-channel high-voltage source driver datasheetGeroldo 'Rollie' L. QuerijeroNo ratings yet

- UC3842B/3843B: Unisonic Technologies Co., LTDDocument11 pagesUC3842B/3843B: Unisonic Technologies Co., LTDvannadioNo ratings yet

- Unisonic Technologies Co., LTD: Telephone Tone RingerDocument5 pagesUnisonic Technologies Co., LTD: Telephone Tone Ringerzero cloudNo ratings yet

- LM 386Document7 pagesLM 38619thmnlfreemsNo ratings yet

- Unisonic Technologies Co., LTD: Eight High Voltage, High Current Darlington ArraysDocument5 pagesUnisonic Technologies Co., LTD: Eight High Voltage, High Current Darlington ArraysTojo BasheerNo ratings yet

- TBD62304AFNG Datasheet en 20170324-1313625Document11 pagesTBD62304AFNG Datasheet en 20170324-1313625basheer almetwakelNo ratings yet

- 5-V Low-Drop Voltage Regulator TLE 4260Document15 pages5-V Low-Drop Voltage Regulator TLE 4260marce822No ratings yet

- TLE4260Document15 pagesTLE4260NoelNo ratings yet

- LM386 Linear Integrated Circuit Specification SheetDocument7 pagesLM386 Linear Integrated Circuit Specification SheetEmmanuel AlvarezNo ratings yet

- FZT Sgs-Thomson: Tl082 7 # Likmiijoirirmoos Tl082A-Tl082BDocument10 pagesFZT Sgs-Thomson: Tl082 7 # Likmiijoirirmoos Tl082A-Tl082BMarwa mbrtNo ratings yet

- DatasheetDocument8 pagesDatasheetduc vinhNo ratings yet

- 4274GV50 5v Regulator PDFDocument13 pages4274GV50 5v Regulator PDFvanadium0No ratings yet

- Datasheet FAN8082 (KA3082N) PDFDocument12 pagesDatasheet FAN8082 (KA3082N) PDFJose BenavidesNo ratings yet

- TD62083APG, TD62083AFG, TD62084APG, TD62084AFG: 8ch Darlington Sink DriverDocument13 pagesTD62083APG, TD62083AFG, TD62084APG, TD62084AFG: 8ch Darlington Sink DriverEdgar DauzonNo ratings yet

- IRAMS10UP60A Integrated Power Module for Appliance Motor DriveDocument18 pagesIRAMS10UP60A Integrated Power Module for Appliance Motor DriveAnselmo LimaNo ratings yet

- Uita6586 0001Document4 pagesUita6586 000111031974didinNo ratings yet

- 7912CT EtcDocument13 pages7912CT EtcCuong TranNo ratings yet

- HF/VHF Applications RF & Microwave Transistors: Pin ConnectionDocument5 pagesHF/VHF Applications RF & Microwave Transistors: Pin Connectionbellscb100% (1)

- Toshiba 8-Channel High Voltage Source DriverDocument10 pagesToshiba 8-Channel High Voltage Source DriverLider Ch CuevaNo ratings yet

- TDA2822Document6 pagesTDA2822josetantonioNo ratings yet

- HD74LS02: Quadruple 2-Input Positive NOR GatesDocument6 pagesHD74LS02: Quadruple 2-Input Positive NOR GatesStevhen Dem SonNo ratings yet

- TVL ST23 04 Ad0Document9 pagesTVL ST23 04 Ad0coulsonpfilNo ratings yet

- IXDD414Document11 pagesIXDD414CHARIS ZEVGARASNo ratings yet

- 7915Document13 pages7915ysfhkNo ratings yet

- Amplificador de Audio Samsung MAX DC650Document9 pagesAmplificador de Audio Samsung MAX DC650Enya Andrea Ribba HernandezNo ratings yet

- 3A Single-CH DC Motor Driver Circuit RZ7889: FeaturesDocument4 pages3A Single-CH DC Motor Driver Circuit RZ7889: Featuresmohmd zubaaNo ratings yet

- DatasheetDocument17 pagesDatasheetAlaa Ibrahem AhmedNo ratings yet

- TD62164APG, TD62164AFG: 4ch High-Current Darlington Sink DriverDocument12 pagesTD62164APG, TD62164AFG: 4ch High-Current Darlington Sink DriversyahabdulrizalNo ratings yet

- DP8212Document10 pagesDP8212Toat Nur AlfianNo ratings yet

- Data Sheet TLE4262G Regulador 5v 20 PinesDocument16 pagesData Sheet TLE4262G Regulador 5v 20 Pinesaagreco73No ratings yet

- TEA1620P: 1. General DescriptionDocument16 pagesTEA1620P: 1. General DescriptionJose BenavidesNo ratings yet

- Synchronous Rectifier Driver: Description ApplicationsDocument7 pagesSynchronous Rectifier Driver: Description ApplicationsJorge BlomdahlNo ratings yet

- CA3450Document8 pagesCA3450MUHAMMAD SISWANTORONo ratings yet

- RP108J Series: Low Input Voltage 3A LDO Regulator OutlineDocument29 pagesRP108J Series: Low Input Voltage 3A LDO Regulator OutlineArie DinataNo ratings yet

- IP4002CR DatasheetDocument7 pagesIP4002CR DatasheetJose BenavidesNo ratings yet

- INPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Document8 pagesINPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Isaac CostaNo ratings yet

- LOW POWER QUAD OP AMPSDocument11 pagesLOW POWER QUAD OP AMPSАлександрNo ratings yet

- Dual Channel OTL Audio Power Amplifier IC Data SheetDocument8 pagesDual Channel OTL Audio Power Amplifier IC Data SheetJose M PeresNo ratings yet

- TD62591APGDocument11 pagesTD62591APGThein Htoon lwinNo ratings yet

- ULN2804Document5 pagesULN2804vka_princeNo ratings yet

- Reliable General Purpose Relay with Long LifeDocument7 pagesReliable General Purpose Relay with Long Lifevalimorsk ltd.No ratings yet

- L7900 Series: Negative Voltage RegulatorsDocument13 pagesL7900 Series: Negative Voltage Regulatorsmhd_almahayniNo ratings yet

- 74LVT16244 - 74LVTH16244 Low Voltage16-Bit Buffer/Line Driver With 3-STATE OutputsDocument7 pages74LVT16244 - 74LVTH16244 Low Voltage16-Bit Buffer/Line Driver With 3-STATE OutputsLelik GhhNo ratings yet

- Infineon Tle7230r Ds v03 04 enDocument15 pagesInfineon Tle7230r Ds v03 04 enياسين الطنفوريNo ratings yet

- Unisonic Technologies Co., LTD: 4 Pin Dip Phototransistor PhotocouplerDocument7 pagesUnisonic Technologies Co., LTD: 4 Pin Dip Phototransistor PhotocouplerAbdul Rauf MughalNo ratings yet

- YG4558/E/L: Dual Operational AmplifierDocument7 pagesYG4558/E/L: Dual Operational AmplifierJoel Rondinel PachecoNo ratings yet

- DatasheetDocument9 pagesDatasheetjim campbellNo ratings yet

- AN15525A Data Sheet: Semiconductor IC for CRT Vertical Deflection OutputDocument7 pagesAN15525A Data Sheet: Semiconductor IC for CRT Vertical Deflection OutputDede Tuhadi PrayitnoNo ratings yet

- stp110n8f6 230421 205435Document14 pagesstp110n8f6 230421 205435Andres PaezNo ratings yet

- Complete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesDocument15 pagesComplete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesIgor LabutinNo ratings yet

- Unisonic Technologies Co., LTD: Multiple Rs-232 Drivers and ReceiversDocument10 pagesUnisonic Technologies Co., LTD: Multiple Rs-232 Drivers and ReceiversRamon Alexander PradaNo ratings yet

- 3.3V Octal Buffer/line Driver With 30 Series Termination Resistors (3-State)Document11 pages3.3V Octal Buffer/line Driver With 30 Series Termination Resistors (3-State)Dwp BhaskaranNo ratings yet

- HD74LS00PDocument5 pagesHD74LS00PBIMO MODELADONo ratings yet

- VC201, VC202, VC203Document36 pagesVC201, VC202, VC203RogerNo ratings yet

- Tachometers and Tach/Hourmeters: AT and ATH SeriesDocument2 pagesTachometers and Tach/Hourmeters: AT and ATH SeriesRogerNo ratings yet

- Totalcomp - t500 BrochureDocument2 pagesTotalcomp - t500 BrochureRogerNo ratings yet

- Tuerca de Seguridad Con PrisioneroDocument1 pageTuerca de Seguridad Con PrisioneroRogerNo ratings yet

- Manual U en 38Document89 pagesManual U en 38ramdarkmasterNo ratings yet

- Wieland R1.190.0100.0 ManualDocument62 pagesWieland R1.190.0100.0 ManualRogerNo ratings yet

- IGBT - Basic - 1 EE TimeDocument11 pagesIGBT - Basic - 1 EE TimeRichard TsengNo ratings yet

- Panasonic tc-21fj30p Chassis gp3Document30 pagesPanasonic tc-21fj30p Chassis gp3Prabir Kumar SurNo ratings yet

- NORSOK E 001 Requirements PDFDocument9 pagesNORSOK E 001 Requirements PDFP Venkata SureshNo ratings yet

- Electr - Connect.diagram: Neutraubling PlantDocument238 pagesElectr - Connect.diagram: Neutraubling PlantAhmedNo ratings yet

- Ingecon Sun 1165tl b420 IndoorDocument4 pagesIngecon Sun 1165tl b420 IndoorfdasfNo ratings yet

- Esd Makilan Jhon Experiment 3 Indiv ReportDocument8 pagesEsd Makilan Jhon Experiment 3 Indiv ReportJhon MakilanNo ratings yet

- The Zener Diode orDocument1 pageThe Zener Diode orLupu DanielNo ratings yet

- PST Unit 2Document12 pagesPST Unit 2Karthick Sivakumar ChellamuthuNo ratings yet

- PC923Document6 pagesPC923David JuarezNo ratings yet

- Boglinf: How To BuildDocument36 pagesBoglinf: How To BuildWillian LopesNo ratings yet

- Idc (Industrial Drives and Control)Document4 pagesIdc (Industrial Drives and Control)Savan RathodNo ratings yet

- Type Examination Certificate: Ii 3 G Ex Ec Iic GCDocument3 pagesType Examination Certificate: Ii 3 G Ex Ec Iic GCabdur rafayNo ratings yet

- Oc and SC Tests On A Single-Phase Transformer: Experiment No. 1Document5 pagesOc and SC Tests On A Single-Phase Transformer: Experiment No. 1Abuturab MohammadiNo ratings yet

- Francis Francis x1 Espresso Machine Circuit Board Schematic and Wiring Diagram v2Document2 pagesFrancis Francis x1 Espresso Machine Circuit Board Schematic and Wiring Diagram v2frox123100% (2)

- Industrial Batten Light for Workshops and FactoriesDocument6 pagesIndustrial Batten Light for Workshops and FactoriesARIJIT KUNDUNo ratings yet

- SMPSBuckDesign 031809Document17 pagesSMPSBuckDesign 031809shaheerdurraniNo ratings yet

- Rain AlramDocument7 pagesRain AlramFatima Azam Chattha100% (2)

- X Ray Condition ProhibiDocument9 pagesX Ray Condition ProhibiJessica HrovatinNo ratings yet

- DC-325 Ceiling Fan Instruction ManualDocument15 pagesDC-325 Ceiling Fan Instruction ManualKeziah SantosNo ratings yet

- Multiple Choice Question (MCQ) of Alternator and Synchronous Motors PageDocument29 pagesMultiple Choice Question (MCQ) of Alternator and Synchronous Motors Pagekibrom atsbha0% (1)

- Capacitor Lab For PhetDocument8 pagesCapacitor Lab For PhetKarlo AnibanNo ratings yet

- This Is Brochure-Trafo-Auto-Centrado-type-DryDocument1 pageThis Is Brochure-Trafo-Auto-Centrado-type-DryfendynovapamelaNo ratings yet

- Hydraulic Excavator PC200-8 PC200LC-8 PC220-8 PC220LC-8: 90 Diagrams and DrawingsDocument5 pagesHydraulic Excavator PC200-8 PC200LC-8 PC220-8 PC220LC-8: 90 Diagrams and Drawingsari100% (3)

- Insulect+Switchgear+ +Link+Box+and+SVL+A4+V2019 1Document6 pagesInsulect+Switchgear+ +Link+Box+and+SVL+A4+V2019 1Sara FahmyNo ratings yet

- +B Signal Line: - B Signal Line: Q5951 2SB0621AHADocument1 page+B Signal Line: - B Signal Line: Q5951 2SB0621AHAwilfreddelgadoNo ratings yet

- Technical Data Sheet - 250kva TransformersDocument2 pagesTechnical Data Sheet - 250kva TransformerspavanNo ratings yet

- IEC Categories Contactor PDFDocument1 pageIEC Categories Contactor PDFasalasv65No ratings yet

- What Is The Turns Ratio For A Resistance Welding Transformer - How-To Resistance WeldDocument4 pagesWhat Is The Turns Ratio For A Resistance Welding Transformer - How-To Resistance Weldmohamed lamine elbiskriNo ratings yet

- Dkp-E1-12 4 2023Document1 pageDkp-E1-12 4 2023Alvin DeliroNo ratings yet

- Chapter 8 Power PointDocument31 pagesChapter 8 Power PointABCDNo ratings yet