Professional Documents

Culture Documents

Analysis of Various Memory Circuits Used in Digital VLSI

Uploaded by

AdiseshuMiddeCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analysis of Various Memory Circuits Used in Digital VLSI

Uploaded by

AdiseshuMiddeCopyright:

Available Formats

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

Analysis of Various Memory Circuits Used In Digital VLSI

Tanvi Upaskar, Ganesh Thorave, Prof. Sumita G*, Mayuresh Yerandekar, Siddhesh Mahadik

K C College of Engineering and Management Studies Thane, India

Corresponding author’s email id: sumitagupta128@gmail.com*

DOI: http://doi.org/10.5281/zenodo.2652717

Abstract

This paper presents comparison of semiconductor memory circuits such as

volatile memories like SRAM, DRAM and non-volatile memories like ROM,

PROM, EPROM, EEPROM, FLASH (NOR based & NAND based). This

comparison is on the basis of some parameters including read speed, write

speed, volatility, bits/cell, cell structure, cell density, power consumption,

etc. In this paper we also focused on applications of those memory cells

based on their characteristics. This paper presents the appropriate choice

for selecting memory circuit with the read-write speed, capacity, power

consumption.

Keywords: Semiconductor memories, Volatility, Flash memory, memory

cell, digital.

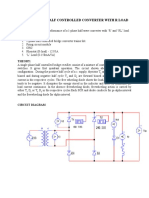

INTRODUCTION non-volatile memory (which holds its data

Semiconductor memory cells are capable even if the power is turned off). (See

of storing large quantities of digital Figure:-1)

information, essential to all digital

systems. It is an essential element of VOLATILE MEMORY

today's technical world. With the rapid Volatile memory needs power to maintain

growth in the requirement for the stored information; it retains its

semiconductor memories there have been contents while powered on but when the

many types of memory that have emerged. power is interrupted, the stored data is

There are basically two types of memory quickly lost. Volatile memory has many

such as Volatile memory (which maintains uses including as primary storage

its data while the device is powered) and

34 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

In addition to usually being faster than information, as it becomes unavailable on

forms of mass storage such as a hard disk power-down.[4]

drive, volatility can protect sensitive

Figure:-1

A. Dynamic Random Access Memory

Dynamic random-access memory is a type of random access semiconductor memory that

stores each bit of data in a different capacitor within an integrated circuit. The capacitor can

either be charged or discharged; these two states are used to represent the two values of a bit,

conventionally called 0 and 1.

Figure:-2

35 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

A typical 1-bit DRAM cell is shown in SRAM, but it is much more widely used.

Figure 2. The capacitor CS stores the The advantage of DRAM is the structural

charge for the cell. Transistor M1 gives the simplicity of its memory cells: only one

R/W access to the cell. CB is the transistor and a capacitor are required.

capacitance of the bit line per unit length. This allows DRAM to reach very high

Memory cells are etched onto a silicon densities, making DRAM much cheaper

wafer in an array of columns (bit lines) per bit. The transistors and capacitors used

and rows (word lines). are extremely small; billions can fit on a

single memory chip. Due to the dynamic

The intersection of a bit line and word line nature of its memory cells, DRAM uses

constitutes the address of the memory cell. relatively large amounts of power.[3]

DRAM works by sending a charge through

the appropriate column (CAS) to activate B. Static Random Access Memory

the transistor at each bit in the column. Static random-access memory is a type of

When writing, the row lines contain the semiconductor memory that uses bistable

state the capacitor should take on. When latching circuitry (flip-flop) to store each

reading, the sense amplifier determines the bit. SRAM exhibits data remanence, but it

level of charge in the capacitor if it is more is still volatile in the conventional sense

than 50%, it reads it as "1"; otherwise it that data is eventually lost when the

reads it as "0". memory is not powered.

One of the problems with this arrangement

is that capacitors do not hold their charge

indefinitely as there is some leakage across

the capacitor. It will not be acceptable for

the memory to lose its data, and to

overcome this problem the data is

periodically refreshed. The data is sensed

and written and it then ensures that any

leakage is overcome, and the data is re-

instated. Due to its need of a system to Fig. 2 – 6T SRAM cell

refreshing, DRAM has more complexed

circuitry and timing requirements than

36 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

6T-SRAM cell is shown in fig 2. SRAM needed to be refreshed and due to their

takes 6 transistors to store a 1 bit. It has latching arrangement. Due to its high

three input ports (BL, BL bar, WL) and speed the SRAM is also used as the cache

two output ports (Q,Qbar). In Fig. M5 and memory and also the main memory in the

M6 are access transistors, M2 and M4 pull servers for providing the best performance

up, M1 and M3 are pull down transistors. to the users.[3]

SRAM has basic three operations.

NON-VOLATILE MEMORY

Hold operation: For Hold Operation both A drawback of volatile memory structures

access transistors must be turned OFF such as DRAM and SRAM is that the

(M5=M6=0). Due to presence of latching stored data is lost in the absence power

element SRAM hold its state. supply. To overcome this problem, various

types of non-volatile memory have been

Read Operation: For Read operation both proposed. Non-volatile memory (NVM) is

bit lines (BL, BL bar) must be precharged a type of computer memory that has the

to VDD and access transistors must be turn ability to hold saved data even if the power

on (M5=M6=1). Based data value stores is turned off. Unlike volatile memory,

any one of bit line is discharge and the NVM does not require its memory data to

voltage difference between two bit lines is be periodically refreshed. It is commonly

sensed by sense amplifier and we are able used for secondary storage or long-term

to detect what is present in memory. consistent storage. Non-volatile memory is

highly popular among digital media; it is

Write Operation: The data which we want widely used in memory chips for USB

to write in the memory is given to bit line memory sticks and digital cameras. Non-

and access transistors are turn volatile memory eradicates the need for

on(M5=M6=1) and we are able to write relatively slow types of secondary storage

the data. systems, including hard disks.[4]

In one memory bit there are 6 transistors Read Only Memory

of SRAM which makes the SRAM bulky. Read-only memory (ROM), also known as

It needs the more space for the storage firmware, is an integrated circuit

purpose. the speed of the SRAM is much programmed with specific data when it is

faster than the DRAM as they are not manufactured. ROM chips are not only

37 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

used in computers, but in most other B. Programmable Read Only Memory

electronic items as well. ROM-memory PROM is read-only memory that can be

does not allow for deletion; it cannot be modified only once by a user. The user

overwritten by the user's program buys a blank PROM and enters the desired

commands. Therefore, all programs and contents using a PROM program. Inside

data are supposed to be in the ROM to be the PROM chip, there are small fuses

installed through the production process. which are burnt open during programming.

This is done using a "ROM-Mask" which It can be programmed only once and is not

contains all the data and is used during the erasable.[2]

processing of the silicon chip.

C. Erasable Programmable Read Only

Memory

An EPROM is erased by shining

ultraviolet light on the cells through a

transparent window in the package. The

UV radiation renders the oxide slightly

conductive by direct generation of an

electron-hole pair in the material. The

erasure process is slow and can take from

Fig. 3- ROM array

seconds to several minutes, depending on

the intensity of the UV source.

At first sight, the limitation of the

Programming takes several (5-10)

irreversible writing process seems to be a

microseconds / word. Another problem

disadvantage. But it also discourages

with the process is limited endurance, that

potential attackers to modify the program

is, the number of erase / program cycles

code on less secure chip cards.

are generally limited to maximum of 1000,

mainly due to UV erase procedure.

The two different types of implementation

Reliability is also an issue. The device

of ROM array are –

threshold may vary with repeated

NOR based ROM array

programming cycles. Most EPROM

NAND based ROM array

memories therefore contain an on-chip

circuitry to control the value of the

thresholds within a specified range during

38 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

programming. Finally, the injection always device that can be implemented with fewer

entails a large channel current, as high as standards in cell design. The more

0.5mA at a control gate voltage of 12.5V. common cell is composed of two

This causes high power dissipation during transistors. The storage transistor has a

programming. The EPROM cell is floating gage similar to the EPROM. The

extremely simple and dense, making it EEPROM has two families which are

possible to fabricate large memories at a serial EEPROM and parallel EEPROMs.

low cost. EPROMs were therefore The parallel EEPROM is faster and cost

attractive in applications that do not effective than serial memory.[2]

require regular programming. Due to cost

and reliability issues, EPROMs have fallen E. Flash Memory

out of favor and have been replaced by The flash memory is the most widely used

Flash Memories. [2] device for electronics and computer

devices. The flash memory is among the

D. Electrically Erasable Programmable special types of memory that can be erased

Read Only Memory and programmed with a block of data. The

These memory devices are used in flash memory keeps its data even with no

computers and other electronic devices to power at all. The flash memory is popular

store a small amount of data that needs to because it works fast and efficiently than

be saved when the power supply is EEPROM. The flash memory module is

removed. The contents of the EEPROM designed for about 100000 -10000000

are erased by exposing it to an electrical write cycles. The main constraint with the

charge. The EEPROM data is stored and flash memory is number of times data can

removed by 1 byte of data at a time. The be written to it. The data can be read from

EEPROM does not need to be modified. flash memory as many times as desired,

The changing of the content does not but after a certain number of write

require additional equipment. The modern operations, it will stop working.[1]

EEPROM allows multi-byte page

operations and has limited life. The

EEPROM can be designed for 10 to 1000

write cycles. When the number of write

operations is completed, the EEPROM

stops working. EEPROM is a storage

39 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

NOR BASED

Fig. 4 - NOR cell configuration

Table 1 – Bias conditions of the NOR cells for erase, programming and read operation

Operation

Signal Erase Programming Read

Bit line 1 Open 6V 1V

Bit line 1 Open 0V 0V

Source line 12V 0V 0V

Word line 1 0V 0V 0V

Word line 2 0V 12V 5V

Word line 3 0V 0V 0V

Fig 6 and table 1 show the NOR cell configuration and bias conditions for erase,

programming and read operations, respectively. The NOR cell uses the F-N tunneling

mechanism for the erase operation and the hot-electron injection mechanism for the

programming operation.[1]

40 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

NAND BASED

Table 2 – Bias conditions of the NAND cells for erase, programming and read operation

Operation

Signal Erase Programming Read

Bit line 1 Open 0V 1V

Bit line 1 Open 0V 1V

Select line 1 0V 5V 5V

Word line 1 0V 10V 5V

Word line 2 0V 10V 5V

Word line 3 0V 10V 5V

Word line 4 0V 10V 5V

Word line 5 0V 20V 0V

Word line 6 0V 10V 5V

Word line 7 0V 10V 5V

Word line 8 0V 10V 5V

Source line 2 Open 0V 5V

Source line 20V 0V 0V

p-well 2 20V 0V 0V

n-sub 20V 0V 0V

41 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

Fig. 5 - Equivalent circuit of the 8 bit NAND cell

Equivalent circuit of the 8 bit NAND cell structure is shown in fig 6. Bias conditions for

erase, programming and read operations are shown in table 2. The NAND cell uses an F-N

tunneling mechanism for the erase operation.[1]

RESULT & CONCLUSION

Table 3 – Comparison

Memory Type

Parameter DRAM SRAM

Cell Structure 1T-1C 6T

Cell Density High Low

Power consumption High High/Low

42 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

Read Speed ~50 ns ~10/70 ns

Write Speed ~40 ns ~5/50 ns

Cost Low High

Application Main Memory Cache/PADs

Memory type

Parameter EPROM EEPROM FLASH

Cell structure 1T 2T 1T

Cell Density High Low High

Power consumption Low Low Low

Read speed ~50 ns ~50 ns ~50 ns

Write speed ~10 µs ~5 ms ~(10 ns-1ms)

Cost Low High Low

Application Game machines Id card Memory card solid

state disk

We have analyzed different types of of EPROM, they have fallen out of favor

memory cells in digital VLSI. Each type of and have been replaced by Flash

memory has its own special Memories. NAND flash is used for data

characteristics. Memory circuits are very storage due to non-volatility and high

important in analysis of low power circuits density while NOR flash is used for code

[5]. For example, DRAM has features of storage due to non-volatility and fast

high density and fast speed and is used in random access speed. So we can conclude

main memory. SRAM is used as the cache that each memory cell has its own

memory due to its high speed. Drawback advantages and area in which it may be

of volatile memory is that stored data in used.

memory is lost when power is turned off,

to overcome this problem ROM came into

picture. Due to cost and reliability issues

43 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

REFERENCES IV. “Power optimization for Low

I. „CMOS Digital Integrated Power VLSI circuits” by Sumita

Circuit‟,by Sung-Mo Kang $th Gupta, Sukanya Padavein

edition Mc Graw Hill international Journal of advanced

research in Computer science &

II. NPTEL Electronics & software Engineering Volume 6

Telecommunication ,module issue 3

6,Lecture 26,27,28 „comparative

study of technology in Cite this Article

semiconductor memories –A Tanvi Upaskar, Ganesh Thorave, Prof.

review‟-IICE2016 Sumita G, Mayuresh Yerandekar,

Siddhesh Mahadik (2019). Analysis of

Various Memory Circuits Used In

III. „A study of semiconductor memory Digital VLSI International Journal of

VLSI Design, Microelectronics and

technology by comaring volatile

Embedded System, 4 (1), 34- 44

and non volatile memories‟ by

http://doi.org/10.5281/zenodo.2652717

Hamsa S.

AUTHORS’ PROFILE

[1] Tanvi Upaskar, Student

Department: Electronics & Telecommunication Engineering

College: K C College of Engineering and Management Studies Thane, India

[2] Ganesh Thorave, Student

Department: Electronics & Telecommunication Engineering

College: K C College of Engineering and Management Studies Thane, India

[3] Prof. Sumita G, Assistant Professor

Department: Electronics & Telecommunication Engineering

College: K C College of Engineering and Management Studies Thane, India

[4] Mayuresh Yerandekar, Student

Department: Electronics & Telecommunication Engineering

College: K C College of Engineering and Management Studies Thane, India

[5] Siddhesh Mahadik, Student

Department: Electronics & Telecommunication Engineering

College: K C College of Engineering and Management Studies Thane, India

44 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

45 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

International Journal of VLSI Design, Microelectronics and Embedded

System

Volume 4 Issue 1

46 Page 34-44 © MANTECH PUBLICATIONS 2019. All Rights Reserved

You might also like

- Matrix operations on DSP array architectureDocument9 pagesMatrix operations on DSP array architectureAdiseshuMiddeNo ratings yet

- AC 4th Unit Receiver PDFDocument21 pagesAC 4th Unit Receiver PDFAdiseshuMiddeNo ratings yet

- Critical RegionDocument7 pagesCritical RegionmustafaNo ratings yet

- Lecture25 PDFDocument13 pagesLecture25 PDFJunaid RajputNo ratings yet

- Antennas PropagationDocument40 pagesAntennas PropagationSafura BegumNo ratings yet

- Radio Ranges Radar NotesDocument7 pagesRadio Ranges Radar NotesAdiseshuMiddeNo ratings yet

- Program 8queensDocument1 pageProgram 8queensAdiseshuMiddeNo ratings yet

- AC 4th Unit Receiver PDFDocument21 pagesAC 4th Unit Receiver PDFAdiseshuMiddeNo ratings yet

- AWP (Antenna Measurement) PDFDocument94 pagesAWP (Antenna Measurement) PDFAdiseshuMiddeNo ratings yet

- Newdoc 1Document1 pageNewdoc 1AdiseshuMiddeNo ratings yet

- 7.3 Antennas and Wave PropagationDocument32 pages7.3 Antennas and Wave PropagationAdiseshuMidde0% (1)

- Advantages of NwellDocument1 pageAdvantages of NwellAdiseshuMidde100% (2)

- Untitled DocumentDocument1 pageUntitled DocumentAdiseshuMiddeNo ratings yet

- PTSP Qus BankDocument6 pagesPTSP Qus BankAdiseshuMiddeNo ratings yet

- Field Programmable Gate ArrayDocument1 pageField Programmable Gate ArrayAdiseshuMiddeNo ratings yet

- Step by Step Procedure To Run A Program Xilinix On FPGA BoardDocument11 pagesStep by Step Procedure To Run A Program Xilinix On FPGA BoardAdiseshuMiddeNo ratings yet

- Docu KLMDocument1 pageDocu KLMAdiseshuMiddeNo ratings yet

- Message Contain Either Audio or Video or Picture InformationDocument1 pageMessage Contain Either Audio or Video or Picture InformationAdiseshuMiddeNo ratings yet

- Overal Final Documentation For ThesisDocument1 pageOveral Final Documentation For ThesisAdiseshuMiddeNo ratings yet

- .Model Small .Stack 200 .Code Start: Mov Ax, 1111h Mov BX, 1111h Add Ax, BX Int 03h End StartDocument1 page.Model Small .Stack 200 .Code Start: Mov Ax, 1111h Mov BX, 1111h Add Ax, BX Int 03h End StartAdiseshuMiddeNo ratings yet

- Step by Step Procedure To Run A Program On FPGA BoardDocument11 pagesStep by Step Procedure To Run A Program On FPGA BoardAdiseshuMiddeNo ratings yet

- Modern CommunicationDocument1 pageModern CommunicationAdiseshuMiddeNo ratings yet

- Stack Full Out OperationDocument1 pageStack Full Out OperationAdiseshuMiddeNo ratings yet

- Final Documentation For ThesisDocument1 pageFinal Documentation For ThesisAdiseshuMiddeNo ratings yet

- Ic 123Document1 pageIc 123AdiseshuMiddeNo ratings yet

- Untitled 1Document1 pageUntitled 1AdiseshuMiddeNo ratings yet

- SsstacDocument1 pageSsstacAdiseshuMiddeNo ratings yet

- Stack Full OperationDocument1 pageStack Full OperationAdiseshuMiddeNo ratings yet

- Integrated Circuit - Ic Vlsi-Very Large Scale IntegrationDocument1 pageIntegrated Circuit - Ic Vlsi-Very Large Scale IntegrationAdiseshuMiddeNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Power Converters For: Traction ApplicationDocument2 pagesPower Converters For: Traction ApplicationMohamedNo ratings yet

- Panasonic Pcz1203031ce Tx-P50gt50e tx-p50gt50j Chassis Gpf15d-E PDFDocument116 pagesPanasonic Pcz1203031ce Tx-P50gt50e tx-p50gt50j Chassis Gpf15d-E PDFnovyNo ratings yet

- M9F/J BLOCK DIAGRAM content overviewDocument63 pagesM9F/J BLOCK DIAGRAM content overviewЮра ИвановNo ratings yet

- ZMM 1... ZMM200: Silicon Planar Zener DiodesDocument8 pagesZMM 1... ZMM200: Silicon Planar Zener DiodesMu YuNo ratings yet

- Interrupt Lab Timing Diagrams and ProgrammingDocument4 pagesInterrupt Lab Timing Diagrams and Programmingنفیسه احمدیNo ratings yet

- Embedded Systems Unit 1 and 2 NotesDocument51 pagesEmbedded Systems Unit 1 and 2 NoteskarnamittapalliNo ratings yet

- Grade 6Document160 pagesGrade 6Tejas ViswanathanNo ratings yet

- Research Profile 2019 PDFDocument7 pagesResearch Profile 2019 PDFMd. Ashikur RahmanNo ratings yet

- How To Solder The Chip ComponentsDocument19 pagesHow To Solder The Chip ComponentsjackNo ratings yet

- Invent A RioDocument54 pagesInvent A RioKatherine Navas LugoNo ratings yet

- Digital Fundamentals: FloydDocument42 pagesDigital Fundamentals: FloydJavier Alberto MontañaNo ratings yet

- 7XV5662-0AC00/7XV5662-0AC01 Communication Converter For Pilot WiresDocument2 pages7XV5662-0AC00/7XV5662-0AC01 Communication Converter For Pilot WiresVictor Manuel BonettoNo ratings yet

- Scanner (Optimised) PDFDocument377 pagesScanner (Optimised) PDFAkansha Jain100% (1)

- Rm0444 Stm32g0x1 Advanced Armbased 32bit Mcus StmicroelectronicsDocument1,390 pagesRm0444 Stm32g0x1 Advanced Armbased 32bit Mcus StmicroelectronicsiwjvbbqzNo ratings yet

- Dell Alienwarem r2 Compal Edq51 La h351p La f552p La f553p 1 0 Xa00Document109 pagesDell Alienwarem r2 Compal Edq51 La h351p La f552p La f553p 1 0 Xa00013azizNo ratings yet

- Performance Testing: Key ConsiderationsDocument9 pagesPerformance Testing: Key ConsiderationssahilNo ratings yet

- Sperry SussiDocument1 pageSperry SussiCostin CaraimanNo ratings yet

- DVD BookDocument187 pagesDVD BookParamedico GuadalajaraNo ratings yet

- Manual - Sapphire Touch ScreenDocument2 pagesManual - Sapphire Touch ScreenSamuel Castro SedanoNo ratings yet

- CY4611B - Kit User GuideDocument78 pagesCY4611B - Kit User GuideIon PungaNo ratings yet

- Proposed Switches Five Level Inverter With Switching Frequencies For LinearDocument6 pagesProposed Switches Five Level Inverter With Switching Frequencies For Linearfarid kerroucheNo ratings yet

- Silicon Switching Diode Array BAV 70: Type Ordering Code (Tape and Reel) Marking Package Pin ConfigurationDocument4 pagesSilicon Switching Diode Array BAV 70: Type Ordering Code (Tape and Reel) Marking Package Pin Configurationjavier venturaNo ratings yet

- BuildYourCNC - Mach3 USB Interface Board PDFDocument13 pagesBuildYourCNC - Mach3 USB Interface Board PDFManuel Lorenzo100% (1)

- Inverter List A19Document2 pagesInverter List A19Raimundo OliveiraNo ratings yet

- Intro. To Internet of Things, Fall 2020: Ydlin@cs - Nctu.edu - TWDocument2 pagesIntro. To Internet of Things, Fall 2020: Ydlin@cs - Nctu.edu - TWMohammed AhmedNo ratings yet

- Huawei AAU PDFDocument14 pagesHuawei AAU PDFsunny kumarNo ratings yet

- Single Phase Half Controlled Converter With R LoadDocument3 pagesSingle Phase Half Controlled Converter With R LoadB ANIL KUMARNo ratings yet

- Memory Manufacturing Company MMC Produces Memory Modules in A Two StepDocument1 pageMemory Manufacturing Company MMC Produces Memory Modules in A Two StepAmit PandeyNo ratings yet

- Lec 6Document18 pagesLec 6Rama DeviNo ratings yet

- Electronic Devices 9th Edition - CHP 2 Basic ProblemsDocument9 pagesElectronic Devices 9th Edition - CHP 2 Basic ProblemsThivhulawi MukondeleliNo ratings yet