Professional Documents

Culture Documents

6.2 ALU - Arithmetic Logic Unit: Section "" On Page 281

Uploaded by

salarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

6.2 ALU - Arithmetic Logic Unit: Section "" On Page 281

Uploaded by

salarCopyright:

Available Formats

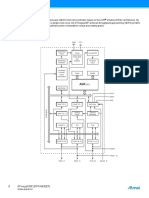

The fast-access register file contains 32 8-bit general purpose working registers with a single clock cycle access

time. This

allows single-cycle arithmetic logic unit (ALU) operation. In a typical ALU operation, two operands are output from the

register file, the operation is executed, and the result is stored back in the register file – in one clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for data space addressing – enabling

efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in

flash program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register

operations can also be executed in the ALU. After an arithmetic operation, the status register is updated to reflect

information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole

address space. Most AVR® instructions have a single 16-bit word format. Every program memory address contains a 16- or

32-bit instruction.

Program flash memory space is divided in two sections, the boot program section and the application program section. Both

sections have dedicated lock bits for write and read/write protection. The SPM instruction that writes into the application flash

memory section must reside in the boot program section.

During interrupts and subroutine calls, the return address program counter (PC) is stored on the stack. The stack is

effectively allocated in the general data SRAM, and consequently the stack size is only limited by the total SRAM size and

the usage of the SRAM. All user programs must initialize the SP in the reset routine (before subroutines or interrupts are

executed). The stack pointer (SP) is read/write accessible in the I/O space. The data SRAM can easily be accessed through

the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status

register. All interrupts have a separate interrupt vector in the interrupt vector table. The interrupts have priority in accordance

with their interrupt vector position. The lower the interrupt vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as control registers, SPI, and other I/O functions.

The I/O memory can be accessed directly, or as the data space locations following those of the register file, 0x20 - 0x5F. In

addition, the ATmega328P has extended I/O space from 0x60 - 0xFF in SRAM where only the ST/STS/STD and

LD/LDS/LDD instructions can be used.

6.2 ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a

single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are

executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some

implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and

fractional format. See Section “” on page 281 for a detailed description.

6.3 Status Register

The status register contains information about the result of the most recently executed arithmetic instruction. This

information can be used for altering program flow in order to perform conditional operations. Note that the status register is

updated after all ALU operations, as specified in the instruction set reference. This will in many cases remove the need for

using the dedicated compare instructions, resulting in faster and more compact code.

The status register is not automatically stored when entering an interrupt routine and restored when returning from an

interrupt. This must be handled by software.

10 ATmega328P [DATASHEET]

7810D–AVR–01/15

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (589)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5806)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- HR Policies in HCL at HCL CDC, Noida (HR)Document99 pagesHR Policies in HCL at HCL CDC, Noida (HR)sanyakap100% (1)

- Activity 1 AbdonDocument8 pagesActivity 1 AbdonAnonymous JJ6E0Lpy2nNo ratings yet

- Bill Alignment DispenserDocument186 pagesBill Alignment Dispenserbruno-rocha-brn9057100% (1)

- HP SSP Server Support GuideDocument31 pagesHP SSP Server Support Guidepera_petronijevicNo ratings yet

- T L E Module 1 Grade 8Document20 pagesT L E Module 1 Grade 8Jared Floyd Lorezo100% (3)

- 8.3 Low Power Crystal Oscillator: Figure 8-2Document1 page8.3 Low Power Crystal Oscillator: Figure 8-2salarNo ratings yet

- Sbic RJMP: Wait For Completion of Previous WriteDocument1 pageSbic RJMP: Wait For Completion of Previous WritesalarNo ratings yet

- 7.6 Register Description: 7.5.1 General Purpose I/O RegistersDocument1 page7.6 Register Description: 7.5.1 General Purpose I/O RegisterssalarNo ratings yet

- System Clock and Clock OptionsDocument1 pageSystem Clock and Clock OptionssalarNo ratings yet

- 8.2 Clock Sources: 8.1.4 Asynchronous Timer Clock - CLKDocument1 page8.2 Clock Sources: 8.1.4 Asynchronous Timer Clock - CLKsalarNo ratings yet

- Oscillator Source / Power Conditions Start-Up Time From Power-Down and Power-Save Additional Delay From Reset (V 5.0V) Cksel0 SUT1..0Document1 pageOscillator Source / Power Conditions Start-Up Time From Power-Down and Power-Save Additional Delay From Reset (V 5.0V) Cksel0 SUT1..0salarNo ratings yet

- Figure 8-3. Crystal Oscillator ConnectionsDocument1 pageFigure 8-3. Crystal Oscillator ConnectionssalarNo ratings yet

- 7.3 SRAM Data Memory: Figure 7-2Document1 page7.3 SRAM Data Memory: Figure 7-2salarNo ratings yet

- Eepm1 Eepm0 Programming Time Operation: Table 7-1. EEPROM Mode BitsDocument1 pageEepm1 Eepm0 Programming Time Operation: Table 7-1. EEPROM Mode BitssalarNo ratings yet

- 8.5 Low Frequency Crystal Oscillator: Table 8-7Document1 page8.5 Low Frequency Crystal Oscillator: Table 8-7salarNo ratings yet

- Avr Memories: Figure 7-1. Program Memory Map Atmega328PDocument1 pageAvr Memories: Figure 7-1. Program Memory Map Atmega328PsalarNo ratings yet

- 7.4 EEPROM Data Memory: Section 27. "Memory Programming" On Page 241Document1 page7.4 EEPROM Data Memory: Section 27. "Memory Programming" On Page 241salarNo ratings yet

- In Cli Sbi Sbi Out: Store SREG ValueDocument1 pageIn Cli Sbi Sbi Out: Store SREG ValuesalarNo ratings yet

- 6.4 General Purpose Register File: Figure 6-2Document1 page6.4 General Purpose Register File: Figure 6-2salarNo ratings yet

- Atmel 0013Document1 pageAtmel 0013salarNo ratings yet

- 6.3.1 SREG - AVR Status Register: - Bit 7 - I: Global Interrupt EnableDocument1 page6.3.1 SREG - AVR Status Register: - Bit 7 - I: Global Interrupt EnablesalarNo ratings yet

- 6.6 Instruction Execution Timing: 6.5.1 SPH and SPL - Stack Pointer High and Stack Pointer Low RegisterDocument1 page6.6 Instruction Execution Timing: 6.5.1 SPH and SPL - Stack Pointer High and Stack Pointer Low RegistersalarNo ratings yet

- 1.1 Pin Descriptions: Atmega328P (Datasheet) 4Document1 page1.1 Pin Descriptions: Atmega328P (Datasheet) 4salarNo ratings yet

- Figure 2-1. Block DiagramDocument1 pageFigure 2-1. Block DiagramsalarNo ratings yet

- Pin Configurations: Figure 1-1. PinoutDocument1 pagePin Configurations: Figure 1-1. PinoutsalarNo ratings yet

- 7 Atmega328P (Datasheet) : 7810D-Avr-01/15Document1 page7 Atmega328P (Datasheet) : 7810D-Avr-01/15salarNo ratings yet

- 579-1006 List Part 4100ESDocument22 pages579-1006 List Part 4100ESRafael ContrerasNo ratings yet

- Windows 10 Pro Retail DVD Activation Key Inside 32 64 Bit Lifetime LicenseDocument34 pagesWindows 10 Pro Retail DVD Activation Key Inside 32 64 Bit Lifetime Licenseaddoe jonathanNo ratings yet

- Manual+Catalogo+de+Despiece+y+Numeros+de+Parte+Para+Laptop+Toshiba+Portege+ 7010CTnumbersDocument2 pagesManual+Catalogo+de+Despiece+y+Numeros+de+Parte+Para+Laptop+Toshiba+Portege+ 7010CTnumberseurospeed2No ratings yet

- Ch9 Memory MGNT QuestionsDocument7 pagesCh9 Memory MGNT QuestionsGourav JangidNo ratings yet

- GPUParallelProgramming PDFDocument104 pagesGPUParallelProgramming PDFJavad Rahman NezhadNo ratings yet

- Kalinga University Department of Computer ScienceDocument16 pagesKalinga University Department of Computer SciencePooja Singh ThakurNo ratings yet

- Chapter 9Document48 pagesChapter 9Shamayl Al-zadjaliNo ratings yet

- SP C262Dnw SP C262Sfnw: A4 Colour Printer & MFPDocument4 pagesSP C262Dnw SP C262Sfnw: A4 Colour Printer & MFPAivars LīpenītsNo ratings yet

- TechSolve VizAdapter Data Sheet - Heidenhain CNC MTConnect AdapterDocument1 pageTechSolve VizAdapter Data Sheet - Heidenhain CNC MTConnect AdapterDörky LefieuwNo ratings yet

- Inside Intel InsideDocument4 pagesInside Intel InsideSagar BoraNo ratings yet

- Assembly Language Programming:: 8085 Program To Add Two 8 Bit NumbersDocument9 pagesAssembly Language Programming:: 8085 Program To Add Two 8 Bit NumbersAnkit ratan pradhanNo ratings yet

- COMSATS University, Islamabad: Islamabad Campus Department of Computer ScienceDocument2 pagesCOMSATS University, Islamabad: Islamabad Campus Department of Computer ScienceMuqaddas PervezNo ratings yet

- E 95 A 020Document6 pagesE 95 A 020Ag CristianNo ratings yet

- Guide - 66333 - en - Desmontar Pantalla LCD de Laptop HP550Document5 pagesGuide - 66333 - en - Desmontar Pantalla LCD de Laptop HP550rubenNo ratings yet

- Memory OrganizationDocument57 pagesMemory OrganizationvpriyacseNo ratings yet

- Unit 3Document104 pagesUnit 3Avantee SinghNo ratings yet

- Discovering Computers Chapter 8Document37 pagesDiscovering Computers Chapter 8dragon slzNo ratings yet

- AllenBradley PLC 2 PDFDocument18 pagesAllenBradley PLC 2 PDFEstebanPieraNo ratings yet

- Apple II Reference Manual 1979 Apple TextDocument209 pagesApple II Reference Manual 1979 Apple Textvmarquez25No ratings yet

- CSS L4 NewDocument32 pagesCSS L4 NewjheraNo ratings yet

- Programmable Communication Interface and Programmable Interval TimerDocument48 pagesProgrammable Communication Interface and Programmable Interval TimerMahendra Singh MeenaNo ratings yet

- External Hard Drive NEWDocument8 pagesExternal Hard Drive NEWshakeelNo ratings yet

- Cost To Cost: Cost To Cost Whatsapp No: 9811616164 Amd Apu (Cpu+Gpu) A-10 4,1 GHZ Rs - 4990Document8 pagesCost To Cost: Cost To Cost Whatsapp No: 9811616164 Amd Apu (Cpu+Gpu) A-10 4,1 GHZ Rs - 4990Mohit VermaNo ratings yet

- Multiweld BV Orbitaal Stroombron OM 165 CB PDFDocument2 pagesMultiweld BV Orbitaal Stroombron OM 165 CB PDFMarcos AndréNo ratings yet

- AMD Computer AccessoriesDocument3 pagesAMD Computer AccessoriesCalon RadiantNo ratings yet