Professional Documents

Culture Documents

M5L8155P Mitsubishi

M5L8155P Mitsubishi

Uploaded by

micaelfn0 ratings0% found this document useful (0 votes)

47 views8 pagesOriginal Title

M5L8155P-Mitsubishi

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

47 views8 pagesM5L8155P Mitsubishi

M5L8155P Mitsubishi

Uploaded by

micaelfnCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 8

MITSUBISHI LSI

MSL8155P

STATIC RAM WITH 1/0 PORTS AND TIMER

DESCRIPTION

The MBLBISEP ie a 2K-bt RAM (255-word by bt) fabri-

010d by the N-channel silcen-gate ED-MOS technology.

‘Ths LSI at 3 VO ports and & 14-bit courterimer which

‘make it good extention of the functions of an B-bit micro:

‘computer is packaged in @ 40spin plastic DIL package

and operates witha single SV power supoly.

FEATURES

1 Single SV auppy votage

© THU compattie

Static RAM: 256.word by 8-it

Programmable 6-b« 1/0 part: 2

Programmable 6-bt /0 port!

Programmable counterimer: 14-bit

(© Mutiplesed adcress/aata bus

PIN CONFIGURATION (TOP VIEW)

EEsEeES

a

ssi

nomenomy 20-70

APPLICATION

Extension f 1/0 ports and timer function for MELPS 85 ang

MELPS 848 devices,

BEEEGESESSE!

FUNCTION

‘The MSLBISSP is composed of RAM. 1/0 pests and counter!

Lumet. The RAM i¢ a 2K-bt slate RAM organized as 256

‘words by 8 Bis. The 0 pons consist ot 2 programmable &-

Dt pots and 1 programmabie 6b port. The terminals of he

-bit pat can be programmed as contol terminals forthe

bit pots, so thatthe 8-it ports can be operated in a hand

shake mode. The counter/imer is composed of 18bit down

counter (events ore} and i can generate square wave

pulses that can be uted fot counting and tning

sg «dC

Outine 406

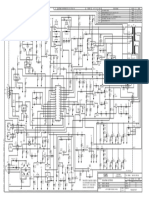

BLOCK DIAGRAM

12. zsworoxeem) | bo] fe porns a

soovmecrionat | Abe S—foara ou «LE

00H SSDATA BU = ‘ourren = 2 |

so ‘

‘One ENABLE INPUTCE x 1a)

#eia=| eee.

LW -

atom mPUr TER OU

MITSUBISHI LSis

MSL81SSP

2048-BIT STATIC RAM WITH 1/0 PORTS AND TIMER

OPERATION

Data Bus Butter

This $-state biirectonal 6-bit butler is used to wane the

ata wile input or output nstrctions are Being executed by

te CPU. Command and address inloeation i ago Wane.

‘ed through te data ous butter.

Read/Write Contro! Logic

‘The read/write contol logic conto the transfer of dala and

commands by inlerpreing the signals (CE, RD, WR, 107%,

[ALE and RESET) rom CPU

Bidirectional AddressiData Bus (AD5~AD,)

‘The bidirectional address/osta bus if a 3-slate B-bit bus

“The B-bt addr i atched! in tho storal latch by the fall

ing edge of ALE. Then i 10/M input signal is at high-level

the address of 1/0 por, countertmer, or command register

is selected. iis al low-level, adcress of RAMs selected

‘The Bit data is ranstetred by read input (RO) or wrt in-

put we

Chip Enable Input (CE)

Wen CE is at low-level, the adress information on

adoress/data bs i stored in the MSLBISSP

Fad input (RO)

Wien RD isa low-level, the data bus butler is active, 1O/

IM input signal isa low-level, the contante of RAM are read

trough me agaress/gata bus. 1! 1O/M input i at Mgh-evel

‘the contonls of selacted 1/0 port of counterimer are read

trough the acaeese/data bus

‘Write input (WA)

When WA is st low-level he dats on he addess/data bus

fare wittan info RAM IO/M isa low-lavel, of they ate wnt

tan nto por, eountertimar or cammang register i 10/4

is atnigh-ieve

‘Address Latch Enable input (ALE)

‘An address. on the aderess/dals bus 1 latched in the

[MSLAIESP on the fang edge of ALE along with the levels of

CE and 10M

O/Memory Input (10/M)

When 1O/M is a low-level, the RAM is selected, white at

high-tevel the VO pon, counterimer or command register

ate selected

VO Port & (PAy~PA;)

Port A an B-bt general-purpose 140 por Inpuoutput set

ting is contoles by the system software

VO Port B (PB,~PB,)

Port Bis an 8-bt general-purpose 1/0 port Input/cuput set

Lung is contoog by the system sottware,

WO Port ¢ (PC,~PCy)

Port C is a 6:51 1/0 port that ean aso be used to output

contol signals of pot A (PA) oF pest 8 (PB). The functions

cof por C are contaled bythe system sortware. When por ©

's used to output cont signals of pore A or 8, the assign-

‘mont of he signals othe pins is as shown in Tabi |

Table 1 Pin assignment of control signals of pot C

“Timer Input (TIMER IN)

‘The signal on this input termina is uted by the countertimer

for counting evens crime. (3MHz max}

‘Timer Output (TIMER OUT)

‘A square wave signal or pulso trom the countertie

ut through thie pin when inthe operation mode,

Command Registor (8 bits)

‘The command rogisor isan 8-bit latched register. The lowe

exder 4 bits (bis O~3) are used for contating and deter-

‘mination of mode of the pets its 4 and § are used ac intr

rupt enable flags fr pois A and B when pert Cis used as

Control por. Bits 6 and 7 are used for controling the coun

{er/timer. The conients of the command register are rewrt

ton by etput instructions (1/0 adress YXXKK0O0)

Details ofthe functions ofthe individual Bits of he command

regjster are shown in Table 2.

is out

‘Table 2 Bit functions of the command register

[ot

Th mine

aT po, |eomeser

Jeena.

Ar

MITSUBISHI LSis

MSL8155P

2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

‘Status Register (7-bit)

The status register isa 7-0i latched registor. The low-order

6 bis (bits 0~5) are used as status lags forthe VO ports

6 is used as a status fag forthe counter/timer. The con-

Table 3 Bit functions of the status register

a

vo PORTS

‘Commandistatus registers (6-biv7-bit)

‘These registers are assigned adcress XX0EX000. When an

OUTPUT command le executed, he contents of the com

‘mand register are rewntten. When an INPUT command is

‘recited tho contents ofthe aus register are road

Port A Register (8-it)

Port A Repistr is assigned address XXXXXO01. This reqister

can be programmed as an input o¢ output by vetting the

lpropriate bls ofthe command register as shown in Table

2

Port A can be operated in basic or strobe mode and Is

assigned 1/0 terminal PPA

Port B Register (8-it)

Port B register i assigned accross XXIOXX010. As with Port

Table 4 Functions of port ©

(mcoecnmaene. |

scams on

tents of the status register are ansteted into the CPU by

reading (INPUT instruction, VO addess XXXAX000}. Data

‘of the funetons of the indvigual bits of the slaus register

fate shown in Table 3.

1 rogiser, this register can be programmed as an iaput

cutput by seting tne appropiate bits ofthe command regis

ter a8 shown in Table 2, Pat B can bo operated in basic or

stvobe mode and is assigned 1/0 terminals PB, ~PB;

Port C Register (6-bt)

Port C register assigned sdatoss XXXXX01). This por Is

‘sed not only for input oF cut but algo fer contatng in

put/output operations of ports A and & by selectively sting

bits 2 and 3 ofthe command register a8 shown in Table 2

Detala of he functions ofthe varous seting of bits 2 and 3

fare shown in Tabla 4. Port Css assigned /0 terminals PC:~

C., When used at port contol signals, the 3 low-order bits

fare assigned for port A while the 3 high-order bis are

assigned tor pont 8

eae

MITSUBISHI LSIs

MSL8155P

2048-BIT STATIC RAM WITH 1/0 PORTS AND TIMER

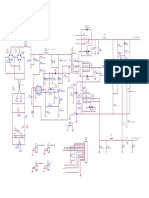

CONFIGURATION OF PORTS

A block clagram of | bt of pats A ond 8 ls shown in Fig

While por or 8 Is programmed as an output por, the

por is addressed by an input instruction, the contents ofthe

selected port can be read. When a pot is put in input mode,

me output latch is cleared and wing into the output ath 6

isableg. Therefore when a port is changed to output mode

{rom input modo, low-level sgnele sre output through the

‘ort. When a rset signa is applied, all3 ports (PA, PB, and

PC) wil be Input ports and their output latches are cleared.

Port © has the same configuration as pore A and 6 in mod-

‘Os ALTI and ALTZ

MaLerseP

OTs

Fig. 1 Gontiguration for 1 Bi of port A or B

Table 5 Basle functions of 1/0 ports

some Flt eae

Table 5 Port contol signal levels at ALT3 and ALT4

‘The basle uaclions ofthe VO pons are shown in Table 5

‘The contol signal levels fo pots A and B, wnen port C is

programmed as a cont por, are shown In Tele 6

COUNTER/TIMER

‘Tho countertimar is composed of a 14-bit courting ragister

‘and 2 mode tags, The register has wo sections: 1/0

‘addreas XOXXXI00 Is assigned tthe low-order 8 bits and I/

© deeoss 140XKI01 is assigned to the high-order 6 Bi

fd timer mode flag 2 bis. The low-order Bits 0~ 13 ar

sed for counting oF timing. The countor i niaized by the

program and then counted down to 0. The intl value can

be ranged fom 2s to 3FFFig. Bits 14 and 15 aro used as

mode fags

‘The mode flags select 1 of {modes with functions a8 fol

lows

Genes Sonn [Ot ne ree nae Mode 0: Outputs high-level signal during the former

8 Input ro ha of te counter operation

°F re (Outputs low-level signal during the later nat

a ofthe counter eperation

ry fe mersumise

ELECTRIC

MITSUBISHI LSts

MSL81S55P

2048-BIT STATIC RAM WITH 1/0 PORTS AND TIMER

‘Table 7 Format of counter/imer Mode

aoe 2

wm Lleisie[sTere ye = Mode 3 Outputs s low-level pulse during each tna

Hocexcto| ttl tas Ta Te Mew Be he ome

Staring and stopping he counter/imer is cooled by bits

6 and 7 of the commend register (see Table 2 fr detail).

‘The formst and timer modes of the countertimer register

‘ara snow In Tale 7 and Table 8

Qe ‘The contents of counter/timer i nok affected by a reset, but

counting Is dscontinsed. To resume counting, a sar com-

Ca ‘mand must be writen ite the command resicter a8 shown

De eemessaee in Table 2. While operating 2n++1 count down in modes 0

oe enseceee and 1, a high-tevel signal is cut crng the tamer n-+1

@ | 1 ouomurenmenyuninncord ims} S289 8nd a low-level signa soup ding te lalern

sateen counting.

+ ‘note? | RESET

1 | 1 Sanit sient ung anew aot on | The MSLEISSP I reset by Ons (min) pulse input on RE

SET ph,

By rose, all3 ports are sett Input mode. And courrier

stops, but contents of countertimar i na reset. Theratore i

is necessary to input start command again

ABSOLUTE MAXIMUM RATINGS

7 zt

Syme! owen

ELECTRICAL CHARACTERISTICS (14=-20~75¢. Yeo= 5259 Vyr0¥. unas aeris rte)

Note 3+ Gover towing inte an 10 pone ol eps

ELECTRIC ca

MITSUBISHI LSI

MSL81SSP

2048-BIT STATIC RAM WITH 1/0 PORTS AND TIMER

TIMING REQUIREMENTS (12-~2~75¢, Yeon 5V15%, Veynov, ions ober ste

1 nations a —_ et

Ht E-F3

[00 on

fet :

[=t t+3

a)

a

eel poaee ‘econ ‘| =i :

Et :

[ae =]

o~ BG

ee itsh

es aoe

anew

MITSUBISHI LSis

MSL8155P

2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

TIMING DIAGRAM

Basic Output

Basic Input

ws ——

soto =e Oo >

fe mersuaisio By

MITSUBISHI LSis

MSL8155P

2048-BIT STATIC RAM WITH 1/0 PORTS AND TIMER

Strobed Output

Strobed input

Timer

rarour Canaan)

suARe SAVE MODE enna (t0

ex yar ma tow ct tag dno 0

‘riot pen au conmusay onset

ne Acree

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5819)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Schematic Motherboard Biostar G41D3C PDFDocument32 pagesSchematic Motherboard Biostar G41D3C PDFManuel Prado40% (5)

- SMS Power Vision MPV 2 e 3KVA (T0403707)Document1 pageSMS Power Vision MPV 2 e 3KVA (T0403707)micaelfnNo ratings yet

- 1ZC12 1ZC120Document3 pages1ZC12 1ZC120micaelfnNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : 4 X 47W MOSFET Quad Bridge Power AmplifierDocument12 pagesObsolete Product(s) - Obsolete Product(s) : 4 X 47W MOSFET Quad Bridge Power AmplifiermicaelfnNo ratings yet

- User GuideDocument193 pagesUser GuidemicaelfnNo ratings yet

- Philips+40PFT5100+TPS15 1A+LADocument112 pagesPhilips+40PFT5100+TPS15 1A+LAmicaelfnNo ratings yet

- NUWTR v5.09.04 Support Body ListDocument10 pagesNUWTR v5.09.04 Support Body ListmicaelfnNo ratings yet

- 2A (Inverter) : Comp VCC RT NC CS VCC OUTDocument2 pages2A (Inverter) : Comp VCC RT NC CS VCC OUTmicaelfnNo ratings yet

- Z32F064 Evaluation Kit: ZNEO32! Family of MicrocontrollersDocument13 pagesZ32F064 Evaluation Kit: ZNEO32! Family of MicrocontrollersmicaelfnNo ratings yet

- EM78P447SAMDocument55 pagesEM78P447SAMmicaelfnNo ratings yet

- Nrf2401A: Single Chip 2.4 GHZ TransceiverDocument40 pagesNrf2401A: Single Chip 2.4 GHZ TransceivermicaelfnNo ratings yet

- RF 300CH 11440 KysanDocument2 pagesRF 300CH 11440 KysanmicaelfnNo ratings yet

- TB2929HQ: 45W × 4-ch BTL Audio Power ICDocument17 pagesTB2929HQ: 45W × 4-ch BTL Audio Power ICmicaelfnNo ratings yet

- FR9887 FitiDocument2 pagesFR9887 FitimicaelfnNo ratings yet

- Monolithic Digital Stereo FM Transmitter Radio-Station-on-a-Chip™Document23 pagesMonolithic Digital Stereo FM Transmitter Radio-Station-on-a-Chip™micaelfnNo ratings yet

- FR9887 FitiDocument2 pagesFR9887 FitimicaelfnNo ratings yet