Professional Documents

Culture Documents

Character/Graphic TFT LCD Controller: Application Note

Uploaded by

Gonzalo RiveraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Character/Graphic TFT LCD Controller: Application Note

Uploaded by

Gonzalo RiveraCopyright:

Available Formats

RAiO

RA8875

Character/Graphic

TFT LCD Controller

Application Note

Version 1.3

July 11, 2011

RAiO Technology Inc.

©Copyright RaiO Technology Inc. 2011

RAiO TECHNOLOGY INC. 1/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

Update History

Version Date Description

1.0 May, 03, 2011 First Release

1.1 May,09,2011 Schematic 2 updata ,initial code updata

1.2 June,22,2011 Schematic 2 updata

1.3 July,11,2011 Add chapter 6.appendix

RAiO TECHNOLOGY INC. 2/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

Chapter Contents Page

1. Application Circuit ................................................................................... 4

2. Initial Code................................................................................................ 7

3. Display on Sequence............................................................................. 15

4. Sleep Mode Sequence ........................................................................... 16

5. Display RAM pure data write example ................................................. 18

6. Appendix ................................................................................................ 19

RAiO TECHNOLOGY INC. 3/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

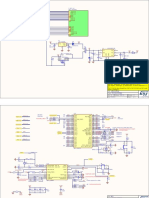

1. Application Circuit

Figure 1-1

RAiO TECHNOLOGY INC. 4/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

※(Please refer to the appendix a)

Figure 1-2

RAiO TECHNOLOGY INC. 5/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

Figure 1-3

RAiO TECHNOLOGY INC. 6/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

2. Initial Code

void RA8875_PLL_ini(void)

{

#ifdef P320x240

LCD_CmdWrite(0x88);

LCD_DataWrite(0x0a);

Delay1ms(1);

LCD_CmdWrite(0x89);

LCD_DataWrite(0x02);

Delay1ms(1);

#endif

#ifdef P480x272

LCD_CmdWrite(0x88);

LCD_DataWrite(0x0a);

Delay1ms(1);

LCD_CmdWrite(0x89);

LCD_DataWrite(0x02);

Delay1ms(1);

#endif

#ifdef P640x480

LCD_CmdWrite(0x88);

LCD_DataWrite(0x0b);

Delay1ms(1);

LCD_CmdWrite(0x89);

LCD_DataWrite(0x02);

Delay1ms(1);

#endif

#ifdef P800x480

LCD_CmdWrite(0x88);

LCD_DataWrite(0x0b);

Delay1ms(1);

LCD_CmdWrite(0x89);

LCD_DataWrite(0x02);

Delay1ms(1);

#endif

RAiO TECHNOLOGY INC. 7/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

//------------------------------------------//

void LCD_Initial(void)

{

RA8875_PLL_ini();

LCD_CmdWrite(0x10); //SYSR bit[4:3]=00 256 color bit[2:1]= 00 8bit MPU interface

LCD_DataWrite(0x0c); // if 8bit MCU interface and 65k color display

//LCD_DataWrite(0x0F); // if 16bit MCU interface and 65k color display

#ifdef P320x240

//============== Display Window320x240 ==================

LCD_CmdWrite(0x04); //set PCLK invers

LCD_DataWrite(0x03);

Delay1ms(1);

//Horizontal set

LCD_CmdWrite(0x14); //HDWR//Horizontal Display Width Setting Bit[6:0]

LCD_DataWrite(0x27);//Horizontal display width(pixels) = (HDWR + 1)*8

LCD_CmdWrite(0x15); //Horizontal Non-Display Period Fine Tuning Option Register (HNDFTR)

LCD_DataWrite(0x00);//Horizontal Non-Display Period Fine Tuning(HNDFT) [3:0]

LCD_CmdWrite(0x16); //HNDR//Horizontal Non-Display Period Bit[4:0]

LCD_DataWrite(0x05);//Horizontal Non-Display Period (pixels) = (HNDR + 1)*8

LCD_CmdWrite(0x17); //HSTR//HSYNC Start Position[4:0]

LCD_DataWrite(0x04);//HSYNC Start Position(PCLK) = (HSTR + 1)*8

LCD_CmdWrite(0x18); //HPWR//HSYNC Polarity ,The period width of HSYNC.

LCD_DataWrite(0x03);//HSYNC Width [4:0] HSYNC Pulse width(PCLK) = (HPWR + 1)*8

//Vertical set

LCD_CmdWrite(0x19); //VDHR0 //Vertical Display Height Bit [7:0]

LCD_DataWrite(0xef);//Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1A); //VDHR1 //Vertical Display Height Bit [8]

LCD_DataWrite(0x00);//Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1B); //VNDR0 //Vertical Non-Display Period Bit [7:0]

LCD_DataWrite(0x05);//Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1C); //VNDR1 //Vertical Non-Display Period Bit [8]

LCD_DataWrite(0x00);//Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1D); //VSTR0 //VSYNC Start Position[7:0]

LCD_DataWrite(0x0e);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1E); //VSTR1 //VSYNC Start Position[8]

LCD_DataWrite(0x00);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1F); //VPWR //VSYNC Polarity ,VSYNC Pulse Width[6:0]

RAiO TECHNOLOGY INC. 8/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

LCD_DataWrite(0x02);//VSYNC Pulse Width(PCLK) = (VPWR + 1)

//Active window set

//setting active window X

LCD_CmdWrite(0x30); //Horizontal Start Point 0 of Active Window (HSAW0)

LCD_DataWrite(0x00); //Horizontal Start Point of Active Window [7:0]

LCD_CmdWrite(0x31); //Horizontal Start Point 1 of Active Window (HSAW1)

LCD_DataWrite(0x00); //Horizontal Start Point of Active Window [9:8]

LCD_CmdWrite(0x34); //Horizontal End Point 0 of Active Window (HEAW0)

LCD_DataWrite(0x3F); //Horizontal End Point of Active Window [7:0]

LCD_CmdWrite(0x35); //Horizontal End Point 1 of Active Window (HEAW1)

LCD_DataWrite(0x01); //Horizontal End Point of Active Window [9:8]

//setting active window Y

LCD_CmdWrite(0x32); //Vertical Start Point 0 of Active Window (VSAW0)

LCD_DataWrite(0x00); //Vertical Start Point of Active Window [7:0]

LCD_CmdWrite(0x33); //Vertical Start Point 1 of Active Window (VSAW1)

LCD_DataWrite(0x00); //Vertical Start Point of Active Window [8]

LCD_CmdWrite(0x36); //Vertical End Point of Active Window 0 (VEAW0)

LCD_DataWrite(0xef); //Vertical End Point of Active Window [7:0]

LCD_CmdWrite(0x37); //Vertical End Point of Active Window 1 (VEAW1)

LCD_DataWrite(0x00); //Vertical End Point of Active Window [8]

#endif

#ifdef P480x272

LCD_CmdWrite(0x04); //set PCLK invers

LCD_DataWrite(0x82);

Delay1ms(1);

//Horizontal set

LCD_CmdWrite(0x14); //HDWR//Horizontal Display Width Setting Bit[6:0]

LCD_DataWrite(0x3B);//Horizontal display width(pixels) = (HDWR + 1)*8

LCD_CmdWrite(0x15); //Horizontal Non-Display Period Fine Tuning Option Register (HNDFTR)

LCD_DataWrite(0x00);//Horizontal Non-Display Period Fine Tuning(HNDFT) [3:0]

LCD_CmdWrite(0x16); //HNDR//Horizontal Non-Display Period Bit[4:0]

LCD_DataWrite(0x01);//Horizontal Non-Display Period (pixels) = (HNDR + 1)*8

LCD_CmdWrite(0x17); //HSTR//HSYNC Start Position[4:0]

LCD_DataWrite(0x00);//HSYNC Start Position(PCLK) = (HSTR + 1)*8

LCD_CmdWrite(0x18); //HPWR//HSYNC Polarity ,The period width of HSYNC.

RAiO TECHNOLOGY INC. 9/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

LCD_DataWrite(0x05);//HSYNC Width [4:0] HSYNC Pulse width(PCLK) = (HPWR + 1)*8

//Vertical set

LCD_CmdWrite(0x19); //VDHR0 //Vertical Display Height Bit [7:0]

LCD_DataWrite(0x0f); //Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1a); //VDHR1 //Vertical Display Height Bit [8]

LCD_DataWrite(0x01); //Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1b); //VNDR0 //Vertical Non-Display Period Bit [7:0]

LCD_DataWrite(0x02); //VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1c); //VNDR1 //Vertical Non-Display Period Bit [8]

LCD_DataWrite(0x00); //Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1d); //VSTR0 //VSYNC Start Position[7:0]

LCD_DataWrite(0x07);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1e); //VSTR1 //VSYNC Start Position[8]

LCD_DataWrite(0x00);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1f); //VPWR //VSYNC Polarity ,VSYNC Pulse Width[6:0]

LCD_DataWrite(0x09); //VSYNC Pulse Width(PCLK) = (VPWR + 1)

//Active window set

//setting active window X

LCD_CmdWrite(0x30); //Horizontal Start Point 0 of Active Window (HSAW0)

LCD_DataWrite(0x00); //Horizontal Start Point of Active Window [7:0]

LCD_CmdWrite(0x31); //Horizontal Start Point 1 of Active Window (HSAW1)

LCD_DataWrite(0x00); //Horizontal Start Point of Active Window [9:8]

LCD_CmdWrite(0x34); //Horizontal End Point 0 of Active Window (HEAW0)

LCD_DataWrite(0xDF); //Horizontal End Point of Active Window [7:0]

LCD_CmdWrite(0x35); //Horizontal End Point 1 of Active Window (HEAW1)

LCD_DataWrite(0x01); //Horizontal End Point of Active Window [9:8]

//setting active window Y

LCD_CmdWrite(0x32); //Vertical Start Point 0 of Active Window (VSAW0)

LCD_DataWrite(0x00); //Vertical Start Point of Active Window [7:0]

LCD_CmdWrite(0x33); //Vertical Start Point 1 of Active Window (VSAW1)

LCD_DataWrite(0x00); //Vertical Start Point of Active Window [8]

LCD_CmdWrite(0x36); //Vertical End Point of Active Window 0 (VEAW0)

LCD_DataWrite(0x0F); //Vertical End Point of Active Window [7:0]

LCD_CmdWrite(0x37); //Vertical End Point of Active Window 1 (VEAW1)

LCD_DataWrite(0x01); //Vertical End Point of Active Window [8]

#endif

RAiO TECHNOLOGY INC. 10/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

#ifdef P640x480

//============== Display Window640x480 ==================

LCD_CmdWrite(0x04); //PCLK inverse

LCD_DataWrite(0x01);

Delay1ms(1);

//Horizontal set

LCD_CmdWrite(0x14);//HDWR//Horizontal Display Width Setting Bit[6:0]

LCD_DataWrite(0x4F);//Horizontal display width(pixels) = (HDWR + 1)*8

LCD_CmdWrite(0x15); //Horizontal Non-Display Period Fine Tuning Option Register (HNDFTR)

LCD_DataWrite(0x05);//Horizontal Non-Display Period Fine Tuning(HNDFT) [3:0]

LCD_CmdWrite(0x16);//HNDR//Horizontal Non-Display Period Bit[4:0]

LCD_DataWrite(0x0f);//Horizontal Non-Display Period (pixels) = (HNDR + 1)*8

LCD_CmdWrite(0x17);//HSTR//HSYNC Start Position[4:0]

LCD_DataWrite(0x01);//HSYNC Start Position(PCLK) = (HSTR + 1)*8

LCD_CmdWrite(0x18); //HPWR//HSYNC Polarity ,The period width of HSYNC.

LCD_DataWrite(0x00);//HSYNC Width [4:0] HSYNC Pulse width(PCLK) = (HPWR + 1)*8

//Vertical set

LCD_CmdWrite(0x19); //VDHR0 //Vertical Display Height Bit [7:0]

LCD_DataWrite(0xdf);//Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1A);//VDHR1 //Vertical Display Height Bit [8]

LCD_DataWrite(0x01);//Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1B);//VNDR0 //Vertical Non-Display Period Bit [7:0]

LCD_DataWrite(0x0A);//Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1C);//VNDR1 //Vertical Non-Display Period Bit [8]

LCD_DataWrite(0x00);//Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1D);//VSTR0 //VSYNC Start Position[7:0]

LCD_DataWrite(0x0E);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1E);//VSTR1 //VSYNC Start Position[8]

LCD_DataWrite(0x00);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1F);//VPWR //VSYNC Polarity ,VSYNC Pulse Width[6:0]

LCD_DataWrite(0x01);//VSYNC Pulse Width(PCLK) = (VPWR + 1)

//Active window set

//setting active window X

LCD_CmdWrite(0x30); //Horizontal Start Point 0 of Active Window (HSAW0)

LCD_DataWrite(0x00); //Horizontal Start Point of Active Window [7:0]

LCD_CmdWrite(0x31); //Horizontal Start Point 1 of Active Window (HSAW1)

LCD_DataWrite(0x00); //Horizontal Start Point of Active Window [9:8]

LCD_CmdWrite(0x34); //Horizontal End Point 0 of Active Window (HEAW0)

RAiO TECHNOLOGY INC. 11/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

LCD_DataWrite(0x7f); //Horizontal End Point of Active Window [7:0]

LCD_CmdWrite(0x35); //Horizontal End Point 1 of Active Window (HEAW1)

LCD_DataWrite(0x02); //Horizontal End Point of Active Window [9:8]

//setting active window Y

LCD_CmdWrite(0x32); //Vertical Start Point 0 of Active Window (VSAW0)

LCD_DataWrite(0x00); //Vertical Start Point of Active Window [7:0]

LCD_CmdWrite(0x33); //Vertical Start Point 1 of Active Window (VSAW1)

LCD_DataWrite(0x00); //Vertical Start Point of Active Window [8]

LCD_CmdWrite(0x36); //Vertical End Point of Active Window 0 (VEAW0)

LCD_DataWrite(0xdf); //Vertical End Point of Active Window [7:0]

LCD_CmdWrite(0x37); //Vertical End Point of Active Window 1 (VEAW1)

LCD_DataWrite(0x01); //Vertical End Point of Active Window [8]

#endif

#ifdef P800x480

//AT070TN92 setting

//============== Display Window800x480 ==================

/*

LCD_CmdWrite(0x04); //PCLK inverse

LCD_DataWrite(0x81);

Delay1ms(1);

//Horizontal set

LCD_CmdWrite(0x14); //HDWR//Horizontal Display Width Setting Bit[6:0]

LCD_DataWrite(0x63);//Horizontal display width(pixels) = (HDWR + 1)*8

LCD_CmdWrite(0x15); //Horizontal Non-Display Period Fine Tuning Option Register (HNDFTR)

LCD_DataWrite(0x03);//Horizontal Non-Display Period Fine Tuning(HNDFT) [3:0]

LCD_CmdWrite(0x16); //HNDR//Horizontal Non-Display Period Bit[4:0]

LCD_DataWrite(0x03);//Horizontal Non-Display Period (pixels) = (HNDR + 1)*8

LCD_CmdWrite(0x17); //HSTR//HSYNC Start Position[4:0]

LCD_DataWrite(0x02);//HSYNC Start Position(PCLK) = (HSTR + 1)*8

LCD_CmdWrite(0x18); //HPWR//HSYNC Polarity ,The period width of HSYNC.

LCD_DataWrite(0x00);//HSYNC Width [4:0] HSYNC Pulse width(PCLK) = (HPWR + 1)*8

//Vertical set

LCD_CmdWrite(0x19); //VDHR0 //Vertical Display Height Bit [7:0]

LCD_DataWrite(0xdf);//Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1a); //VDHR1 //Vertical Display Height Bit [8]

RAiO TECHNOLOGY INC. 12/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

LCD_DataWrite(0x01);//Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1b); //VNDR0 //Vertical Non-Display Period Bit [7:0]

LCD_DataWrite(0x14);//Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1c); //VNDR1 //Vertical Non-Display Period Bit [8]

LCD_DataWrite(0x00);//Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1d); //VSTR0 //VSYNC Start Position[7:0]

LCD_DataWrite(0x06);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1e); //VSTR1 //VSYNC Start Position[8]

LCD_DataWrite(0x00);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1f); //VPWR //VSYNC Polarity ,VSYNC Pulse Width[6:0]

LCD_DataWrite(0x01);//VSYNC Pulse Width(PCLK) = (VPWR + 1)

//LCD_CmdWrite(0xf2);

//LCD_DataWrite(0x01);

*/

//HSD050IDW1 setting

//============== Display Window800x480 ==================

LCD_CmdWrite(0x04); //PCLK inverse

LCD_DataWrite(0x81);

Delay1ms(1);

//Horizontal set

LCD_CmdWrite(0x14); //HDWR//Horizontal Display Width Setting Bit[6:0]

LCD_DataWrite(0x63);//Horizontal display width(pixels) = (HDWR + 1)*8

LCD_CmdWrite(0x15);//Horizontal Non-Display Period Fine Tuning Option Register (HNDFTR)

LCD_DataWrite(0x00);//Horizontal Non-Display Period Fine Tuning(HNDFT) [3:0]

LCD_CmdWrite(0x16); //HNDR//Horizontal Non-Display Period Bit[4:0]

LCD_DataWrite(0x03);//Horizontal Non-Display Period (pixels) = (HNDR + 1)*8

LCD_CmdWrite(0x17); //HSTR//HSYNC Start Position[4:0]

LCD_DataWrite(0x03);//HSYNC Start Position(PCLK) = (HSTR + 1)*8

LCD_CmdWrite(0x18); //HPWR//HSYNC Polarity ,The period width of HSYNC.

LCD_DataWrite(0x0B);//HSYNC Width [4:0] HSYNC Pulse width(PCLK) = (HPWR + 1)*8

//Vertical set

LCD_CmdWrite(0x19); //VDHR0 //Vertical Display Height Bit [7:0]

LCD_DataWrite(0xdf);//Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1a); //VDHR1 //Vertical Display Height Bit [8]

LCD_DataWrite(0x01);//Vertical pixels = VDHR + 1

LCD_CmdWrite(0x1b); //VNDR0 //Vertical Non-Display Period Bit [7:0]

LCD_DataWrite(0x20);//Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1c); //VNDR1 //Vertical Non-Display Period Bit [8]

LCD_DataWrite(0x00);//Vertical Non-Display area = (VNDR + 1)

LCD_CmdWrite(0x1d); //VSTR0 //VSYNC Start Position[7:0]

RAiO TECHNOLOGY INC. 13/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

LCD_DataWrite(0x16);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1e); //VSTR1 //VSYNC Start Position[8]

LCD_DataWrite(0x00);//VSYNC Start Position(PCLK) = (VSTR + 1)

LCD_CmdWrite(0x1f); //VPWR //VSYNC Polarity ,VSYNC Pulse Width[6:0]

LCD_DataWrite(0x01);//VSYNC Pulse Width(PCLK) = (VPWR + 1)

//Active window set

//setting active window X

LCD_CmdWrite(0x30); //Horizontal Start Point 0 of Active Window (HSAW0)

LCD_DataWrite(0x00); //Horizontal Start Point of Active Window [7:0]

LCD_CmdWrite(0x31); //Horizontal Start Point 1 of Active Window (HSAW1)

LCD_DataWrite(0x00); //Horizontal Start Point of Active Window [9:8]

LCD_CmdWrite(0x34); //Horizontal End Point 0 of Active Window (HEAW0)

LCD_DataWrite(0x1F); //Horizontal End Point of Active Window [7:0]

LCD_CmdWrite(0x35); //Horizontal End Point 1 of Active Window (HEAW1)

LCD_DataWrite(0x03); //Horizontal End Point of Active Window [9:8]

//setting active window Y

LCD_CmdWrite(0x32); //Vertical Start Point 0 of Active Window (VSAW0)

LCD_DataWrite(0x00); //Vertical Start Point of Active Window [7:0]

LCD_CmdWrite(0x33); //Vertical Start Point 1 of Active Window (VSAW1)

LCD_DataWrite(0x00); //Vertical Start Point of Active Window [8]

LCD_CmdWrite(0x36); //Vertical End Point of Active Window 0 (VEAW0)

LCD_DataWrite(0xdf); //Vertical End Point of Active Window [7:0]

LCD_CmdWrite(0x37); //Vertical End Point of Active Window 1 (VEAW1)

LCD_DataWrite(0x01); //Vertical End Point of Active Window [8]

#endif

}

RAiO TECHNOLOGY INC. 14/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

3. Display on Sequence

RA8875_RESET = 0;

Delay 1 ms;

RA8875_RESET = 1;

Delay 10 ms;

PLL initial setting

LCD initial setting

Write data to RA8875

display RAM

Display on setting :

LCD_CmdWrite(0x01);

LCD_DataWrite(0x80);

TFT LCD Backlight on

Figure 3-1

RAiO TECHNOLOGY INC. 15/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

4. Sleep Mode Sequence

Enter Sleep :

TFT LCD Backlight off

Set RA8875 display off :

LCD_CmdWrite(0x01);

LCD_DataWrite(0x00);

Delay100ms(1);

Set sleep mode:

LCD_CmdWrite(0x01);

LCD_DataWrite(0x02);

Figure 4-1

*Attention:

We suggest to confirm your TFT panel could be disable when the RA8875 enter sleep, to avoid liquid

crystal polarization.RAiO shall not be held liable for any damages about TFT panel ,when customers use

sleep mode incorrect !

RAiO TECHNOLOGY INC. 16/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

Exit Sleep :

Set exit sleep:

LCD_CmdWrite(0x01);

LCD_DataWrite(0x00);

Delay 100ms

Display on setting :

LCD_CmdWrite(0x01);

LCD_DataWrite(0x80);

Delay100ms(1);

TFT LCD Backlight on

Figure 4-2

RAiO TECHNOLOGY INC. 17/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

5. Display RAM pure data write example

Include RA8875_subrotine.c first , then refer the code below.

If MCU 8 bit interface :

Graphic_Mode( ); //set to graphic mode

XY_Coordinate(0,0); //set write cursor position

LCD_CmdWrite(0x02);//set CMD [02h] before data write

for (i=384000;i>0;i--)

{ LCD_DataWrite(0xf8); // write color red data

LCD_DataWrite(0x00);

}

If MCU 16 bit interface :

Graphic_Mode( ); //set to graphic mode

XY_Coordinate(0,0); //set write cursor position

LCD_CmdWrite(0x02);// //set CMD [02h] before data write

for (i=384000;i>0;i--)

{ LCD_DataWrite(0xf800); }// write color red data

You could download some example code and RA8875 subrotine on the website :

www.raio.com.tw

RAiO TECHNOLOGY INC. 18/19 www.raio.com.tw

RA8875

Version 1.1 Application Note

6. Appendix

a. How to program the Serial Flash Memory by the external programmer?

If the advance circuit is already designed by the LCM factory as the following picture1 and picture2, just

leading the related pins of the serial flash out to the connector and then the user will be able to program the

picture data(*.bin) by the external memory programmer. Please refer to the following pinture3.

The resisters(R136~R139) should be

took out when the serial flash memory is

programmed by the external memory

programmer.

Picture3

RAiO TECHNOLOGY INC. 19/19 www.raio.com.tw

You might also like

- Content Beyond SyllabusDocument3 pagesContent Beyond SyllabusRahul PolNo ratings yet

- Introduction To Mikroc PRO For PIC12Document27 pagesIntroduction To Mikroc PRO For PIC12Anonymous 0OpfKVQNo ratings yet

- AUO 42 Inch Led Panel DataDocument32 pagesAUO 42 Inch Led Panel DataVenkatesh SubramanyaNo ratings yet

- LCD Dot Matrix Display Single LineDocument9 pagesLCD Dot Matrix Display Single LineMd MansoorNo ratings yet

- Datasheet Red - DVR Rtl8211f-Cg c187932Document69 pagesDatasheet Red - DVR Rtl8211f-Cg c187932Luis Felipe CasasNo ratings yet

- RF Interfacing With 8051 FriendlyDocument14 pagesRF Interfacing With 8051 Friendlysrinu5890% (1)

- Example: Input Pin TestingDocument14 pagesExample: Input Pin Testinghasan911No ratings yet

- Exp-04Document7 pagesExp-04Prisha SinghaniaNo ratings yet

- LTN133AT01Document28 pagesLTN133AT01Selmar CavalcantiNo ratings yet

- Lab Manual Part 2 UpdatedDocument12 pagesLab Manual Part 2 UpdatedPradyumna GRNo ratings yet

- Aou A121ew01 v0Document18 pagesAou A121ew01 v0divubi2004No ratings yet

- Pic 16 C 711Document8 pagesPic 16 C 711Michael LiuNo ratings yet

- LCD Grafico Wg12864aDocument25 pagesLCD Grafico Wg12864aseykarimNo ratings yet

- 8051 Enhanced)Document58 pages8051 Enhanced)Vinay Nagnath Jokare100% (1)

- FCR2XX7 Service Manual CDocument632 pagesFCR2XX7 Service Manual CArshad Jummani100% (4)

- Lc315tu3a Panda PDFDocument23 pagesLc315tu3a Panda PDFAli MontielNo ratings yet

- Write A Program For Interfacing The 16x2 LCD MODULES AimDocument7 pagesWrite A Program For Interfacing The 16x2 LCD MODULES AimLeelasrikanth TubatiNo ratings yet

- Aou A121ew02 V0 PDFDocument26 pagesAou A121ew02 V0 PDFdivubi2004No ratings yet

- MES Lab ManualDocument77 pagesMES Lab ManualNavya MNo ratings yet

- Real Time Digital Clock ReportDocument14 pagesReal Time Digital Clock ReportNoor AhmedNo ratings yet

- 00 Aw RTPDDocument36 pages00 Aw RTPDFred 2Rockstar100% (1)

- Sharp Lq065t5ar01 Lcdpanel DatasheetDocument33 pagesSharp Lq065t5ar01 Lcdpanel Datasheetkarol1301No ratings yet

- Section 15. Quadrature Encoder Interface (QEI) HighlightsDocument35 pagesSection 15. Quadrature Encoder Interface (QEI) HighlightsSourabh KhandelwalNo ratings yet

- Evd19i018-Esdp Lab 9Document18 pagesEvd19i018-Esdp Lab 9Jampani sarath chandraNo ratings yet

- Interfacing The Densitron LCD To The 8051: February 1996Document10 pagesInterfacing The Densitron LCD To The 8051: February 1996Bhanu DanduNo ratings yet

- Direct Drive LCDDocument13 pagesDirect Drive LCDTrijeth DatlaNo ratings yet

- Lab 05-Interfacing LCD and Pic C and Its ApplicationDocument4 pagesLab 05-Interfacing LCD and Pic C and Its ApplicationNida AliNo ratings yet

- Specification FOR Approval: 15.4" Wxga TFT LCD TitleDocument31 pagesSpecification FOR Approval: 15.4" Wxga TFT LCD TitleDaniel GómezNo ratings yet

- LCD Driver For The HC08/HCS08 Family: Application NoteDocument12 pagesLCD Driver For The HC08/HCS08 Family: Application NoteCarlos BallezaNo ratings yet

- HD 61202Document5 pagesHD 61202kalangeNo ratings yet

- LS07 Chassis Service ManualDocument33 pagesLS07 Chassis Service ManualnaughtybigboyNo ratings yet

- Datasheet pdf - http://www.DataSheet4U.netDocument26 pagesDatasheet pdf - http://www.DataSheet4U.netMugia LanaNo ratings yet

- LMB 162 AdcDocument11 pagesLMB 162 AdcMohamedSalahNo ratings yet

- Rtl8211fsi Vs CGDocument100 pagesRtl8211fsi Vs CGDhananjay MathaneNo ratings yet

- DatasheetDocument12 pagesDatasheetsanseh20019016No ratings yet

- LCD DisplayDocument3 pagesLCD DisplayNARENDRA SENCHA100% (1)

- Line Following Code For Firebird VDocument6 pagesLine Following Code For Firebird VSivaji KumarNo ratings yet

- Test CodeDocument20 pagesTest Codeantonio vukeNo ratings yet

- 8051 TutorialDocument47 pages8051 TutorialSumit OjhaNo ratings yet

- Lab 7Document9 pagesLab 7zaqNo ratings yet

- Panel AUO T460HW04 V3 0 (DS)Document26 pagesPanel AUO T460HW04 V3 0 (DS)Javier PellejeroNo ratings yet

- Link Budget Analysis Guide: November 21, 2014Document19 pagesLink Budget Analysis Guide: November 21, 2014Анатолий МаловNo ratings yet

- Anadolu University Department of Electrical & Electronics Engineering EEM 336 Microprocessors 1 CHARACTER LCD INTERFACEDocument32 pagesAnadolu University Department of Electrical & Electronics Engineering EEM 336 Microprocessors 1 CHARACTER LCD INTERFACESĩ Anh NguyễnNo ratings yet

- Ancortek Manual V1.0 20150601Document21 pagesAncortek Manual V1.0 20150601Wesley GeorgeNo ratings yet

- GPS Leica-Rx1200 ManualDocument210 pagesGPS Leica-Rx1200 ManualalejoelingNo ratings yet

- DSP Digital Signal Processing Hardware Manual: Techno AP CorporationDocument9 pagesDSP Digital Signal Processing Hardware Manual: Techno AP CorporationOmar SuarezNo ratings yet

- LTY400HM01Document28 pagesLTY400HM01plasma plasmaNo ratings yet

- 8051 Architecture (Enhanced) OctY09Document59 pages8051 Architecture (Enhanced) OctY09Santhoshreddy GogulaNo ratings yet

- RPMDocument18 pagesRPMCarlos Alberto Venancio PerezNo ratings yet

- Taxi Fare MeterDocument6 pagesTaxi Fare MeterJawad malik0% (2)

- Submitted By: Aanchal Chaudhary Enrollment No.-Jnu-jpr-2011/00871Document17 pagesSubmitted By: Aanchal Chaudhary Enrollment No.-Jnu-jpr-2011/00871Sonu LovesforuNo ratings yet

- LCD character programming and animation using AVR microcontrollerDocument21 pagesLCD character programming and animation using AVR microcontrollerLiakNo ratings yet

- Section 15 QuadratureEncoderInterface (QEI)Document24 pagesSection 15 QuadratureEncoderInterface (QEI)Abraham MuñozNo ratings yet

- Embedded Systems Lab ManualDocument60 pagesEmbedded Systems Lab Manualtmuthu123100% (1)

- Sensor STVI101WT-01Document36 pagesSensor STVI101WT-01Efraín Jara CasteloNo ratings yet

- Datasheet SHARPDocument23 pagesDatasheet SHARPedilsonbomtempoNo ratings yet

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCFrom EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNo ratings yet

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Distributed Process Control ReportFrom EverandDistributed Process Control ReportNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- DSE CN3065 Specs PDFDocument11 pagesDSE CN3065 Specs PDFLeeNo ratings yet

- MCP73871 Demo Board With Voltage Proportional Current Control User's GuideDocument24 pagesMCP73871 Demo Board With Voltage Proportional Current Control User's GuideGonzalo RiveraNo ratings yet

- Distributed By:: Electronics Parts and KitsDocument8 pagesDistributed By:: Electronics Parts and KitsGonzalo RiveraNo ratings yet

- MB1136Document4 pagesMB1136laurentiu.melinteNo ratings yet

- Specification: Product Type: 7" LCD Nunmber: Module NumberDocument16 pagesSpecification: Product Type: 7" LCD Nunmber: Module NumberGonzalo RiveraNo ratings yet

- Relay Iso9002: (Unit:mm) (Unit:mm)Document2 pagesRelay Iso9002: (Unit:mm) (Unit:mm)Gabun KirillNo ratings yet

- 7 Inch Display DatasheetDocument27 pages7 Inch Display DatasheetMuhammad ZanuarNo ratings yet

- RA8875 DS V19 EngDocument178 pagesRA8875 DS V19 EngGonzalo RiveraNo ratings yet

- SIM7070 - SIM7080 - SIM7090 Series - Linux - Application Note - V1.02Document18 pagesSIM7070 - SIM7080 - SIM7090 Series - Linux - Application Note - V1.02Gonzalo RiveraNo ratings yet

- Micronote 128 1 Unidirectional/Bidirectional Tvs DifferencesDocument3 pagesMicronote 128 1 Unidirectional/Bidirectional Tvs DifferencesGonzalo RiveraNo ratings yet

- Force Sensor Vibration Motor PCB Circuit DiagramDocument1 pageForce Sensor Vibration Motor PCB Circuit DiagramGonzalo RiveraNo ratings yet

- Pi Mbus 300 PDFDocument121 pagesPi Mbus 300 PDFhipercortexNo ratings yet

- Sidewinder - Current Sensor: Low Frequency Equivalent CircuitDocument3 pagesSidewinder - Current Sensor: Low Frequency Equivalent CircuitGonzalo RiveraNo ratings yet

- Applications Information: Linear Hall-Effect Sensor IcsDocument9 pagesApplications Information: Linear Hall-Effect Sensor IcsGonzalo RiveraNo ratings yet

- Quectel M95 R2.0 Upgrade Application Note V1.0Document18 pagesQuectel M95 R2.0 Upgrade Application Note V1.0Gonzalo RiveraNo ratings yet

- Atmel 46104 SE M90E36A ApplicationNoteDocument43 pagesAtmel 46104 SE M90E36A ApplicationNoteKaik Wulck BassanelliNo ratings yet

- ACS712 DatasheetDocument15 pagesACS712 DatasheetwirawansatriaNo ratings yet

- TouchDocument19 pagesTouchmartintinceNo ratings yet

- Modbus RTU Serial Communications ManualDocument76 pagesModbus RTU Serial Communications ManualJonathan Fruelda100% (1)

- CortexDocument3 pagesCortexViraj Jain100% (1)

- UOP ATMega Handbook 1 0Document15 pagesUOP ATMega Handbook 1 0prashanttyagi85No ratings yet

- Atmel AVR Micro Controller Primer - Programming and InterfacingDocument195 pagesAtmel AVR Micro Controller Primer - Programming and Interfacingjfg872189% (9)

- SSD 1298Document82 pagesSSD 1298Gonzalo RiveraNo ratings yet

- PEC IT 601D CA3 SuggestionDocument2 pagesPEC IT 601D CA3 SuggestionrealaryaroyNo ratings yet

- PanodicDocument5 pagesPanodicAlexander WieseNo ratings yet

- LTW32/42DV-SERVICE MANUAL TROUBLESHOOTING GUIDEDocument44 pagesLTW32/42DV-SERVICE MANUAL TROUBLESHOOTING GUIDEMaria de GuerreroNo ratings yet

- LG PW1500 1500 Lumen Minibeam LED Projector With Screen Share and Bluetooth Sound OutDocument1 pageLG PW1500 1500 Lumen Minibeam LED Projector With Screen Share and Bluetooth Sound OutWebAntics.com Online Shopping StoreNo ratings yet

- Manual Samsung PL-42C91HPDocument56 pagesManual Samsung PL-42C91HPGeovanny Saldarriaga AristizabalNo ratings yet

- Omputersony November 2014 V1 Component & PC PricelistDocument90 pagesOmputersony November 2014 V1 Component & PC PricelistRidah SolomonNo ratings yet

- LG 29wq600Document4 pagesLG 29wq600johnyNo ratings yet

- Transformers The Last Knight.2017.HC.HDRip.XviD.AC3-EVODocument1 pageTransformers The Last Knight.2017.HC.HDRip.XviD.AC3-EVORAMAKRISHNAN RNo ratings yet

- KDL 40ex657Document51 pagesKDL 40ex657Alexander VillalbaNo ratings yet

- Sony Klv-40x200a Klv-46x200a Klv-40x250a Klv-46x250a Chassis FixDocument125 pagesSony Klv-40x200a Klv-46x200a Klv-40x250a Klv-46x250a Chassis FixjimkarnoNo ratings yet

- Phillips Universal Remote Sbc-Ru-252Document18 pagesPhillips Universal Remote Sbc-Ru-252Malo ModeNo ratings yet

- Monitor LG L1953SDocument35 pagesMonitor LG L1953SjsalvagaiaNo ratings yet

- THC-B120-PC 2 MP EXIR Bullet Camera: Key FeaturesDocument3 pagesTHC-B120-PC 2 MP EXIR Bullet Camera: Key FeaturesMega VoltNo ratings yet

- TV Diggio 32Document42 pagesTV Diggio 32JesucristoEsmividaNo ratings yet

- Polaroid FLU 2632Document46 pagesPolaroid FLU 2632simipopaNo ratings yet

- WF70A6TIAGDNN0Document6 pagesWF70A6TIAGDNN0Matthew Sa LoneNo ratings yet

- Samsung Le22b450c4w PDFDocument318 pagesSamsung Le22b450c4w PDFgnormaNo ratings yet

- YA587 r005Document28 pagesYA587 r005taraservNo ratings yet

- Samsung LE32S86BC ManualDocument176 pagesSamsung LE32S86BC ManualJanne JäppinenNo ratings yet

- Manual TV SamsungDocument61 pagesManual TV SamsungRubén Medina HerreraNo ratings yet

- The Cathode Ray TubeDocument13 pagesThe Cathode Ray Tubeapi-269382043No ratings yet

- In Focus Projector 114Document3 pagesIn Focus Projector 114Bams SubagioNo ratings yet

- Best Region Free 3D Blu-ray PlayerDocument16 pagesBest Region Free 3D Blu-ray PlayerJohnny OhNo ratings yet

- MPEG Video Coding I - MPEG-1 and 2: 11.1 Overview 11.2 MPEG-1 11.3 MPEG-2 11.4 Further ExplorationDocument20 pagesMPEG Video Coding I - MPEG-1 and 2: 11.1 Overview 11.2 MPEG-1 11.3 MPEG-2 11.4 Further Explorationgayathri.seelamNo ratings yet

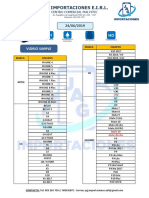

- Jag Importaciones E.I.R.L.: Vidrio SimpleDocument4 pagesJag Importaciones E.I.R.L.: Vidrio SimpleJhon Ramón HuariNo ratings yet

- DVDP 355Document62 pagesDVDP 355milorad24No ratings yet

- Tracker Tsel Ver3Document1,754 pagesTracker Tsel Ver3telkominfra.jabotabekNo ratings yet

- Silver Crest KH2150 enDocument38 pagesSilver Crest KH2150 enWildWest100% (1)

- Product Specification: Preliminary Specification (V) Final SpecificationDocument20 pagesProduct Specification: Preliminary Specification (V) Final Specificationเกียรติศักดิ์ ภูมิลาNo ratings yet

- Dell 27 Monitor - E2720H Data SheetDocument4 pagesDell 27 Monitor - E2720H Data SheetShakilNo ratings yet