Professional Documents

Culture Documents

Unit 42 Pages From 0625 - s14 - QP - 32

Uploaded by

Little FishOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Unit 42 Pages From 0625 - s14 - QP - 32

Uploaded by

Little FishCopyright:

Available Formats

17

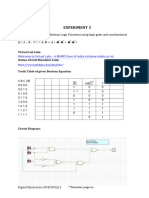

10 (a) Fig. 10.1 shows a digital logic circuit, not using the recognised symbols.

AND gate

input A D

input B

OR gate

output E

input C

Fig. 10.1

Complete the table below to indicate the logic levels of points D and E in the circuit, when

points A, B and C are at the logic levels indicated.

0 represents low or off. 1 represents high or on.

A B C D E

0 0 0

0 0 1

1 1 1

[3]

(b) Draw the recognised symbol for an AND gate.

[1]

(c) A NAND gate can be replaced by an AND gate and a NOT gate.

Draw a diagram to show how the AND gate and the NOT gate should be connected. Label

clearly the logic gates and any input or output.

[2]

[Total: 6]

© UCLES 2014 0625/32/M/J/14 [Turn over

You might also like

- Faculty of Computing and Informatics Multimedia UniversityDocument11 pagesFaculty of Computing and Informatics Multimedia UniversityBala GanabathyNo ratings yet

- 1 Syed Hasan Saeed, Integral University, LucknowDocument33 pages1 Syed Hasan Saeed, Integral University, LucknowRockRahilNo ratings yet

- CEJ - ECE 3rd - Unit No.1 - Decoder & Encoder - DSDDocument32 pagesCEJ - ECE 3rd - Unit No.1 - Decoder & Encoder - DSDsonu sreekumarNo ratings yet

- Encoder and DecoderDocument30 pagesEncoder and DecoderSuresh KumarNo ratings yet

- Data-Processing Circuits 3.2Document83 pagesData-Processing Circuits 3.2DEEPAK UPADHYAYNo ratings yet

- Digital Logic Design Exp. No. 10Document20 pagesDigital Logic Design Exp. No. 10Abbas RaxaNo ratings yet

- CE Low, WE Low: RAM Horizontal Expansion (Using IC 7489)Document2 pagesCE Low, WE Low: RAM Horizontal Expansion (Using IC 7489)d dNo ratings yet

- Homework #3 Solution: Department of Electrical and Computer Engineering University of Wisconsin - MadisonDocument7 pagesHomework #3 Solution: Department of Electrical and Computer Engineering University of Wisconsin - MadisonPRAKRITI SANKHLANo ratings yet

- DSD Lab Manual 2021Document21 pagesDSD Lab Manual 2021adityaNo ratings yet

- MultiplexerDocument5 pagesMultiplexerhariNo ratings yet

- COA AktuDocument14 pagesCOA AktuIndexNo ratings yet

- Bayan University of Science and Technology Collage of EngineeringDocument31 pagesBayan University of Science and Technology Collage of EngineeringOmur NoorNo ratings yet

- 271 6 PDFDocument5 pages271 6 PDFpriyanshiNo ratings yet

- Lab 9 Encoders and DecodersDocument7 pagesLab 9 Encoders and Decoderssafdarmunir070No ratings yet

- Experiment-11 BCD Code To 7-Segment Decoder 11-1 ObjectDocument3 pagesExperiment-11 BCD Code To 7-Segment Decoder 11-1 ObjectMohammed Dyhia AliNo ratings yet

- Decoders and EncodersDocument7 pagesDecoders and EncodersEstefania GuarnizoNo ratings yet

- Experiment 10: Multiplexers: Mr. Mohamed El-SaiedDocument4 pagesExperiment 10: Multiplexers: Mr. Mohamed El-SaiedEstéfano GómezNo ratings yet

- Experiment 4 - DDCADocument6 pagesExperiment 4 - DDCAsaikrishnavarma50No ratings yet

- American International University-Bangladesh: Title: Design of A 2 To 4 Decoder and A Decimal To BCD EncoderDocument4 pagesAmerican International University-Bangladesh: Title: Design of A 2 To 4 Decoder and A Decimal To BCD EncoderAbid ChowdhuryNo ratings yet

- 4, Encoder & Decoder MUX and DEMUX EEngDocument46 pages4, Encoder & Decoder MUX and DEMUX EEngIsrael EliasNo ratings yet

- Combinational Circuit IIT DelhiDocument2 pagesCombinational Circuit IIT DelhiSimone SinghNo ratings yet

- DLD Lab 8Document10 pagesDLD Lab 8KING BotNo ratings yet

- Seven Segments ReportDocument12 pagesSeven Segments ReportJun TobiasNo ratings yet

- DSD BookDocument270 pagesDSD BookROUGH X YTNo ratings yet

- Modul Minggu Ke-2 (DB6 Dan DB7)Document14 pagesModul Minggu Ke-2 (DB6 Dan DB7)farrel prambudiNo ratings yet

- DP-Assignment Brief A1 - UpdatedDocument12 pagesDP-Assignment Brief A1 - UpdatedTân NguyễnNo ratings yet

- Multiplexers & Demultiplexers: Object: TheoryDocument4 pagesMultiplexers & Demultiplexers: Object: TheoryMonir JihadNo ratings yet

- Addis Ababa University: (DLD-Assignment 1)Document7 pagesAddis Ababa University: (DLD-Assignment 1)mesfinNo ratings yet

- Presentation 1Document14 pagesPresentation 1Tapu GhoshNo ratings yet

- EE2205Document2 pagesEE2205Harsh AgarwalNo ratings yet

- Unit 42 Pages From 0625 - s13 - QP - 33Document2 pagesUnit 42 Pages From 0625 - s13 - QP - 33Little FishNo ratings yet

- 8 To 3 Bit Priority EncoderDocument12 pages8 To 3 Bit Priority EncoderDev SejvaniNo ratings yet

- SD Lec 7Document13 pagesSD Lec 7Harsh AgarwalNo ratings yet

- Modul Minggu Ke-2 (DB6 Dan DB7)Document15 pagesModul Minggu Ke-2 (DB6 Dan DB7)Eden HamamNo ratings yet

- Wa0002.Document15 pagesWa0002.wocison461No ratings yet

- KIE1003 Tutorial6Document3 pagesKIE1003 Tutorial6brainnytanNo ratings yet

- Chapter 3 Data Processing CircuitDocument26 pagesChapter 3 Data Processing CircuitKiddozesNo ratings yet

- Demp Mid-1 Bit BankDocument5 pagesDemp Mid-1 Bit BankMᴀɴɪ TᴇᴊᴀNo ratings yet

- 01 Combinatorial LogicDocument29 pages01 Combinatorial LogicagungNo ratings yet

- Pages From 0625 - w22 - QP - 42 - Q9 - Chapter 4Document2 pagesPages From 0625 - w22 - QP - 42 - Q9 - Chapter 4lelon81No ratings yet

- Exp-3 HarviDocument5 pagesExp-3 Harviharvi.kotadiya121816No ratings yet

- WE Low: RAM Vertical Expansion (Using IC 7489 and IC 7404)Document1 pageWE Low: RAM Vertical Expansion (Using IC 7489 and IC 7404)d dNo ratings yet

- 4-Bit Synchronous Counter: Final ProjectDocument7 pages4-Bit Synchronous Counter: Final Projectahmed IsmailNo ratings yet

- DECODERDocument13 pagesDECODERanzilshahjahan1No ratings yet

- American International University-BangladeshDocument7 pagesAmerican International University-Bangladeshanon_776365175No ratings yet

- TEST1 Revision PracticeDocument16 pagesTEST1 Revision Practicemarksman471No ratings yet

- CS101 Assignment Mc220203384Document2 pagesCS101 Assignment Mc220203384Careers LahoreNo ratings yet

- Ece 218 Spring 21 Final Exam 2Document2 pagesEce 218 Spring 21 Final Exam 2Anh Quân Nguyễn ThắngNo ratings yet

- Comb CircuitsDocument12 pagesComb CircuitskauyaNo ratings yet

- DLCmanual 4Document7 pagesDLCmanual 4Md Shamin YasarNo ratings yet

- Lab7: Part (A) : Design of 2-Out-Of-5 To BCD Code Converter With DisplayDocument7 pagesLab7: Part (A) : Design of 2-Out-Of-5 To BCD Code Converter With DisplaySanan yaqoobNo ratings yet

- Experiment-7 Design A Binary Subtractor Circuit Half and Full Subtractor 7-1 ObjectDocument4 pagesExperiment-7 Design A Binary Subtractor Circuit Half and Full Subtractor 7-1 ObjectMohammed Dyhia AliNo ratings yet

- STLD ObjDocument8 pagesSTLD ObjshyamNo ratings yet

- TestcieeDocument7 pagesTestcieefallonNo ratings yet

- Bayan University of Science and Technology Collage of EngineeringDocument21 pagesBayan University of Science and Technology Collage of EngineeringOmur NoorNo ratings yet

- ECE20022 Assignment Module 1 2 3Document3 pagesECE20022 Assignment Module 1 2 3Nandini PandeyNo ratings yet

- Combinational Digital Design Laboratory Manual: Experiment #8 Decoders & EncodersDocument10 pagesCombinational Digital Design Laboratory Manual: Experiment #8 Decoders & EncodersJaideep Singh100% (1)

- Name: Syed Ali Haider Class: Bsse Iii-A (Morning) ROLL NO: NUML-F19-13701 DATE: 30-11-2020 Submitted To: Ma'Am Benish ShafreenDocument5 pagesName: Syed Ali Haider Class: Bsse Iii-A (Morning) ROLL NO: NUML-F19-13701 DATE: 30-11-2020 Submitted To: Ma'Am Benish ShafreenRoastinG DhabbaNo ratings yet

- Lab 4Document4 pagesLab 4KianJohnCentenoTuricoNo ratings yet

- Unit 42 Pages From Paper 3 (Nov)Document1 pageUnit 42 Pages From Paper 3 (Nov)Little FishNo ratings yet

- Pages From 0625 - s21 - QP - 62Document2 pagesPages From 0625 - s21 - QP - 62Little FishNo ratings yet

- Pages From 0625 - w18 - QP - 63Document4 pagesPages From 0625 - w18 - QP - 63Little FishNo ratings yet

- Pages From 0625 - s17 - QP - 63Document5 pagesPages From 0625 - s17 - QP - 63Little FishNo ratings yet

- Pages From 0625 - s18 - QP - 62Document3 pagesPages From 0625 - s18 - QP - 62Little FishNo ratings yet

- Pages From 0625 - s21 - QP - 62-2Document3 pagesPages From 0625 - s21 - QP - 62-2Little FishNo ratings yet

- Pages From 0625 - s21 - QP - 62-4Document2 pagesPages From 0625 - s21 - QP - 62-4Little FishNo ratings yet

- Y8 Unit 2 Sequences, Expressions and FormulaeDocument2 pagesY8 Unit 2 Sequences, Expressions and FormulaeLittle FishNo ratings yet

- Cambridge International AS & A Level: PHYSICS 9702/05Document8 pagesCambridge International AS & A Level: PHYSICS 9702/05Little FishNo ratings yet